## **CMOS Dual Counter-Timer**

#### Features:

- Compatible with general-purpose and CDP1800-series microprocessor systems

- Two 16-bit down-counters and two 8-bit control registers

- 5 modes including a versatile variable-duty cycle mode

- Programmable gate-level select

- Two-complemented output pins for each counter-timer

- Software-controlled interrupt output

- Addressable in memory space or CDP1800-series I/O space

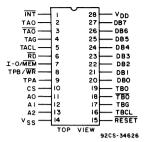

TERMINAL ASSIGNMENT

The RCA-CDP1878 and CDP1878C<sup> $\Delta$ </sup> are dual countertimers consisting of two 16-bit programmable down counters that are independently controlled by separate control registers. The value in the registers determine the mode of operation and control functions. Counters and registers are directly addressable in memory space by any general-industry-type microprocessors, in addition to input/output mapping with the CDP1800-series microprocessors.

Each counter-timer can be configured in five modes with the additional flexibility of gate-level control. The control registers in addition to mode formatting, allow software start and stop, interrupt enable, and an optional read control that allows a stable readout from the counters. Each counter-timer has software control of a common interrupt output with an interrupt status register indicating which counter-timer has timed out.

In addition to the interrupt output, true and complemented outputs are provided for each counter-timer for control of peripheral devices.

The CDP1878 and CDP1878C are functionally identical. They differ in that the CDP1878 has a recommended operating voltage range of 4 to 10.5 volts, and the CDP1878C has a recommended operating voltage range of 4 to 6.5 volts. These types are supplied in 28-lead dual-inline ceramic packages (D suffix), and 28-lead dual-in-line plastic packages (E suffix).

<sup>A</sup>Formerly RCA Dev. Type No. TA10981 and TA10981C, respectively

|   | Mode                     | Function                                                              | Application           |  |  |

|---|--------------------------|-----------------------------------------------------------------------|-----------------------|--|--|

| 1 | Timeout                  | Outputs change when clock decrements counter to "0"                   | Event counter         |  |  |

| 2 | Timeout Strobe           | One clockwide output pulse when clock decrements<br>counter to "0"    | Trigger pulse         |  |  |

| 3 | Gate-Controlled One Shot | Outputs change when clock decrements counter to "0".<br>Retriggerable | Time-delay generation |  |  |

| 4 | Rate Generator           | Repetitive clockwide output pulse                                     | Time-base generator   |  |  |

| 5 | Variable-Duty Cycle      | Repetitive output with programmed duty cycle                          | Motor control         |  |  |

### Table I - Mode Description

OPERATING CONDITIONS at  $T_A$ =Full Package-Temperature Range. For maximum reliability, operating conditions should be selected so that operation is always within the following ranges:

| CHARACTERISTIC                                                          | CD   | P1878 | CDP1 | UNITS |     |

|-------------------------------------------------------------------------|------|-------|------|-------|-----|

|                                                                         | Min. | Max.  | Min. | Max.  |     |

| DC Operating Voltage Range                                              | 4    | 10.5  | 4    | 6.5   |     |

| Input Voltage Range                                                     | VSS  | VDD   | VSS  | VDD   | , v |

| Maximum Clock Input Rise or<br>Fall Time t <sub>r</sub> ,t <sub>f</sub> | _    | 5     | -    | 5     | μs  |

| Minimum Clock Pulse Width twL, twH                                      | 200  | —     | 200  | —     | ns  |

| Maximum Clock Input Frequency, fCL                                      | DC   | 1     | DC   | 1     | MHz |

File Number 1341

### MAXIMUM RATINGS. Absolute-Maximum Values: DC SUPPLY-VOLTAGE RANGE, (VDD) (Voltage referenced to VSS terminal) CDP1878 .....-0.5 to +11 V CDP1878C .....-0 5 to +7 V POWER DISSIPATION PER PACKAGE (PD). For Ta=+60 to +85°C (PACKAGE TYPE E).....Derate Linearly at 12 mW/°C to 200 mW For T<sub>A</sub>=+100 to 125°C (PACKAGE TYPE D) .....Derate Linearly at 12 mW/°C to 200 mW DEVICE DISSIPATION PER OUTPUT TRANSISTOR OPERATING-TEMPERATURE RANGE (TA). STORAGE-TEMPERATURE RANGE (Tsta).....-65 to +150°C LEAD TEMPERATURE (DURING SOLDERING).

### STATIC ELECTRICAL CHARACTERISTICS at TA=-40 to +85° C, VDD $\pm$ 5%, Except as noted

|                          |                   | co                   | NDITIO        | NS      | LIMITS |          |          |       |         |      |       |

|--------------------------|-------------------|----------------------|---------------|---------|--------|----------|----------|-------|---------|------|-------|

| CHARACTERISTIC           |                   | ٧o                   | VIN           | VDD     |        | CDP1878  | 1        |       | CDP1878 | С    | UNITS |

|                          |                   | (V)                  | (V)           | (V)     | Min.   | Тур.●    | Max.     | Min.  | Тур.∙   | Max. |       |

| Quiescent Device Current | IDD               | -                    | 0, 5          | 5       | -      | 0.01     | 50       | -     | 0.02    | 200  | μA    |

| Output Low Drive         |                   | 0.4                  | 0, 10<br>0, 5 | 10<br>5 | 1.6    | 1<br>3.2 | 200      | 1.6   | 3.2     |      |       |

| (Sink) Current           | ΙΟL               | 0.5                  | 0, 10         | 10      | 2.6    | 5.2      | _        | _     | -       | _    |       |

| Output High Drive        |                   | 4.6                  | 0, 5          | 5       | -1.15  | -2.3     |          | -1.15 | -2.3    |      | mA    |

| (Source) Current         | юн                | 9.5                  | 0, 10         | 10      | -2.6   | -5.2     | _        | -     | _       |      |       |

| Output Voltage           |                   | -                    | 0, 5          | 5       | —      | 0        | 0.1      |       | 0       | 0.1  |       |

| Low-Level                | Vol‡              | -                    | 0, 10         | 10      | _      | 0        | 0.1      | _     | -       | -    |       |

| Output Voltage           |                   | -                    | 0, 5          | 5       | 4.9    | 5        | -        | 4.9   | 5       | —    | 1     |

| High Level               | Vон‡              | —                    | 0, 10         | 10      | 9.9    | 10       | _        | _     | —       |      | l v   |

| Input Low Voltage        | Vu                | 0545                 | -             | 5<br>10 | -      |          | 1.5<br>3 | -     | -       | 1.5  |       |

|                          |                   | 0545                 |               | 5       | 3.5    |          | -        | 3.5   | _       | _    |       |

| Input High Voltage       | Vін               | 0.5, 4.5<br>0.5, 9.5 | _             | 10      | 7      | —        | _        | _     | _       | _    |       |

| Input Leakage Current    | lin               | Anv I                | 0, 5          | 5       |        |          | ±1       | -     | —       | ±1   | μA    |

|                          |                   | Input                | 0, 10         | 10      |        | _        | ±2       |       | _       |      |       |

| Operating Current        | IDD1 <sup>4</sup> | -                    | 0, 5          | 5       | —      | 1.5      | 3        | -     | 1.5     | 3    | mA    |

| La sut Casa sita sa      | 0                 |                      | 0, 10         | 10      |        | 6        | 12       |       |         |      |       |

| Input Capacitance        | CIN               |                      |               |         |        | 5        | 7.5      |       | 5       | 7.5  | pF    |

| Output Capacitance       | COUT              |                      |               | -       | _      | 10       | 15       |       | 10      | 15   |       |

•Typical values are for  $T_A=25^{\circ}$  C and nominal  $V_{DD}$   $\ddagger I_{OL}=I_{OH}=1 \ \mu A.$

△Operating current is measured at 200 kHz for V<sub>DD</sub>=5 V and 400 kHz for V<sub>DD</sub>=10 V, with open outputs (worst-case frequencies for CDP1802A system operating at maximum speed of 3.2 MHz)

. CMOS Peripherals

CDP1878, CDP1878C

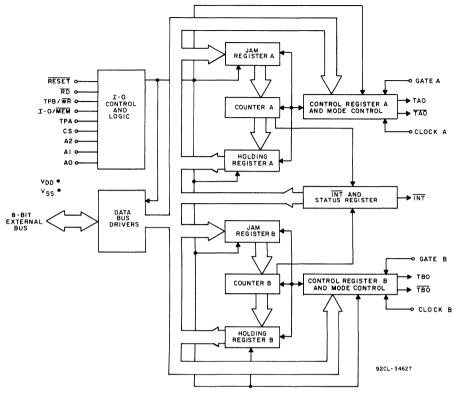

Fig. 1 - Functional diagram CDP1878 and CDP1878C.

### Functional Definitions for CDP1878 and CDP1878C Terminals

| TERMINAL                                              | USAGE                                                                                                                                                                                                       | TERMINAL           | USAGE                                                                                                                                     |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| VDD-VSS<br>DB0-DB7<br>TPB/WR, RD<br>A0, A1, A2        | Power<br>Data to and from device<br>Directional control signals<br>Addresses that select counters<br>or registers                                                                                           | CS<br>INT<br>RESET | Active high input that enables device<br>Low when counter is "0"<br>When active, TAO, TBO are low,<br>TAO, TBO are high. Interrupt status |

| TACL, TBCL<br>TAG, TBG<br>TAO, TAO<br>TBO, TBO<br>TPA | Clocks used to decrement counters<br>Gate inputs that control counters<br>Complemented outputs of Timer A<br>Complemented outputs of Timer B<br>Used with CDP1800-series processors,<br>tied high otherwise | I-O/MEM            | register is cleared<br>Tied high in CDP1800 input/output<br>mode, otherwise tied low                                                      |

### **REGISTER TRUTH TABLE**

| A  | DDRE | SS       | ACT    | IVE |                           |

|----|------|----------|--------|-----|---------------------------|

| A2 | A1   | A0       | TPB/WR | RD  | REGISTER OPERATION        |

| 1  | 1    | 0        | X      | •   | Write Counter A MSB       |

| 1  | 1    | 0        |        | X   | Read Counter A MSB        |

| 0  | 1    | 0        | X      |     | Write Counter A LSB       |

| 0  | 1    | 0        |        | X   | Read Counter A LSB        |

| 1  | 0    | 0        | X      |     | Control Register A        |

| 1  | 1    | 1        | X      |     | Write Counter B MSB       |

| 1  | 1    | 1        |        | X   | Read Counter B MSB        |

| 0  | 1    | 1        | X      |     | Write Counter B LSB       |

| 0  | 1    | 1        |        | X   | Read Counter B LSB        |

| 1  | 0    | 1        | X      |     | Control Register B        |

| 1  | 0    | 0        |        | x   |                           |

| 1  | 0    | 1        |        | x   | Interrupt Status Register |

| 0  | 0    | 0        |        |     | Not Used                  |

| 0  | 0    | 1        |        |     | Not Used                  |

| J  |      | <b>'</b> |        | I   | Not Used                  |

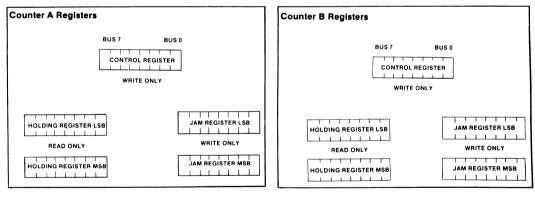

### **PROGRAMMING MODEL**

#### Functional Description—See Fig. 1

The dual counter-timer consists of two programmable 16bit down counters, separately addressable and controlled by two independent 8-bit control registers. The word in the control register determines the mode and type of operation that the counter-timer performs. Writing to or reading from a counter or register is enabled by selective addressing during a write or read cycle. The data is placed on the data bus by the microprocessor during the write cycle or read from the counter during the read cycle. Data to and from the counters and to the control registers is in binary format.

Each counter-timer consists of three parts. The first is the counter itself, a 16-bit down counter that is decremented on the trailing edge of the clock input. The second is the jam register that receives the data when the counter is written to. The word in the control register determines when the jam register value is placed into the counter. The third part is the holding register that places the counter value on the data bus when the counter is read.

When the counter has decremented to zero, three events occur. The first involves the common interrupt output pin that, if enabled, becomes active low. The second is the setting of a bit in the interrupt status register. This register can be read to determine which counter-timer has timed out. The third event is the logic change of the complemented output pins.

In addition to the clock input used to decrement the counter, a gate input is available to enable or initiate operation. The counter-timers are independent and can have different mode operations.

#### Write Operation

The counters and registers are separately addressable and are programmed via the data bus when the chip is selected with the TPB/WR pin active. Normal sequencing requires that the counter jam register be loaded first with the required value (most significant and least significant byte

# CDP1878, CDP1878C

in any order), and then the control register be accessed and loaded with the control word. The trailing edge of the TPB/WR pulse will latch the control word into the control register. The trailing edge of the first clock to occur with gate valid will cause the counter to be jammed with its initial value. The counter will decrement on the trailing edge of succeeding clocks as long as the gate is valid, until it reaches zero. The output levels will then change, and if enabled, the interrupt output will become active and the appropriate timer bit will be set in the interrupt status register. The interrupt output and the interrupt status register can be cleared (to their inactive state) by addressing the control register with the TPB/WR line active. For example, if counter A times out, control register A must be accessed to reset the interrupt output high and reset the timer A bit in the status register low. Timer B bit in the status register will be unaffected.

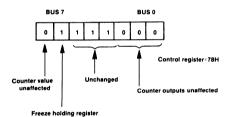

#### **Read Operation**

Each counter has a holding register that is continuously being updated by the counter and is accessed when the counter is addressed during read cycles. Counter reads are accomplished by halting the holding register directly. If the holding register is read directly, data will appear on the bus if the counters are addressed with the  $R\overline{D}$  line active. However, if the clock decrements the counter between the two read operations (most and least significant byte), an inaccurate value will be read. To preclude this from happening, writing a "1" into bit 6 of the control register and then addressing and reading the counter will result in a stable reading. This operation prevents the holding register from being updated by the counter and does not affect the counter's operation.

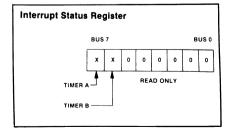

The interrupt status register is read by addressing either control register with the RD line active. A "1" in bit 7 indicates Timer A has timed out and a "1" in bit 6 indicates Timer B has timed out. Bits 0-5 are zeros.

#### **Control Register**

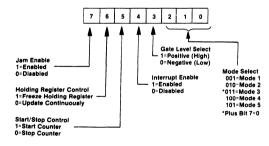

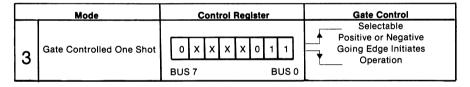

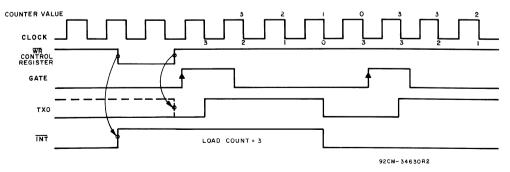

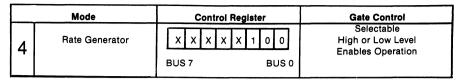

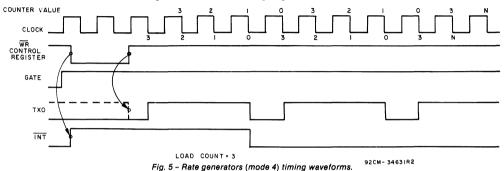

Bits 0, 1 and 2 — Mode Selects—See Mode Timing Diagrams (Figs. 2, 3, 4, 5 and 6).

|                                               | Bit 7 | Bit 2 | Bit 1 | Bit 0 |

|-----------------------------------------------|-------|-------|-------|-------|

| Mode 1 — Timeout                              | _     | 0     | 0     | 1     |

| Mode 2 — Timeout Strobe                       | -     | 0     | 1     | 0     |

| Mode 3 — Gate Controlled One Shot             | 0     | 0     | 1     | 1     |

| Mode 4 — Rate Generator                       | _     | 1     | 0     | 0     |

| Mode 5 — Variable-Duty Cycle                  | -     | 1     | 0     | 1     |

| No Mode selected. Counter outputs unaffected. | -     | 0     | 0     | 0     |

Note: When selecting a mode, the timer outputs TAO and TBO are set low, and TAO and TBO are set high. If bits 0, 1 and 2 are all zero's when the control register is loaded, no

mode is selected, and the counter-timer outputs are unaffected. Issuing mode 6 will cause an indeterminate condition of the counter, issuing mode 7 is equivalent to issuing mode 5.

**Bit 3**—Gate level select—All modes require an enabling signal on the gate to allow counter operation. This enabling signal is either a level or a pulse (edge). Positive gate level or edge enabling is selected by writing a "1" into this bit and negative (low) enabling is selected when bit 3 is "0".

Bit 4—Interrupt enable—Setting this bit to "1" enables the INT output, and setting it to "0" disables it. When reset, the INT output is at a high level. If the interrupt enable bit in the control register is enabled and the counter decrements to zero, the INT output will go low and will not return high until the counter-timer is reset or the selected control register is written to. Example: If timer B times out, control register B must be accessed to reset the INT output high. If the interrupt enable bit is set to "0", the counter's timeout will have no effect on the INT output.

In mode 5, the variable-duty cycle mode, the INT pin will become active low when the MSB in the counter has decremented to zero.

**Bit 5**—Start/stop control—This bit controls the clock input to the counter and must be set to "1" to enable it. Writing a "0" into this location will halt operation of the counter. Operation will not resume until the bit is set to "1".

**Bit 6**—Holding register control—Since the counter may be decrementing during a read cycle, writing a "1" into this location will hold a stable value in the hold register for

subsequent read operations. Rewriting a "1" into bit 6 will cause an update in the holding register on the next trailing clock edge. If this location contains a "0", the holding register will be updated continuously by the value in the counter.

Bit 7-Jam enable-When this bit is set to "1" during a write to the control register, the 16-bit value in the jam register will be available to the counter; TAO and TBO are reset low and TAO and TBO are set high. On the trailing edge of the first input clock signal with the gate valid this value will be latched in the counter, the counter outputs TAO and TBO will be set high and the TAO and TBO will be reset low. Setting bit 7 to "0" will leave the counter value unaffected. This location should be set to "0" any time a write to the control register must be performed without changing the present counter value. If the value in the jam register has not been changed, writing a "1" into bit 7 of the control register with zeros in bits 0, 1, and 2 (mode select) will reload the counter with the old value and leave the mode unchanged. If the value in the jam register is changed, then the next write to the control register (with bit 7 a "1") must include a valid mode select (i.e., at least 1 of the bits 0, 1, or 2 must be a "1").

In mode 3, the hardware start is enabled by writing a "0" into bit 7. If a "1" is written to bit 7, the timeout will start immediately and mode 3 will resemble mode 1.

### **MODE DESCRIPTIONS**

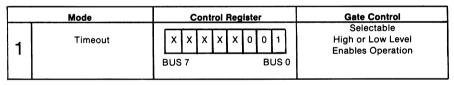

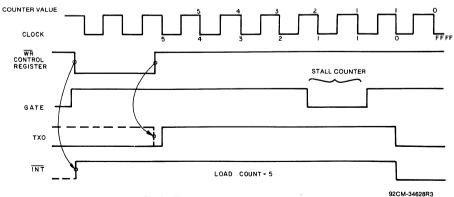

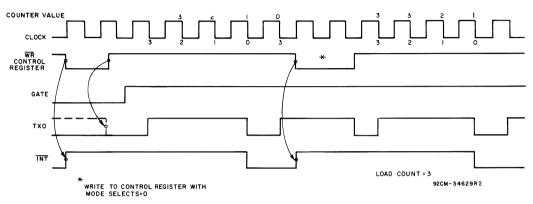

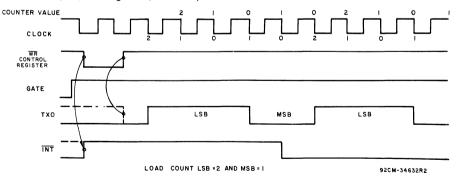

#### Mode 1:

After the count is loaded into the jam register and the control register is written to with the jam-enable bit high on the trailing edge of the first clock after the gate is valid, TXO goes high and TXO goes low. The input clock decrements the counter as long as the gate remains valid. When it reaches zero, TXO goes low and TXO goes high, and if

enabled, the interrupt output is set low. Writing to the counter while it is decrementing has no effect on the counter value unless the control register is subsequently written to with the jam-enable bit high. After timeout the counter remains at FFFF unless reloaded.

Fig. 2 - Timeout (mode 1) timing waveforms.

|   | Mode           | Control F        | Register         | Gate Control                                         |

|---|----------------|------------------|------------------|------------------------------------------------------|

| 2 | Timeout Strobe | X X X X<br>BUS 7 | X 0 1 0<br>BUS 0 | Selectable<br>High or Low Level<br>Enables Operation |

#### Mode 2:

Operation of this mode is the same as mode 1, except the outputs will change for one clock period only and then

return to the condition of TXO high and  $\overline{TXO}$  low, and the counter is reloaded.

Fig. 3 - Timeout strobe (mode 2) timing waveforms.

#### Mode 3:

After the jam register is loaded with the required value, the gate edge will initiate this mode. TXO will be set high, and TXO will be set low. The clock will decrement the counter. When zero is reached, TXO will go low and TXO will be high, and the interrupt output will be set low. The counter is

retriggerable: While the counter is decrementing, a gate edge or write to the control register with the jam-enable bit high, will load the counter with the jam register value and restart the one-shot operation.

Fig. 4 - Gate controlled one-shot (mode 3) timing waveforms.

### Mode 4:

A repetitive clock-wide output pulse will be output, with the time between pulses equal to the counter's value, (trailing edge to leading edge). This model is software started with a write to the control register if the gate level is valid. If the counter is written to while decrementing, the new value will not affect the counter's operation until the present timeout has concluded, unless the control register is written to with the jam-enable bit high. If the gate input (TAG or TBG) is used to start this mode. The first cycle following the gate going true is indeterminate.

|   | Mode                |    | Control Register |   |   |   |   |        |           | Gate Control                                         |

|---|---------------------|----|------------------|---|---|---|---|--------|-----------|------------------------------------------------------|

| 5 | Variable Duty Cycle | ļĽ | ( )<br>IS 7      | × | x | × | 1 | 0<br>В | 1<br>US 0 | Selectable<br>High or Low Level<br>Enables Operation |

#### Mode 5:

After the mode is initiated, the outputs will remain at one level until the clock decrements the least significant byte of the counter to N+1. The outputs will then change level and the counter decrements the most significant byte to N+1. The process will then repeat, resulting in a repetitive output

with a duty cycle directly controlled by the value in the counter. The output period will be equal to LSB+MSB+2.

The interrupt output will become active after the MSB is loaded into the counter and decrements to zero.

Fig. 6 - Variable-duty cycle (mode 5) timing waveforms.

#### Note:

In order to avoid unwanted starts when selecting mode 3 or 4, the gate signal must be set to the opposite level that will be programmed.

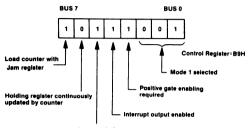

#### **Setting the Control Register**

The following will illustrate a counter write and subsequent reads that places stable, accurate values on the data bus from the counter-timer.

The counter is addressed and the required values are loaded with a write operation. The control register is addressed next and loaded with B9H.

Counter start

The counter will now decrement with each input clock pulse while the gate is valid. Assuming the counter has not decremented to zero and its value is to be read without affecting the counter's operation, a write to the control register is performed. 78H is loaded into the control register.

The counter is addressed and read operations are performed.

#### Function Pin Definition

**DB7-DB0**—8-bit bidirectional bus used to transfer binary information between the microprocessor and the dual counter-timer.

VDD, VSS-Power and ground for device.

A0, A1, and A2-Addresses used to select counters or registers.

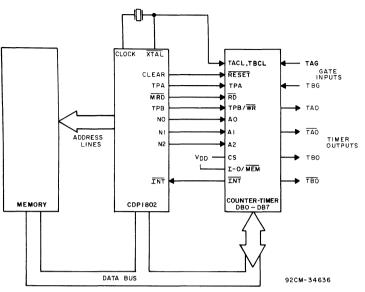

**TPB/WR, RD**—Directional signals that determine whether data will be placed on the bus from a counter or the interrupt status register (RD active) (memory mapped), or data on the bus will be placed into a counter or control register (TPB/WR active). The following connections are required between the microprocessor and the countertimer in the CDP1800-series input/output mapping mode.

| Microprocessor | Counter-Timer |

|----------------|---------------|

| MRD            | RD            |

| ТРВ            | TPB/WR        |

| TPA            | ТРА           |

| N Lines        | Address Lines |

|                |               |

and I-O/MEM to VDD.

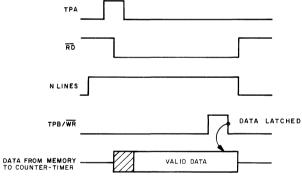

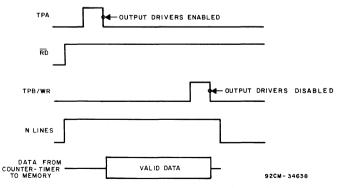

During an output instruction, data from the memory is strobed into the counter-timer during TPB when  $\overline{RD}$  is active, and latched on TPB's trailing edge. Data is read from the counter-timer when  $\overline{RD}$  is not active between the trailing edges of TPA and TPB. (See Figs. 10, 11, and 12.)

TACL, TBCL-Clocks used to decrement the counter.

TAG, TBG-Gate inputs used to control counter.

TAO, TAO-Complemented outputs of Timer A.

TBO, TBO—Complemented outputs of Timer B.

**INT**—Common interrupt output. Active when counter decrements to zero.

**RESET**—Active <u>low</u> signal that resets counter outputs (TAO, TBO low, TAO, TBO high). The interrupt output is set high and the status register is cleared.

I-O/MEM — Tied high in CDP1800-series input/output mode, otherwise tied low.

$\label{eq:transformation} \begin{array}{l} \textbf{TPA} - \text{Tied to TPA of the CDP1800-series microprocessors.} \\ \text{During memory mapping, it is used to latch the high order address bit for the chip select. In the CDP1800 input/output mode, it is used to gate the N lines. When the counter-timer is used with other microprocessors, or when the high order address of the CDP1800-series microprocessors is externally latched, it is connected to V_DD. \end{array}$

CS-An active high signal that enables the device.

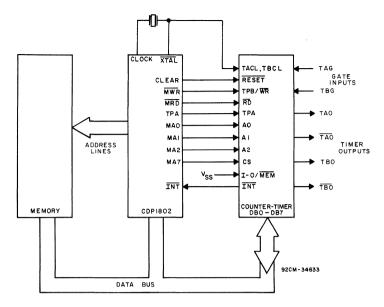

Fig. 7 - Typical CDP1802 memory-mapped system.

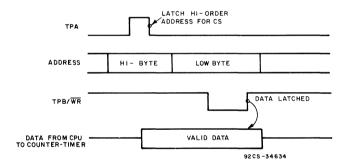

Fig. 8 - CDP1800-series memory-mapping write cycle timing waveforms.

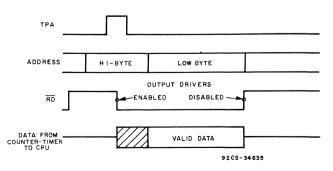

Fig. 9 - CDP1800-series memory-mapping read cycle timing waveforms.

Fig 10 - Typical CDP1802 input/output-mapped system.

92CM-34637

Fig. 11 - CDP1800-series input/output-mapping timing waveforms with output instruction.

Fig. 12 - CDP1800-series input/output-mapping timing waveforms with input instruction.

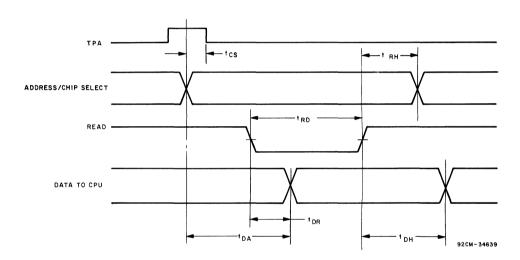

DYNAMIC ELECTRICAL CHARACTERISTICS at TA=-40 to +85° C, VDD=5 V  $\pm$  5%,

Input tr,tf=10 ns; CL=50 pF and 1 TTL Load

| CUADAOTEDIOTIO                 | CHARACTERISTIC  |       |      |       | 1111170 |

|--------------------------------|-----------------|-------|------|-------|---------|

| CHARACTERISTIC                 | Min.†           | Typ.• | Max. | UNITS |         |

| Read Cycle Times (see Fig. 13) |                 |       |      |       |         |

| Data Access from Address       | t DA            | _     | 350  | —     |         |

| Read Pulse Width               | tRD             | 400   | —    | —     |         |

| Data Access from Read          | <sup>t</sup> DR | _     | 250  | _     |         |

| Address Hold after Read        | tRH             | 0     | _    | _     | ns      |

| Output Hold after Read         | <sup>t</sup> DH | 50    | _    |       |         |

| Chip Select Setup to TPA       | tCS             | 50    | -    | _     |         |

<sup>†</sup>Time required by a limit device to allow for the indicated function.

•Typical values are for  $T_A$ =25° C and nominal  $V_{DD}$ .

Fig. 13 - Read cycle timing waveforms.

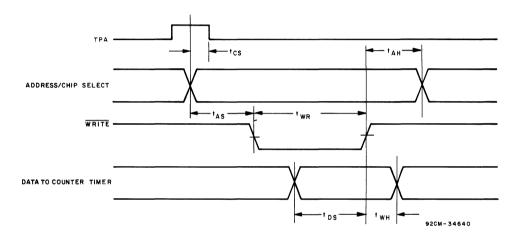

### DYNAMIC ELECTRICAL CHARACTERISTICS at TA=-40 to +85° C, VDD=5 V $\pm$ 5%,

Input t<sub>r</sub>,t<sub>f</sub>=10 ns; CL=50 pF and 1 TTL Load

| CHARACTERISTIC                  |       | UNITS |      |       |    |

|---------------------------------|-------|-------|------|-------|----|

|                                 | Min.† | Тур.• | Max. | UNITS |    |

| Write Cycle Times (see Fig. 14) |       |       |      |       |    |

| Address Setup to Write          | tAS   | 150   | _    | _     |    |

| Write Pulse Width               | twR   | 150   |      | _     |    |

| Data Setup to Write             | tDS   | 200   |      | _     |    |

| Address Hold after Write        | tAH   | 50    |      | _     | ns |

| Data Hold after Write           | twн   | 50    | _    | _     |    |

| Chip Select Setup to TPA        | tcs   | 50    | -    | _     |    |

<sup>†</sup>Time required by a limit device to allow for the indicated function.

•Typical values are for TA=25° C and nominal VDD.

Fig. 14 - Write cycle timing waveforms.