### High Efficiency 1MHz, 3A Boost Regulator

# CE8310 Series

#### ■ INTRODUCTION:

The CE8310 is a high efficiency boost switching regulator designed for single cell lithium or two cells alkaline, NiMH, or NiCd battery powered applications. It generates an output voltage of up to 5.5V from an input voltage as low as 1.6V. Ideal for applications where space is limited, it switches at 1MHz, allowing the use of tiny, low cost and low profile external components, minimizes solution footprint. Its internal 3A, 100mΩ NMOS switch provides high efficiency even at heavy load, while the constant frequency, current mode architecture results in low, predictable output noise that is easy to filter. Internal frequency compensation is designed to accommodate ceramic output capacitors, further reducing noise.

#### ■ FEATURES:

- 1MHz Switching Frequency

- Built-in 100mΩ N-CH Power MOSFET Switch

- PWM/PFM Auto Switching Maintains High Efficiency Overall Load Current Range

- Up to 90% Efficiency: Delivers 1A@5V from Single Li Cell

- Wide Input Voltage Range: 1.6V to 6.0V

- Wide Output Voltage Range: 2.8V to 6.0V

- Output Current: 1.2A@V<sub>IN</sub>=3.0V

- 600mV Feedback Voltage

- Low Shutdown Current: 0.1µA(Typ.)

- Over-Current Protection

- Over-Thermal Protection

- Uses Small,Low Profile External Components

- Ceramic Capacitor Compatible

### ■ APPLICATIONS:

- Back-up Battery

- Solar Battery Charger

- Portable Applications Using Single Li+ Cel

- Bus Powered USB Hosts

- USB Hosts Without Native 5-V Supplies

- 3G/4G Wireless Routers

- Networking card powered from PCI or PCI-express slots

- Portable Audio Players

- Personal Medical Products

# ■ ORDER INFORMATION<sup>(1)</sup>

| Operating free air | Quitaut Voltage | Deekage   | Device No.  |

|--------------------|-----------------|-----------|-------------|

| temperature range  | Output Voltage  | Package   | Device No.  |

| -40~+85℃           | Adjustable      | SOT-23-5  | CE8310CM    |

| -40~+85℃           | 5.1V            | SOT-23-5  | CE8310C51M  |

| -40~+85℃           | Adjustable      | SOT-23-6  | CE8310CE    |

| -40~+85℃           | Adjustable      | SOP8-PP   | CE8310CES   |

| -40~+85℃           | Adjustable      | DFN3X3-10 | CE8310CFC10 |

(1) Contact Chipower to check availability of other fixed output voltage versions.

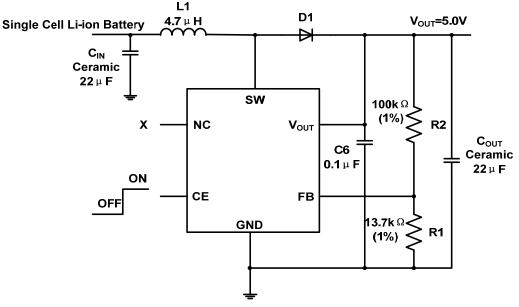

# TYPICAL APPLICATION CIRCUIT

Figure 1 Standard Application Circuit

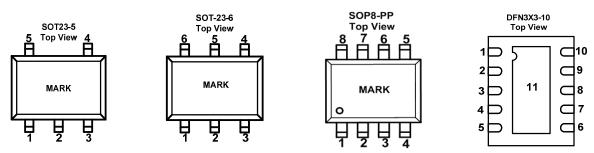

# ■ PIN CONFIGURATION:

SOT-23-5

| P   | PIN              | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|-----|------------------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME             | ITPE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 1   | SW               | I                   | Switch Pin. Connect inductor between SW and IN. A Schottky diode is connected between SW and $V_{OUT}$ . Trace connections made to the inductor and schottky diode should be minimized to reduce power dissipation and increase overall efficiency.<br>Keep these PCB trace lengths as short and wide as possible to reduce EMI and voltage overshoot.                                                                                                                                                                                          |  |  |

| 2   | GND              | Ρ                   | Signal and Power Ground.<br>Connect GND with large copper areas directly to the input and output<br>supply returns and negative terminals of the input and output capacitors<br>This pin should be connected to a continuous PCB ground for high-current<br>power converter as close as to the device by several vias directly under<br>the CE8310CM or CE8310C50M for electrical contact and rated thermal<br>performance. It dissipates the heat from the IC.                                                                                 |  |  |

| 3   | FB/NC            | I                   | Feedback Input / No Connect (for fixed Voltage).Feedback Input to the gm Error Amplifier. Connect resistor divider tap tothis pin.The output voltage can be adjusted from 3.0V to 5.5V by: $V_{OUT} = 0.6V \cdot [1 + (R2/R1)]$ The feedback network, resistors R1 and R2, should be kept close to theFB pin, and away from the inductor, SW, inductor and Schottky diodeswitching node on the PCB layout to minimize copper trace connectionsthat can inject noise into the system.                                                            |  |  |

| 4   | CE               | I                   | <ul> <li>Chip Enable.</li> <li>CE = High: Normal free running operation</li> <li>CE = Low: Shutdown, quiescent current &lt; 1μA.</li> <li>Typically, CE should be connected to IN through a 1M pull-up resistor.</li> </ul>                                                                                                                                                                                                                                                                                                                     |  |  |

| 5   | V <sub>OUT</sub> | I                   | <b>Chip Supply Voltage &amp; Output Voltage Sense Input</b> .<br>The V <sub>OUT</sub> pin should be connected to the negative terminal of the schottky diode and bypassed with a low ESR ceramic bypass capacitor. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the V <sub>OUT</sub> pin, and the CE8310CE GND pin.<br>The minimum recommended bypass capacitance is 100nF ceramic with a X5R or X7R dielectric and the optimum placement is closest to the V <sub>OUT</sub> pin and the GND pin. |  |  |

(1) I = input; O = output; P = power

SOT-23-6

| PIN |                  | TYPE <sup>(1)</sup> | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME             | IYPE."              | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1   | SW               | I                   | <ul> <li>Switch Pin. Connect inductor between SW and IN. A Schottky diode is connected between SW and V<sub>OUT</sub>. Trace connections made to the inductor and schottky diode should be minimized to reduce power dissipation and increase overall efficiency.</li> <li>Keep these PCB trace lengths as short and wide as possible to reduce EMI and voltage overshoot.</li> </ul>                                                                                                                                      |

| 2   | GND              | Ρ                   | Signal and Power Ground.<br>Connect GND with large copper areas directly to the input and output<br>supply returns and negative terminals of the input and output capacitors<br>This pin should be connected to a continuous PCB ground for high-current<br>power converter as close as to the device by several vias directly under<br>the CE8310CE for electrical contact and rated thermal performance. It<br>dissipates the heat from the IC.                                                                          |

| 3   | FB/NC            | I                   | Feedback Input / No Connect (for fixed Voltage).Feedback Input to the gm Error Amplifier. Connect resistor divider tap tothis pin.The output voltage can be adjusted from 3.0V to 5.5V by:V <sub>OUT</sub> =0.6V • [1+(R2/R1)]The feedback network, resistors R1 and R2, should be kept close to theFB pin, and away from the inductor, SW, inductor and Schottky diodeswitching node on the PCB layout to minimize copper trace connectionsthat can inject noise into the system.                                         |

| 4   | CE               | Ι                   | <ul> <li>Chip Enable.</li> <li>CE = High: Normal free running operation</li> <li>CE = Low: Shutdown, quiescent current &lt; 1μA.</li> <li>Typically, CE should be connected to IN through a 1M pull-up resistor.</li> </ul>                                                                                                                                                                                                                                                                                                |

| 5   | V <sub>OUT</sub> | I                   | <b>Chip Supply Voltage &amp; Output Voltage Sense Input</b> .<br>The $V_{OUT}$ pin should be connected to the negative terminal of the schottky diode and bypassed with a low ESR ceramic bypass capacitor. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the $V_{OUT}$ pin, and the CE8310CE GND pin.<br>The minimum recommended bypass capacitance is 100nF ceramic with a X5R or X7R dielectric and the optimum placement is closest to the $V_{OUT}$ pin and the GND pin. |

| 6   | NC               |                     | Not Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

(2) I = input; O = output; P = power

#### SOP8-PP

| PIN              |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |   |                                                                                                    |

|------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|---|----------------------------------------------------------------------------------------------------|

| NAME             | TYPE                                                       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Analog Ground. The analog ground ties to all of the noise sensitive signals. Provide a clean                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |      |   |                                                                                                    |

| AGND             | I                                                          | ground for the analog control circuitry and should not be in the path of large currents.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Return for output voltage set resistor divider.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |   |                                                                                                    |

|                  |                                                            | <b>Feedback Input</b> . Feedback Input to the gm Error Amplifier. Connect resistor divider tap to this pin. The output voltage can be adjusted from 3.0V to 5.5V by: $V_{OUT} = 0.6V \cdot [1 + (R2/R1)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |   |                                                                                                    |

|                  |                                                            | The feedback networks should be connected directly to a dedicated analog ground plane and this ground plane must connect to the AGND pin. If no analog ground plane is available, then the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |      |      |      |   |                                                                                                    |

| FB               | I                                                          | ground connection of the feedback network must tie directly to the AGND pin. Connecting the network to the PGND can inject noise into the system and effect performance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |      |   |                                                                                                    |

|                  |                                                            | The feedback network, resistors R1 and R2, should be kept close to the FB pin, and away from the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |      |      |   |                                                                                                    |

|                  |                                                            | inductor, SW, inductor and Schottky diode switching node on the PCB layout to minimize copper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |   |                                                                                                    |

|                  |                                                            | trace connections that can inject noise into the system.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |      |   |                                                                                                    |

| NC               |                                                            | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |   |                                                                                                    |

| 110              |                                                            | Switch Pin. Connect inductor between SW and IN. A Schottky diode is connected between SW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |      |   |                                                                                                    |

|                  |                                                            | and $V_{OUT}$ . Trace connections made to the inductor and schottky diode is connected between over and $V_{OUT}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |      |      |   |                                                                                                    |

| SW               | I                                                          | reduce power dissipation and increase overall efficiency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Keep these PCB trace lengths as short and wide as possible to reduce EMI and voltage overshoot.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |   |                                                                                                    |

|                  |                                                            | <b>Power Ground</b> . Ground connection for high-current power converter node. High current return for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |      |      |      |   |                                                                                                    |

|                  | _                                                          | the low-side driver and power N-MOSFET. Connect PGND with large copper areas directly to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |      |   |                                                                                                    |

| PGND             | ID P                                                       | input and output supply returns and negative terminals of the input and output capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Only connect to AGND through the Exposed Pad underneath the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Chip Supply Voltage & Output Voltage Sense Input. The VOUT pin should be connected to the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |   |                                                                                                    |

|                  |                                                            | negative terminal of the schottky diode and bypassed with a low ESR ceramic bypass capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |      |      |      |   |                                                                                                    |

| V                |                                                            | Care should be taken to minimize the loop area formed by the bypass capacitor connections, the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |      |      |      |   |                                                                                                    |

| V <sub>OUT</sub> | VOUT                                                       | VOUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | VOUT | VOUT | VOUT | VOUT | I | $V_{\text{OUT}}$ pin, and the CE8310CES ground pins. The minimum recommended bypass capacitance is |

|                  |                                                            | 100nF ceramic with a X5R or X7R dielectric and the optimum placement is closest to the $V_{\text{OUT}}$ pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |   |                                                                                                    |

|                  |                                                            | and the AGND pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |      |      |      |   |                                                                                                    |

| NC               |                                                            | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Chip Enable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |      |   |                                                                                                    |

| CE               | I.                                                         | CE = High: Normal free running operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |      |      |      |   |                                                                                                    |

| 0L               | 1                                                          | CE = Low: Shutdown, quiescent current < 1µA.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Typically, CE should be connected to IN through a 1M pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |      |      |      |   |                                                                                                    |

|                  |                                                            | Exposed Paddle (bottom). Provide a short direct PCB path between exposed pad and negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |      |      |      |   |                                                                                                    |

|                  |                                                            | terminals of the input and output capacitor(s). This pin should be connected to a continuous PCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |      |      |      |   |                                                                                                    |

| EP               | Р                                                          | ground for high-current power converter as close as to the device by several vias directly under the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |      |      |      |   |                                                                                                    |

|                  |                                                            | CE8310CES for electrical contact and rated thermal performance. It dissipates the heat from the IC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |      |      |      |   |                                                                                                    |

|                  | NAME<br>AGND<br>FB<br>NC<br>SW<br>PGND<br>Vout<br>NC<br>CE | NAME       TYPE"         AGND       I         AGND       I         FB       I         NC       I         SW       I         PGND       P         VOUT       I         NC       I         PGND       P         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I         I       I |      |      |      |      |   |                                                                                                    |

(3) I = input; O = output; P = power

V1.4

#### DFN3X3-10

|     |      |                     | DECODIDITION                                                                                                  |

|-----|------|---------------------|---------------------------------------------------------------------------------------------------------------|

| NO. | NAME | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                   |

| 1   | NC   |                     | No Connect.                                                                                                   |

|     |      |                     | Feedback Input.                                                                                               |

|     |      |                     | Feedback Input to the gm Error Amplifier. Connect resistor divider tap to this pin.                           |

|     |      |                     | The output voltage can be adjusted from 3.0V to 5.5V by:                                                      |

| 2   | FB   | Ι                   | V <sub>OUT</sub> =0.6V•[1+(R2/R1)]                                                                            |

|     |      |                     | The feedback network, resistors R1 and R2, should be kept close to the FB pin, and away from                  |

|     |      |                     | the inductor, SW $_{\smallsetminus}$ inductor and Schottky diode switching node on the PCB layout to minimize |

|     |      |                     | copper trace connections that can inject noise into the system.                                               |

| 3   | NC   |                     | No Connect.                                                                                                   |

|     |      |                     | Switch Pin.                                                                                                   |

|     |      |                     | Connect inductor between SW and IN. A Schottky diode is connected between SW and $V_{OUT}$ .                  |

| 4/5 | SW   |                     | Trace connections made to the inductor and schottky diode should be minimized to reduce                       |

| 7/0 | 011  |                     | power dissipation and increase overall efficiency.                                                            |

|     |      |                     | Keep these PCB trace lengths as short and wide as possible to reduce EMI and voltage                          |

|     |      |                     | overshoot.                                                                                                    |

| 6   | NC   |                     | No Connect.                                                                                                   |

|     |      |                     | Chip Supply Voltage & Output Voltage Sense Input.                                                             |

|     |      |                     | The $V_{OUT}$ pin should be connected to the negative terminal of the schottky diode and bypassed             |

| 7   | Vout | 1                   | with a low ESR ceramic bypass capacitor. Care should be taken to minimize the loop area                       |

|     | •001 |                     | formed by the bypass capacitor connections, the $V_{OUT}$ pin, and the CE8310CFC10 ground pin.                |

|     |      |                     | The minimum recommended bypass capacitance is 100nF ceramic with a X5R or X7R                                 |

|     |      |                     | dielectric and the optimum placement is closest to the V <sub>OUT</sub> pin and the GND pin.                  |

| 8   | NC   |                     | No Connect.                                                                                                   |

|     |      |                     | Chip Enable.                                                                                                  |

| 9   | CE   | I.                  | CE = High: Normal free running operation                                                                      |

|     |      | -                   | CE = Low: Shutdown, quiescent current < $1\mu$ A.                                                             |

|     |      |                     | Typically, CE should be connected to IN through a 1M pull-up resistor.                                        |

| 10  | NC   |                     | No Connect.                                                                                                   |

|     |      |                     | Signal and Power Ground.                                                                                      |

|     |      |                     | Connect PGND with large copper areas directly to the input and output supply returns and                      |

| 11  | GND  | Р                   | negative terminals of the input and output capacitors                                                         |

|     |      |                     | This pin should be connected to a continuous PCB ground for high-current power converter as                   |

|     |      |                     | close as to the device by several vias directly under the CE8310CFC10 for electrical contact                  |

|     |      |                     | and rated thermal performance. It dissipates the heat from the IC.                                            |

(1) I = input; O = output; P = power

### ABSOLUTE MAXIMUM RATINGS

#### (Unless otherwise specified, $T_A=25^{\circ}C$ )<sup>(1)</sup>

|                                     |                        | (••                      | i wise specifie | .,    |

|-------------------------------------|------------------------|--------------------------|-----------------|-------|

| PARAMETER                           |                        | SYMBOL                   | RATINGS         | UNITS |

| Output Voltage                      | e range <sup>(2)</sup> | V <sub>OUT</sub>         | -0.3~7          | V     |

| SW Volta                            | ge <sup>(2)</sup>      |                          | -0.3~7          | V     |

| CE, FB Vol                          | tage <sup>(2)</sup>    |                          | -0.3~7          | V     |

| Peak SW Sinl                        | < Current              | I <sub>SWMAX</sub>       | 3               | А     |

|                                     | SOT-23                 |                          | 400             | mW    |

| Power Dissipation <sup>(3)</sup>    | SOP8-PP                | P <sub>D</sub>           | 1200            | mW    |

|                                     | DFN3x3-10              |                          | 2200            | mW    |

| Operating Junction Te               | mperature Range        | Tj                       | -40~150         | °C    |

| Storage Tem                         | perature               | T <sub>stg</sub>         | -40~125         | °C    |

| Lead Temperature(Soldering, 10 sec) |                        | T <sub>solder</sub>      | 260             | °C    |

| ESD rating <sup>(4)</sup>           |                        | Human Body Model - (HBM) | 4000            | V     |

| ESD Talli                           | IQ <sup>®</sup>        | Machine Model- (MM)      | 200             | V     |

(1) Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

(2) All voltages are with respect to network ground terminal.

(3) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) = [ $T_J$ (MAX)- $T_A$ ]/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

(4) ESD testing is performed according to the respective JESD22 JEDEC standard.

The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

#### CAUTION

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. Chipower recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### RECOMMENDED OPERATING CONDITIONS

|                                                                      | MIN | NOM | MAX | UNITS |

|----------------------------------------------------------------------|-----|-----|-----|-------|

| Supply voltage at V <sub>IN</sub>                                    | 1.8 |     | 5.5 | V     |

| Output voltage at V <sub>OUT</sub>                                   | 3.0 |     | 5.5 | V     |

| Operating free air temperature range <sup>(1)</sup> , T <sub>A</sub> | -40 |     | 85  | °C    |

| Operating junction temperature range, T <sub>j</sub>                 | -40 |     | 125 | °C    |

(1) The CE8310 is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

V1.4

#### **ELECTRICAL CHARACTERISTICS**

Typical values are at T<sub>A</sub>=25℃, unless otherwise specified, specifications apply for condition  $V_{IN}=V_{CE}=3.6V, V_{OUT}=5.0V.$

| PARAMETER                                         | SYMBOL               | CONDITIONS                                               | MIN   | TYP <sup>(1)</sup> | MAX             | UNITS |

|---------------------------------------------------|----------------------|----------------------------------------------------------|-------|--------------------|-----------------|-------|

| SUPPLY                                            |                      |                                                          | 1     |                    |                 | I     |

| Operating quiescent current into $V_{\text{OUT}}$ | Ι <sub>Q</sub>       | Measured On V <sub>OUT</sub> ,<br>V <sub>FB</sub> =0.75V |       | 130                | 300             | μA    |

| Shutdown Current into IN                          | I <sub>SHDNVIN</sub> | V <sub>CE</sub> =0V                                      |       | 0.1                | 1               | μA    |

| LOGIC SIGNAL CE                                   |                      |                                                          |       |                    |                 |       |

| CE High-level Voltage                             | V <sub>CEH</sub>     | V <sub>CE</sub> Falling, Device ON                       | 1.5   |                    | V <sub>IN</sub> | V     |

| CE Low-level Voltage                              | V <sub>CEL</sub>     | V <sub>CE</sub> Rising, Device Off                       |       |                    | 0.4             | V     |

| CE Leakage Current                                | I <sub>CE</sub>      | V <sub>CE</sub> =5.0V                                    |       | ±0.1               | ±1              | μA    |

| OSCILLATOR                                        |                      |                                                          |       |                    |                 |       |

| Oscillator Frequency                              | f <sub>osc</sub>     |                                                          |       | 1.0                |                 | MHz   |

| Max Duty Cycle                                    | D <sub>MAX</sub>     | V <sub>FB</sub> =0V                                      | 80    | 87                 |                 | %     |

| POWER SWITCH                                      |                      |                                                          |       |                    |                 |       |

| N-CH MOSFET On Resistance <sup>(2)</sup>          | R <sub>DS(ON)</sub>  |                                                          |       | 100                |                 | mΩ    |

| N-CH MOSFET Switch Leakage                        | I <sub>SWLEAK</sub>  | V <sub>CE</sub> =0V,V <sub>SW</sub> =5.0V                |       | ±0.01              | ±1              | μA    |

| NMOS Cycle by Cycle Current Limit <sup>(3)</sup>  | I <sub>CL</sub>      | V <sub>OUT</sub> =5.0V                                   |       | 3.0                |                 | А     |

| Current Limit Delay to Output <sup>(4)</sup>      |                      |                                                          |       | 40                 |                 | nS    |

| OUTPUT                                            |                      |                                                          |       |                    |                 |       |

| Output Voltage Range <sup>(5)</sup>               | V <sub>OUT</sub>     |                                                          | 3.0   |                    | 5.5             | V     |

| Feedback regulation voltage                       | V <sub>FB</sub>      |                                                          | 0.588 | 0.600              | 0.612           | V     |

| Feedback Input bias Current <sup>(6)</sup>        | I <sub>FB</sub>      | V <sub>FB</sub> =0.75V                                   |       |                    | 0.1             | μA    |

| OVER TEMPERATURE PROTECTION                       |                      | •                                                        |       |                    |                 |       |

| Thermal Shutdown                                  | T <sub>TSD</sub>     |                                                          |       | 140                |                 | °C    |

| Thermal Shutdown Hysteresis                       | T <sub>TSDHYS</sub>  |                                                          |       | 20                 |                 | °C    |

(1) Typical numbers are at 25°C and represent the most likely norm.

(2) Does not include the bond wires. Measured directly at the die.

(3) Duty cycle affects current limit due to ramp generator.

(4) Specification is guaranteed by design and not 100% tested in production.

(5) The fixed voltage version effective output voltage.

(6) Bias current flows into FB pin. Specification is guaranteed by design and not 100% tested in production.

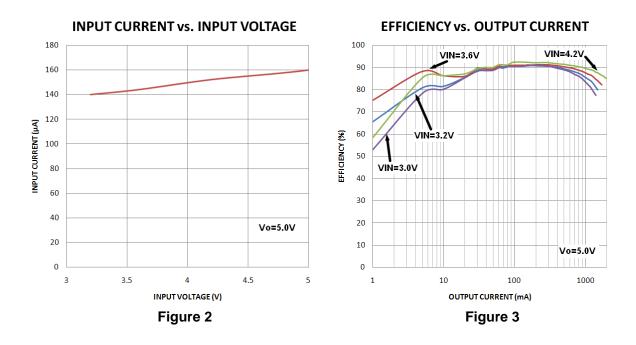

### ■ TYPICAL PERFORMANCE CHARACTERISTICS (T<sub>A</sub>=25<sup>°</sup>C, unless otherwise specified, Test Figure1 above)

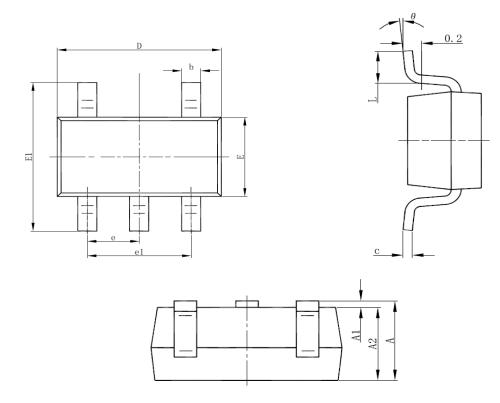

#### PACKAGING INFORMATION

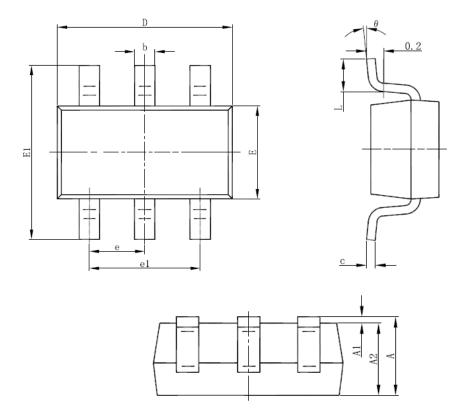

SOT-23-5 Package Outline Dimensions •

| Symbol | Dimensions | In Millimeters | Dimensions | In Inches |

|--------|------------|----------------|------------|-----------|

| Symbol | Min        | Max            | Min        | Max       |

| A      | 1.050      | 1.250          | 0.041      | 0.049     |

| A1     | 0.000      | 0.100          | 0.000      | 0.004     |

| A2     | 1.050      | 1.150          | 0.041      | 0.045     |

| b      | 0.300      | 0.500          | 0.012      | 0.020     |

| С      | 0.100      | 0.200          | 0.004      | 0.008     |

| D      | 2.820      | 3.020          | 0.111      | 0.119     |

| E      | 1.500      | 1.700          | 0.059      | 0.067     |

| E1     | 2.650      | 2.950          | 0.104      | 0.116     |

| е      | 0.950(BSC) |                | 0.037(BSC) |           |

| e1     | 1.800      | 2.000          | 0.071      | 0.079     |

| L      | 0.300      | 0.600          | 0.012      | 0.024     |

| θ      | 0°         | 8°             | 0°         | 8°        |

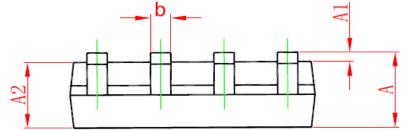

#### SOT-23-6 Package Outline Dimensions •

| Symbol | Dimensions | In Millimeters | Dimensions In Inches |       |  |

|--------|------------|----------------|----------------------|-------|--|

| Symbol | Min        | Max            | Min                  | Max   |  |

| А      | 1.050      | 1.250          | 0.041                | 0.049 |  |

| A1     | 0.000      | 0.100          | 0.000                | 0.004 |  |

| A2     | 1.050      | 1.150          | 0.041                | 0.045 |  |

| b      | 0.300      | 0.500          | 0.012                | 0.020 |  |

| С      | 0.100      | 0.200          | 0.004                | 0.008 |  |

| D      | 2.820      | 3.020          | 0.111                | 0.119 |  |

| E      | 1.500      | 1.700          | 0.059                | 0.067 |  |

| E1     | 2.650      | 2.950          | 0.104                | 0.116 |  |

| е      | 0.950      | 0.950(BSC)     |                      | BSC)  |  |

| e1     | 1.800      | 2.000          | 0.071                | 0.079 |  |

| L      | 0.300      | 0.600          | 0.012                | 0.024 |  |

| θ      | 0°         | 8°             | 0°                   | 8°    |  |

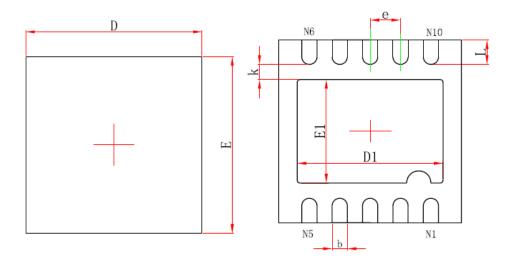

#### SOP8-PP Package Outline Dimensions •

| Symbol | Dimensions | In Millimeters | Dimensions | In Inches |

|--------|------------|----------------|------------|-----------|

| Symbol | Min        | Max            | Min        | Max       |

| А      | 1.350      | 1.750          | 0.053      | 0.069     |

| A1     | 0.100      | 0.250          | 0.004      | 0.010     |

| A2     | 1.350      | 1.550          | 0.053      | 0.061     |

| b      | 0.330      | 0.510          | 0.013      | 0.020     |

| С      | 0.170      | 0. 250         | 0.006      | 0.010     |

| D      | 4.700      | 5.100          | 0.185      | 0.200     |

| D1     | 3.100      | 3.500          | 0.122      | 0.137     |

| E      | 3.800      | 4.000          | 0.150      | 0.157     |

| E1     | 5.800      | 6.200          | 0.228      | 0.244     |

| E2     | 2.200      | 2.600          | 0.086      | 0.102     |

| е      | 1.270(BSC) |                | 0.050(     | BSC)      |

| L      | 0.400      | 1.270          | 0.016      | 0.050     |

| θ      | 0°         | 8°             | 0°         | 8°        |

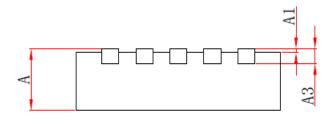

# • DFN3x3-10 Package Outline Dimensions

Top View

**Bottom View**

Side View

| Symbol | Dimensions In Millimeters |             | Dimensions In Inches |             |  |

|--------|---------------------------|-------------|----------------------|-------------|--|

| Symbol | Min                       | Max         | Min                  | Max         |  |

| A      | 0.700/0.800               | 0.800/0.900 | 0.028/0.031          | 0.031/0.035 |  |

| A1     | 0.000                     | 0.050       | 0.000                | 0.002       |  |

| A3     | 0.203                     | 3REF        | 0.008                | REF         |  |

| D      | 2.900                     | 3.100       | 0.114                | 0.122       |  |

| E      | 2.900                     | 3.100       | 0.114                | 0.122       |  |

| D1     | 2.300                     | 2.500       | 0.091                | 0.098       |  |

| E1     | 1.600                     | 1.800       | 0.063                | 0.071       |  |

| k      | 0.20                      | OMIN        | 0.008MIN             |             |  |

| b      | 0.180                     | 0.300       | 0.007                | 0.012       |  |

| е      | 0.500TYP                  |             | 0.020                | ТҮР         |  |

| L      | 0.300                     | 0.500       | 0.012                | 0.020       |  |

© Nanjing Chipower Electronics Inc.

V1.4

Chipower cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Chipower product. No circuit patent license, copyrights or other intellectual property rights are implied. Chipower reserves the right to make changes to their products or specifications without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.