# CE8323 Series

#### **■** INTRODUCTION:

The CE8323 is a high efficiency boost switching regulator especially designed for single cell lithium battery powered applications. It generates an output voltage of up to 5.5V from an input voltage as low as 2.7V. Ideal for applications where space is limited, it switches at 1MHz, allowing the use of tiny, low cost and low profile external components, minimizes solution footprint. Its internal 4.5A,  $60m\Omega$  NMOS switch provides high efficiency even at heavy load, while the constant frequency, current mode architecture results in low, predictable output noise that is easy to filter. Internal frequency compensation is designed to accommodate ceramic output capacitors, further reducing noise.

## **■ FEATURES:**

- 1MHz Switching Frequency

- Built-in 60mΩ N-CH Power MOSFET Switch

- PWM/PFM Auto Switching Maintains High Efficiency Overall Load Current Range

- Up to 90% Efficiency:

Delivers 2.1A@5V from Single Li Cell

- Wide Input Voltage Range: 2.7V to 6.0V

- Wide Output Voltage Range: 3.0V to 5.5V

- Output Current: 2.1A@V<sub>IN</sub>=3.0V

- 0.6V (±2%) Feedback Reference Voltage

- Low Shutdown Current: 0.1μA(Typ.)

- Adjustable Over Current Protection:

0.5A~4.5A

- Over Temperature Protection

- Uses Small, Low Profile External Components

- Ceramic Capacitor Compatible

### ■ APPLICATIONS:

- Back-up Battery

- Solar Battery Charger

- Portable Applications Using Single Li+ Cell

- Bus Powered USB Hosts

- USB Hosts Without Native 5-V Supplies

- 3G/4G Wireless Routers

- Networking card powered from PCI or PCI-express slots

- Portable Audio Players

- Personal Medical Products

### ORDER INFORMATION

| Operating free air temperature range | Output Voltage | Package | Device No. |

|--------------------------------------|----------------|---------|------------|

| -40~+85°C                            | Adjustable     | SOP8-PP | CE8323CES  |

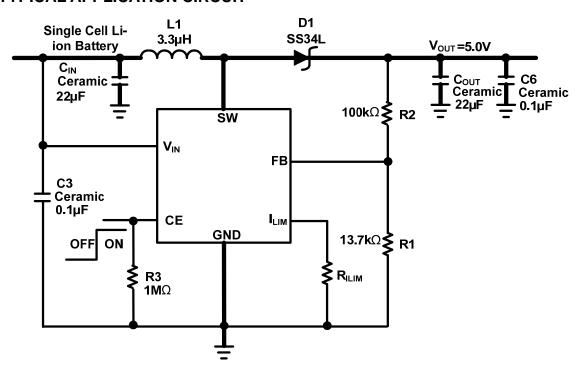

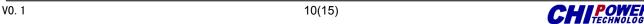

# **■ TYPICAL APPLICATION CIRCUIT**

**Figure 1 Standard Application Circuit**

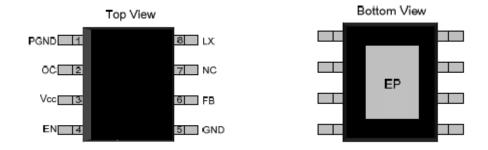

# **■ PIN CONFIGURATION:**

# SOP8-PP

| I   | PIN              | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                 |  |                                                                                             |  |

|-----|------------------|---------------------|---------------------------------------------------------------------------------------------|--|---------------------------------------------------------------------------------------------|--|

| NO. | NAME             | ITPE                | DESCRIPTION                                                                                 |  |                                                                                             |  |

|     |                  |                     | Power Ground. Ground connection for high-current power converter node. High                 |  |                                                                                             |  |

|     |                  |                     | current return for the low-side driver and power N-MOSFET. Connect PGND with                |  |                                                                                             |  |

| 1   | PGND             | Р                   | large copper areas directly to the input and output supply returns and negative             |  |                                                                                             |  |

|     |                  |                     | terminals of the input and output capacitors.                                               |  |                                                                                             |  |

|     |                  |                     | Only connect to AGND through the Exposed Pad underneath the IC.                             |  |                                                                                             |  |

| 2   | I <sub>LIM</sub> | I                   | Adjustable Input Valley Current Limit. Can be floated for maximum current.                  |  |                                                                                             |  |

|     |                  |                     | Chip Supply Voltage & input Voltage Sense Input.                                            |  |                                                                                             |  |

|     |                  |                     | The $V_{\text{IN}}$ pin should be connected to the positive terminal of the battery and     |  |                                                                                             |  |

|     |                  |                     | bypassed with a low ESR ceramic bypass capacitor. Care should be taken to                   |  |                                                                                             |  |

| 3   | V <sub>IN</sub>  | 1                   | minimize the loop area formed by the bypass capacitor connections, the $V_{\text{IN}}$ pin, |  |                                                                                             |  |

|     | VIN              | '                   | and the CE8323CES AGND pin.                                                                 |  |                                                                                             |  |

|     |                  |                     | The minimum recommended bypass capacitance is 100nF ceramic with a X5R or                   |  |                                                                                             |  |

|     |                  |                     | X7R dielectric and the optimum placement is closest to the V <sub>IN</sub> pin and the AGND |  |                                                                                             |  |

|     |                  |                     | pin.                                                                                        |  |                                                                                             |  |

|     |                  |                     | Chip Enable.                                                                                |  |                                                                                             |  |

| 4   | CE               | I                   | CE = High: Normal free running operation                                                    |  |                                                                                             |  |

|     |                  |                     | CE = Low: Shutdown, quiescent current < 1µA.                                                |  |                                                                                             |  |

|     | AGND             |                     | Analog Ground. The analog ground ties to all of the noise sensitive signals.                |  |                                                                                             |  |

| 5   |                  | 1                   | Provide a clean ground for the analog control circuitry and should not be in the path       |  |                                                                                             |  |

|     | 7.011            | •                   | of large currents.                                                                          |  |                                                                                             |  |

|     |                  |                     | Return for output voltage set resistor divider.                                             |  |                                                                                             |  |

|     |                  |                     | Feedback Input                                                                              |  |                                                                                             |  |

|     |                  |                     |                                                                                             |  | Feedback Input to the gm Error Amplifier. Connect resistor divider tap to this pin.         |  |

|     |                  |                     |                                                                                             |  | The output voltage can be adjusted from 3.0V to 5.5V by: V <sub>OUT</sub> =0.6V•[1+(R2/R1)] |  |

| 6   | FB               | 1                   | The feedback network, resistors R1 and R2, should be kept close to the FB pin, and          |  |                                                                                             |  |

|     |                  |                     | away from the inductor, SW、inductor and Schottky diode switching node on the                |  |                                                                                             |  |

|     |                  |                     | PCB layout to minimize copper trace connections that can inject noise into the              |  |                                                                                             |  |

|     |                  |                     | system.                                                                                     |  |                                                                                             |  |

| 7   | NC               | -                   | Connected to AGND or Floating, cannot be connected to other node.                           |  |                                                                                             |  |

|     |                  |                     | Switch Pin. Connect inductor between SW and IN. A Schottky diode is connected               |  |                                                                                             |  |

|     |                  |                     | between SW and OUT. Trace connections made to the inductor and schottky diode               |  |                                                                                             |  |

| 8   | SW               | - 1                 | should be minimized to reduce power dissipation and increase overall efficiency.            |  |                                                                                             |  |

|     |                  |                     | Keep these PCB trace lengths as short and wide as possible to reduce EMI and                |  |                                                                                             |  |

|     |                  |                     | voltage overshoot.                                                                          |  |                                                                                             |  |

| L   | l                |                     | I.                                                                                          |  |                                                                                             |  |

V0. 1 3(15)

|   |    |   | Exposed Paddle (bottom). This pin should be connected to a continuous ground          |

|---|----|---|---------------------------------------------------------------------------------------|

|   | EP | P | plane as close as to the device by several vias directly under the CE8323 for         |

| 9 |    | Р | electrical contact and rated thermal performance. It dissipates the heat from the IC. |

|   |    |   | EP must be connected to AGND at a single point with a star ground connection.         |

(1) I = input; O = output; P = power

## ■ ABSOLUTE MAXIMUM RATINGS

(Unless otherwise specified, T<sub>A</sub>=25°C)<sup>(1)</sup>

| PARAMETER                                                      |                       | SYMBOL                   | RATINGS            | UNITS |

|----------------------------------------------------------------|-----------------------|--------------------------|--------------------|-------|

| Supply Voltage                                                 | range (2)             | V <sub>IN</sub>          | -0.3~7             | V     |

| SW Voltag                                                      | le <sup>(2)</sup>     |                          | -0.3~7             | V     |

| CE, FB, I <sub>LIM</sub> Vo                                    | oltage <sup>(2)</sup> |                          | -0.3~7             | V     |

| Peak SW Sink                                                   | Current               | I <sub>SWMAX</sub>       | 4.5                | Α     |

| Power Dissipation                                              | SOP8-PP               | P <sub>d</sub>           | 1.5 <sup>(3)</sup> | mW    |

| Thermal Resistance                                             | SOP8-PP               | $\theta_{JA}$            | 80 <sup>(4)</sup>  | °C/W  |

| Operating Junction                                             | Temperature           | T <sub>j</sub>           | -40~150            | °C    |

| Range                                                          |                       | ' ' '                    | 40 100             |       |

| Storage Temp                                                   | erature               | T <sub>stg</sub>         | -40~125            | °C    |

| Lead Temperature(Soldering, 10 sec)  ESD rating <sup>(5)</sup> |                       | T <sub>solder</sub>      | 260                | °C    |

|                                                                |                       | Human Body Model - (HBM) | 4000               | V     |

| LOD Idini                                                      | ษ                     | Machine Model- (MM)      | 200                | V     |

<sup>(1)</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

- (2) All voltages are with respect to network ground terminal.

- (3) Surface mounted on FR-4 Board using 1 square inch pad size, dual side, 1oz copper

- (4)  $\theta_{JA}$  is measured in the natural convection at  $T_A$ =25°C on a low effective thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

- (5) ESD testing is performed according to the respective JESD22 JEDEC standard.

The human body model is a 100 pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. The machine model is a 200pF capacitor discharged directly into each pin.

#### **CAUTION**

This integrated circuit can be damaged by ESD if you don't pay attention to ESD protection. Chipower recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

## ■ RECOMMENDED OPERATING CONDITIONS

|                                                                      | MIN | NOM | MAX | UNITS |

|----------------------------------------------------------------------|-----|-----|-----|-------|

| Supply voltage at V <sub>IN</sub>                                    | 2.7 |     | 5.5 | V     |

| Output voltage at V <sub>OUT</sub>                                   | 3.0 |     | 5.5 | V     |

| Operating free air temperature range <sup>(1)</sup> , T <sub>A</sub> | -40 |     | 85  | °C    |

| Operating junction temperature range, T <sub>j</sub>                 | -40 |     | 125 | °C    |

<sup>(1)</sup> The CE8323 is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the –40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

# **■ ELECTRICAL CHARACTERISTICS**

Typical values are at  $T_A=25$ °C, unless otherwise specified, specifications apply for condition  $V_{IN}=V_{CE}=3.3V,\ V_{OUT}=5.0V.$

| PARAMETER                                        | SYMBOL                         | CONDITIONS                                | MIN | TYP <sup>(1)</sup> | MAX      | UNITS |  |  |

|--------------------------------------------------|--------------------------------|-------------------------------------------|-----|--------------------|----------|-------|--|--|

| SUPPLY                                           |                                |                                           |     |                    |          |       |  |  |

| Input Supply Range                               | V <sub>IN</sub>                |                                           | 2.7 |                    | 5.5      | V     |  |  |

| Under Voltage Lockout                            | $V_{UVL}$                      | V <sub>IN</sub> Rising                    |     | 2.2                | 2.7      | V     |  |  |

| UVLO Hysteresis                                  | $\Delta V_{UVL}$               |                                           |     | 0.2                |          | V     |  |  |

|                                                  |                                | V <sub>FB</sub> =0.65V, device is         |     |                    |          |       |  |  |

| Operating quiescent current into $V_{\text{IN}}$ | $I_Q$                          | not switching,                            |     | 190                |          | μA    |  |  |

|                                                  |                                | Measured On V <sub>IN</sub> ,             |     |                    |          |       |  |  |

|                                                  |                                | V <sub>FB</sub> =0.55V, device is         |     |                    |          |       |  |  |

| Average Supply Current                           | $I_{AVG}$                      | switching, Measured                       |     | 1.2                |          | mA    |  |  |

|                                                  |                                | On V <sub>IN</sub> ,                      |     |                    |          |       |  |  |

| Shutdown Current into V <sub>IN</sub>            | I <sub>SHDNVIN</sub>           | V <sub>CE</sub> =0V                       |     | 0.1                | 1        | μA    |  |  |

| LOGIC SIGNAL CE                                  |                                | 1                                         |     | -1                 |          |       |  |  |

| CE High-level Voltage                            | V <sub>CEH</sub>               | V <sub>CE</sub> Falling, Device ON        | 1.5 |                    | $V_{IN}$ | V     |  |  |

| CE Low-level Voltage                             | V <sub>CEL</sub>               | V <sub>CE</sub> Rising, Device Off        |     |                    | 0.4      | V     |  |  |

| CE Leakage Current                               | I <sub>CE</sub>                | V <sub>CE</sub> =5.0V                     |     | ±0.1               | ±1       | μA    |  |  |

| OSCILLATOR                                       |                                | 1                                         |     |                    |          |       |  |  |

| Oscillator Frequency                             | f <sub>osc</sub>               |                                           | 8.0 | 1                  | 1.2      | MHz   |  |  |

| Frequency Change with Input Voltage              | $\Delta f_{osc}/\Delta V_{IN}$ | V <sub>IN</sub> =2.7V to 5.5V             |     | 2.5                |          | %/V   |  |  |

| Max Duty Cycle                                   | D <sub>MAX</sub>               | V <sub>FB</sub> =0.55V                    | 85  | 90                 |          | %     |  |  |

| POWER SWITCH                                     |                                |                                           |     |                    |          | 1     |  |  |

| N-CH MOSFET On Resistance <sup>(2)</sup>         | R <sub>DS(ON)</sub>            |                                           |     | 60                 |          | mΩ    |  |  |

| N-CH MOSFET Switch Leakage                       | I <sub>SWLEAK</sub>            | V <sub>CE</sub> =0V,V <sub>SW</sub> =5.0V |     | ±0.01              | ±1       | μA    |  |  |

| NMOS Programmable Valley Cycle                   | I <sub>V(CL)</sub>             | I <sub>LIM</sub> pin Floating             |     | 4.5                |          | Α     |  |  |

|                                                  |                                | I                                         | l   | l .                |          | l     |  |  |

| by Cycle Switch Current Limit <sup>(3)</sup> |                     | With External Resistor:       | 0.5   |       | 4.5   |     |

|----------------------------------------------|---------------------|-------------------------------|-------|-------|-------|-----|

|                                              |                     | 10.7kΩ~96kΩ                   | 0.5   |       | 4.5   | Α   |

| Current Limit Delay to Output <sup>(4)</sup> |                     |                               |       | 40    |       | nS  |

| ОИТРИТ                                       |                     |                               |       | I     |       |     |

| Output Voltage Range                         | $V_{OUT}$           |                               | 3.0   |       | 5.5   | V   |

| Feedback regulation voltage                  | $V_{FB}$            |                               | 0.588 | 0.600 | 0.612 | V   |

| Line Regulation                              |                     | V <sub>IN</sub> =2.7V to 5.5V |       | 0.2   |       | %/V |

| Load Regulation                              |                     | I <sub>LOAD</sub> =0A to 1A   |       | 0.5   |       | %/A |

| Feedback Input bias Current <sup>(5)</sup>   | I <sub>FB</sub>     | V <sub>FB</sub> =0.65V        |       |       | 0.1   | μA  |

| OVER TEMPERATURE PROTECTION                  |                     |                               |       |       |       |     |

| Thermal Shutdown                             | $T_{TSD}$           |                               |       | 150   |       | °C  |

| Thermal Shutdown Hysteresis                  | T <sub>TSDHYS</sub> |                               |       | 30    |       | °C  |

- (1) Typical numbers are at 25°C and represent the most likely norm.

- (2) Does not include the bond wires. Measured directly at the die.

- (3) Duty cycle affects current limit due to ramp generator

- (4) Specification is guaranteed by design and not 100% tested in production.

- (5) Bias current flows into FB pin. Specification is guaranteed by design and not 100% tested in production.

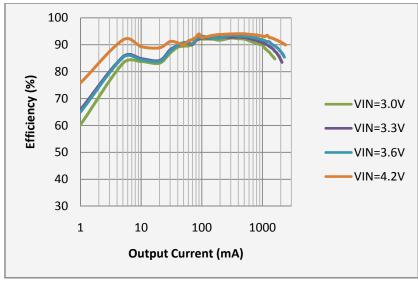

## ■ TYPICAL PERFORMANCE CHARACTERISTICS

(T<sub>A</sub>=25℃, unless otherwise specified, Test Figure1 above)

### **Efficiency VS Output Current**

Figure 2

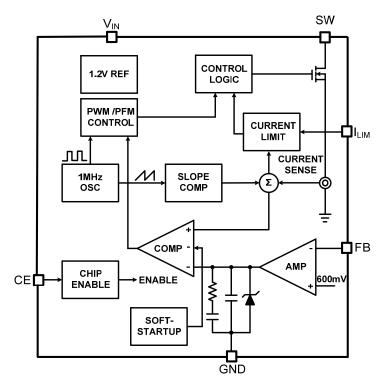

#### **■ BLOCK DIAGRAM**

Figure 3

#### DETAILED DESCRIPTION

The CE8323 is a monolithic 1MHz boost converter housed in a 8-lead thermal enhanced package. The device features current mode PWM control for excellent line and load regulation. The low R<sub>DS(ON)</sub> NMOS switch enables the device to maintain high efficiency over a wide range of load current. The control loop architecture is peak current mode control. This means that switch duty cycle is directly controlled by the peak switch current rather than only by output voltage.

The CE8323 regulates the output voltage using a combined pulse-width (PWM) and pulse-frequency (PFM) modulation topology. In PWM mode, the device runs at a 1MHz fixed frequency. Operation of the feedback loop which sets the peak inductor current to keep the output in regulation can be best understood by referring to the Block Diagram in Figure 3. At the start of each clock cycle a latch in the PWM logic is set and the NMOS switch is turned on. The sum of a voltage proportional to the switch current and a slope compensating voltage ramp is fed to the positive input to the PWM comparator. When this voltage exceeds either a voltage proportional to the 4A current limit or the PWM control voltage, the latch in the PWM logic is reset and NMOS switch is turned off. Slope compensation is necessary to prevent sub-harmonic oscillations that may occur in peak current mode architectures when exceeding 50% duty cycle. The PWM control voltage at the output of the error amplifier is the amplified and compensated difference between the feedback voltage on the FB pin and the internal reference voltage of 0.6V. If the control voltage increases, more current is delivered to the output. When the control voltage exceeds the I<sub>LIM</sub> reference voltage, the peak current is limited to a minimum of 4A. The current limit helps protect the

CE8323 internal switch and external components connected to it. If the control voltage decreases, less current is delivered to the output. During load transients control voltage may decrease to the point where no switching occurs until the feedback voltage drops below the reference. At very light loads, the CE8323 will automatically enter pulse frequency mode (PFM). When the converter output voltage is slightly higher than the preset voltage, the device will stop switching and skip some periods to maintain output regulation.

The CE8323 has an integrated soft-start feature which slowly ramps up the feedback control node from 0V. The soft-start is initiated when CE is pulled high. Additional features include Cycle-By-Cycle Current Limit Protection, Under Voltage Protection and Over Temperature Protection.

#### **PWM/PFM Auto Switching**

The CE8323 offers PWM/PFM automatic switching operation. The PWM operation is shifted to the PFM operation automatically at light load to improve efficiency at light load. So it maintains high efficiency over a wide range of load currents.

#### **Soft Start-Up**

Soft start circuitry is integrated into CE8323 to avoid inrush current during power on. After the IC is enabled, the output of error amplifier is clamped by the internal soft-start function, which causes PWM pulse width increasing slowly and thus reducing input surge current.

#### **Cycle by Cycle Current Limit**

The CE8323 uses a cycle-by-cycle current limit circuitry to limit the inductor peak current in the event of an overload condition. The current flow through inductor in charging phase is detected by a current sensing circuit. As the value comes across the current limiting threshold the NMOS turns off, so that the inductor will be forced to leave charging stage and enter discharging stage. Therefore, the inductor current will not increase over the current limiting threshold.

#### **Current Limit Program**

A resistor between I<sub>LIM</sub> and GND pin programs peak switch current. The resistor value should be between 10.7k and 96k. The current limit will be set from 4.5A to 0.5A. Keep traces at this pin as short as possible. Do not put capacitance at this pin.

$$I_{LIM} = \frac{48000}{R_{ILIM}}$$

#### **UVLO Protection**

To avoid malfunction of the CE8323 at low input voltages, an under voltage lockout is included that disables the device, until the input voltage exceeds 2.2V (Typ.).

### **Over Temperature Protection (OTP)**

The CE8323 features integrated thermal overload protection. A thermal shutdown is implemented to prevent damages due to excessive heat and power dissipation. Typically the thermal shutdown happens at a internal junction temperature of 150°C. When the thermal shutdown is triggered, the device automatically turns off the power NMOS and disables the controller, until the internal junction temperature decreases to typically 30°C below the thermal shutdown trip point. Then the device is released from shutdown automatically and starts switching again.

Thermal shutdown provides protection when an overload condition is sustained for several milliseconds. With a persistent fault condition, the device cycles continuously; heating up due to the fault, and then shutting down upon reaching the thermal shutdown point.

#### **Shutdown Mode Operation**

Pulling the CE pin low (<0.4V) forces the device in shutdown mode. In shutdown mode, the reference, control circuit, and the main NMOS switch are turned off, drawing <1µA supply current. As with all non-synchronous boost DC/DC converters, the external Schottky diode provides a DC path from the input to the output in shutdown mode. As a result, the output drops to one diode voltage drop below the input in shutdown.

Setting the CE pin high (>1.5V) will turn on the IC again.

For proper operation, the CE pin must be terminated and must not be left floating

#### APPLICATION INFORMATION

Because of the high integration in the CE8323 IC, the application circuit based on this boost converter IC is rather simple. Only input capacitor  $C_{\text{IN}}$ , output capacitor  $C_{\text{OUT}}$ , inductor L, feedback resistors (R1 and R2) and output rectify diode need to be selected for the targeted application specifications. External component selection for the application circuit depends on the load current requirements. Certain tradeoffs between different performance parameters can also be made. The following sections describe selection of components for a boost converter.

#### **Power Inductor Selection**

A 3.3uH inductor is recommended to connect from IN to SW. The minimum and maximum inductor values are constrained by many considerations. The minimum inductance is limited by the peak inductor-current value. The ripple current in the inductor is inversely proportional to the inductance value, so the output voltage may fall out of regulation if the peak inductor current exceeds the current-limit value (2A minimum). Using a nominal 3.3µH inductor allows full recommended current operation even if the inductance is 20% low (2.64µH) due to component variation.

A maximum 4.7uH (typical) inductor value is recommended to maintain adequate phase margin over the full range of recommended operating conditions.

The saturation current of inductor should be higher enough than the peak switch current. And the inductor should have low core losses at 1MHz and low DCR (copper wire resistance).

#### **Output Capacitor Selection**

Connect the boost-converter output capacitance from Output to the reference ground plane. The Output capacitance controls the ripple voltage on the Output rail and provides a low-impedance path for the switching and transient-load currents of the boost converter. It also sets the location of the output pole in the control loop of the boost converter. There are limitations to the minimum and maximum capacitance on Output. The recommended minimum capacitors on Output are two 22uF/16V, X5R or X7R ceramic capacitor. The low ESR of the ceramic capacitor minimizes ripple voltage and power dissipation from the

large, pulsating currents of the boost converter and provides adequate phase margin across all recommended operating conditions.

#### **Input Capacitor Selection**

Connect the input capacitance from  $V_{\text{IN}}$  to the reference ground plane. Input capacitance reduces the ac voltage ripple on the input rail by providing a low-impedance path for the switching current of the boost converter. A 22uF/16V, X7R or X5R ceramic capacitor is recommended for most applications for reasonable input-voltage ripple performance. There are several scenarios where it is recommended to use additional input capacitance.

## **Output Diode Selection**

The output rectifier diode supplies current path to the inductor when the internal NMOS is Turned off. Use a schottky diode with low forward voltage to reduce losses. The diode should be rated for a reverse blocking voltage greater than the output voltage used. The average current rating must be greater than the maximum load current expected, and the peak current rating must be greater than the peak inductor current. The output rectify diode select requirements are listed as below:

Low forward voltage

High switching speed: 50ns max.

Reverse voltage: V<sub>OUT</sub> + V<sub>F</sub> or more

Rated current : I<sub>PK</sub> or more

## **Programming The Output Voltage**

For the CE8323 adjustable output version, the internal 0.6V reference voltage is compared to the voltage at the FB pin to generate an error signal at the output of the error amplifier. The output voltage is set by an external resistive voltage divider from the OUT to FB. The current drawn by the resistor network should be limited to maintain the overall converter efficiency. The maximum value of the resistor network is limited by the feedback input bias current and the potential for noise being coupled into the feedback pin. A resistor network less than 100k is recommended.

Typically, a minimum current of  $40\mu A$  flowing through the feedback divider gives good accuracy and noise covering. A standard low side resistor of  $10k\Omega$  is typically selected. The resistors are then calculated as:  $R1=V_{FB}/60\mu A=10k\Omega$ , R2=R1X [ $(V_{OUT}-V_{FB})/V_{FB}$ ],  $V_{FB}=0.6V$

To minimize the power consumption under light loads, it is desirable to choose large resistance values for both R1 and R2.

The use of 1% accuracy metal film resistor is recommended for the better output voltage accuracy.

#### **EXAMPLE**

During the Application Information section one specific example will be used to define and work with the different equations.

| Parameter             | Symbol               | Value | Unit |

|-----------------------|----------------------|-------|------|

| Input Voltage         | V <sub>IN</sub>      | 3.6   | V    |

| Minimum Input Voltage | V <sub>IN(min)</sub> | 2.9   | V    |

| Output Voltage        | V <sub>OUT</sub>     | 5.0   | V    |

| Input Current Limit set by R <sub>ILIM</sub>    | I <sub>LIM</sub> | 4     | А   |

|-------------------------------------------------|------------------|-------|-----|

| Feedback Voltage                                | $V_{FB}$         | 0.6   | V   |

| Switching Frequency                             | f                | 1     | MHz |

| Estimated Efficiency                            | η                | 90    | %   |

| Inductor Value of Choice                        | L1               | 3.3   | μH  |

| Output Capacitor Value of Choice                | C <sub>OUT</sub> | 22x 2 | μF  |

| Input Capacitor Value of Choice                 | C <sub>IN</sub>  | 22    | μF  |

| Output Rectifier Diode V <sub>F</sub> of Choice | $V_{F(D1)}$      | 0.43  | V   |

| Feedback Divider Resistor of Choice             | R1               | 13.7  | kΩ  |

|                                                 | R2               | 100   | kΩ  |

#### **PCB LAYOUT CONSIDERATION**

In the CE8323 boost regulator circuit, high pulsing current flows through two circuit loops. The first loop starts from the input capacitors, to the filter inductor, to the SW pin, to the internal NMOS switch, to the ground and back to the input capacitor, when the switch turns on. The second loop starts from input capacitor, to the filter inductor, to the SW pin to the external output rectifier diode, to the ground and back to the input capacitor, when the switch is off.

In PCB layout, minimizing the two loops area reduces the noise of this circuit and improves efficiency. A ground plane is recommended to connect input capacitor, output capacitor, and PGND pin of the CE8323. A good circuit board layout aids in extracting the most performance from the CE8323. Poor circuit layout degrades the output ripple and the electromagnetic interference (EMI) or electromagnetic compatibility (EMC) performance.

Several layout tips are listed below for the best electric and thermal performance. Figure 4 below illustrates the PCB layout example as reference.

- 1) Do not use thermal relief connection to the IN and the PGND pin. It is desirable to pour a maximized copper area connecting to PGND pin and the IN to help thermal dissipation and achieve the best noise performance.

- 2) If the board space allowed, a ground plane is highly desirable.

- 3) Use separate analog and power ground planes. Connect the sensitive analog circuitry (such as feedback divider resistors) to analog ground; connect the power components (such as input and output bypass capacitors) to power ground. Connect the two ground planes together near the load to reduce the effects of voltage dropped on circuit board traces.

- 4) Make the current trace from IN to inductor to SW pin (when internal NMOS turn on) as short as possible to reduce power dissipation and increase overall efficiency. Also the current trace from IN to inductor to output rectifier Schottky diode to  $C_{OUT}$  to PGND (when internal NMOS turn off) should be as short as possible. Put enough multiply-layer pads when they need to change the trace layer.

- 5) The CE8323 uses two separate ground connections, PGND for the driver and NMOS power device

and AGND for the sensitive analog control circuitry. The AGND and PGND pins should be tied directly together at the package. The PGND pin of the IC is the ground connection for high-current power converter node. High current return for the low-side driver and power NMOS. Connect PGND with large copper areas directly to the input and output supply returns and negative terminals of the input and output capacitors as close as possible, together directly to a power ground plane. Only connect to AGND through the Exposed Pad underneath the IC. The AGND pin of the IC is the analog ground connection to all of the noise sensitive signals. Provide a clean ground for the analog control circuitry and should not be in the path of large currents. Return for output voltage set resistor divider.

- 6) Place the positive terminal of  $C_{IN}$  near  $V_{IN}$  as closely as possible. This will reduce copper trace resistance which effects input voltage ripple of the IC. And the loop area formed by  $C_{IN}$  and PGND must be minimized to maintain input voltage steady and filter out the pulsing input current. For additional input voltage filtering, a 100nF bypass capacitor can be placed in parallel with  $C_{IN}$ , close to the  $V_{IN}$  pin, to shunt any high frequency noise to ground.

- 7) The output capacitor,  $C_{OUT}$ , should be placed as closely as possible to the negative terminal of the output rectifier Schottky diode and the IC. Any copper trace connections for the  $C_{OUT}$  capacitor can increase the series resistance, which directly effects output voltage ripple. For additional output voltage filtering, a low ESR ceramic bypass capacitor can be placed in parallel with  $C_{OUT}$ , to shunt any high frequency noise to ground. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the output, and the CE8323 PGND pin. The minimum recommended bypass capacitance is 100nF ceramic with a X5R or X7R dielectric and the optimum placement is closest to the output.

- 8) The output filter of the boost converter is also critical for layout. The Diode and Output capacitors should be placed to minimize the area of current loop through Output PGND SW.

- 9) The PCB copper area associated with SW, inductor and Schottky diode switching node must be minimized to reduce EMI and voltage overshoot, and avoid the potential noise problem.

- 10) Avoid routing high impedance traces, such as FB, near the high current traces and components or near the Diode node (D1). The feedback network, resistors R1 and R2 must be connected to FB pin directly as closely as possible. And FB is a sensitive signal node, trace area at FB pin should be small. Please keep it away from the inductor, SW, inductor and Schottky diode switching node on the PCB layout to avoid the noise inject into the system.

The feedback networks should be connected directly to a dedicated analog ground plane and this ground plane must connect to the AGND pin. If no analog ground plane is available, then the ground connection of the feedback network must tie directly to the AGND pin. Connecting the network to the PGND can inject noise into the system and effect performance.

- 11) If high impedance traces are routed near high current and/or the SW node, place a ground plane shield between the traces.

- 12) Exposed Paddle (bottom) should be connected to a continuous ground plane as close as to the device by several vias directly under the CE8323 for electrical contact and rated thermal performance. It

12(15)

dissipates the heat from the IC. EP must be connected to AGND at a single point with a star ground connection.

- 13) Pour copper plane on all unused board area and connect it to stable DC nodes, like IN, ground or OUT.

- 14) If the system chip interfacing with the CE pin has a high impedance state at shutdown mode and the IN is connected directly to a power source such as a Li-lon battery, it is desirable to add a pull down 1Mohm resistor between the CE and AGND pins to prevent the noise from falsely turning on the boost regulator at shutdown mode.

Figure 4. Recommended Top layer Component Placement for two Layers Board

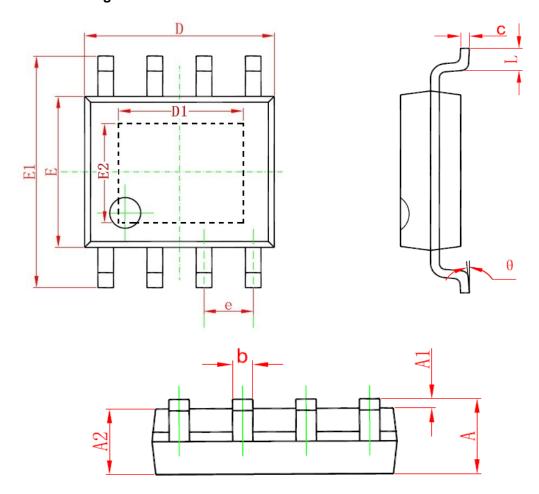

# ■ PACKAGING INFORMATION

# SOP8-PP Package Outline Dimensions

| Symbol   | Dimensions | In Millimeters | Dimensions | In Inches |

|----------|------------|----------------|------------|-----------|

| Cyrribor | Min        | Max            | Min        | Max       |

| Α        | 1.350      | 1.750          | 0.053      | 0.069     |

| A1       | 0.100      | 0.250          | 0.004      | 0.010     |

| A2       | 1.350      | 1.550          | 0.053      | 0.061     |

| b        | 0.330      | 0.510          | 0.013      | 0.020     |

| С        | 0.170      | 0. 250         | 0.006      | 0.010     |

| D        | 4.700      | 5.100          | 0.185      | 0.200     |

| D1       | 3.100      | 3.500          | 0.122      | 0.137     |

| Е        | 3.800      | 4.000          | 0.150      | 0.157     |

| E1       | 5.800      | 6.200          | 0.228      | 0.244     |

| E2       | 2.200      | 2.600          | 0.086      | 0.102     |

| е        | 1.270(BSC) |                | 0.050(     | BSC)      |

| L        | 0.400      | 1.270          | 0.016      | 0.050     |

| θ        | 0°         | 8°             | 0°         | 8°        |

#### © Nanjing Chipower Electronics Inc.

Chipower cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Chipower product. No circuit patent license, copyrights or other intellectual property rights are implied. Chipower reserves the right to make changes to their products or specifications without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.