# 1.5MHz 600mA Synchronous Step-Down

# CE8501 Series

## **Converter with Low Quiescent Current**

# ■ INTRODUCTION:

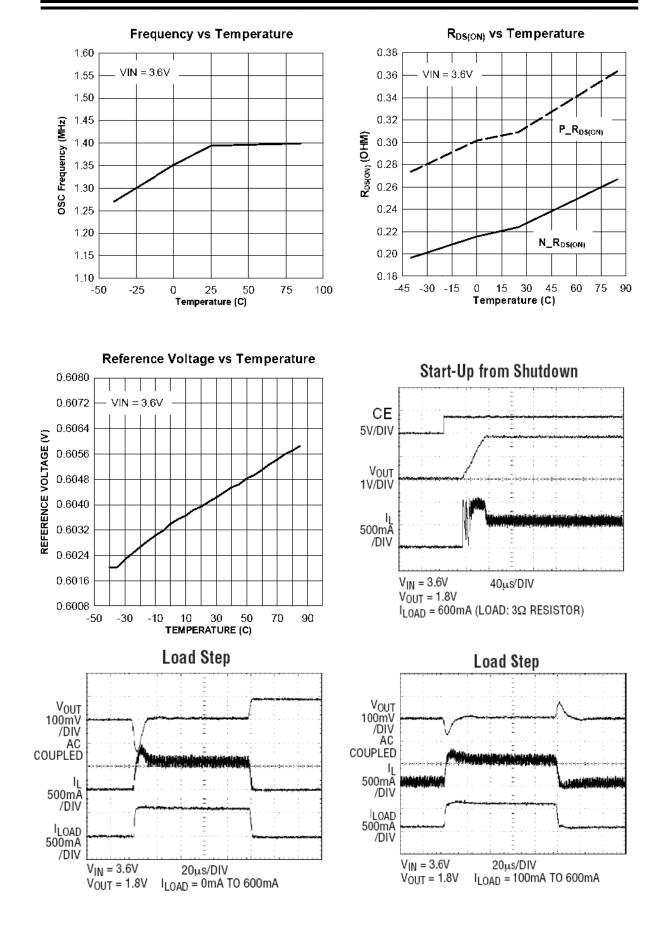

The CE8501 is a 1.5MHz constant frequency, slope compensated current mode PWM synchronous step-down converter. It is ideal for powering portable equipment which runs from a single cell Lithium-Ion battery. 100% duty cycle provides low dropout operation, extending battery life in portable systems. In power saving mode, 40 µ A quiescent current is very suitable for DSP/MCU in standby operation; and in active mode, low output ripple voltage is good enough for noise sensitive applications. The two modes can be automatically switched according to the load current.

# ■ APPLICATIONS:

- Cellular and Smart Phones

- Personal Information Appliances

- Wireless and DSL Modems

# ■ PIN CONFIGURATION:

# FEATURES:

- High efficiency : Up to 96%

- Output Current: 600mA (Typ.)

- 1.5MHz Constant Switching Frequency

- No Schottky Diode Required

- Input Voltage: 1.8V to 5.5V

- 0.6V Reference Allows Low Output Voltage

- Low Dropout: 100% duty Cycle

- Low Quiescent Current: 40µA

- Shutdown Current: <1µA

- Current Mode Operation for Excellent Line and Load Transient Response

- Built-in Thermal Protection

- Package: SOT-23-5

- Digital Still and Video Cameras

- Microprocessors Core Supplies

- Portable consumer equipments

# **ORDER INFORMATION:**

#### CE8501(1)2(3)(4)

| DESIGNATOR | SYMBOL DESCRIPTION |                                                   |

|------------|--------------------|---------------------------------------------------|

| 1          | А                  | Standard                                          |

| 23         | Integer            | Output Voltage<br>e.g.1.8V=②:1, ③:8<br>Adj=②:, ③: |

| 4          | M/MR               | Package: SOT-23-5                                 |

| PIN NU | MBER |                      | EUNCTION                         |  |

|--------|------|----------------------|----------------------------------|--|

| М      | MR   | PIN NAME             | FUNCTION                         |  |

| 1      | 3    | CE                   | Chip Enable Pin                  |  |

| 2      | 2    | V <sub>SS</sub>      | Ground                           |  |

| 3      | 5    | SW                   | External Inductor Connection Pin |  |

| 4      | 1    | V <sub>IN</sub>      | Power Input                      |  |

| 5      | 4    | V <sub>OUT</sub> /FB | Output Pin/Feedback(ADJ Version) |  |

### Tabel1. Pin Description

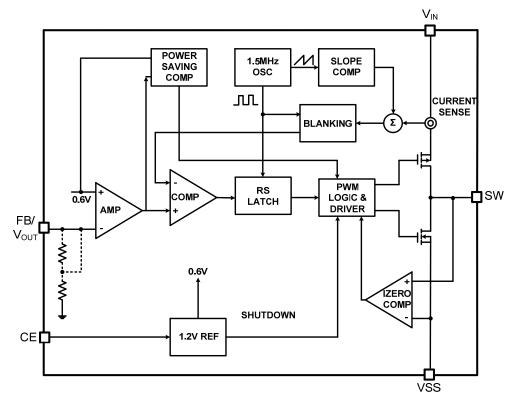

# BLOCK DIAGRAM

# ■ ABSOLUTE MAXIMUM RATINGS

| PARAME                             | ſER      | SYMBOL              | RATINGS                                   | UNITS |

|------------------------------------|----------|---------------------|-------------------------------------------|-------|

| Input Volta                        | age      | V <sub>IN</sub>     | V <sub>SS</sub> -0.3~V <sub>SS</sub> +6.5 | V     |

| CE,SW,FB/V <sub>OU</sub>           | ⊤Voltage |                     | V <sub>SS</sub> -0.3~V <sub>IN</sub> +0.3 | V     |

| Peak SW Sink and Source<br>Current |          | I <sub>SWMAX</sub>  | 1500                                      | mA    |

| Power Dissipation                  | SOT-23-5 | Pd                  | 400                                       | mW    |

| Operating Tem                      | perature | T <sub>opr</sub>    | -40~+85                                   | °C    |

| Junction Temperature               |          | Tj                  | 125                                       | °C    |

| Storage Temperature                |          | T <sub>stg</sub>    | -40~+125                                  | °C    |

| Soldering Temperature & Time       |          | T <sub>solder</sub> | <b>260</b> ℃, <b>10s</b>                  |       |

# ELECTRICAL CHARACTERISTICS

CE8501 Series

(V<sub>IN</sub>=CE=3.6V, Ta=25  $^\circ \!\! C$ , Test Circuit Figure1, unless otherwise specified)

| PARAMETER                              | SYMBOL                             | CONDITIONS                                                            | MIN                    | TYP              | MAX                    | UNITS |

|----------------------------------------|------------------------------------|-----------------------------------------------------------------------|------------------------|------------------|------------------------|-------|

| Output Voltage                         | V <sub>OUT(F)</sub> <sup>(1)</sup> | I <sub>OUT</sub> =100mA                                               | V <sub>OUT</sub> ×0.97 | V <sub>OUT</sub> | V <sub>OUT</sub> ×1.03 | V     |

|                                        |                                    | T <sub>A</sub> =25℃                                                   | 0.5880                 | 0.600            | 0.6120                 |       |

| Feedback Voltage                       | V <sub>FB</sub>                    | 0°C≤T <sub>A</sub> ≤85°C                                              | 0.5865                 | 0.600            | 0.6135                 | V     |

|                                        |                                    | -40°C≤T <sub>A</sub> ≤85°C                                            | 0.5850                 | 0.600            | 0.6150                 |       |

| Input Voltage                          | V <sub>IN</sub>                    |                                                                       | 1.8                    |                  | 5.5                    | V     |

| Supply Current1<br>(Active MODE)       | I <sub>SS1</sub>                   | V <sub>FB</sub> =0.50V                                                |                        | 270              | 400                    | μA    |

| Supply Current2<br>(Power Saving Mode) | I <sub>SS2</sub>                   | V <sub>FB</sub> =0.63V                                                |                        | 40               | 50                     | μA    |

| Shutdown Current                       | I <sub>SHDN</sub>                  | V <sub>CE</sub> =V <sub>SS</sub>                                      |                        | 0.1              | 1.0                    | μA    |

| Feedback Current                       | I <sub>FB</sub>                    | V <sub>FB</sub> =0.65V                                                |                        |                  | ±30                    | nA    |

| Maximum Output Current                 | I <sub>OUT</sub>                   | —                                                                     | 600                    |                  |                        | mA    |

| V <sub>FB</sub> Line Regulation        | $\Delta V_{FB}$                    | V <sub>IN</sub> = 1.8V~5.5V                                           |                        | 0.40             |                        | %/V   |

| Output Voltage Line<br>Regulation      | $\Delta V_{OUT}$                   | V <sub>IN</sub> = 1.8V~5.5V<br>I <sub>OUT</sub> =10mA                 |                        | 0.40             |                        | %/V   |

| Output Voltage<br>Load Regulation      | $\Delta V_{LOAD}$                  | I <sub>OUT</sub> =1mA<br>∼600mA                                       |                        | 0.02             |                        | %/mA  |

| Oscillator Frequency                   | f <sub>osc</sub>                   | V <sub>FB</sub> =0.6V or<br>V <sub>OUT</sub> =100%                    | 1.2                    | 1.5              | 1.8                    | MHz   |

| Peak Inductor Current                  | I <sub>PK</sub>                    | V <sub>IN</sub> =3V,V <sub>FB</sub> =0.5V<br>or V <sub>OUT</sub> =90% |                        | 1.0              |                        | А     |

| R <sub>DS(ON)</sub> OF P-CH FET        | R <sub>PFET</sub>                  | I <sub>SW</sub> = 100mA                                               |                        | 0.45             | 0.60                   | Ω     |

| R <sub>DS(ON)</sub> OF N-CH FET        | R <sub>NFET</sub>                  | I <sub>SW</sub> = -100mA                                              |                        | 0.35             | 0.50                   | Ω     |

| SW Leakage                             | I <sub>LSW</sub>                   | CE=0,V <sub>SW</sub> =0<br>or 5V, V <sub>IN</sub> =5V                 |                        | ±0.01            | ±1                     | μA    |

| CE "High" Voltage <sup>(2)</sup>       | V <sub>CE</sub> "H"                |                                                                       | 1.5                    |                  | V <sub>IN</sub>        | V     |

| CE "Low" Voltage <sup>(3)</sup>        | V <sub>CE</sub> "L"                |                                                                       |                        |                  | 0.3                    | V     |

| CE Leakage Current                     | I <sub>CE</sub>                    |                                                                       |                        | ±0.1             | ±1                     | μA    |

# NOTE :

1.  $V_{\text{OUT}(F)} \text{:} The fixed voltage version effective output voltage.$

2. High Voltage: Forcing CE above 1.5V enables the part.

3. Low Voltage: Forcing CE below 0.3V shuts down the device.

#### OPERATION

#### MAIN CONTROL LOOP

The CE8501 uses a constant frequency, current mode step-down architecture. Both the main (P-channel MOSFET) and synchronous (N-channel MOSFET) switches are internal. During normal operation, the internal top power MOSFET is turned on each cycle when the oscillator sets the RS latch, and turned off when the current comparator, I<sub>COMP</sub>, resets the RS latch. The peak inductor current at which I<sub>COMP</sub> resets the RS latch, is controlled by the output of error amplifier EA. When the load current increases, it causes a slight decrease in the feedback voltage. FB, relative to the 0.6V reference, which in turn, causes the EA amplifier's output voltage to increase until the average inductor current matches the new load current. While the top MOSFET is off, the bottom MOSFET is turned on until either the inductor current starts to reverse. as indicated by the current reversal comparator I<sub>RCMP</sub>, or the beginning of the next clock cycle.

#### MAXIMUM LOAD CURRENT

The CE8501 will operate with input voltage as low as 1.8V, however, the maximum load current decreases at lower input due to large IR drop on the main switch and synchronous rectifier. The slope compensation signal reduces the peak inductor current as a function of the duty cycle to prevent sub-harmonic oscillations at duty cycles greater than 50%.Conversely the current limit increase as the duty cycle decreases.

#### DISCONTINUOUS MODE OPERATION

At light loads, the inductor current may reach zero reverse on each pulse. The bottom MOSFET is turned off by the current reversal comparator,  $I_{RCMP}$ , and the switch voltage will ring. This is discontinuous mode operation, and is normal behavior for the switching regulator. At very light loads, the CE8501 will automatically skip pulses in discontinuous mode operation to maintain output regulation.

#### **SLOPE COMPENSATION**

Slope compensation provides stability in constant frequency architecture by preventing sub-harmonic oscillations at high duty cycles. It is accomplished internally by adding a compensating ramp to the inductor current signal at duty cycles in excess of 50%. This slope compensated current mode PWM control provides stable switching and cycle-by-cycle current limit for excellent load and line response.

#### POWER SAVING MODE OPERATION

At very light loads, the chip automatically enters power saving mode. In power saving mode at light load, a control circuit puts most of the circuit into sleep in order to reduce guiescent current and improve efficiency at light load. When the output voltage drops to certain threshold, the control circuit turns back on the oscillator and the PWM control loop, boosting output backup. When an upper threshold is reached, the control circuit again puts most of circuit into sleep, reducing quiescent current. During power saving mode operation, the converter positions the output voltage slightly higher than the nominal output voltage during PWM operation, allowing additional headroom for voltage drop during a load transient from light to heavy load. While the power saving mode improves light load efficiency, however, with the turning on and off, the noise or ripple voltage is

larger than that in the active Mode.

#### **DROPOUT OPERATION**

As the input supply voltage decreases to a value approaching the output voltage, the duty cycle increases toward the maximum on-time. Further reduction of the supply voltage forces the main switch to remain on for more than one cycle until reaches 100% duty cycle. The output voltage

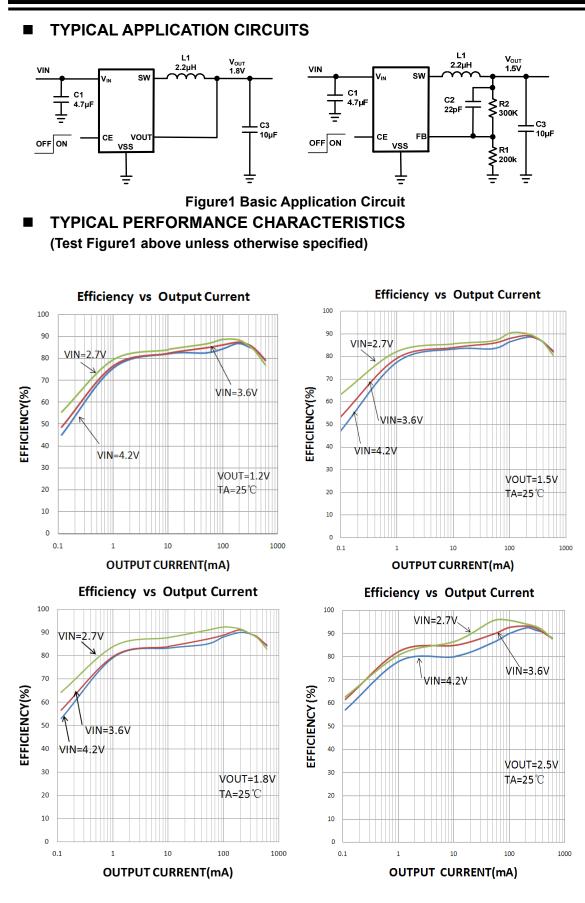

#### APPLICATION INFORMATION

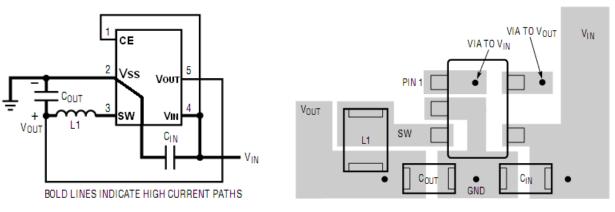

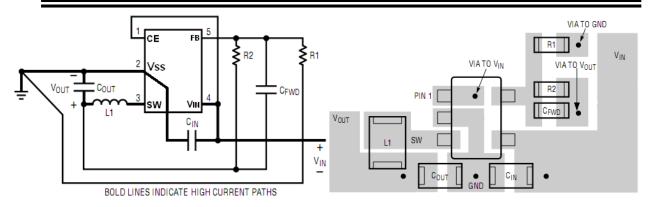

The basic CE8501 application circuits are shown in Figure 1.External component selection is driven by the load requirement and begins with the selection of L followed by  $C_{IN}$  and  $C_{OUT}$ .

#### SETTING THE OUTPUT VOLTAGE

Figure1 shows the basic application circuit with CE8501 adjustable output version. The external resistor sets the output voltage according to the following equation:

$$V_{OUT} = 0.6V \times \left(1 + \frac{R2}{R1}\right)$$

Table 2.Resistor select for output voltage setting

| V <sub>OUT</sub> | R1   | R2   |

|------------------|------|------|

| 1.2V             | 316K | 316K |

| 1.5V             | 316K | 470K |

| 1.8V             | 316K | 634K |

| 2.5V             | 316K | 1M   |

#### INPUT CAPACITOR SELECTION

In continuous mode, the source current of the top MOSFET is a square wave of duty cycle  $V_{OUT}/V_{IN}$ . To prevent large voltage transients, a low ESR input capacitor sized for the maximum RMS current must be used. The maximum RMS capacitor current is given by:

$C_{IN} \text{ required } I_{RMS} \cong I_{OMAX} \frac{[V_{OUT}(V_{IN} - V_{OUT})]^{1/2}}{V_{IN}}$

will then be determined by the input voltage minus the voltage drop across the P-channel MOSFET and the inductor.

An important detail to remember is that at low inputs supply voltages, the  $R_{DS(ON)}$  of the P-channel switch increases. Therefore, the user should calculate the power dissipation when the CE8501 is used at 100% duty cycle with low input voltage.

This formula has a maximum at  $V_{IN} = 2V_{OUT}$ , where  $I_{RMS} = I_{OUT}/2$ . This simple worst-case condition is commonly used for design because even significant deviations do not offer much relief. Ceramic capacitors with X5R or X7R dielectrics are highly recommended because of their low ESR and small temperature coefficients. A 4.7µF ceramic capacitor for most application is sufficient.

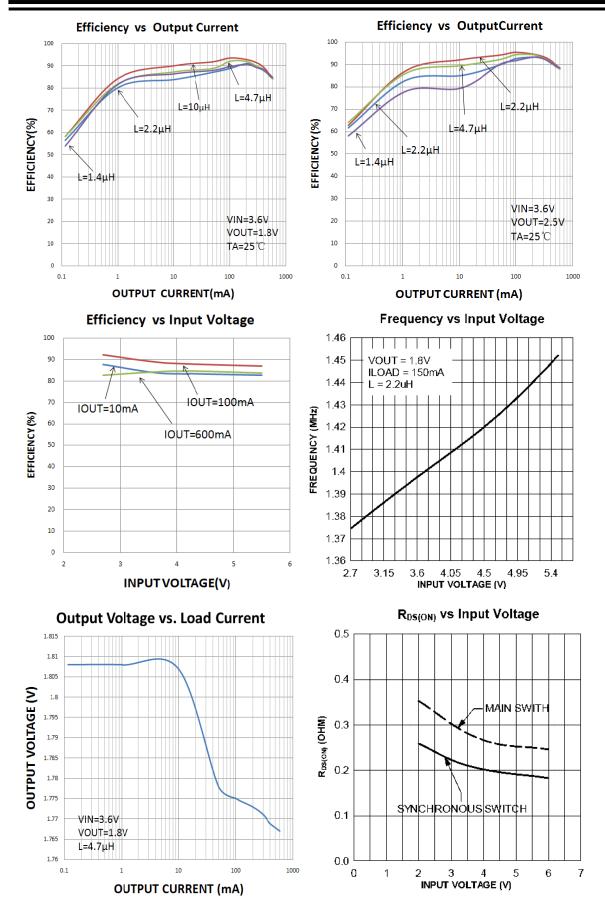

#### INDUCTOR SELECTION

For most applications, the value of the inductor will fall in the range of  $1\mu$ H to  $4.7\mu$ H. Its value is chosen based on the desired ripple current. Large value inductor lower ripple current and small value inductor result in higher ripple currents. Higher V<sub>IN</sub> or V<sub>OUT</sub> also increases the ripple current as shown in the following equation:

$$\Delta I_{L} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times L \times f_{osc}}$$

A reasonable starting point for setting ripple current is  $\triangle I_L$ =240mA (40% of 600mA). The DC current rating of the inductor should be at least equal to the maximum load current plus half the ripple current to prevent core saturation.

Different core materials and shapes will change the size/current and price/current relationship of an inductor. The choice of which

#### 1.5MHz 600mA Synchronous Step-Down Converters with Low Quiescent Current

CE8501 Series

style inductor to use often depends more on the price vs. size requirements and any radiated field/EMI requirements than on what the CE8501 requires to operate. Table 3 shows some typical surface mount inductors that work well in CE8501 applications.

Table 3.Representative Surface Mount Inductors

| PART   | VALUE | MAX  | MAX DC  | SIZE                  |

|--------|-------|------|---------|-----------------------|

| NUMBER | (µH)  | DCR  | CURRENT | $W \times L \times H$ |

|        |       | (mΩ) | (A)     | (mm <sup>3</sup> )    |

## **OUTPUT CAPACITOR SELECTION**

The selection of  $C_{OUT}$  is driven by the required effective series resistance (ESR). Typically, once the ESR requirement for  $C_{OUT}$  has been met, the RMS current rating generally far exceeds the  $I_{RIPPLE}$  requirement. The output ripple  $\triangle V_{OUT}$  is determined by:

$$\Delta V_{\rm OUT} \cong \Delta I_{\rm L} \left( {\rm ESR} + \frac{1}{8 {\rm fC}_{\rm OUT}} \right)$$

Where f = operating frequency,  $C_{OUT}$  = output capacitance and  $\triangle I_L$  = ripple current in the inductor. For a fixed output voltage, the output ripple is highest at maximum input voltage since  $\triangle I_L$  increase with input voltage. Ceramic capacitors with X5R or X7R dielectrics are recommended due to their low ESR and high ripple current.

| Sumida | 2.2 | 75    | 1.20 |         |

|--------|-----|-------|------|---------|

| CDRH   | 3.3 | 110   | 1.10 | 3.8×3.8 |

| 3D16   | 4.7 | 162   | 0.90 | ×1.8    |

| Sumida | 2.2 | 71.2  | 1.75 |         |

| CR43   | 3.3 | 86.2  | 1.44 | 4.5×4.0 |

|        | 4.7 | 108.7 | 1.15 | ×3.5    |

| Sumida | 2.2 | 75    | 1.32 | 4.7×4.7 |

| CDRH   | 3.3 | 110   | 1.04 | ×2.0    |

| 4D18   | 4.7 | 162   | 0.84 |         |

# PCB LAYOUT GUIDANCE

When laying out the printed circuit board, the following suggestions should be taken to ensure proper operation of the CE8501.

- The power traces, including the GND trace, the SW trace and the V<sub>IN</sub> trace should be kept short, direct and wide to allow large current flow. Put enough multiply-layer pads when they need to change the trace layer.

- 2. Keep the switching node, SW, away from the sensitive FB node.

- The FB pin should directly connect to the feedback resistors. The resistive divider R1/R2 must be connected between the (+) plate of C<sub>OUT</sub> and ground.

- Connect the (+) plate of C<sub>IN</sub> to the V<sub>IN</sub> pin as closely as possible.

5. Keep the (-) plate of  $C_{\mathsf{IN}}$  and  $C_{\mathsf{OUT}}$  as close as

## Figure 2a CE8501-1.8V Layout

Figure 2b CE8501-Adj Layout

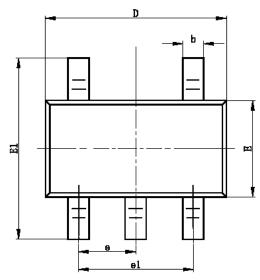

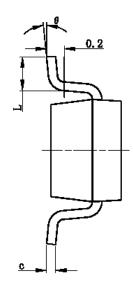

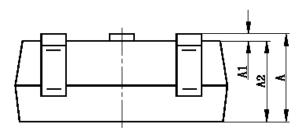

# PACKAGING INFORMATION

• SOT23-5 Package Outline Dimensions

| Sumb a l | Dimensions In | Millimeters      | Dimensions | In Inches |

|----------|---------------|------------------|------------|-----------|

| Symbol   | Min           | Max              | Nin        | Max       |

| A        | 1.050         | 1.250            | 0.041      | 0.049     |

| A1       | 0.000         | 0.100            | 0.000      | 0.004     |

| A2       | 1.050         | 1.150            | 0.041      | 0.045     |

| b        | 0.300         | 0.500            | 0.012      | 0.020     |

| с        | 0.100         | 0.200            | 0.004      | 0.008     |

| D        | 2.820         | 3.020            | 0.111      | 0.119     |

| E        | 1.500         | 1.700            | 0.059      | 0.067     |

| E1       | 2.650         | 2.950            | 0.104      | 0.116     |

| е        | 0.950(        | (BSC) 0.037(BSC) |            | BSC)      |

| e1       | 1.800         | 2.000            | 0.071      | 0.079     |

| L        | 0.300         | 0.600            | 0.012      | 0.024     |

| θ        | 0°            | 8°               | 0°         | 8°        |

#### © Nanjing Chipower Electronics Inc.

Chipower cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Chipower product. No circuit patent license, copyrights or other intellectual property rights are implied. Chipower reserves the right to make changes to their products or specifications without notice. Customers are advised to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete.