# CGS2536V Commercial Quad 1 to 4 Clock Drivers CGS2536TV Industrial Quad 1 to 4 Clock Drivers

## **General Description**

These Clock Generation and Support clock drivers are specifically designed for driving memory arrays requiring large fanouts while operating at high speeds.

This device meets the rise and fall time requirements of the 90 MHz and 100 MHz Pentium<sup>™</sup> procrssors.

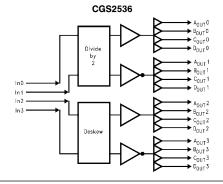

The CGS2536 I/O structures are CMOS. The outputs are separated into two banks of eight. One bank consists of divide by two outputs, the other, straight-through buffers. Within each bank, half the outputs are inverting, the other half non-inverting.

The CGS2536 specification guarantees part-to-part skew variation.

#### **Features**

- Guaranteed:

- 1.0 ns rise and fall times while driving 12 inches of 50  $\!\Omega$  microstrip terminated with 25 pF

- 350 ps pin-to-pin skew (t<sub>OSLH</sub> and t<sub>OSHL</sub>)

- 650 ps part-to-part variation on positive or negative transition

- Operates with either 3.3V or 5.0V supply

- Inputs 5V tolerant with V<sub>CC</sub> in 3.3V range

- Symmetric output current drive: 24 mA I<sub>OH</sub>/I<sub>OL</sub>

- Industrial temperature of -40°C to +85°C

- Symmetric package orientation

- Large fanout for memory driving applications

- Guaranteed 2 kV ESD protection

- Implemented on National's ABT family process

- 28-pin PLCC for optimum skew performance

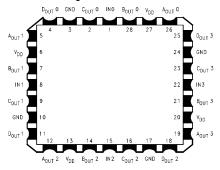

# **Connection Diagrams**

#### Pin Assignment for 28-Pin PLCC

TL/F/12325-1

# **Truth Table**

| Input | Output           |  |  |  |  |

|-------|------------------|--|--|--|--|

| In 0  | ABCD Out (0) ÷ 2 |  |  |  |  |

| In 1  | ABCD Out (1) ÷ 2 |  |  |  |  |

| In 2  | ABCD Out (2)     |  |  |  |  |

| In 3  | ABCD Out (3)     |  |  |  |  |

Pentium™ is a trademark of Intel Corporation

### **Absolute Maximum Ratings** (Note)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage (V<sub>CC</sub>) Input Voltage (V<sub>I</sub>) 7.0V Input Current  $-30 \, \text{mA}$

Current Applied to Output

(High/Low) Twice the Rated IOH/IOL

Operating Temperature

Industrial Grade -40°C to +85°C Commercial grade  $0^{\circ}$ C to  $+70^{\circ}$ C Storage Temperature Range  $-65^{\circ}\text{C}$  to  $+\,150^{\circ}\text{C}$

> Typical  $\theta_{\rm JA}$  62°C/W Airflow 0 LFM 225 LFM 43°C/W 500 LFM 34°C/W 900 LFM 27°C/W

# **Recommended Operating Conditions**

Supply Voltage  $V_{CC}\quad 4.5V \ to \ 5.5V$

V<sub>CC</sub> 3.0V to 3.6V

5 ns Maximum Input Rise/Fall Time (0.8V to 2.0V)

Free Air Operating Temperature

Commercial  $0^{\circ}$ C to +  $70^{\circ}$ C

Industrial -40°C to +85°C

Note: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the DC and AC Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions will define the conditions for actu-

#### **DC Electrical Characteristics**

Over recommended operating free air temperature range. All typical values are measured at  $V_{\rm CC}=5V,\,T_{\rm A}=25^{\circ}{\rm C}.$

| Symbol            | Parameter                         | Conditions                            | V <sub>CC</sub><br>(V) | Min  | Тур | Max  | Units    |  |

|-------------------|-----------------------------------|---------------------------------------|------------------------|------|-----|------|----------|--|

| V <sub>IH</sub>   | Input High Level Voltage          |                                       | 3.0                    | 2.1  |     |      |          |  |

|                   |                                   |                                       | 4.5                    | 3.15 |     |      | V        |  |

|                   |                                   |                                       | 5.5                    | 3.85 |     |      |          |  |

| V <sub>IL</sub>   | Input Low Level Voltage           |                                       | 3.0                    |      |     | 0.9  |          |  |

|                   |                                   |                                       | 4.5                    |      |     | 1.35 | V        |  |

|                   |                                   |                                       | 5.5                    |      |     | 1.65 |          |  |

| $V_{IK}$          | Input Clamp Voltage               | $I_{\parallel} = -18 \text{ mA}$      | 4.5                    |      |     | -1.2 | <b>V</b> |  |

| V <sub>OH</sub> F | High Level Output Voltage         | $I_{OH} = -50 \mu A$                  | 3.0                    | 2.9  |     |      |          |  |

|                   |                                   |                                       | 4.5                    | 4.4  |     |      | V        |  |

|                   |                                   |                                       | 5.5                    | 5.4  |     |      |          |  |

|                   |                                   | $I_{OH} = -24 \text{ mA}$             | 3.0                    | 2.46 |     |      |          |  |

|                   |                                   |                                       | 4.5                    | 3.76 |     |      | V        |  |

|                   |                                   |                                       | 5.5                    | 4.76 |     |      |          |  |

| V <sub>OL</sub>   | Low Level Output Voltage          | $I_{OL} = 50 \mu A$                   | 3.0                    |      |     | 0.1  |          |  |

|                   |                                   |                                       | 4.5                    |      |     | 0.1  | V        |  |

|                   |                                   |                                       | 5.5                    |      |     | 0.1  |          |  |

|                   |                                   | I <sub>OL</sub> = 24 mA               | 3.0                    |      |     | 0.44 |          |  |

|                   |                                   |                                       | 4.5                    |      |     | 0.44 | V        |  |

|                   |                                   |                                       | 5.5                    |      |     | 0.44 |          |  |

| I                 | Input Current @ Max Input Voltage | $V_{IH} = 7V$                         | 5.5                    |      |     | 7    | ^        |  |

|                   |                                   | $V_{IH} = V_{CC}$                     | 3.6                    |      |     | 1    | μΑ       |  |

| I <sub>IH</sub>   | High Level Input Current          | $V_{IH} = V_{CC}$                     | 5.5                    |      |     | 5    | μΑ       |  |

| I <sub>IL</sub>   | Low Level Input Current           | $V_{IL} = 0V$                         | 5.5                    | -5   |     |      | μΑ       |  |

| l <sub>OLD</sub>  | Minimum Dynamic Output Current*   | V <sub>OLD</sub> = 1.65V (max) 5.5 75 |                        |      |     | ^    |          |  |

|                   |                                   | $V_{OLD} = 0.9V \text{ (max)}$        | 3.0**                  | 36   |     |      | mA       |  |

| I <sub>OHD</sub>  | Minimum Dynamic Output Current*   | V <sub>OHD</sub> = 3.85V (min)        | 5.5                    | -75  |     |      |          |  |

|                   |                                   | V <sub>OHD</sub> = 2.1V (min)         | 3.0**                  | -25  |     |      | mA       |  |

| Icc               | Supply Current                    |                                       | 3.6                    |      |     | 75   |          |  |

|                   |                                   |                                       | 5.5                    |      |     | 235  | μΑ       |  |

| C <sub>IN</sub>   | Input Capacitance                 |                                       | 5.0                    |      | 5   |      | pF       |  |

<sup>\*</sup>Maximum test duration 2.0 ms, one output loaded at a time.

<sup>\*\*</sup>At V $_{CC}=$  3.3V, I $_{OLD}=$  55 mA min; @ V $_{CC}=$  3.6V, I $_{OLD}=$  64 mA min At V $_{CC}=$  3.6V, I $_{OHD}=$  -66 mA min

### AC Electrical Characteristics (Notes 1, 2, and 3)

Over recommended operating free air temperature range. All typical values are measured at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

| Symbol                                   | Parameter                                                        | V <sub>CC</sub><br>(V)<br>(Note 8) | CGS2536                                                                                                                                                                              |            |             |                                                                                                           |            |             |       |

|------------------------------------------|------------------------------------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-----------------------------------------------------------------------------------------------------------|------------|-------------|-------|

|                                          |                                                                  |                                    | $\begin{aligned} \textbf{T}_{\textbf{A}} &= +25^{\circ}\textbf{C} \\ \textbf{C}_{\textbf{L}} &= \textbf{50}~\textbf{pF}, \textbf{R}_{\textbf{L}} = \textbf{500}\Omega \end{aligned}$ |            |             | $T_{A} = -40^{\circ}\text{C to} + 85^{\circ}\text{C}$ (Note 4) $C_{L} = 50 \text{ pF}, R_{L} = 500\Omega$ |            |             | Units |

|                                          |                                                                  |                                    | Min                                                                                                                                                                                  | Тур        | Max         | Min                                                                                                       | Тур        | Max         |       |

| f <sub>max</sub>                         | Frequency Maximum                                                | 3.0<br>5.0                         |                                                                                                                                                                                      |            |             |                                                                                                           | 100<br>125 |             | MHz   |

| t <sub>PLH</sub>                         | Low-to-High Propagation Delay<br>CK to O <sub>n</sub>            | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 7.25<br>5.0 |                                                                                                           |            | 7.25<br>5.0 | ns    |

| t <sub>PHL</sub>                         | High-to-Low Propagation Delay<br>CK to O <sub>n</sub>            | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 5.5<br>4.5  |                                                                                                           |            | 5.5<br>4.5  | ns    |

| t <sub>OSLH</sub>                        | Maximum Skew Common Edge Output-to-Output Variation (Notes 1, 3) | 3.3<br>5.0                         |                                                                                                                                                                                      | 150<br>150 | 350<br>350  |                                                                                                           | 300<br>300 | 350<br>350  | ps    |

| t <sub>OSHL</sub>                        | Maximum Skew Common Edge Output-to-Output Variation (Notes 1, 3) | 3.3<br>5.0                         |                                                                                                                                                                                      | 150<br>150 | 350<br>350  |                                                                                                           | 300<br>300 | 350<br>350  | ps    |

| t <sub>rise</sub> ,<br>t <sub>fall</sub> | Rise/Fall Time<br>(from 0.8V/2.0V to 2.0V/0.8V) (Note 5)         | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 4.5<br>3.5  |                                                                                                           |            | 4.5<br>3.5  | ns    |

| t <sub>rise</sub> ,<br>t <sub>fall</sub> | Rise/Fall Time<br>(from 0.8V/2.0V to 2.0V/0.8V) (Note 6)         | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 0.8<br>0.4  |                                                                                                           |            | 1.0<br>0.6  | ns    |

| t <sub>rise</sub> ,<br>t <sub>fall</sub> | Rise/Fall Time<br>(from 0.8V/2.0V to 2.0V/0.8V) (Note 7)         | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 1.0<br>0.7  |                                                                                                           |            | 1.0<br>0.9  | ns    |

| t <sub>High</sub>                        | Pulse Width Duration High (Notes 2, 3)                           | 3.3<br>5.0                         | 4.0<br>4.0                                                                                                                                                                           |            |             | 4.0<br>4.0                                                                                                |            |             | 20    |

| t <sub>Low</sub>                         | Pulse Width Duration Low (Notes 2, 3)                            | 3.3<br>5.0                         | 4.0<br>4.0                                                                                                                                                                           |            |             | 4.0<br>4.0                                                                                                |            |             | ns    |

| t <sub>PVLH</sub>                        | Part-to-Part Variation of Low-to-High Transitions                | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 650<br>650  |                                                                                                           |            | 650<br>650  | no    |

| t <sub>PVHL</sub>                        | Part-to-Part Variation of High-to-Low Transitions                | 3.3<br>5.0                         |                                                                                                                                                                                      |            | 650<br>650  |                                                                                                           |            | 650<br>650  | ps    |

Note 1: Output-to-Output Skew is defined as the absolute value of the difference between the actual propagation delay for any outputs within the same packaged device. The specifications apply to any outputs switching in the same direction either LOW to HIGH (toSLH) or HIGH to LOW (toSHL).

Note 2: Time high is measured with outputs at 2.0V or above. Time low is measured with outputs at 0.8V or below. Input waveform characteristics for t<sub>High</sub>, t<sub>Low</sub> measurement: f = 66.67 MHz, duty cycle = 50%.

Note 3: The input waveform has a rise and fall time transition time of 2.5 ns (10% to 90%).

Note 4: Industrial range ( $-40^{\circ}$ C to  $+85^{\circ}$ C) limits apply to the commercial temperature range ( $0^{\circ}$ C to  $+70^{\circ}$ C).

Note 5: These Rise and Fall times are measured with C  $_L$  = 50 pF,  $R_L$  =  $500\Omega$  (see Figure 3).

Note 6: These Rise and Fall times are measured with  $C_L=25$  pF,  $R_L=500\Omega$  (see Figure 3), and are guaranteed by design.

Note 7: These Rise and Fall times are measured driving 12 inches of  $50\Omega$  microstrip terminated with equivalent  $C_L = 25$  pF (see Figure 4), and are guaranteed by design.

Note 8: Voltage Range 5.0 is 5.0V  $\pm$  0.5V, 3.3 is 3.3V  $\pm$  0.3V.

Note 9: For increased output drive, output pins may be connected together when the corresponding input pins are connected together.

### **Power On Requirements**

#### **DETAILED DESCRIPTION**

The divide by two block of the CGS2536 is accomplished using two negative-edge-triggered flip-flops. During poweron, the inverting flip-flop causes outputs Aout1 through Dout1 to be High. The non-inverting flip-flop causes outputs Aout0 through Dout0 to be Low. Two flip-flops are used to achieve minimum skew between the non-inverting and inverting outputs.

To guarantee that the flip-flops power-up out of phase, the IN0 and IN1 pins must be held low while power is applied to  $V_{CC}.$  IN0 and IN1 must remain low until  $V_{CC} \geq 3V.$

#### **Application Hints**

In a typical user environment INO and IN1 inputs may be connected common. Power is applied simultaneously to the crystal oscillator and the CGS2536. If the oscillator output does not deliver a clean first negative-going-edge to the INO and IN1 inputs, only one flip-flop may toggle.

Even if the user delays application of  $V_{CC}$  to the CGS2536, a false trigger may occur. Simply gating the oscillator to the IN0 and IN1 inputs will not guarantee correct operation, since a "runt" pulse may propagate through the gate and toggle only one of the flip-flops.

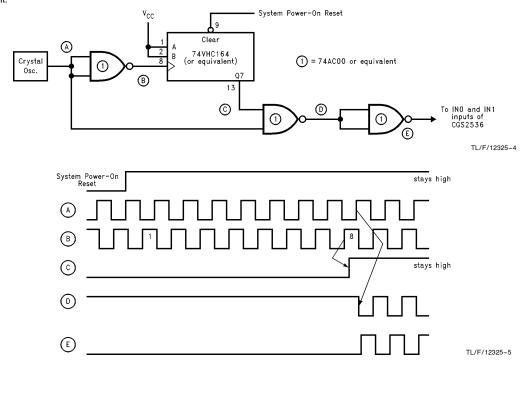

Figure 1 shows a circuit that delivers "runt-free" negative-going-edges to the IN0 and IN1 inputs. This circuit ensures that the first clocking pulse seen by the IN0 and IN1 inputs consists of a full positive half-cycle of the crystal oscillator. Figure 2 shows the waveforms from the synchronizing circuit

The propagation delay of the 74AC00 gates and the toggle frequency of the 74VHC164 limit the maximum frequency of operation. Equivalent logic elements that have faster propagation delays can be substituted for the NAND gates and shift register. For example, a generic GAL22V10-5 could be programmed as the NAND gates that drive the CGS2536.

#### Figure 1 CIRCUIT DESCRIPTION

Assumptions:

- V<sub>CC</sub> is applied simultaneously to the crystal oscillator, CGS2536, 74AC00, and 74VHC164.

- 2. A system power-on reset is "Low" long enough for  $V_{CC}$  and the crystal oscillator to stabilize.

At power-on, assertion (low) of the system power-on reset clears the outputs of the 74VHC164 serial to parallel converter.

As a result, nodes C and E are low ensuring power-on requirements for the CGS2536 are met. When the system power-on reset is de-asserted, the eighth positive-going-edge received by the 74VHC164 causes node C to go high. Node C remains high as long as power is applied. However, node D still remains high due to the oscillator output (A) being low. Node E stays low until the next positive-going-edge of the oscillator. Thus, a full positive half-cycle of the oscillator is seen by the IN1 and IN0 inputs, which ensures that both flip-flops of the divide by two toggle.

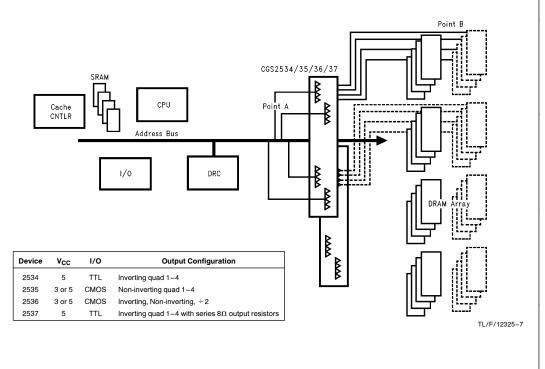

### CGS2534/35/36/37

## **Memory Array Driving**

In order to minimize the total load on the address bus, quite often memory arrays are driven by buffers while having the inputs of the buffers tied together. Although this practice was feasible in the conventional memory designs, in today's high speed, large buswidth designs which require address fetching at higher speeds, this technique produces many undesired results such as cross-talk and over/undershoot.

CGS2534/35/36/37 Quad 1 to 4 clock drivers were designed specifically to address these application issues on high speed, large memory arrays systems.

These drivers are optimized to drive large loads, with 3.5 ns propagation delays. These drivers produce less noise while reducing the total capacitive loading on the address bus by having only four inputs tied together (see the diagram below, point A). This helps to minimize the overshoot and undershoot by having only four outputs being switched simultaneously.

Also this larger fan-out helps to save board space since for every one of these drivers, two conventional buffers were typically being used.

Another feature associated with these clock drivers is a 350 ps pin-to-pin skew specification. The minimum skew specification allows high speed memory system designers to optimize the performance of their memory sub-system by operating at higher frequencies without having concerns about output-to-output (bank-to-bank) synchronization problem which are associated with driving high capacitive loads (Point B).

The diagram below depicts a "2534/35/36/37" a memory subsystem operating at high speed with large memory capacity. The address bus is common to both the memory and the CPU and I/Os.

These drivers can operate beyond 125 MHz, and are also available in 3V-5V TTL/CMOS versions with large current drive .

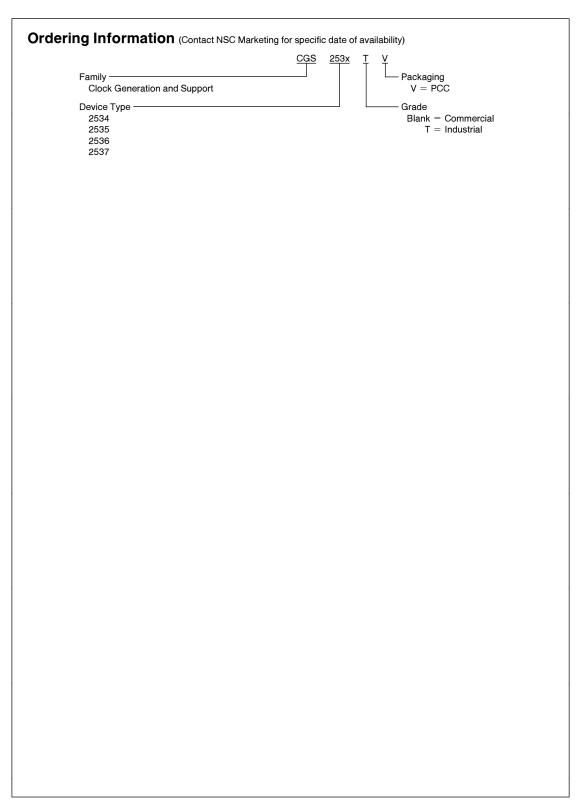

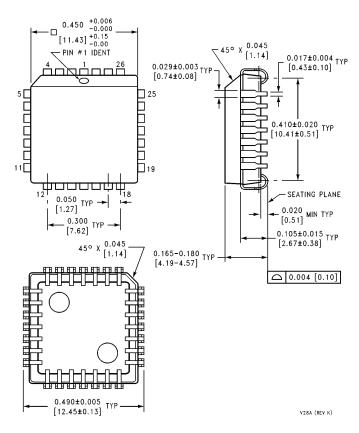

# Physical Dimensions inches (millimeters)

28-Lead Molded Plastic Leaded Chip Carrier Order Number CGS2536V or CGS2536TV **NS Package Number V28A**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018

**National Semiconductor**

Europe Fax: (+49) 0-180-530 85 86 Fax: (+49) U-18U-35U oo oo Email: onjwege etevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tei: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 **National Semiconductor** Hong Kong Ltd.

13th Floor, Straight Block,

Ocean Centre, 5 Canton Rd.

Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408