#### PRELIMINARY

#### **General Description**

National

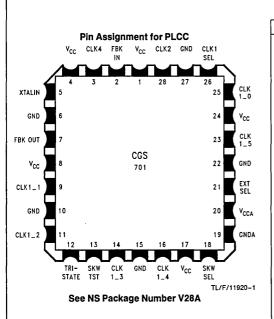

CGS701 is an off the shelf clock driver specifically designed for today's high speed designs. It provides low skew outputs which are produced at different frequencies from three fixed input references. The XTALIN input pin is designed to be driven from a 15 MHz–50 MHz crystal oscillator.

The PLL, using a charge pump and an internal loop filter, multiplies this input frequency to create a maximum output frequency of four times the input.

The device includes a TRI-STATE® control pin to disable the outputs. This feature allows for low frequency functional testing and debugging.

Also included, is an EXTSEL pin to allow testing the chip via an external source. The EXTSEL pin, once set to high, causes the External-Clock\_MUX to change its input from the output of the VCO and Counter to the external clock signal provided via SKWTST input pin. (continued)

#### **Features**

- Guaranteed and tested: 500 ps pin-to-pin skew (t<sub>OSHL</sub> and t<sub>OSLH</sub>) on 1X outputs. ±500 ps propagation delay

- Output buffer of eight drivers for large fanout

- 25 MHz-160 MHz output frequency range

- Outputs operating at 4X, 2X, 1X of the reference frequency for multifrequency bus applications

- Selectable output frequency

- Internal loop filter to reduce noise and jitter

- Separate analog and digital V<sub>CC</sub> and ground pins

- Low frequency test mode by disabling the PLL

- Implemented on National's Core CMOS process

- Symmetric output current drive: +30/-30 mA I<sub>OL</sub>/I<sub>OH</sub>

- Industrial temperature of -40°C to +85°C

- 28-pin PCC for optimum skew performance

- Guaranteed 2 kV ESD protection

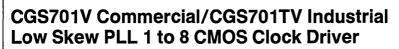

#### **Connection Diagram**

## Pin Description

|     | FLUC            | Package                     |

|-----|-----------------|-----------------------------|

| Pin | Name            | Description                 |

| 1   | Vcc             | Digital V <sub>CC</sub>     |

| 2   | FBK IN          | Feedback Input Pin          |

| 3   | CLK4            | 4X Clock Output             |

| 4   | V <sub>CC</sub> | Digital V <sub>CC</sub>     |

| 5   | XTALIN          | Crystal Oscillator Input    |

| 6   | GND             | Digital Ground              |

| 7   | FBK OUT         | Feedback Output Pin         |

| 8   | V <sub>CC</sub> | Digital V <sub>CC</sub>     |

| 9   | CLK1I           | 1X Clock Output             |

| 10  | GND             | Digital Ground              |

| 11  | CLK12           | 1X Clock Output             |

| 12  | TRI-STATE       | Output TRI-STATE Control    |

| 13  | SKWTST          | Skew Testing Pin            |

| 14  | CLK1_3          | 1X Clock Output             |

| 15  | GND             | Digital Ground              |

| 16  | CLK1_4          | 1X Clock Output             |

| 17  | Vcc             | Digital V <sub>CC</sub>     |

| 18  | SKWSEL          | Skew Test Selector Pin      |

| 19  | GNDA            | Analog Ground               |

| 20  | VCCA            | Analog V <sub>CC</sub>      |

| 21  | EXTSEL          | External Clock MUX Selector |

| 22  | GND             | Digital Ground              |

| 23  | CLK1_5          | 1X Clock Output             |

| 24  | Vcc             | Digital V <sub>CC</sub>     |

| 25  | CLK1_0          | 1X Clock Output             |

| 26  | CLK1SEL         | CLK1 Multiplier Selector    |

| 27  | GND             | Digital Ground              |

| 28  | CLK2            | 2X Clock Output             |

|     |                 |                             |

#### General Description (Continued)

CLK1SEL pin changes the output frequency of the CLK1\_0 thru CLK1\_5 outputs. During normal operation, when CLK1SEL pin is high, these outputs are at the same frequency as the input crystal oscillator, while CLK2 and CLK4 outputs are at twice and four times the input frequency respectively.

Once CLK1SEL pin is set to a low logic level, the CLK1 outputs will be at twice the input frequency, the same as the

### **Block Diagram**

CLK2 output, with CLK4 output still being at four times the input frequency.

In addition, another pin is added for increasing the test capability. SKWSEL pin allows testing of the counter's output and skew of the output drivers by bypassing the VCO. In this test mode CLK4 frequency is the same as SKWTST input frequency, while CLK2 is 1/2 and CLK1 frequencies are 1/4 respectively (refer to the Truth Table). In addition CLK1SEL functionality is also true under this test condition.

#### **Truth Table**

| Input       |            |            |            |           | Output    |             |             |  |

|-------------|------------|------------|------------|-----------|-----------|-------------|-------------|--|

| CLK1<br>SEL | EXT<br>SEL | SKW<br>SEL | SKW<br>TST | TRI-STATE | CLK4      | CLK2        | CLK1        |  |

| Н           | L          | L          | х          | н         | 4 x f in  | 2 x f in    | fin         |  |

| L           | L          | L          | х          | н         | 4 x f in  | 2 x f in    | 2 x f in    |  |

| X           | н          | х          | л          | н         | л         | Л           | л           |  |

| Н           | L          | н          | Л          | Н         | 1 x f tst | 1/2 x f tst | 1/4 x f tst |  |

| L           | L          | н          | Л          | н         | 1 x f tst | 1/2 x f tst | 1⁄₂ x f tst |  |

| Х           | Х          | Х          | х          | L         | Z         | Z           | Z           |  |

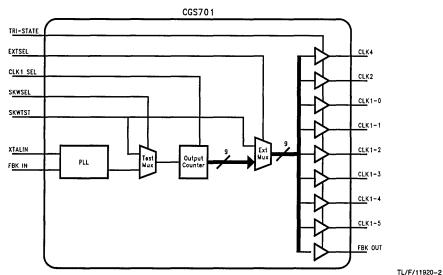

#### **Typical Application**

4-89

4

#### Absolute Maximum Ratings (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage (V <sub>CC</sub> )                     | -0.5V to +7.0V                      |

|-------------------------------------------------------|-------------------------------------|

| DC Input Voltage Diode Current (IIK)                  |                                     |

| V = -0.5V                                             | — 20 mA                             |

| $V = V_{\rm CC} + 0.5 V$                              | + 20 mA                             |

| DC Input Voltage (V <sub>I</sub> )                    | $-0.5 V$ to $V_{CC}$ + 0.5 V        |

| DC Output Diode Current (I <sub>O</sub> )             |                                     |

| V = -0.5V                                             | -20 mA                              |

| $V = V_{\rm CC} + 0.5 V$                              | + 20 mA                             |

| DC Output Voltage (V <sub>O</sub> )                   | $-0.5 V$ to $V_{\mbox{CC}}$ + 0.5 V |

| DC Output Source                                      |                                     |

| or Sink Current (I <sub>O</sub> )                     | ±60 mA                              |

| DC V <sub>CC</sub> or Ground Current                  |                                     |

| per Output Pin (I <sub>CC</sub> or I <sub>GND</sub> ) | ±60 mA                              |

| Storage Temperature (T <sub>STG</sub> )               | -65°C to +150°C                     |

| Junction Temperature                                  | 150°C                               |

| Power Dissipation                                     |                                     |

| (Static and Dynamic) (Note 2)                         | 1400 mW                             |

|                                                       |                                     |

# Recommended Operating Conditions

| Supply Voltage (V <sub>CC</sub> )   | 4.5V to 5.5V          |

|-------------------------------------|-----------------------|

| Input Voltage (V <sub>I</sub> )     | 0V to V <sub>CC</sub> |

| Output Voltage (V <sub>O</sub> )    | 0V to V <sub>CC</sub> |

| Input Crystal Frequency             | 25 MHz-40 MHz         |

| Operating Temperature               |                       |

| Commercial                          | 0°C to +70°C          |

| Industrial                          | -40°C to +85°C        |

| External Clock Frequency            |                       |

| (EXTCLK Pin)                        | 1 MHz-10 MHz          |

| Minimum Input Edge Rate (ΔV/Δt)     |                       |

| Crystal Input VIN from 0.8V to 2.0V | 5 ns                  |

| All Other Inputs                    | 50 ns                 |

|                                     |                       |

Note 1: The Absolute MAximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the DC and AC Electrical Characteristics tables are not guaranteed at the absolute maximum ratings. The Recommended Operating Conditions will define the conditions for actual device operation.

Note 2: Power dissipation is calculated using 49°C/W as the thermal coefficient for the PCC package at 225 LFM airllow. The input frequency is assumed at 33 MHz with CLK4 at 132 MHz and CLK2 and CLK1 being at 66 MHz. In addition, the ambient temperature is assumed 70°C.

#### **DC Electrical Characteristics**

Over recommended operating free air temperature range. All typical values are measured at V<sub>CC</sub> = 5V,  $T_A$  = 25°C.

| Symbol          | Parameter                            | Vcc        | $V_{CC} = 4.5V - 5.5V$<br>T = 0°C to 70°C              |                                                      |            | Units | Conditions                                             |  |

|-----------------|--------------------------------------|------------|--------------------------------------------------------|------------------------------------------------------|------------|-------|--------------------------------------------------------|--|

|                 |                                      |            | Min                                                    | Тур                                                  | Max        |       |                                                        |  |

| V <sub>IH</sub> | Minimum Input High<br>Level Voltage  | 4.5<br>5.5 | 2.0<br>2.0                                             |                                                      |            | v     |                                                        |  |

| VIL             | Maximum Input Low<br>Level Voltage   | 4.5<br>5.5 |                                                        |                                                      | 0.8<br>0.8 | v     |                                                        |  |

| V <sub>OH</sub> | Minimum Output High<br>Level Voltage | 4.5<br>5.5 | 4.4<br>5.4                                             | 4.4<br>5.4                                           |            | v     | $I_{OUT} = -50 \ \mu A$<br>$I_{OH} = -30 \ m A$        |  |

|                 |                                      | 4.5<br>5.5 | $\begin{array}{c} V_{CC}-0.6\\ V_{CC}-0.6 \end{array}$ |                                                      |            |       |                                                        |  |

| V <sub>OL</sub> | Maximum Output High<br>Level Voltage |            | v                                                      | l <sub>OUT</sub> = -50 μA<br>l <sub>OL</sub> = 30 mA |            |       |                                                        |  |

|                 |                                      | 4.5<br>5.5 |                                                        |                                                      | 0.6<br>0.6 | ] `   |                                                        |  |

| ЮН              | High Level<br>Output Current         | 4.5        | 50                                                     | 110                                                  | 170        | mA    | $V_{OH} = V_{CC} - 1.0V$                               |  |

| I <sub>OL</sub> | Low Level Output Current             | 5.5        | 50                                                     | 110                                                  | 170        | mA    | V <sub>OL</sub> = 1.0V                                 |  |

| I <sub>IN</sub> | Leakage Current                      | 4.5<br>5.5 | -50                                                    |                                                      | 50.0       | μΑ    | $V_{IN} = 0.4V \text{ or } 4.6V$                       |  |

| C <sub>IN</sub> | Input Capacitance                    | 4.5<br>5.5 |                                                        |                                                      | 10.0       | pF    |                                                        |  |

| ICC             | Quiescent Current<br>(No Load)       | 5.5        |                                                        | 0.02                                                 | 0.2        | mA    | $V_{IN} = V_{CC}, GND$<br>$V_{IN} = V_{CC} - 2.1, GND$ |  |

| Ісст            | I <sub>CC</sub> per TTL Input        | 5.5        |                                                        |                                                      | 2.5        | 7     |                                                        |  |

| Symbol             | Parameter                                                                        |                      |                                                                            | Conditions                                 | V <sub>CC</sub> = 4.5V-5.5V<br>T = 0°C to +70°C<br>C <sub>L</sub> = Circuit 1<br>R <sub>L</sub> = Circuit 1 |                |                   | Units          |    |

|--------------------|----------------------------------------------------------------------------------|----------------------|----------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------|-------------------|----------------|----|

|                    |                                                                                  |                      |                                                                            |                                            | Min                                                                                                         | Тур            | Max               | ]              |    |

| t <sub>rise</sub>  | Output Rise                                                                      | CLK4<br>CLK2<br>CLK1 | 0.8V to 2.6V<br>1.0V to V <sub>CC</sub> - 1<br>1.0V to V <sub>CC</sub> - 1 |                                            | (Note 1)                                                                                                    |                |                   | 2.0            | ns |

|                    |                                                                                  | All                  | 0.8V to 2.0V                                                               |                                            |                                                                                                             |                |                   | 1.5            |    |

| t <sub>fall</sub>  | Output Fall                                                                      | CLK4<br>CLK2<br>CLK1 | 2.6V to 0.8V<br>$V_{CC} = 1.0V$ to 1.0V<br>$V_{CC} = 1.0V$ to 1.0V         |                                            | (Note 1)                                                                                                    |                |                   | 2.0            | ns |

|                    |                                                                                  | All                  | 0.8V to 2.0V                                                               |                                            |                                                                                                             |                |                   | 1.5            |    |

| t <sub>SKEW</sub>  | Maximum Edge-to-<br>Edge Output Skew+ to + Edges<br>+ to + Edges<br>+ to + Edges |                      | CLK1 Outputs<br>CLK1 and CLK4<br>CLK2 and CLK4                             | (Note 2)                                   |                                                                                                             |                | 500<br>500<br>500 | ps             |    |

| tLOCK              | Time to Lock the Output to the Synch Input                                       |                      |                                                                            |                                            |                                                                                                             |                |                   | 10.0           | ms |

| <sup>t</sup> CYCLE | Output Duty Cycle                                                                |                      |                                                                            | CLK1 Outputs<br>CLK2 Output<br>CLK4 Output | (Note 3)                                                                                                    | 40<br>40<br>30 |                   | 60<br>60<br>70 | %  |

| Jitter             | Output Jitter                                                                    |                      |                                                                            |                                            | (Note 4)                                                                                                    |                |                   | 0.4            | ns |

| t <sub>PD</sub>    | Propogation Delay from XTALIN to FBKOUT                                          |                      |                                                                            |                                            | (Notes 6, 2, 4, 5)                                                                                          | -0.5           |                   | +0.5           | ns |

Note 1:  $t_{rise}$  and  $t_{fall}$  parameters are measured at the pin of the device.

Note 2: Skew is measured at 50% of V<sub>CC</sub>.

Note 3: Output duty cycle is measured at  $V_{DD}/2$ .

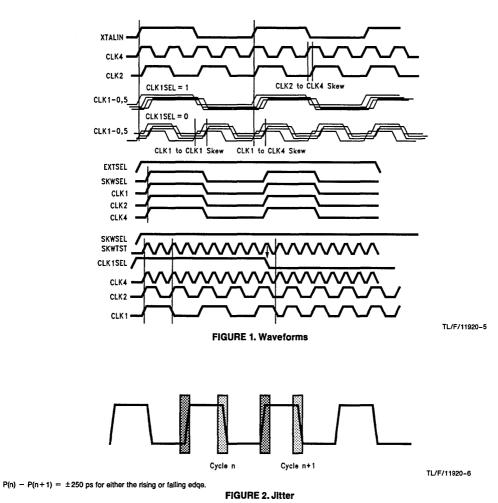

Note 4: Jitter parameter is characterized and is guaranteed by design only. It measures the uncertainty of either the positive or the negative edge compared to its previous cycle. It is also measured at output levels of V<sub>CC</sub>/2. Refer to *Figure 2* for further explanation.

Note 5: Measured from the ref. input to any output pin. The length of the feedback and XTALIN traces will impact this delay time.

Note 6: This parameter includes pin-to-pin skew, cycle to cycle jitter, part-to-part variation as well as propagation delay thru the device.

Note 7: The GNDA pins of the 701 must be as free of noise as possible for minimum jitter. Separate analog ground plane is recommended for the PCB.

Also the V<sub>CCA</sub> pin requires extra filtering to further reduce noise. Ferrite beads for filtering and bypass capacitors are suggested for the V<sub>CCA</sub> pin.

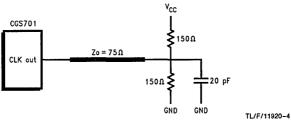

#### Circuit 1. Test Circuit

**CGS701**

#### AC Electrical Characteristics (Continued)

CGS701