# CH7308B SDVO¹ LVDS Transmitter

#### **Features**

- Single/Dual LVDS Transmitter up to 165Mpixels/s

- Support resolutions up to 1600x1200 (1920x1200 with reduced blanking)

- LVDS low jitter PLL accepts spread spectrum input

- LVDS 18-bit and 24-bit outputs

- 2D dither engine

- Panel protection and power sequencing

- High-speed SDVO<sup>1</sup> serial (1G~2Gbps) AC-coupled differential RGB inputs

- Low voltage interface support to graphics device

- Programmable power management

- Fully programmable through serial port

- Configuration through OpCodes<sup>1</sup>

- Complete Windows driver support

- Boundary scan support

- Offered in a 64-pin LQFP package

### **General Description**

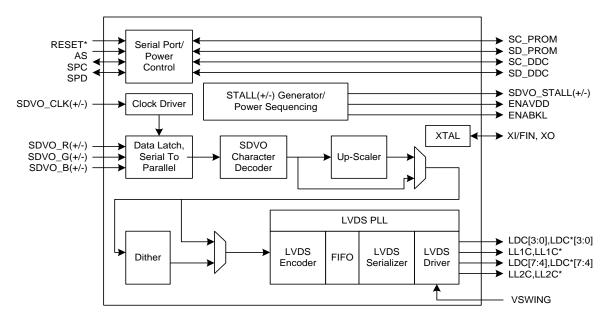

The CH7308B is a display controller device, which accepts digital graphics input signals, upscales, encodes, and transmits data through an LVDS transmitter to a LCD panel. This device accepts one channel of RGB data over three pairs of serial data ports.

The LVDS Transmitter includes a low jitter PLL to generate a high frequency serialized clock and all circuitry required to upscale, encode, serialize and transmit data. The CH7308B supports a maximum pixel rate of 165MP/s.

The LVDS transmitter includes a panel fitting up-scaler and a programmable dither function to support 18-bit LCD panels. Data is encoded into commonly used formats, including those specified in the OpenLDI and SPWG specifications. Serialized data is outputted on three to eight differential channels.

### <sup>1</sup>Intel Proprietary

Figure 1: Functional Block Diagram

# **Table of Contents**

| 1.0 | Pin Assignment                          | 3  |

|-----|-----------------------------------------|----|

| 1.1 | Package Diagram                         | 3  |

| 1.2 | Pin Description                         |    |

| 2.0 | Functional Description                  | 6  |

| 2.1 | Input Interface                         |    |

| 2.2 | Automatic Panel-Fitting                 | 8  |

| 2.3 | Emission Reduction Clock                | 9  |

| 2.4 | Dithering                               | 9  |

| 2.5 | Power Sequencing                        |    |

| 2.6 | Panel Protection                        |    |

| 2.7 | Command Interface                       | 10 |

| 3.0 | Register Control                        | 13 |

| 4.0 | Electrical Specifications               | 13 |

| 4.1 | Absolute Maximum Ratings                |    |

| 4.2 | Recommended Operating Conditions        |    |

| 4.3 | Electrical Characteristics              |    |

| 4.4 | DC Specifications                       |    |

| 4.5 | AC Specifications                       |    |

| 4.6 | LVDS Output Specifications              |    |

| 4.7 | LVDS Output Timing                      |    |

| 5.0 | Package Dimensions                      | 20 |

| 6.0 | Revision History                        | 21 |

|     | - · · · - J · · · · · · · · · · · · · · |    |

## 1.0 Pin Assignment

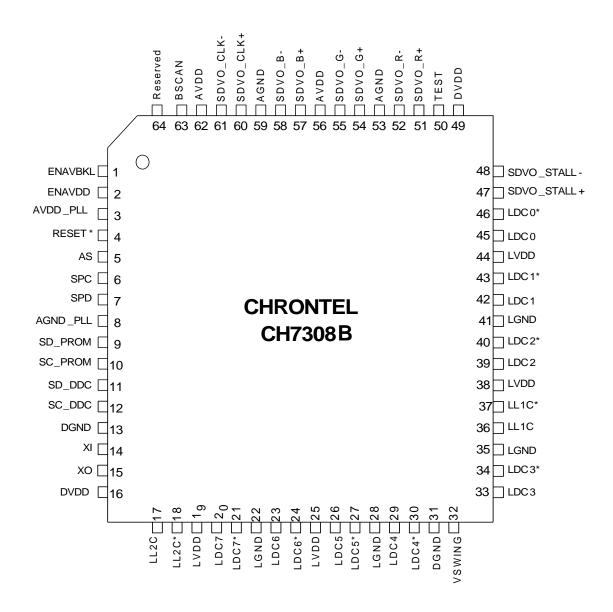

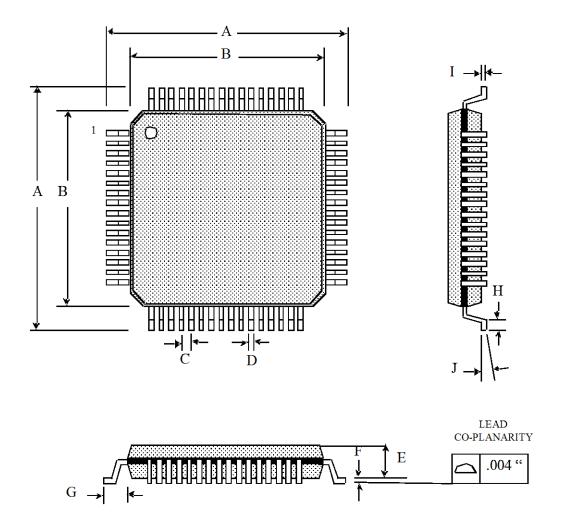

### 1.1 Package Diagram

Figure 2: 64 Pin LQFP Pin Out (Top View)

# 1.2 Pin Description

**Table 1: Pin Description**

| Pin# | Type   | Symbol   | Description                                                                    |

|------|--------|----------|--------------------------------------------------------------------------------|

| 4    | In     | RESET*   | Reset* Input (Internal pull-up)                                                |

|      |        |          | When this pin is low, the device is held in the power-on reset                 |

|      |        |          | condition. When this pin is high, reset is controlled through the              |

|      |        |          | serial port interface.                                                         |

| 5    | In     | AS       | Address Select (Internal pull-up)                                              |

|      |        |          | This pin determines the serial port address of the device                      |

|      |        |          | (0,1,1,1,0,0,AS*,0).                                                           |

| 6    | In/Out | SPC      | Serial Port Clock Input                                                        |

|      |        |          | This pin functions as the clock input of the serial port interface             |

|      |        |          | and operates with from 0 to 2.5V. This pin requires an external                |

|      |        |          | $4k\Omega$ - $9k\Omega$ pull up resistor to 2.5V                               |

| 7    | In/Out | SPD      | Serial Port Data Input/Output                                                  |

|      |        |          | This pin functions as the bi-directional data pin of the serial port           |

|      |        |          | interface and operates with inputs from 0 to 2.5V. Outputs are                 |

|      |        |          | driven from 0 to 2.5V. This pin requires an external $4k\Omega$ - $9k\Omega$   |

|      |        |          | pull up resistor to 2.5V.                                                      |

| 9    | In/Out | SD_PROM  | Routed Data Output to PROM                                                     |

|      |        |          | This pin functions as the bi-directional data pin of the serial port           |

|      |        |          | interface for the external 5V serial EEPROM used for ADD2 card                 |

|      |        |          | designs. This pin requires an external 5.6K pull-up resistor to the            |

|      |        |          | desired high state voltage. Leave open if unused.                              |

| 10   | In/Out | SC_PROM  | Routed Clock Output to PROM                                                    |

|      |        |          | This pin functions as the clock bus of the serial port interface for           |

|      |        |          | the external 5V serial EEPROM used for ADD2 card designs.                      |

|      |        |          | This pin requires an external 5.6K pull-up resistor to the desired             |

|      |        |          | high state voltage. Leave open if unused.                                      |

| 11   | In/Out | SD_DDC   | Routed Serial Port Data Output to DDC                                          |

|      |        |          | This pin functions as the bi-directional data pin of the serial port           |

|      |        |          | to the DDC of the receiver. This pin requires an external $4$ – $9$ k $\Omega$ |

|      |        |          | pull-up resistor to the desired high state voltage. Leave open if              |

|      |        |          | unused.                                                                        |

| 12   | In/Out | SC_DDC   | Routed Serial Port Clock Output to DDC                                         |

|      |        |          | This pin functions as the clock bus of the serial port to the DDC of           |

|      |        |          | the receiver. This pin requires an external 4–9k $\Omega$ pull-up resistor     |

|      |        |          | to the desired high state voltage. Leave open if unused.                       |

| 2    | Out    | ENAVDD   | Panel Power Enable                                                             |

|      |        |          | Enable LCD panel VDD (2.5V).                                                   |

| 1    | Out    | ENABKL   | Backlight Enable                                                               |

|      |        |          | Enable backlight of LCD panel (2.5V).                                          |

| 63   | In     | BSCAN    | BSCAN (internal pull low)                                                      |

|      |        |          | This pin should be left open or be pulled low with $10k\Omega$ resistor.       |

| 50   | Out    | TEST     | TEST                                                                           |

|      |        |          | Internal test pin to monitor the state of the ENEXBUF (External                |

|      |        |          | Buffer Enable) signal. See TB49 for details. If the ENEXBUF                    |

|      |        |          | signal does not need to be monitored, this pin may be left open.               |

| 64   | In     | Reserved | Reserved                                                                       |

|      |        |          | This pin should be left open                                                   |

| Pin#        | Type  | Symbol              | Description                                                                                                                   |

|-------------|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| 51, 52, 54, | In    | SDVO_R+/-           | SDVO Data Channel Inputs                                                                                                      |

| 55, 57, 58  |       | SDVO_G+/-           | These pins accept 3 AC-coupled differential pair of inputs from                                                               |

|             |       | SDVO_B+/-           | the digital video port of a graphics controller. These 3 pairs of                                                             |

|             |       |                     | inputs can be R, G, B. The differential p-p input voltage has a                                                               |

|             |       |                     | maximum value of 1.2V, with a minimum value of 175mV.                                                                         |

| 60, 61      | In    | SDVO_CLK+/-         | Differential Clock Input associated with SDVO Data Channel                                                                    |

|             |       |                     | (SDVO_R+/-, SDVO_G+/-, SDVO_B+/-)                                                                                             |

|             |       |                     | The range of this clock pair is 100~200MHz. For specific pixel                                                                |

|             |       |                     | rates in specific modes, this clock pair will run at an integer                                                               |

| 1= 10       |       | antio amitt         | multiple of the pixel rate. Refer to section 2.1.2 for details.                                                               |

| 47, 48      | Out   | SDVO_STALL+/-       | Stall Signal Pair associated with SDVO Data Channel (SDVO R+/-, SDVO G+/-, SDVO B+/-)                                         |

|             |       |                     | This differential pair is used as a stall indication for a VGA                                                                |

|             |       |                     | controller, which is capable of driving out SDVO_R+/-,                                                                        |

|             |       |                     | SDVO_G+/-, SDVO_B+/- data. When toggling between 100MHz                                                                       |

|             |       |                     | and 200MHz, the stall indication state is asserted ('1' value);                                                               |

|             |       |                     | when not toggling at all the state is de-asserted ('0' value). The                                                            |

|             |       |                     | differential p-p output voltage has a maximum value of 1.2V, with                                                             |

|             |       |                     | a minimum value of 175mV.                                                                                                     |

| 36, 37      | Out   | LL1C, LL1C*         | LVDS Differential Clock Channel 1                                                                                             |

| 17, 18      | Out   | LL2C, LL2C*         | LVDS Differential Clock Channel 2                                                                                             |

| 33, 39, 42, | Out   | LDC[3:0], LDC*[3:0] | LVDS Differential Data[3:0]                                                                                                   |

| 45, 34, 40, |       |                     |                                                                                                                               |

| 43, 46      |       |                     |                                                                                                                               |

| 20, 23, 26, | Out   | LDC[7:4], LDC*[7:4] | LVDS Differential Data [7:4]                                                                                                  |

| 29, 21, 24, |       |                     |                                                                                                                               |

| 27, 30      |       |                     |                                                                                                                               |

| 32          | In    | VSWING              | LVDS Swing Control                                                                                                            |

|             |       |                     | This pin sets the swing level of the LVDS outputs. A 2.4KOhm                                                                  |

|             |       |                     | resistor should be connected between this pin and LGND using                                                                  |

| 1.4         | T     | XI /EIN             | short and wide traces.                                                                                                        |

| 14          | In    | XI/FIN              | Crystal Input/External Reference Input                                                                                        |

|             |       |                     | A parallel resonant 14.31818 MHz crystal (+/-1000 ppm) should be attached between this pin and XO. Alternatively, an external |

|             |       |                     | CMOS compatible clock may be used to drive the XI/FIN input.                                                                  |

| 15          | Out   | XO                  | Crystal Output                                                                                                                |

| 1.5         | Jul   | 110                 | A parallel resonant 14.31818 MHz crystal (+/-1000 ppm) should                                                                 |

|             |       |                     | be attached between this pin and XI/FIN. However, if an external                                                              |

|             |       |                     | CMOS clock is attached to XI/FIN, XO should be left open.                                                                     |

| 16, 49      | Power | DVDD                | Digital Supply Voltage (2.5V)                                                                                                 |

| 13, 31      | Power | DGND                | Digital Ground                                                                                                                |

| 19, 25, 38, | Power | LVDD                | LVDS Supply Voltage (3.3V)                                                                                                    |

| 44          |       |                     |                                                                                                                               |

| 22, 28, 35, | Power | LGND                | LVDS Ground                                                                                                                   |

| 41          |       |                     |                                                                                                                               |

| 56, 62      | Power | AVDD                | Analog Supply Voltage (2.5V)                                                                                                  |

| 53, 59      | Power | AGND                | Analog Ground                                                                                                                 |

| 3           | Power | AVDD_PLL            | LVDS PLL Supply Voltage (3.3V)                                                                                                |

| 8           | Power | AGND_PLL            | LVDS PLL Ground                                                                                                               |

201-0000-064 Rev. 3.0, 05/11/2011 5

## 2.0 Functional Description

### 2.1 Input Interface

One pair of differential clock signals and three differential pairs of signals (R/G/B) form one channel data. The input data is 10-bit serialized data. Input data operates from 1GHz~2GHz and is a 10x multiple of the clock rate (SDVO\_CLK+/-). The CH7308B first de-serializes the input into 10-bit parallel data with synchronization and alignment then the 10-bit characters are mapped into 8-bit color data or control data (Hsync, Vsync, DE).

#### 2.1.1 Interface Voltage Levels

All differential SDVO pairs are AC coupled differential signals. Therefore, there is not a specified DC signal level for the signals to operate at. The minimum differential p-p input voltage is 175mVand the maximum differential p-p input voltage is 1.2V. The minimum differential p-p output voltage is 0.247V and the maximum differential p-p output voltage is 0.453V.

#### 2.1.2 Input Clock and Data Timing

A data character is transmitted least significant bit first. The beginning of a character is noted by the falling edge of the SDVO\_CLK+ edge. The skew among input lanes is required to be no larger than 2ns.

The clock rate must be between 100MHz~200MHz. The pixel rate can be 25MP/s~165MP/s. The pixel rate and the clock rate do not have to be equal. The clock rate is a multiple of the pixel rate (1x, 2x or 4x depending on the pixel rate) such that the clock rate remains within the 100MHz~200MHz range. In the condition that the clock rate is running at a multiple of the pixel rate, there isn't enough pixel data to fill the data channels. Dummy fill characters ('0001111010') are used to stuff the data stream. The CH7308B supports the following clock rate multipliers and fill patterns shown in **Table 2**.

Table 2: CH7308B supported Pixel Rates, Clock Rates, Data Transfer Rates and Fill Patterns

| Pixel Rate   | Clock Rate – Multiplier    | Stuffing Format        | Data Transfer Rate - Multiplier |  |

|--------------|----------------------------|------------------------|---------------------------------|--|

| CH7308B      |                            |                        |                                 |  |

| 25~50 MP/s   | 100~200 MHz – 4xPixel Rate | Data, Fill, Fill, Fill | 1.00~2.00 GHz – 10xClock Rate   |  |

| 50~100 MP/s  | 100~200 MHz – 2xPixel Rate | Data, Fill             | 1.00~2.00 GHz – 10xClock Rate   |  |

| 100~165 MP/s | 100~200 MHz – 1xPixel Rate | Data                   | 1.00~2.00 GHz – 10xClock Rate   |  |

#### 2.1.3 Synchronization

Synchronization and channel-to-channel deskewing is facilitated by the transmission of special characters during the blank period. The CH7308B synchronizes during the initialization period and subsequently uses the blank periods to re-synch to the data stream.

#### 2.1.4 LVDS-Output

Table 3: Signal Mapping for Single LVDS Channel

|           | 18-bit SPWG / 18-bit OpenLDI | 24-bit SPWG / 24-bit OpenLDI |

|-----------|------------------------------|------------------------------|

| LDC[0](1) | R0 / R0                      | R0 / R2                      |

| LDC[0](2) | R1 / R1                      | R1 / R3                      |

| LDC[0](3) | R2 / R2                      | R2 / R4                      |

| LDC[0](4) | R3 / R3                      | R3 / R5                      |

| LDC[0](5) | R4 / R4                      | R4 / R6                      |

| LDC[0](6) | R5 / R5                      | R5 / R7                      |

| LDC[0](7) | G0 / G0                      | G0 / G2                      |

| LDC[1](1) | G1 / G1                      | G1 / G3                      |

| LDC[1](2) | G2 / G2                      | G2 / G4                      |

| LDC[1](3) | G3 / G3                      | G3 / G5                      |

| LDC[1](4) | G4 / G4                      | G4 / G6                      |

| LDC[1](5) | G5 / G5       | G5 / G7       |

|-----------|---------------|---------------|

| LDC[1](6) | B0 / B0       | B0 / B2       |

| LDC[1](7) | B1 / B1       | B1 / B3       |

| LDC[2](1) | B2 / B2       | B2 / B4       |

| LDC[2](2) | B3 / B3       | B3 / B5       |

| LDC[2](3) | B4 / B4       | B4 / B6       |

| LDC[2](4) | B5 / B5       | B5 / B7       |

| LDC[2](5) | HSYNC / HSYNC | HSYNC / HSYNC |

| LDC[2](6) | VSYNC / VSYNC | VSYNC / VSYNC |

| LDC[2](7) | DE / DE       | DE / DE       |

| LDC[3](1) |               | R6 / R0       |

| LDC[3](2) |               | R7 / R1       |

| LDC[3](3) |               | G6 / G0       |

| LDC[3](4) |               | G7 / G1       |

| LDC[3](5) |               | B6 / B0       |

| LDC[3](6) |               | B7 / B1       |

| LDC[3](7) |               | RES / RES     |

**Table 4: Signal Mapping for Dual LVDS Channel**

|           | 18-bit SPWG / 18-bit OpenLDI | 24-bit SPWG / 24-bit OpenLDI |

|-----------|------------------------------|------------------------------|

| LDC[0](1) | Ro0 / Ro0                    | Ro0 / Ro2                    |

| LDC[0](2) | Ro1 / Ro1                    | Ro1 / Ro3                    |

| LDC[0](3) | Ro2 / Ro2                    | Ro2 / Ro4                    |

| LDC[0](4) | Ro3 / Ro3                    | Ro3 / Ro5                    |

| LDC[0](5) | Ro4 / Ro4                    | Ro4 / Ro6                    |

| LDC[0](6) | Ro5 / Ro5                    | Ro5 / Ro7                    |

| LDC[0](7) | Go0 / Go0                    | Go0 / Ro2                    |

| LDC[1](1) | Go1 / Go1                    | Go1 / Ro3                    |

| LDC[1](2) | Go2 / Go2                    | Go2 / Go4                    |

| LDC[1](3) | Go3 / Go3                    | Go3 / Go5                    |

| LDC[1](4) | Go4 / Go4                    | Go4 / Go6                    |

| LDC[1](5) | Go5 / Go5                    | Go5 / Go7                    |

| LDC[1](6) | Bo0 / Bo0                    | Bo0 / Bo2                    |

| LDC[1](7) | Bo1 / Bo1                    | Bo1 / Bo3                    |

| LDC[2](1) | Bo2 / Bo2                    | Bo2 / Bo4                    |

| LDC[2](2) | Bo3 / Bo3                    | Bo3 / Bo5                    |

| LDC[2](3) | Bo4 / Bo4                    | Bo4 / Bo6                    |

| LDC[2](4) | Bo5 / Bo5                    | Bo5 / Bo7                    |

| LDC[2](5) | HSYNC / HSYNC                | HSYNC / HSYNC                |

| LDC[2](6) | VSYNC / VSYNC                | VSYNC / VSYNC                |

| LDC[2](7) | DE / DE                      | DE / DE                      |

| LDC[3](1) |                              | Ro6 / Ro0                    |

| LDC[3](2) |                              | Ro7 / Ro1                    |

| LDC[3](3) |                              | Go6 / Ro0                    |

| LDC[3](4) |                              | Go7 / Go1                    |

| LDC[3](5) |                              | Bo6 / Bo0                    |

| LDC[3](6) |                              | Bo7 / Bo1                    |

| LDC[3](7) |                              | RES / RES                    |

| LDC[4](1) | Re0 / Re0                    | Re0 / Re2                    |

| LDC[4](2) | Re1 / Re1                    | Re1 / Re3                    |

| LDC[4](3) | Re2 / Re2                    | Re2 / Re4                    |

| LDC[4](4) | Re3 / Re3                    | Re3 / Re5                    |

| LDC[4](5) | Re4 / Re4                    | Re4 / Re6                    |

| LDC[4](6) | Re5 / Re5                    | Re5 / Re7                    |

| LDC[4](7) | Ge0 / Ge0                    | Ge0 / Ge2                    |

| LDC[5](1) | Ge1 / Ge1     | Ge1 / Ge3     |

|-----------|---------------|---------------|

| LDC[5](2) | Ge2 / Ge2     | Ge2 / Ge4     |

| LDC[5](3) | Ge3 / Ge3     | Ge3 / Ge5     |

| LDC[5](4) | Ge4 / Ge4     | Ge4 / Ge6     |

| LDC[5](5) | Ge5 / Ge5     | Ge5 / Ge7     |

| LDC[5](6) | Be0 / Be0     | Be0 / Be2     |

| LDC[5](7) | Be1 / Be1     | Be1 / Be3     |

| LDC[6](1) | Be2 / Be2     | Be2 / Be4     |

| LDC[6](2) | Be3 / Be3     | Be3 / Be5     |

| LDC[6](3) | Be4 / Be4     | Be4 / Be6     |

| LDC[6](4) | Be5 / Be5     | Be5 / Be7     |

| LDC[6](5) | HSYNC / LCTLE | HSYNC / LCTLE |

| LDC[6](6) | VSYNC / LCTLF | VSYNC / LCTLF |

| LDC[6](7) | DE / LA6RL    | DE / LA6RL    |

| LDC[7](1) |               | Re6 / Re0     |

| LDC[7](2) |               | Re7 / Re1     |

| LDC[7](3) |               | Ge6 / Re0     |

| LDC[7](4) |               | Ge7 / Re1     |

| LDC[7](5) |               | Be6 / Be0     |

| LDC[7](6) |               | Be7 / Be1     |

| LDC[7](7) |               | RES           |

### 2.2 Automatic Panel-Fitting

Serialized input data, sync and clock signals are input to the CH7308B from the graphics controller's serial digital video output port. Input is through three differential data pairs and one differential clock pair. The data rate is in the range of 1.0~2.0GHz. The clock rate, independent from the pixel rate, is 1/10 of the data rate, resulting in the range of 100M~200MHz. Horizontal sync and vertical sync information are embedded in the data stream.

Given the panel information (output timing information), the CH7308B can automatically fit the output timing to the panel. The up-scaler in the CH7308B supports but is not limited to the following LVDS panel sizes:

**Table 5: Popular Panel Sizes**

| WUXGA      | 1920x1200 ( Reduced Blanking) |  |

|------------|-------------------------------|--|

| UXGA       | 1600x1200                     |  |

| Wide SXGA+ | 1680x1050                     |  |

| SXGA+      | 1400x1050                     |  |

|            | 1360x1024                     |  |

| WSXGA      | 1440x900                      |  |

| SXGA       | 1280x1024                     |  |

|            | 1280x960                      |  |

| WXGA       | 1366x768                      |  |

| XGA        | 1024x768                      |  |

|            | 1024x600                      |  |

| SVGA       | 800x600                       |  |

The CH7308B is capable of up-scaling images containing 1400 active horizontal pixels or less to the native resolution of the supported LVDS panel. For resolutions containing more than 1400 horizontal pixels, no up-scaling will be done. The up-scaler periodically sends a pair of SDVO\_STALL(+/-) signals to the graphics controller to halt the transmission of one line of active video data. When the SDVO\_STALL(+/-) signals toggle between 100MHz and 200MHz, this is interpreted as asking for next line of video data to be "stalled"; not toggling at all is considered as asking for the next line of video data to be sent. The Up-scaler performs 2D interpolation of the graphics input data and does not change the pixel rate between the input and the output. The 2D interpolation consists of programmable non-linear functions. The maximum pixel rate supported by the Up-scaler is 200MP/s.

#### 2.3 Emission Reduction Clock

LVDS output can support a  $\pm 2.5\%$  spreading in the output clock to reduce EMI emissions. The frequency and the amplitude of the spreading triangle waveform can be programmed via opcode commands.

#### 2.4 Dithering

The dither engine in the CH7308B converts 24-bit per pixel RGB data to 18-bit per pixel RGB data before sending the data to the LVDS encoder. The maximum pixel rate supported is 165MP/s. This feature supports 18-bit LVDS panels only.

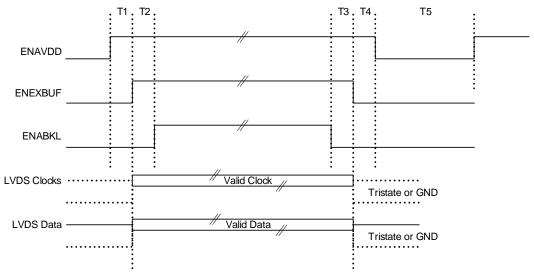

### 2.5 Power Sequencing

The CH7308B conforms to the SPWG requirements on power sequencing. The timing specification shown in figure 4 is a superset of the requirements dictated by the SPWG specification. The timing parameters can be programmed to different values via opcode commands to suit the timing requirements defined by the particular panel specifications to be used.

**Figure 3: Power Sequencing**

**Table 6: Power Sequencing**

|    | Range     | Increment |

|----|-----------|-----------|

| T1 | 1-1023 ms | 1 ms      |

| T2 | 1-1023 ms | 1ms       |

| T3 | 1-1023 ms | 1ms       |

| T4 | 1-1023 ms | 1 ms      |

| T5 | 1-1023 ms | 1ms       |

The power-on sequence begins when the LVDS software registers are set properly via opcode commands and the internal PLL lock detection circuit, the internal Sync detection circuit, and the XCLK detection circuit (see section 2.6) indicate that HSYNC, VSYNC and XCLK are stable. The power-off sequence begins when any of the detection circuits indicates instability in the timing signals (see section 2.6), or through opcode programming. Once the power-off sequence starts, the internal state machine will complete the power-off sequence and power-on sequence is allowed only after T5 is passed.

To verify the T1 – T5 LVDS Panel Power Sequencing, please see TB49 for more details.

#### 2.6 Panel Protection

Damage to the LCD panel may occur if either HSYNC or VSYNC signals are absent from the LVDS link. This situation can happen when there is a catastrophic failure in the PC or the graphics system. The CH7308B is designed to prevent damage to the panel under such a failure. If the system fails, the CH7308B does not expect any software instruction from the graphics controller to power down the panel. Detection circuits are used to monitor the three timing signals – HSYNC, VSYNC and XCLK. If any one, combination of, or all of these signals becomes unstable or missing, the CH7308B will commence Power Down Sequencing.

The power up sequence can occur only if there are no missing HSYNC and VSYNC, the input clock is available, the PLL clock is stable and the SetActiveOutput opcode is called. The power down sequence is initiated if one of those conditions fails. The panel protection circuitry is comprised of the PLL Lock Detection block, which detects an unstable clock from the LVDS PLL, the SYNC Detection block, which detects missing inputs HSYNC and VSYNC, and the Clock Detection block, which detects missing input CLOCK.

The SYNC Detection block consists of counters to count HSYNC and VSYNC pulses. One counter is used to count the number of HSYNC pulses per frame over 3 frames. The end counts for all 3 frames must be equal to enable the power up sequence. In addition, the SYNC Detection block checks for the presence of VSYNC and HSYNC. If VSYNC is missing for 2 frames or if HSYNC is missing for 32us, the power up sequence is disabled. Conversely, if the panel has been enabled and the number of HSYNC pulses per frame is different over 3 frames, VSYNC is missing for 2 frames, or HSYNC is missing for 32us, the CH7308B will go into a power down sequence.

The PLL Lock Detection, SYNC Detection and Clock Detection blocks can be defeated independently. Opcode commands are supported for these features. The power up sequence can also occur if the panel protection circuitry is defeated.

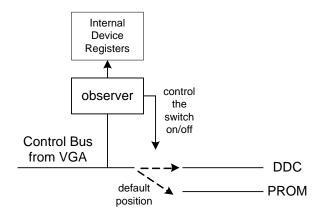

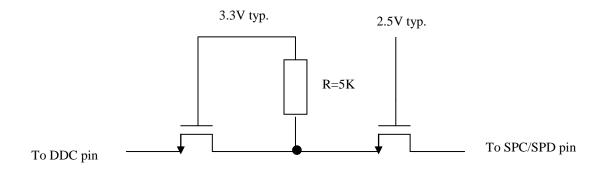

#### 2.7 Command Interface

Communication is through a two-wire path, control clock (SPC) and data (SPD). The CH7308B accepts incoming control clock and data from a graphics controller, and is capable of redirecting that data stream to the ADD2 card PROM, DDC, or CH7308B internal registers. The control bus is able to run up to 1MHz.

Figure 4: Control Bus Switch

Upon reset, the default state of the control bus direction switch is to redirect the control bus interface to the ADD2 PROM. At this stage, the CH7308B observes the Control bus traffic. If the observing logic sees a control bus transaction destined for the internal registers (device address 70h or 72h), it disables the PROM output pairs, and switches to internal registers. In the condition that traffic is to the internal registers, an opcode command is used to set the redirection circuitry to the appropriate destination (ADD2 PROM or DDC). Redirecting the traffic to internal registers while at the stage of traffic to DDC occurs on observing a STOP after a START on the control bus.

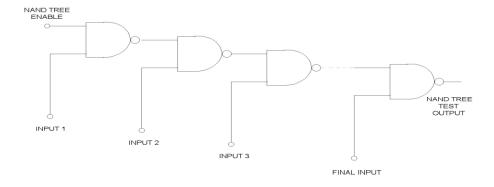

#### 2.7.1 NAND Tree Test

CH7308B provides "NAND TREE Testing" to verify IO cell functions at the PC board level. This test will check the interconnect between the chip's I/O and the printed circuit board for faults (soldering, bent leads, open printed circuit board traces, etc.). The NAND tree test is a simple serial logic which turns all IO cell signals to input mode, connects all inputs with NAND gates as shown in Figure 6 and switches each signal to high or low according to the sequence in **Table 7**. The test results are then passed out of pin 48 (SDVO\_STALL-). This test is enabled when the BSCAN pin (pin 63) is set to "1".

**Figure 5: NAND Tree Connection**

**Testing Sequence**

Set BSCAN = 1; (internal weak pull low)

Set all signals listed in **Table 7** to 1.

Set all signals listed in **Table 7** to 0, toggle one by one with a suggested time period of 200 ns.

Pin 48 will change its value each time an input value changed.

**Table 7: Signal Order in the NAND Tree Testing**

| Order | Pin Name     | LQFP Pin |

|-------|--------------|----------|

| 1     | ENABKL       | 1        |

| 2     | ENAVDD       | 2        |

| 3     | RESET*       | 4        |

| 4     | AS           | 5        |

| 5     | SPC          | 6        |

| 6     | SPD          | 7        |

| 7     | SD_PROM      | 9        |

| 8     | SC_PROM      | 10       |

| 9     | SD_DDC       | 11       |

| 10    | SC_DDC       | 12       |

| 11    | XI           | 14       |

| 12    | XO           | 15       |

| 13    | LL2C         | 17       |

| 14    | LL2C*        | 18       |

| 15    | LDC7         | 20       |

| 16    | LDC7*        | 21       |

| 17    | LDC6         | 23       |

| 18    | LDC6*        | 24       |

| 19    | LDC5         | 26       |

| 20    | LDC5*        | 27       |

| 21    | LDC4         | 29       |

| 22    | LDC4*        | 30       |

| 23    | LDC3         | 33       |

| 24    | LDC3*        | 34       |

| 25    | LL1C         | 36       |

| 26    | LL1C*        | 37       |

| 27    | LDC2         | 39       |

| 28    | LDC2*        | 40       |

| 29    | LDC1         | 42       |

| 30    | LDC1*        | 43       |

| 31    | LDC0         | 45       |

| 32    | LDC0*        | 46       |

| 33    | SDVOB_STALL+ | 47       |

| 34    | SDVOB_STALL- | 48       |

## 3.0 Register Control

The CH7308B is controlled by using Intel opcodes through the serial port. The serial bus uses only the SPC clock to latch data into registers, and does not use any internally generated clocks so that the device can be written to in all power down modes. The device will retain all register values during power down modes.

For details regarding Intel<sup>®</sup> SDVO opcodes, please contact Intel<sup>®</sup>.

# 4.0 Electrical Specifications

### 4.1 Absolute Maximum Ratings

| Symbol            | Description                                                                     | Min          | Тур        | Max        | Units |

|-------------------|---------------------------------------------------------------------------------|--------------|------------|------------|-------|

|                   | All 2.5V power supplies relative to GND All 3.3V power supplies relative to GND | -0.5<br>-0.5 |            | 3.0<br>5.0 | V     |

| T <sub>SC</sub>   | Analog output short circuit duration                                            |              | Indefinite |            | Sec   |

| T <sub>AMB</sub>  | Ambient operating temperature                                                   | -40          |            | 85         | °C    |

| T <sub>STOR</sub> | Storage temperature                                                             | -65          |            | 150        | °C    |

| T <sub>J</sub>    | Junction temperature                                                            |              |            | 150        | °C    |

| T <sub>VPS1</sub> | Vapor phase soldering (5 seconds)                                               |              |            | 260        | °C    |

| T <sub>VPS2</sub> | Vapor phase soldering (11 seconds)                                              |              |            | 245        | °C    |

| T <sub>VPS3</sub> | Vapor phase soldering (60 seconds)                                              |              |            | 225        | °C    |

#### Note:

- Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device.

These are stress ratings only. Functional operation of the device at these or any other conditions above those

indicated under the normal operating condition of this specification is not recommended. Exposure to absolute

maximum rating conditions for extended periods may affect reliability. The temperature requirements of vapor

phase soldering apply to all standard and lead free parts.

- 2) The device is fabricated using high-performance CMOS technology. It should be handled as an ESD sensitive device. Voltage on any signal pin that exceeds the power supply voltages by more than ± 0.5V can induce a destructive latchup.

#### 4.2 Recommended Operating Conditions

| Symbol   | Description                     | Min   | Тур | Max   | Units |

|----------|---------------------------------|-------|-----|-------|-------|

| AVDD     | Analog Power Supply Voltage     | 2.375 | 2.5 | 2.625 | V     |

| AVDD_PLL | Analog PLL Power Supply Voltage | 3.100 | 3.3 | 3.500 | V     |

| DVDD     | Digital Power Supply Voltage    | 2.375 | 2.5 | 2.625 | V     |

| LVDD     | LVDS Power Supply               | 3.100 | 3.3 | 3.500 | V     |

| VDD33    | Generic for all 3.3V supplies   | 3.100 | 3.3 | 3.500 | V     |

| VDD25    | Generic for all 2.5V supplies   | 2.375 | 2.5 | 2.625 | V     |

|          | Ambient operating temperature   | -40   |     | 85    | °C    |

## **4.3** Electrical Characteristics

(Operating Conditions:  $T_A = -40$  °C - +85 °C, VDD25 =2.5V  $\pm$  5%, VDD33=3.3V  $\pm$  5%)

| Symbol               | Description                                                        | Min | Тур | Max | Units |

|----------------------|--------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>VDD25</sub>   | Total VDD25 supply current (2.5V supplies) (no upscaler)           |     | 170 | 200 | mA    |

| I <sub>VDD33</sub>   | Total VDD33 supply current (3.3V supply) (no upscaler)             |     | 70  | 85  | mA    |

| I <sub>VDD25UP</sub> | Total VDD25 supply current (2.5V supplies) (with upscaler enabled) |     | 270 | 340 | mA    |

| I <sub>VDD33UP</sub> | Total VDD33 supply current (3.3V supply) (with upscaler enabled)   |     | 70  | 85  | mA    |

| I <sub>PD</sub>      | Total Power Down Current (all supplies)                            |     | 30  |     | uA    |

# **4.4 DC Specifications**

| Symbol                             | Description Test Condition Min                                            |                                                                                  | Тур     | Max | Unit                           |   |

|------------------------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------|---------|-----|--------------------------------|---|

| $V_{RX\text{-DIFFp-p}}$            | SDVO Receiver Differential<br>Input Peak to Peak Voltage                  | $V_{RX-DIFFp-p} = 2 *$ $ V_{RX-D+} - V_{RX-D-} $                                 | 0.175   |     | 1.200                          | V |

| $Z_{\text{RX-DIFF-DC}}$            | SDVO Receiver DC<br>Differential Input Impedance                          |                                                                                  | 80      | 100 | 120                            | Ω |

| Z <sub>RX-COM-DC</sub>             | SDVO Receiver DC Common<br>Mode Input Impedance                           |                                                                                  | 40      | 50  | 60                             | Ω |

| Z <sub>RX-COM-</sub> INITIAL-DC    | SDVO Receiver Initial DC<br>Common Mode Input<br>Impedance                | Impedance allowed when receiver terminations are first turned on                 | 5       | 50  | 60                             | Ω |

| V <sub>STALL-DIFFp-p</sub>         | SDVO Stall Differential Output<br>Peak to Peak Voltage                    | V <sub>STALL-DIFFp-p</sub> = 2 *   V <sub>STALL-D+</sub> - V <sub>STALL-D-</sub> | 0.8     |     | 1.200                          | V |

| V <sub>SDOL</sub> <sup>1</sup>     | SPD (serial port data) Output<br>Low Voltage                              | I <sub>OL</sub> = 2.0 mA                                                         |         |     | 0.4                            | V |

| V <sub>SPIH</sub> <sup>2</sup>     | Serial Port (SPC, SPD) Input<br>High Voltage                              |                                                                                  | 2.0     |     | VDD25+<br>0.5                  | V |

| V <sub>SPIL</sub> <sup>2</sup>     | Serial Port (SPC, SPD) Input<br>Low Voltage                               |                                                                                  | GND-0.5 |     | 0.4                            | V |

| $V_{HYS}$                          | Hysteresis of Serial Port Inputs                                          |                                                                                  | 0.25    |     |                                | V |

| $V_{DDCIH}$                        | DDC Serial Port<br>Input High Voltage                                     |                                                                                  | 4.0     |     | VDD5 +<br>0.5                  | V |

| $V_{DDCIL}$                        | DDC Serial Port<br>Input Low Voltage                                      |                                                                                  | GND-0.5 |     | 0.4                            | V |

| $V_{PROMIH}$                       | PROM Serial Port<br>Input High Voltage                                    |                                                                                  | 4.0     |     | VDD5 +<br>0.5                  | V |

| $V_{PROMIL}$                       | PROM Serial Port<br>Input Low Voltage                                     |                                                                                  | GND-0.5 |     | 0.4                            | V |

| V <sub>SD_DDCOL</sub> <sup>3</sup> | SPD (serial port data) Output<br>Low Voltage from SD_DDC<br>(or SD_EPROM) | Input is V <sub>INL</sub> at SD_DDC or SD_EPROM.                                 |         |     | 0.9*V <sub>INL</sub> +<br>0.25 | V |

|                                    |                                                                           | $4.0$ K $\Omega$ pullup to $2.5$ V.                                              |         |     |                                |   |

| Symbol                            | Description                             | Test Condition                            | Min     | Тур | Max                              | Unit |

|-----------------------------------|-----------------------------------------|-------------------------------------------|---------|-----|----------------------------------|------|

| V <sub>DDCOL</sub> <sup>4</sup>   | SC_DDC and SD_DDC<br>Output Low Voltage | Input is V <sub>INL</sub> at SPC and SPD. |         |     | 0.933*V <sub>INL</sub><br>+ 0.35 | V    |

|                                   |                                         | $5.6$ K $\Omega$ pullup to $5.0$ V.       |         |     |                                  |      |

| V <sub>EPROMOL</sub> <sup>5</sup> | SC_EPROM and<br>SD_EPROM Output Low     | Input is V <sub>INL</sub> at SPC and SPD. |         |     | 0.933*V <sub>INL</sub><br>+ 0.35 | V    |

|                                   | Voltage                                 | $5.6$ K $\Omega$ pullup to $5.0$ V.       |         |     |                                  |      |

| V <sub>ASIH</sub>                 | AS<br>Input High Voltage                |                                           | 2.0     |     | VDD25 +<br>0.5                   | V    |

| V <sub>ASIL</sub>                 | AS<br>Input Low Voltage                 |                                           | GND-0.5 |     | 0.5                              | V    |

| I <sub>ASPU</sub>                 | AS Pull Up Current                      | V <sub>IN</sub> = 0V                      | 10      |     | 40                               | uA   |

| V <sub>RESETIH</sub>              | RESET*<br>Input High Voltage            |                                           | 2.7     |     | VDD33 +<br>0.5                   | V    |

| V <sub>RESETIL</sub>              | RESET*<br>Input Low Voltage             |                                           | GND-0.5 |     | 0.5                              | V    |

| I <sub>RESETPU</sub>              | RESET* Pull Up Current                  | V <sub>IN</sub> = 0V                      | 10      |     | 40                               | uA   |

| V <sub>TESTIH</sub>               | BSCAN<br>Input High Voltage             |                                           | 2.0     |     | VDD25 +<br>0.5                   | V    |

| V <sub>TESTIL</sub>               | BSCAN<br>Input Low Voltage              |                                           | GND-0.5 |     | 0.5                              | V    |

| I <sub>TESTPD</sub>               | BSCAN<br>Pull Down Current              | V <sub>IN</sub> = 2.5V                    | 10      |     | 40                               | uA   |

| $V_{XIIH}$                        | XI (for clock input) Input High Voltage |                                           | 2.6     |     | VDD33 +<br>0.5                   | V    |

| V <sub>XIIL</sub>                 | XI (for clock input) Input Low Voltage  |                                           | GND-0.5 |     | 0.6                              | V    |

| V <sub>MISCAOH</sub>              | ENAVDD, ENABKL<br>Output High Voltage   | I <sub>OH</sub> = -6.5mA                  | VDD-0.2 |     |                                  | V    |

| V <sub>MISCAOL</sub>              | ENAVDD, ENABKL<br>Output Low Voltage    | I <sub>OL</sub> = 9.0mA                   |         |     | 0.2                              | V    |

#### Notes:

- $V_{\text{SDOL}}$  is the SPD output low voltage when transmitting from internal registers, not from DDC or EEPROM.

- V<sub>SPIL</sub> and V<sub>SPIL</sub> are the serial port (SPC and SPD) input low voltage when transmitting to internal registers. Separate requirements may exist for transmission to the DDC and EEPROM.

- V<sub>SD\_DDCOL</sub> is the output low voltage at the SPD pin when the voltage at SD\_DDC or SD\_EPROM is V<sub>INL</sub>. Maximum output voltage has been calculated with a worst case pullup of  $4.0k\Omega$  to 2.5V on SPD.

- V<sub>DDCOL</sub> is the output low voltage at the SC\_DDC and SD\_DDC pins when the voltage at SPC and SPD is V<sub>INL</sub>. Maximum output voltage has been calculated with 5.6k pullup to 3.3V on SC\_DDC and SD\_DDC.

V<sub>EPROMOL</sub> is the output low voltage at the SC\_EPROM and SD\_EPROM pins when the voltage at SPC and SPD is V<sub>INL</sub>.

- Maximum output voltage has been calculated with 5.6kΩ pullup to 5V on SC\_EPROM and SD\_EPROM.

# 4.5 AC Specifications

| Symbol                     | Description                                                                        | Test Condition                                     | Min              | Тур                          | Max                | Unit           |

|----------------------------|------------------------------------------------------------------------------------|----------------------------------------------------|------------------|------------------------------|--------------------|----------------|

| UI <sub>DATA</sub>         | SDVO Receiver Unit Interval for Data Channels                                      |                                                    | Тур.<br>– 300ppm | 1/[Data<br>Transfer<br>Rate] | Тур.<br>+ 300ppm   | ps             |

| f <sub>SDVOB_CLK</sub>     | SDVO CLK Input Frequency                                                           |                                                    | 100              |                              | 200                | MHz            |

| f <sub>PIXEL</sub>         | SDVO Receiver Pixel frequency                                                      |                                                    | 25               |                              | 200                | MHz            |

| f <sub>SYMBOL</sub>        | SDVO Receiver Symbol frequency                                                     |                                                    | 1                |                              | 2                  | GHz            |

| t <sub>RX-EYE</sub>        | SDVO Receiver Minimum Eye<br>Width                                                 |                                                    | 0.4              |                              |                    | UI             |

| t <sub>RX-EYE-JITTER</sub> | SDVO Receiver Max. time<br>between jitter median and<br>max. deviation from median |                                                    |                  |                              | 0.3                | UI             |

| V <sub>RX-CM-ACp</sub>     | SDVO Receiver AC Peak<br>Common Mode Input Voltage                                 |                                                    |                  |                              | 150                | mV             |

| RL <sub>RX-DIFF</sub>      | Differential Return Loss                                                           | 50MHz – 1.25GHz                                    | 10               |                              |                    | dB             |

| RL <sub>RX-CM</sub>        | Common Mode Return Loss                                                            | 50MHz – 1.25GHz                                    | 6                |                              |                    | dB             |

| t <sub>SKEW</sub>          | SDVO Receiver Total Lane to<br>Lane Skew of Inputs                                 | Across all lanes                                   |                  |                              | 2                  | ns             |

| C <sub>XI</sub>            | XI<br>Input Capacitance                                                            |                                                    |                  |                              | 15                 | pF             |

| f <sub>TOL XI</sub>        | XI Input Clock Frequency Tolerance (when crystal not used)                         |                                                    | -1000            |                              | +1000              | ppm            |

| DC <sub>XI</sub>           | XI<br>Input Clock Duty Cycle (when<br>crystal not used)                            |                                                    | 45               |                              | 55                 | %              |

| $T_{SPR}$                  | SPC, SPD Rise Time<br>(20% - 80%)                                                  | Standard mode 100k Fast mode 400k 1M running speed |                  |                              | 1000<br>300<br>150 | ns<br>ns<br>ns |

| T <sub>SPF</sub>           | SPC, SPD Fall Time<br>(20% - 80%)                                                  | Standard mode 100k Fast mode 400k 1M running speed |                  |                              | 300<br>300<br>150  | ns<br>ns       |

| T <sub>PROMR</sub>         | SC_PROM, SD_PROM Rise<br>Time (20% - 80%)                                          | Fast mode 400K                                     |                  |                              | 300                | ns             |

| $T_{PROMF}$                | SC_PROM, SD_PROM Rise<br>Time (20% - 80%)                                          | Fast mode 400K                                     |                  |                              | 300                | ns             |

| T <sub>DDCR</sub>          | SC_DDC, SD_DDC Rise<br>Time (20% - 80%)                                            | Standard mode 100k                                 |                  |                              | 1000               | ns             |

| $T_{DDCF}$                 | SC_DDC, SD_DDC Fall<br>Time (20% - 80%)                                            | Standard mode 100k                                 |                  |                              | 300                | ns             |

| Symbol                    | Description                             | Test Condition     | Min | Тур | Max | Unit |

|---------------------------|-----------------------------------------|--------------------|-----|-----|-----|------|

| T <sub>DDCR-DELAY</sub> 1 | SC_DDC, SD_DDC Rise<br>Time Delay (50%) | Standard mode 100k |     | 0   |     | ns   |

| T <sub>DDCF-DELAY</sub> 1 | SC_DDC, SD_DDC Fall Time Delay (50%)    | Standard mode 100k |     | 3   |     | ns   |

#### Notes:

1. Refers to the figure below, the delay refers to the time pass through the internal switches.

Figure 6: DDC – SPC/SPD Circuit

17

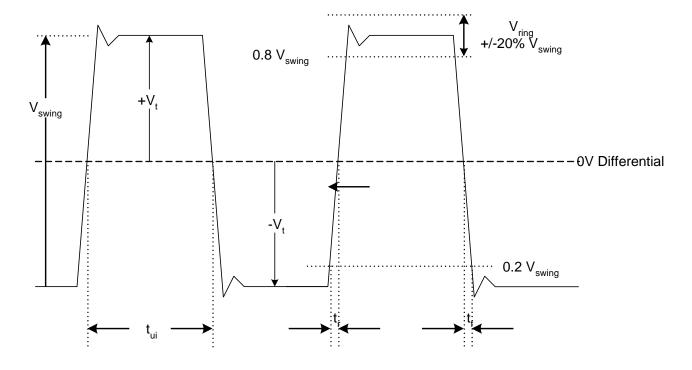

# 4.6 LVDS Output Specifications

The LVDS specifications meet the requirements of ANSI/EIA/TIA-644. Refer to Figure 7 for definitions of parameters.

| Symbol                                | Description                                                                | Test Condition                                                              | Min   | Тур   | Max                        | Unit     |

|---------------------------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------|-------|----------------------------|----------|

| $ V_t $                               | Steady State Differential Output Magnitude for logic 1                     | $100\Omega$ differential load                                               | 247   |       | 453                        | mV       |

| V <sub>t</sub> *                      | Steady State Differential Output Magnitude for logic 0                     | $100\Omega$ differential load                                               | 247   |       | 453                        | mV       |

| V <sub>t</sub>   -   V <sub>t</sub> * | Steady State Magnitude of<br>Differential between Logic 1<br>and 0 Outputs | 100Ω differential load                                                      |       |       | 50                         | mV       |

| Vos                                   | Steady State Magnitude of<br>Offset Voltage for Logic 1                    | Measured at centertap of two $50\Omega$ resistors connected between outputs | 1.125 | 1.125 |                            | ٧        |

| Vos*                                  | Steady State Magnitude of<br>Offset Voltage for Logic 0                    | Measured at centertap of two $50\Omega$ resistors connected between outputs | 1.125 |       | 1.375                      | >        |

| Vos - Vos*                            | Steady State Magnitude of<br>Offset Difference between<br>Logic States     | Measured at centertap of two 50Ω resistors connected between outputs        |       |       | 50                         | mV       |

| f <sub>LLC</sub> <sup>1</sup>         | LVDS Output Clock<br>Frequency                                             |                                                                             | 25    | 108   |                            | MHz      |

| t <sub>UI</sub> <sup>1</sup>          | LVDS data unit time interval                                               | 25MHz <<br>f <sub>LLC</sub> <108MHz                                         | 1.3   |       | 5.7                        | ns       |

| tr                                    | LVDS data rise time  t <sub>UI</sub> > 5ns  1.3ns <t<sub>UI&lt;5ns</t<sub> | 100Ω and 5pF<br>differential load<br>20%->80% Vswing                        |       |       | 0.3*t <sub>UI</sub><br>1.5 | ns<br>ns |

| t <sub>f</sub>                        | LVDS data fall time  T <sub>UI</sub> > 5ns  1.3ns <t<sub>UI&lt;5ns</t<sub> | 100Ω and 5pF<br>differential load<br>80%->20% Vswing                        |       |       | 0.3*t <sub>UI</sub><br>1.5 | ns<br>ns |

| Vring                                 | Voltage ringing after transition                                           | 100Ω and 5pF<br>differential load                                           |       |       | 20%<br>Vswing              |          |

Note 1: Corresponds to maximum pixel rate  $f_{XCLK}$  for single channel operation. Dual channel operation is required for pixel rates greater than 108MHz.

## 4.7 LVDS Output Timing

**Figure 7: AC Timing for LVDS Outputs**

**Table 8: AC Timing for LVDS Outputs**

| Symbol                                   | Parameter                                                        | Min Typ Max                           |  |  |  |  |

|------------------------------------------|------------------------------------------------------------------|---------------------------------------|--|--|--|--|

| V <sub>t</sub>                           | Steady State Differential Output Magnitude                       | see section 4.6                       |  |  |  |  |

| V <sub>SWING</sub>                       | Voltage Difference between the two Steady State Values of Output | V <sub>t</sub>   +   V <sub>t</sub> * |  |  |  |  |

| t <sub>Ui</sub>                          | Unit time interval                                               | see section 4.6                       |  |  |  |  |

| t <sub>r</sub>                           | Rise time                                                        | see section 4.6                       |  |  |  |  |

| t <sub>f</sub> Fall time see section 4.6 |                                                                  |                                       |  |  |  |  |

# 5.0 Package Dimensions

**Table of Dimensions**

| No. of   | Leads  |    | SYMBOL |      |      |      |      |      |      |      |            |

|----------|--------|----|--------|------|------|------|------|------|------|------|------------|

| 64 (10 X | 10 mm) | A  | В      | C    | D    | E    | F    | G    | H    | I    | J          |

| Milli-   | MIN    | 12 | 10     | 0.50 | 0.17 | 1.35 | 0.05 | 1.00 | 0.45 | 0.09 | <b>0</b> ° |

| meters   | MAX    | 12 | 10     | 0.50 | 0.27 | 1.45 | 0.15 | 1.00 | 0.75 | 0.20 | <b>7</b> ° |

Figure 8: 64 Pin LQFP Package

# 6.0 Revision History

**Table 9: Revisions**

| Rev. # | Date       | Section              | Description                                                                                |

|--------|------------|----------------------|--------------------------------------------------------------------------------------------|

| 1.0    | 11/23/04   | All                  | Version 1.0                                                                                |

| 1.1    | 12/20/04   | 2.2                  | Updated panel-fitting scaler information.                                                  |

|        |            | 4.1                  | Updated T <sub>VPS</sub> – Vapor phase soldering information.                              |

| 1.2    | 1/05/05    | Ordering Information | Lead Free tape and reel part number added.                                                 |

|        |            | 4.1                  | Note 1 updated.                                                                            |

| 1.3    | 1/27/05    | 4.4                  | Added V <sub>MISCAOH</sub> and V <sub>MISCAOL</sub> DC Specification data.                 |

| 1.4    | 2/2/05     | 1.1, 1.2             | Added TEST pin (pin50) and description.                                                    |

|        |            | 2.5                  | Updated Figure 4 and added reference to TB49.                                              |

|        |            | Table 8              | Corrected note to which section to refer to                                                |

|        |            | 2.2                  | Added Wide SXGA+, 1680 x 1050, to Table 5                                                  |

| 1.5    | 2/7/05     | 1.2                  | Change descriptions for pin 11, 12, 14, 15, 60, 61                                         |

|        |            | 2.6                  | Replace "PANEN set to 1" with "SetActiveOutput is called".                                 |

|        |            | 4.4, 4.5, 4.6, 4.7   | Change spec. values.                                                                       |

|        |            | 4.4                  | Changed conditions and value for V <sub>DDCOL</sub>                                        |

|        |            | 4.5                  | Changed definition of f <sub>PIXEL</sub> and value for RL <sub>RX-DIFF</sub>               |

|        |            | 4.6                  | Changed parameters $f_{LLC}$ , $t_{UI}$ , $t_R$ , $t_F$ .                                  |

| 1.61   | 8/8/05     | All                  | Changed the maximum pixel rate to 140MP/s                                                  |

|        |            | Features, 2.2        | Changed the maximum upscale resolution to 1600x900                                         |

|        |            | Table 2              | Updated the table to reflect the new maximum pixel rate of 140MP/s                         |

|        |            | 2.2                  | Removed panel sizes no longer supported.                                                   |

|        |            | Ordering Information | Added a footnote stating the current revision of the CH7308A is                            |

|        |            |                      | revision D and marked as XUD                                                               |

|        |            | General Description  | The last sentence of the 2 <sup>nd</sup> paragraph was edited to avoid confusion in        |

|        |            |                      | what is the maximum pixel rate per channel.                                                |

| 1.7    | 10/12/05   | Ordering information | Added Green parts into the ordering information.                                           |

|        |            | 4.4, 4.5             | Added serial interface AC and DC Electrical Specification information.                     |

| 1.8    | 12/20/05   | General Description  | Sentence mentioning supported pixel rates for dual panel LVDS panels (100MP/s to 140MP/s). |

|        |            | 3.0 Register Control | Changed the first sentence to clarify that the CH7308A is controlled by                    |

|        |            |                      | use of Intel Opcodes instead of register reads/writes.                                     |

| 2.0    | 1/11/2006  | All text and figures | Modified the datasheet to include the CH7308B.                                             |

|        |            | Features and General | Added CH7308B related information in the features section and the                          |

|        |            | Description          | second paragraph of the General Description section.                                       |

|        |            | Ordering Information | Added CH7308B ordering information.                                                        |

| 2.1    | 3/13/2008  | Features             | Added 1600x1200 and 1920x1200 reduced blanking resolution                                  |

|        |            |                      | support.                                                                                   |

|        |            | Pin Description      | Pin 63 and Pin 64 are changed to "open"                                                    |

|        |            | Table 5              | Added 1920x1200 resolution reduced blanking to Table 5.                                    |

| 2.2    | 8/5/2008   | Figure 3             | Added LVDS Clock and LVDS Data to Figure 3.                                                |

| 2.3    | 9/22/2008  | 4.4                  | Updated DC Specifications.                                                                 |

| 2.4    | 12/2/2008  | 4.2, 4.3.            | Updated operating temperature.                                                             |

| 2.41   | 3/30/2008  | 1.2 Table 1          | Updated description for Pin 63.                                                            |

| 3.0    | 05/10/2011 | 4.1, 4.2             | Update Ambient operating temperature to -40°C to +85°C.                                    |

|        |            | All                  | Remove CH7308A                                                                             |

201-0000-064 Rev. 3.0, 05/11/2011 21

#### **Disclaimer**

This document provides technical information for the user. Chrontel reserves the right to make changes at any time without notice to improve and supply the best possible product and is not responsible and does not assume any liability for misapplication or use outside the limits specified in this document. We provide no warranty for the use of our products and assume no liability for errors contained in this document. The customer should make sure that they have the most recent data sheet version. Customers should take appropriate action to ensure their use of the products does not infringe upon any patents. Chrontel, Inc. respects valid patent rights of third parties and does not infringe upon or assist others to infringe upon such rights.

Chrontel PRODUCTS ARE NOT AUTHORIZED FOR AND SHOULD NOT BE USED WITHIN LIFE SUPPORT SYSTEMS OR NUCLEAR FACILITY APPLICATIONS WITHOUT THE SPECIFIC WRITTEN CONSENT OF Chrontel. Life support systems are those intended to support or sustain life and whose failure to perform when used as directed can reasonably expect to result in personal injury or death.

| ORDERING INFORMATION |                                   |                |                |  |  |  |  |  |

|----------------------|-----------------------------------|----------------|----------------|--|--|--|--|--|

| Part Number          | Package Type                      | Number of Pins | Voltage Supply |  |  |  |  |  |

| CH7308B-TF           | Lead Free - LQFP                  | 64             | 2.5V, 3.3V     |  |  |  |  |  |

| CH7308B-TF-TR        | Lead Free - Tape<br>and Reel LQFP | 64             | 2.5V, 3.3V     |  |  |  |  |  |

# **Chrontel**

2210 O'Toole Avenue, Suite 100, San Jose, CA 95131-1326 Tel: (408) 383-9328 Fax: (408) 383-9338

www.chrontel.com E-mail: sales@chrontel.com

©2009 Chrontel, Inc. All Rights Reserved. Printed in the U.S.A.