# The Leader in High Temperature Semiconductor Solutions

# CHT-VEGA-DATASHEET

Version: 2.4

# High-Temperature, Low Dropout, Adjustable Voltage Regulator +1.2V to +3.3V / 500mA

## **General description**

The CHT-VEGA is a high-temperature, high-reliability, 500mA adjustable linear voltage regulator suitable to generate from a standard +5V ±10% source any regulated voltage in the range +1.2V to +3.3V. Its typical operation junction temperature ranges from -55°C to +225°C and can possibly go outside that range with some derating of the performance. The regulator is self-protected with a built-in over-current limitation and a thermal protection, the later becoming effective in the range 250°C to 300°C. CHT-VEGA brings unique benefits in applications where the ambient or operating temperature is high and above the temperature supported by traditional semiconductors, or in applications that run in standard 125°C or 150°C, possibly 175°C but that require extended reliability: CHT-VEGA brings at least an order of magnitude in lifetime compared to traditional silicon solutions. It allows as well accelerated aging of the systems for qualification purposes as the device can support extreme temperatures.

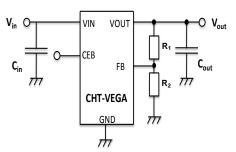

The circuit is stable throughout the whole temperature range and only requires an external output capacitor and a 2-resistor bridge for feedback. The IC features a chipenable (CE active low) input signal allowing placing the circuit in low-power, disable mode. The output voltage is adjustable by the external resistive feedback.

The CHT-VEGA is a one-die solution, available in a tiny ceramic package TDFP-16 for applications where small PCB footprint is critical. The TDFP package is an SMD solution with leads, available by default in 16-pin.

#### **Features**

- Junction operating temperature from -55°C to 225°C

- Input voltage from 4.5V to 5.5V

- Output voltage: from 1.2V to 3.3V

- Output voltage total accuracy: ±5%<sup>1</sup>

- Output current: 500mA max

- Line regulation: -0.2% typ

- Load regulation: -2%/A typ

- C<sub>out</sub>: 1 to 10 μF ceramic low ESR

- Input ripple rejection: 67dB typ (@ 100Hz)

- Quiescent current (no load, Chip Enable active, 225°C): 1 mA typ.

- Stand-by current (no load, Chip Enable inactive, 225°C): 10 µA typ.

- Thermal shutdown: Active in the range 250°C to 300°C

- Current limitation: 1.15A (typ)

- · Latch-up free

- Available in TDFP16 (other packages: contact CISSOID)

- Validated at 225°C for 5000 hours (and still on-going)

#### **Applications**

Regulated power supply in down-hole, aerospace and industrial systems.

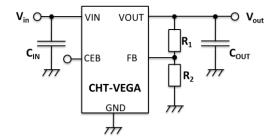

# **Typical Application**

<sup>&</sup>lt;sup>1</sup> Excluding accuracy of external components but including initial accuracy variation, temperature variation, line and load regulation variations

PUBLIC **29-Aug-18 Doc. DS-110961 V2.4 WWW.CISSOID.COM** 1 of 10

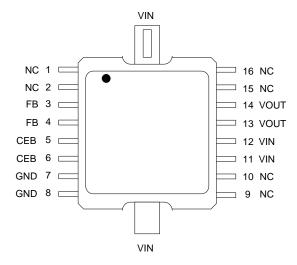

## **Pinout**

| Pin # | Pin Name | Pin Description                                                                                                                                           |

|-------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

| 2     | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

| 3     | FB       | Input pin; feedback pin to be connected via a resistor network to Vout (cfr Typical application diagram on page 1)                                        |

| 4     | FB       | Input pin; feedback pin to be connected via a resistor network to Vout (cfr Typical application diagram on page 1)                                        |

| 5     | CEB      | Input pin; Chip Enable pin; when connected to GND, CHT-VEGA is active; when connected to VIN, VOUT is tied to GND and CHT-VEGA enters in a low-power mode |

| 6     | CEB      | Input pin; Chip Enable pin; when connected to GND, CHT-VEGA is active; when connected to VIN, VOUT is tied to GND and CHT-VEGA enters in a low-power mode |

| 7     | GND      | Negative power supply                                                                                                                                     |

| 8     | GND      | Negative power supply                                                                                                                                     |

| 9     | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

| 10    | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

| 11    | VIN      | Positive power supply                                                                                                                                     |

| 12    | VIN      | Positive power supply                                                                                                                                     |

| 13    | VOUT     | Output voltage                                                                                                                                            |

| 14    | VOUT     | Output voltage                                                                                                                                            |

| 15    | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

| 16    | NC       | Not connected internally; can be left floating or connected to any net to ease PCB routing                                                                |

The 2 vertical large leads are internally connected to VIN and are also connected to the package heat sink. Those 2 vertical pins MUST be connected at PCB level to VIN

PUBLIC

29-Aug-18

Doc. DS-110961 V2.4

WWW.CISSOID.COM

2 of 10

# CISSOID

#### **CHT-VEGA DATASHEET**

# **Absolute Maximum Ratings**

# **Operating Conditions**

Supply Voltage Vin to GND -0.5 to 6V Voltage on CEB and FB max Vin Peak output current Internally limited Junction Temperature (Tj) 250°C

Supply Voltage Vin to GND: 4.5V to 5.5V Junction temperature -55°C to +225°C Continuous current 0 to 500 mA

**ESD Rating**

Human Body Model Class1B

**CAUTION:** Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Frequent or extended exposure to absolute maximum rating conditions or above may affect device reliability. Permanent uses of the device in short-circuit state or in over-temperature state may affect long term reliability of the device.

PUBLIC

29-Aug-18

Doc. DS-110961 V2.4

WWW.CISSOID.COM

3 of 10

# **Electrical Characteristics**

Unless otherwise stated,  $T_j = 25^{\circ}C$ ,  $C_{in} = 1 \mu F$ ,  $C_{out} = 1 \mu F$ . **Bold** figures point out values valid over the whole temperature range ( $T_j = -55^{\circ}C$  to  $+225^{\circ}C$ ).

| Parameter                                | Symbol              | Condition                                                                                           | Min         | Тур             | Max         | Unit     |

|------------------------------------------|---------------------|-----------------------------------------------------------------------------------------------------|-------------|-----------------|-------------|----------|

| Input Voltage                            | V <sub>in</sub>     |                                                                                                     | 4.5         | 5               | 5.5         | V        |

| Output voltage range                     | $V_{out}$           |                                                                                                     | 1.1         |                 | 3.6         | V        |

| Output current                           | l <sub>out</sub>    |                                                                                                     | 0           |                 | 500         | mA       |

| Output voltage total accuracy            |                     | Vin =[4.5-5.5]V<br>lout = [0 500]mA                                                                 | Vout<br>-5% |                 | Vout<br>+5% | V        |

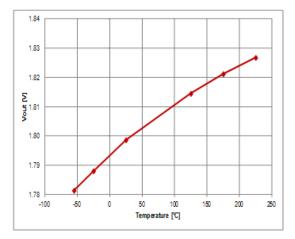

| Output voltage temperature drift         |                     | Vin= 5V; Vout = 1.8V<br>lout = 0mA<br>$T_j = [25^{\circ}C - 225^{\circ}C]$                          |             | +2.5            |             | %        |

| Output voltage line regulation           |                     | Vin =[4.5-5.5]V; Vout = 1.8V<br>lout= 0mA                                                           |             | -0.2            |             | %        |

| Output voltage load regulation           |                     | Vin =5V ; Vout = 1.8V<br>lout = [0 500]mA                                                           |             | -1 <sup>1</sup> |             | %        |

| Quiescent current <sup>2</sup>           | Iq                  | Vin= 5V ; Vout = 1.8V<br>lout = 0 mA                                                                | 0.8         | 1               | 1.4         | mA       |

| Standby current <sup>2</sup>             | I <sub>stdby</sub>  | Vin = 5V ; Vout = 1.8V<br>lout = 0 mA ; T <sub>j</sub> = 25°C<br>CEB = 5V<br>Vin = 5V ; Vout = 1.8V |             |                 | 100         | nA       |

|                                          |                     | lout = 0 mA; $T_j$ = 225°C<br>CEB = 5V                                                              |             |                 | 20          | μΑ       |

| Response to Line Transient               |                     | Vin from 4.5V to 5.5V (1V/µs)<br>Vout = 1.8V; lout = 0mA                                            |             | +2              |             | %        |

| Troopenies to Line Translett             |                     | Vin from 5.5V to 4.5V (1V/µs)<br>Vout = 1.8V;lout = 0mA                                             |             | -2              |             | %        |

| Response to Load Transient               |                     | Vin = 5V; Vout = 1.8V<br>lout from 0mA to 500 mA<br>(10mA/µs)                                       |             | -3              |             | %        |

| ·                                        |                     | Vin = 5V; Vout = 1.8V<br>lout from 500 mA to 0 mA<br>(10mA/µs)                                      |             | +3              |             | %        |

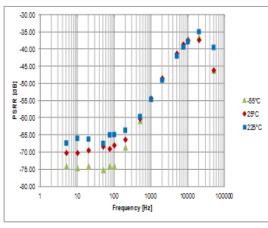

| Power Supply Rejection Ratio             | PSRR                | 100Hz                                                                                               |             | 67              |             | dB       |

| ( Vin=5V, Vout=1.8V, Iout=0mA, ESR<0.2Ω) |                     | 1 KHz                                                                                               |             | 55              |             | dB       |

| Average short-circuit current            | Isc                 | Vin = 5V; Vout = 0V                                                                                 |             | 1.15            |             | Α        |

|                                          |                     | Vin = 5.5V; Vout = 1.2V                                                                             |             | 1.6             |             | Α        |

| Over current detection threshold         | lth                 | Vin = 4.5V; Vout = 3.3V                                                                             |             | 0.88            |             | Α        |

| FB input current                         | I <sub>FB</sub>     | V <sub>FB</sub> = 0.9V +/- 10%                                                                      |             | 5               |             | nA       |

| CEB input current                        | I <sub>CEB</sub>    | Vin = 5V                                                                                            |             | 10              |             | nA       |

| CEB V <sub>IL</sub>                      | V <sub>IL CEB</sub> | Vin = 5V                                                                                            |             |                 | 2           | V        |

| CEB V <sub>IH</sub>                      | V <sub>IH CEB</sub> | Vin = 5V                                                                                            | 3           | 1               |             | V        |

| Over temperature protection threshold    | TH <sub>OTP</sub>   |                                                                                                     |             | 300             |             | °C       |

| Over temperature protection hysteresis   | Hyst <sub>OTP</sub> |                                                                                                     |             | 30              |             | °C       |

| Junction-to-case thermal resistance      | R <sub>OJC</sub>    |                                                                                                     |             | 11              |             | °C/<br>W |

**PUBLIC** 29-Aug-18 Doc. DS-110961 V2.4 WWW.CISSOID.COM 4 of 10

$<sup>^{\</sup>rm 1}$  Load regulation measurements must be done in a way to avoid self-heating effect  $^{\rm 2}$  Current through feedback resistances excluded

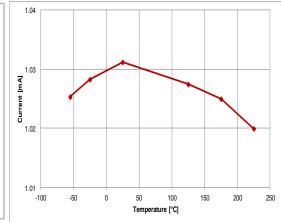

# **Typical Performance Characteristics**

1.83 1.82 •-55°C 7.80 A Out [7] - - 25°C --- 125°C ····· 175°C 225°C 1.78 5.2 5.3 5.4 5.5 4.5 4.6 4.7 4.8 4.9 5.1 Vin [V]

Figure 1: Output voltage temperature drift (Vin =5V, Vout =1.8V, lout = 0 mA)

Figure 2: Output voltage line regulation (lout = 0mA)

Figure 3: Input ripple rejection (PSRR)

(lout=0mA, Vin=5V, Vout=1.8V, Cout =  $1\mu F$ , ESR<0.2 $\Omega$ )

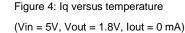

Figure 5: Response to load transient

(0A to 500 mA, 500 mA to 0A, Vin = 5V, Vout = 1.8V, Ta=  $25^{\circ}$ C) (1: Vout,2: lout)

Figure 6: Transition to/from disabled state

(Vin =5V, Vout = 1.8V, lout = 500 mA, Ta = 25°C) (1:Vout,2:CEB)

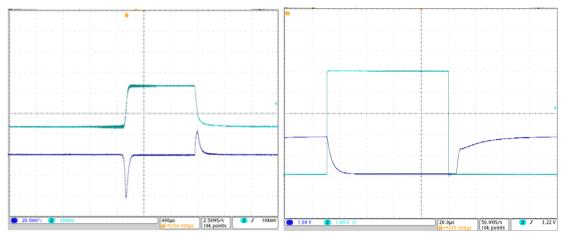

Figure 7: Start-up transient

(Vin = 0 to 5V; Vout = 1.8V, lout = 500 mA, Ta = 25°C) (1: Vout,2:Vin)

Figure 8: Response to line transient

(lout = 0 mA, Vin: 4.5 to 5.5V, 5.5V to 4.5V, Vout = 1.8V, Ta=  $25^{\circ}$ C) (1:Vin,2:Vout AC)

PUBLIC **29-Aug-18 Doc. DS-110961 V2.4 WWW.CISSOID.COM** 6 of 10

#### **Circuit Functionality**

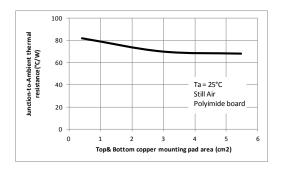

#### Safe operating area wrt to power dissipation including PCB layout guidelines

As the package used for CHT-VEGA is very small, achieving efficient thermal performance for power applications requires efficient management of the heat flow out of the device. The purpose of this section is to guide the user in maximizing the power handling capability of the TDFP16 package. Using natural cooling, the method of improving power performance should be focused on the optimum design of copper mounting pads. The design should take into consideration the size of the copper and its placement on either or both of the board surfaces. A copper mounting pad is important because the substrate of the integrated circuit is mounted directly onto the thermal pad of the TDFP16 package. The pad acts as a heat sink to reduce thermal resistance and leads to improved power performance.

The maximum power dissipation is determined by the maximum junction temperature rating, the ambient temperature, and junction-to-ambient thermal resistance:

$$P_{DMAX} = (T_{JMAX} - T_A)/R_{\theta JA}$$

Where  $T_{JMAX}$ =225°C and  $R_{\theta JA}$ = $R_{\theta JC}$ + $R_{\theta CA}$  with  $R_{\theta JC}$ =11°C/W and  $R_{\theta CA}$  (to be determined) is function of the size of the copper mounting pad and thermal coupling to the TDFP16.

The graph below provides information about junction-to-air thermal resistance of the package mounted on PCB with different sizes of copper thermal pads.

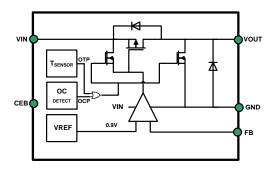

#### Functional Block diagram

A PMOS transistor controls the level of current flowing from VIN to VOUT. An internal voltage reference of 0.9V (highly stable over the whole temperature range) provides the reference to which the voltage on the FB pin is compared. The internal amplifier drives the gate of the PMOS and regulates VOUT.

An on-chip temperature sensor with hysteresis measures the die temperature; if this temperature exceeds a predefined threshold, the PMOS transistor is disabled and VOUT is connected to GND.

An overcurrent protection circuit is implemented. When the output current is reaching a certain threshold (lth), the PMOS transistor is disabled and VOUT is connected to GND for a certain period of time (typ 0.5 µsec); then normal operation is resumed. So in case of eg permanent short-circuit, the overcurrent protection mechanism will alternate between 2 states (ON, OFF) and deliver an average current of 1.15A (typ).

CEB pin provides a Disable feature (when CEB is high, CHT-VEGA is disabled); internally, this signal acts in the same way as the over temperature detection signal (OTP).

#### **External resistances calculation rules**

R1 and R2 values should be computed as follows:

$$\frac{R1+R2}{R2} = \frac{VOUT}{0.9V}$$

R1+R2 value should be lower than  $200k\Omega$  to limit the impact of the FB input leakage current.

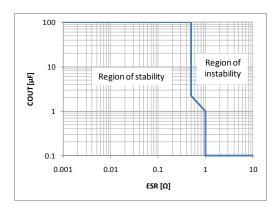

#### **ESR/Cload graph**

The output capacitor of the regulator must be selected in the region of stability indicated by the figure below.

Even though still in the stability region, capacitances less than 1  $\mu F$  should be used with care because they require careful selection of ESR to ensure stability.

#### Input capacitance

Recommended typical value for the  $C_{\text{IN}}$  capacitance is  $1\mu F$ .

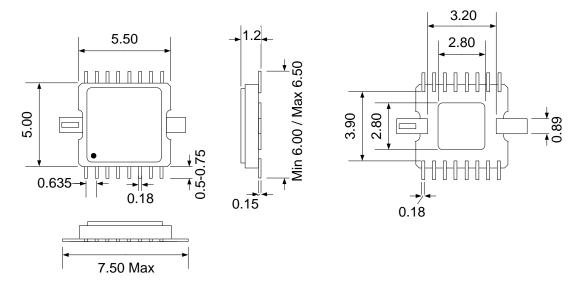

# **Package Dimensions**

TDFP16 physical dimensions (mm +/- 10%)

# **Ordering Information**

| Product Name | Ordering Reference    | Package | Marking      |

|--------------|-----------------------|---------|--------------|

| CHT-VEGA     | CHT-STA4853B-TDFP16-T | TDFP16  | CHT-STA4853B |

## **Contact & Ordering**

#### **CISSOID S.A.**

| Headquarters and contact EMEA: | CISSOID S.A. – Rue Francqui, 3 – 1435 Mont Saint Guibert - Belgium T:+32 10 48 92 10 - F:+32 10 88 98 75 Email: sales@cissoid.com |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Sales<br>Representatives:      | Visit our website: http://www.cissoid.com                                                                                         |

#### **Disclaimer**

Neither CISSOID, nor any of its directors, employees or affiliates make any representations or extend any warranties of any kind, either express or implied, including but not limited to warranties of merchantability, fitness for a particular purpose, and the absence of latent or other defects, whether or not discoverable. In no event shall CISSOID, its directors, employees and affiliates be liable for direct, indirect, special, incidental or consequential damages of any kind arising out of the use of its circuits and their documentation, even if they have been advised of the possibility of such a damage. The circuits are provided "as is". CISSOID has no obligation to provide maintenance, support, updates, or modifications.

PUBLIC

29-Aug-18

Doc. DS-110961 V2.4

WWW.CISSOID.COM

10 of 10