## **FEATURES**

### ■ Single-chip XGA/Super VGA LCD controller

Pin-compatible superset of CL-GD7541/7543 SVGA LCD controllers

— IBM® VGA hardware-compatible

### ■ GUI acceleration

- BitBLT engine (double-buffering, auto-start, memorymapped I/O, and transparent BitBLT)

- Color expansion for 8- or 16-bit pixels

- True packed-pixel addressing for 4, 8, 16, and 24 bits per pixel

- Programmable linear memory addressing

- $32 \times 32$  or  $64 \times 64$  hardware cursor

### ■ Cost-effective multimedia enhancements with 1-MByte DRAM

- Enhanced MVA™ (Motion Video Acceleration™)

- True-color, full-motion video playback

- Mixed graphics/video color depths (multi-format frame accelerator)

- Supports 4:2:2 YCrCb, RGB 5-5-5, and AccuPak (8-bit) color space formats

- Integrated 4:2:2 YCrCb -to-RGB 8-8-8 color space converter

- Up to 4X continuous horizontal/vertical upscaling

- Full MVA™ support with TFT and STN color LCDs

- Dual apertures (video/graphics) with VESA<sup>®</sup> VL-Bus<sup>™</sup> and PCI bus

- Interface to analog NTSC/PAL encoders for TV OUT

GUI-Accelerated XGA/SVGA LCD Controller with Low-Cost Multimedia Options from Enhanced MVA™

# ■ Cost-effective multimedia enhancements with 1-MByte DRAM (cont.)

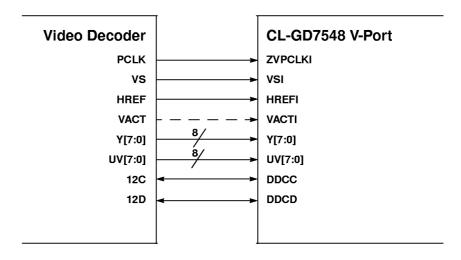

- Flexible V-Port™

- 8-/16-bit V-Port™ connected to display memory

- Single-chip live video solution with popular decoders (such as the Philips<sup>®</sup> SAA7110 or the CL-PX4072)

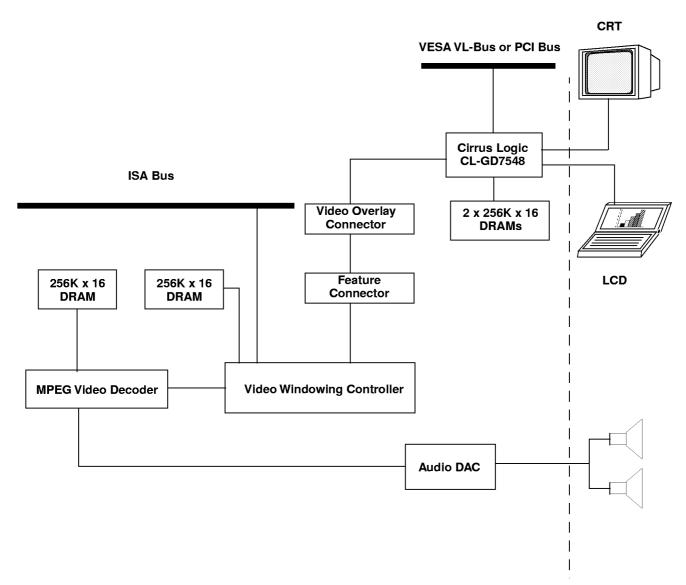

- Two-chip MPEG solution (MPEG decoder and 256K × 16 DRAM)

- 1024 × 768 video using AccuPak (live video and playback)

- On-chip AccuPak: compression through V-Port™, decompression at display time

- Low-cost multimedia solution through PCMCIA multimedia cards

- Supports serial programming interface to popular decoders (video, audio, MPEG) through DDC-2b

- Zoomed Video compliance with DCI 1.x and Windows<sup>®</sup> 95 DirectDraw<sup>™</sup>

Version 1.2 April 1996

## FEATURES (cont.)

### ■ 32-bit direct-connect CPU host bus interfaces

- '486 CPU local bus (up to 50 MHz)

- VESA® VL-Bus™ @ 50-MHz bus clock

- PCI bus @ 33-MHz bus clock with burst support: bigendian byte-order hardware support for PowerPC™

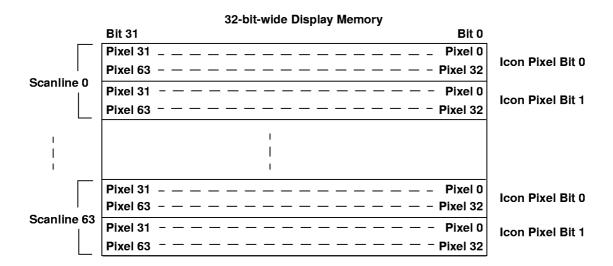

### ■ 64 × 64 pixel size hardware pop-up icons

Displays up to four independently controlled, 4-color icons

### ■ Scalable 1- and 2-Mbyte display memory

- 32-bit-wide interface to display memory

- Two/four 256K × 16 DRAMs

- Four 512K × 8 DRAMs

- Optimized support for Extended Data-Out (Hyper-Page-Mode) DRAMs

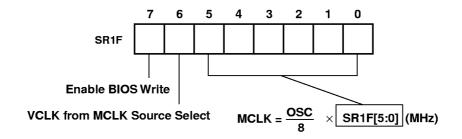

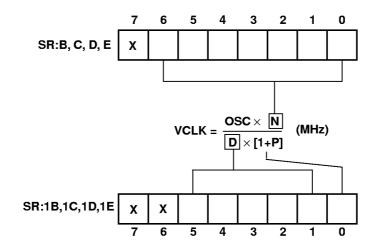

### ■ Integrated programmable frequency synthesizer

- VCLK up to 80 MHz at 5 V; 75 MHz at 3.3 V

- MCLK up to 66 MHz at 5 V; 54 MHz at 3.3 V

### ■ Integrated 24-bit true-color RAMDAC

- Non-interlaced CRTs:  $640 \times 480$  with 16M colors,  $800 \times 600$  with 64K colors, or  $1024 \times 768$  non-interlaced with 256 colors

- Interlaced CRTs: 1280 × 1024 with 256 colors

# ■ 640 × 480 (VGA), 800 × 600 (SVGA), and 1024 × 768 (XGA) LCDs

- Color TFT LCDs

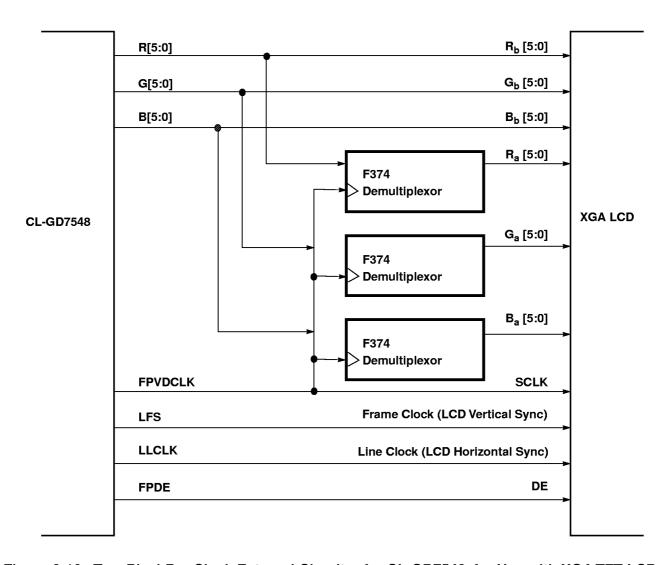

- 1-pixel/shift clock (9-, 12-, 18-, and 24-bit interfaces)

- 2-pixel/shift clock with external multiplexor (18- and 24-bit interfaces)

- Dual-scan color STN LCDs ( $640 \times 480$  and  $800 \times 600$ )

- Dithering algorithm automatically adds up to 6 bits per primary color without decreasing spatial resolution

- Enhanced frame-rate modulation algorithm improves display quality with fast-response STN LCDs

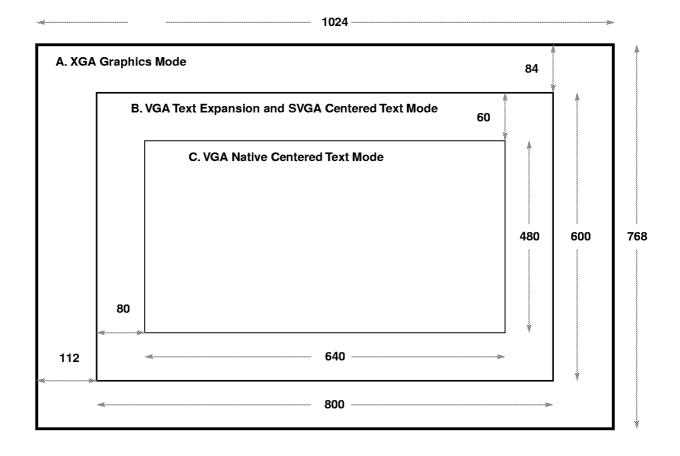

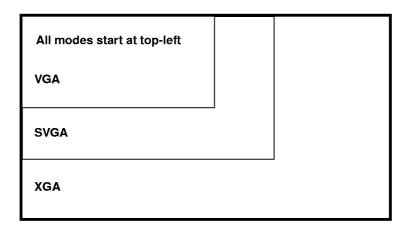

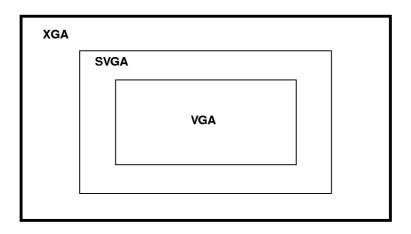

- Hardware expansion to  $800 \times 600$  with lower-resolution VGA modes

- SimulSCAN™ (simultaneous CRT and LCD)

### ■ Power-management capabilities

- 3.3-V, 5.0-V, and mixed-voltage operation

- VESA® DPMS (Display Power Management Signaling)

- DDC-1 and DDC-2b (Display Data Channel) support

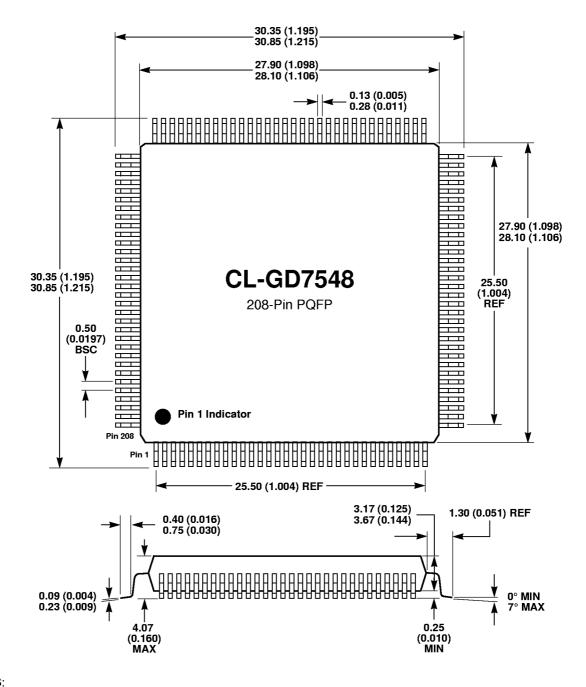

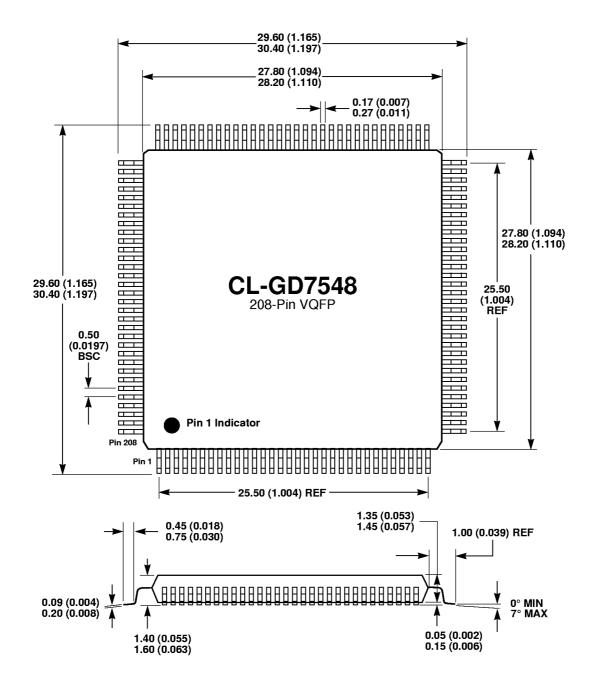

- EIAJ standard 208-pin plastic quad flat package

### **OVERVIEW**

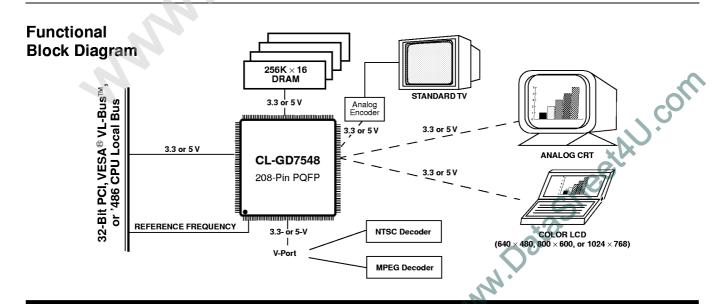

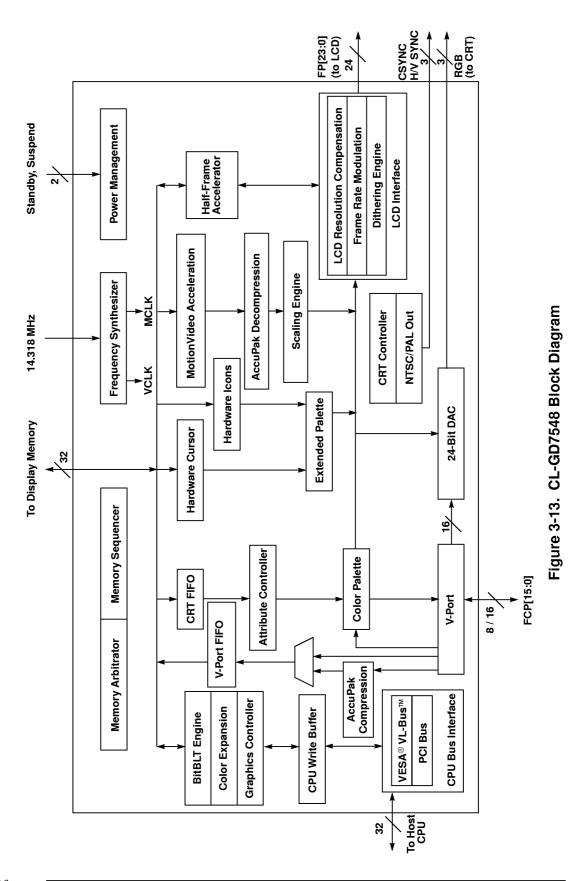

The CL-GD7548 GUI-accelerated SVGA LCD controller with MVA (Motion Video Acceleration) provides an extremely flexible, high-quality, cost-effective multimedia option for the next generation of mid-range to premium portable computers.

With its enhanced BitBLT GUI acceleration, continuous upscaling for  $1024 \times 768$  and  $800 \times 600$  LCDs, true-color capability, and mixed-voltage operation for low power consumption, the CL-GD7548 delivers exceptional graphics/video performance.

The CL-GD7548 V-Port enables high-quality, low-cost multimedia options such as a single-chip NTSC/PAL video decoder or MPEG decoder by eliminating the need for an additional video frame buffer and providing a dedicated path to a PCMCIA card. The CL-GD7548 V-Port is fully Zoomed Video compliant. A complete graphics subsystem can be built with only three active components: the CL-GD7548 and two 256K×16 DRAMs

The CL-GD7548 fully supports all features of the CL-GD7543, including MVA™ for playback of MPEG or Video for Windows .AVI (audio-video interleaved) files.

### **UNIQUE FEATURES**

#### High Performance

- BitBLT engine, color expansion, hardware cursor, linear addressing, and 32-bit memory interface

- BitBLT double-buffering, auto-start, and memory-mapped I/O

- BitBLT with transparency

- 32-bit local bus interfaces operating up to 50 MHz

- Hardware 'pop-up' icons

#### Multimedia and MVA™

- MVA™ (Motion Video Acceleration™)

- Multi-format frame buffer

- Dual independent apertures: one for graphics and one for video

- Interface to CL-PX4072 video pixel decoder requires no external logic

- 8 or 16-bit V-Port to display memory

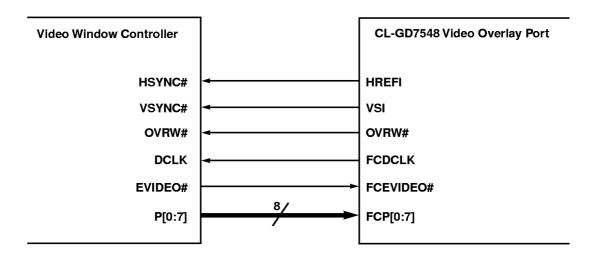

- 8-bit Overlay Port; video data overlay for display

- Interface to NTSC/PAL analog encoders

- AccuPak™ compression and decompression logic on-chip

### Enhanced LCD Support

- 1024×768 LCD support (TFT)

- 800 x 600 LCD support (both TFT and dual-scan STN) with comprehensive hardware resolution-compensation support

- Enhanced frame-rate modulation

- Intelligent dithering algorithm expands the number of input bits per primary color (RGB) on TFT or STN LCDs

### Power Management

- 3.3-V, 5.0-V, or mixed-voltage support

- Hardware-initiated Standby and Suspend modes and VESA® DPMS support for CRTs

### Software

- Complete suite of drivers for multiple operating systems

- User-friendly utilities

### **BENEFITS**

- Accelerates GUIs such as Microsoft<sup>®</sup> Windows<sup>®</sup>; provides high resolution and color-depth capabilities.

- ☐ Reduced BLT setup, overlapped execution, more efficient Windows® GDI (graphical device interface) software.

- ☐ Accelerates games.

- □ Increases system throughput; PCI interface allows use in 'X86, PowerPC™, or other platforms.

- Provides hot-key display for on-screen symbols such as battery 'fuel gauge' and contrast/brightness controls.

- ☐ Hardware enhancement for playback of files that are compatible with the DCI (Display Control Interface) and DirectDraw™ standard.

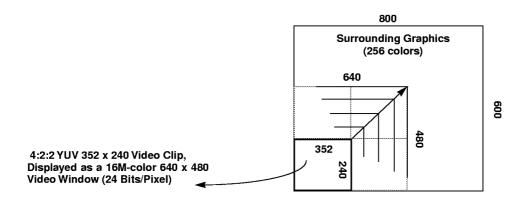

- Displays separate graphics and video windows at independent color depths. Maintains high rate of video playback without degrading performance.

- □ A BitBLT operation in Microsoft® Windows® can be in progress while live video data is being simultaneously shown through the secondary aperture.

- ☐ Allows capability for live 'TV in a window' at real-time speeds.

- Eliminates external video frame buffer and additional hardware; enables low-cost multimedia add-in PCMCIA cards.

- ☐ V-Port clock rate decoupled from display clock rate.

- Enables external hardware to support occlusion.

- Overlay regions defined with internal window registers and/or color keys.

- Integrated design can be developed to display computergenerated data on a TV or to record to a VCR.

- 2:1 reduction in storage and data rate requirements over 16-bpp formats

- ☐ 2-pixel/shift clock external multiplexor.

- $\square$  Up to 800  $\times$  600 hardware expansion for lower-resolution modes.

- Enables full use of the display area whether in graphics or text mode.

- Improves display quality; increases stability of shades for dual-scan STNs.

- Displays high- and true-color modes with smooth shading (no contouring) on all supported LCD types.

- Minimizes operating power consumption; provides manufacturing flexibility.

- Reduces power consumption; supports Energy Star monitors for 'green PC' compliance.

- □ Supports all popular application environments.

- □ Enables fast and on-the-fly changes.

# SOFTWARE SUPPORT

### Operating System and Application Software Drivers

|  | Software Drivers <sup>a</sup>                                                                                                                                                                                                                        | Resolution Supported                                                               | Number<br>of Colors                |

|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|------------------------------------|

|  | Microsoft®/Intel® DCI™ v1.x                                                                                                                                                                                                                          | 640 × 480, 800 × 600, 1024 × 768                                                   | 256                                |

|  | Microsoft <sup>®</sup> Windows <sup>®</sup> v3.1<br>Microsoft <sup>®</sup> Windows <sup>®</sup> 95 <sup>™</sup><br>Microsoft <sup>®</sup> Windows <sup>®</sup> 95 <sup>™</sup> with DirectDraw <sup>™</sup><br>Cirrus Logic VPM (Video Port Manager) | 640 × 480, 800 × 600, 1024 × 768, 1280 × 1024<br>640 × 480, 800 × 600<br>640 × 480 | 256<br>65,536<br>16 million        |

|  | Microsoft® Windows NT™ v3.5                                                                                                                                                                                                                          | 640 × 480, 800 × 600, 1024 × 768                                                   | 16 and 256                         |

|  | OS/2 <sup>®</sup> v2.0, WARP 3.0                                                                                                                                                                                                                     | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480              | 16 and 256<br>65,536<br>16 million |

|  | AutoCAD® v11, v12                                                                                                                                                                                                                                    | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480              | 16 and 256<br>65,536<br>16 million |

|  | Autoshade <sup>®</sup> v2.0<br>3D Studio <sup>®</sup> v1, v2                                                                                                                                                                                         | 640 × 480, 800 × 600, 1024 × 768<br>640 × 480, 800 × 600<br>640 × 480              | 256<br>65,536<br>16 million        |

a Driver support for additional applications is provided by independent software vendors, either with specific drivers or through VESA mode support. For more information concerning driver support, contact the software manufacturer.

### **BIOS**

| Feature                                                                 | Benefit                                                                                                                       |  |  |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--|--|

| ■ 48-Kbyte BIOS                                                         | ☐ Provides optimum performance with VGA and VESA® extended mode support                                                       |  |  |

|                                                                         | <ul> <li>Provides system design options for the best combination of performance and<br/>functionality.</li> </ul>             |  |  |

| ■ Fully IBM® VGA-compatible BIOS                                        | ☐ Compatible with the existing base of PC applications.                                                                       |  |  |

| ■ VESA® VBE (VGA BIOS extensions) 1.2 and PM (power management) support | <ul> <li>Compatible with industry standards for extended mode support beyond VGA and<br/>power-management control.</li> </ul> |  |  |

### Software Utilities

| Utility                  | Function                                                                                                                                                                                                   |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AutoResolution Switching | Windows® application for automatically switching display resolutions (for example, from a 1024 $\times$ 768 CRT to lower-resolution 640 $\times$ 480 or 800 $\times$ 600 LCDs) without relaunching Windows |

| CLMode                   | Video mode and video display configuration utility suitable for end-use distribution (includes foreign language translations)                                                                              |

| OEMSI                    | BIOS-customization utility for OEM development use                                                                                                                                                         |

| PCLRegs                  | VGA controller register viewer/editor for OEM development use                                                                                                                                              |

| V-Port Regs              | Windows®-based register viewer/editor and V-Port/Video Window display configuration utility for OEM development use                                                                                        |

| WinMode                  | Windows® application for graphics mode and display type configuration (includes foreign language translations, selectable from within the utility)                                                         |

# **Table of Contents**

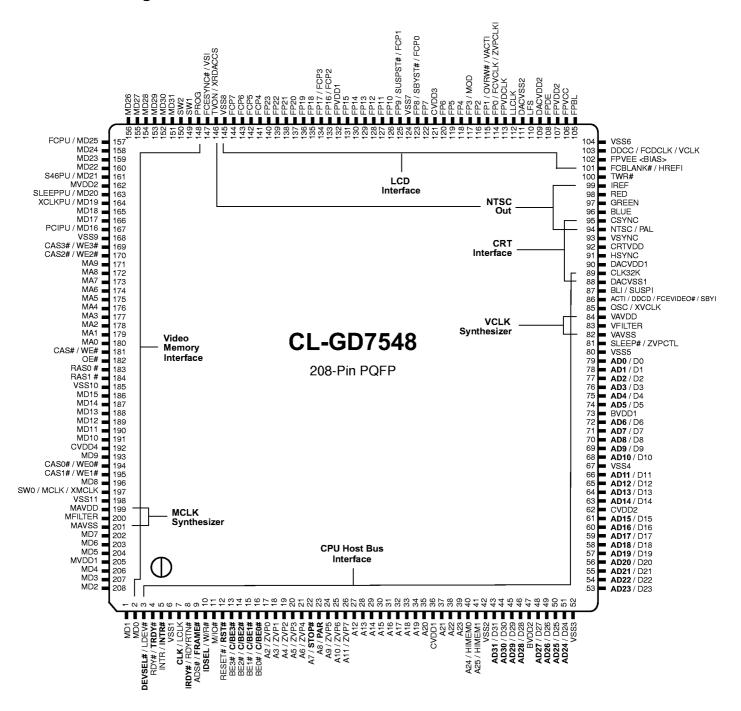

| 1. | PIN IN      | FORMATION                                                                                                                       | .15 |

|----|-------------|---------------------------------------------------------------------------------------------------------------------------------|-----|

|    | 1.1         | Pin Diagram                                                                                                                     | 15  |

|    | 1.2         | Pin Tables                                                                                                                      | 16  |

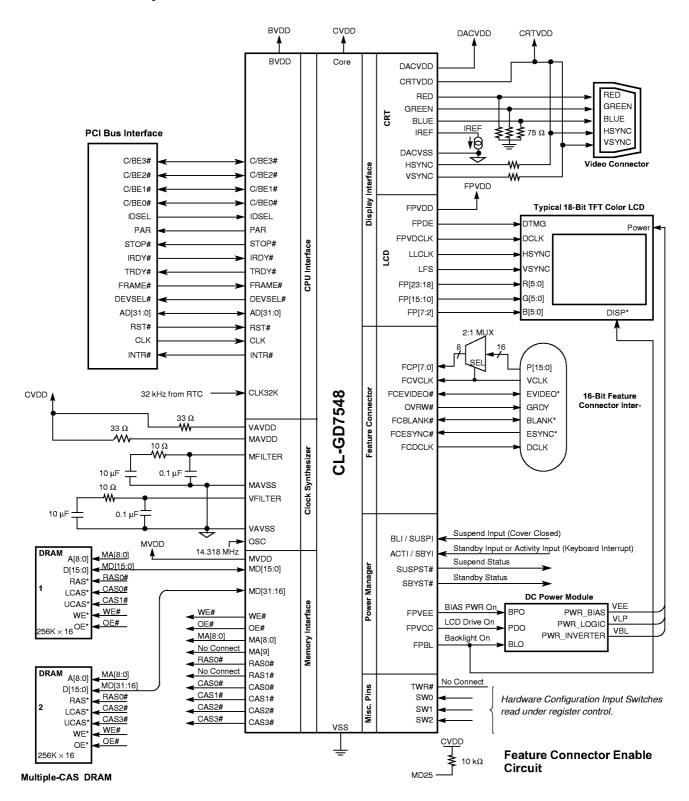

|    | 1.3         | Block Diagrams: CL-GD7548 Interfaces                                                                                            |     |

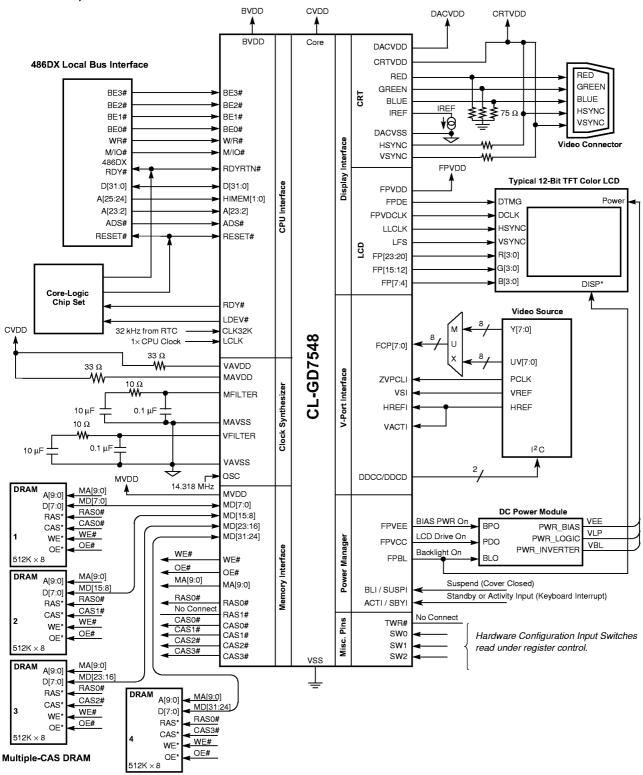

|    | 1.3.1       | Local Bus (32-Bit '486DX or VESA <sup>®</sup> VL-Bus™), 2-Mbyte 512K × 8 DRAM, 12-Bit TFT Color, V-Port™ Interface              | 20  |

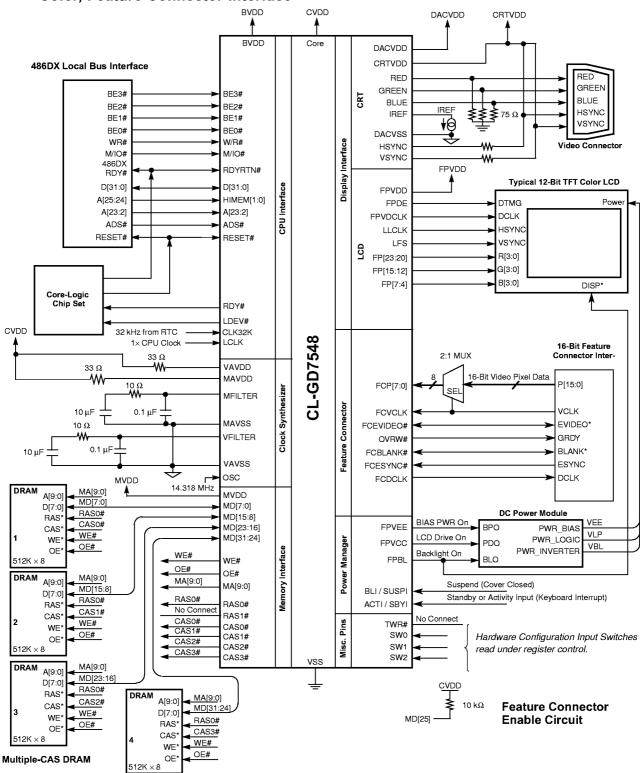

|    | 1.3.2       | Local Bus (32-Bit '486DX or VESA <sup>®</sup> VL-Bus™), 2-Mbyte 512K × 8 DRAM, 12-Bit TFT Color, Feature Connector Interface    | 21  |

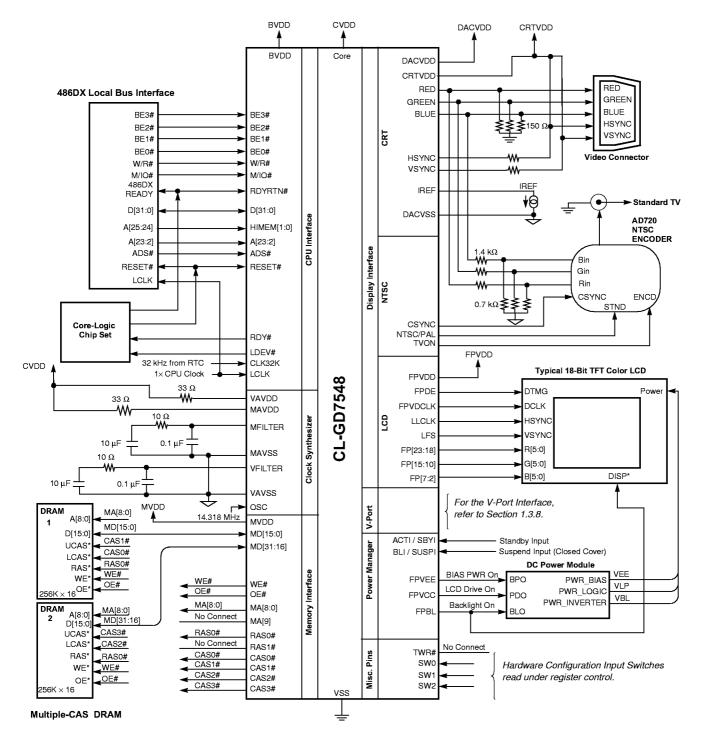

|    | 1.3.3       | Local Bus (32-Bit '486DX or VESA <sup>®</sup> VL-Bus™), 1-Mbyte 256K × 16 DRAM, 18-Bit TFT Color NTSC Output, V-Port™ Interface | r,  |

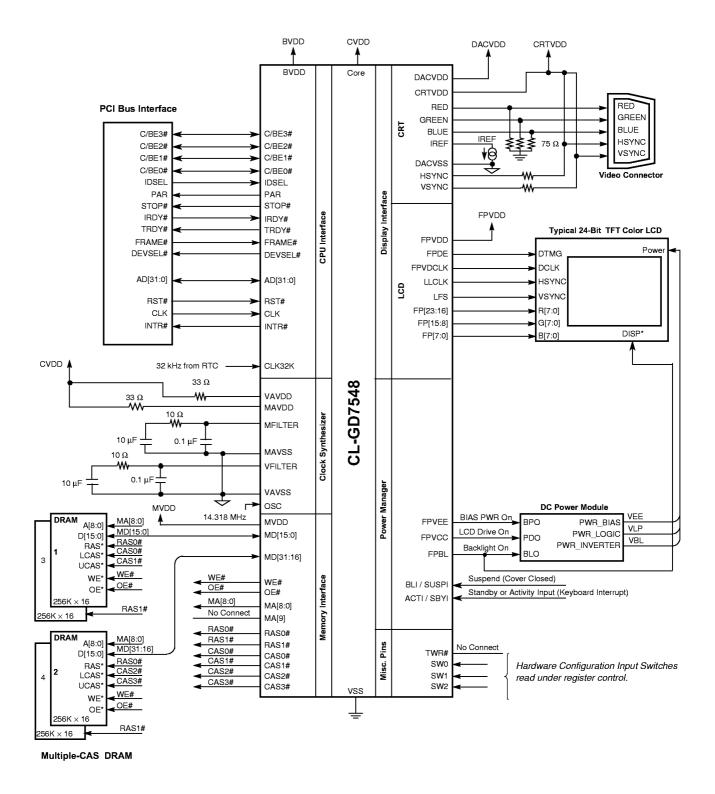

|    | 1.3.4       | PCI Bus, 2-Mbyte 256K × 16 DRAM, 24-Bit TFT Color                                                                               |     |

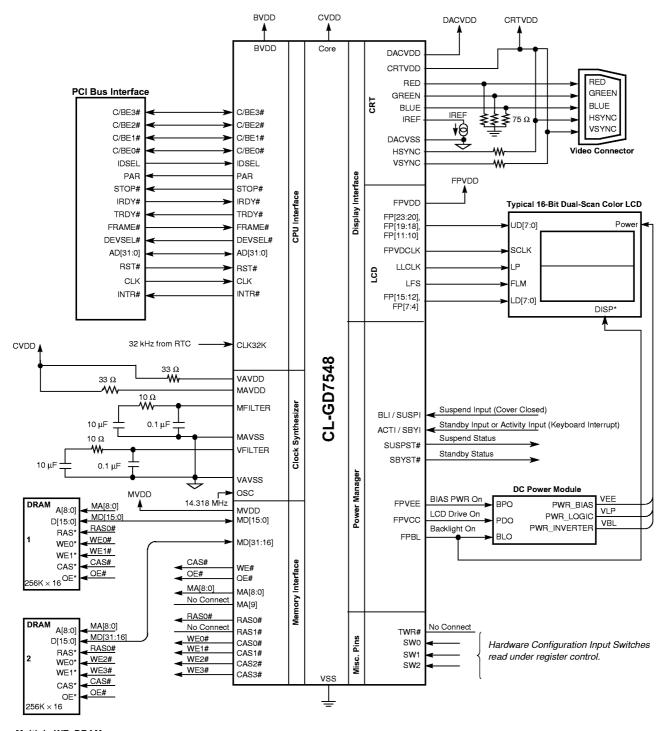

|    | 1.3.5       | PCI Bus, 1-Mbyte 256K × 16 DRAM, 16-Bit Dual-Scan Color                                                                         |     |

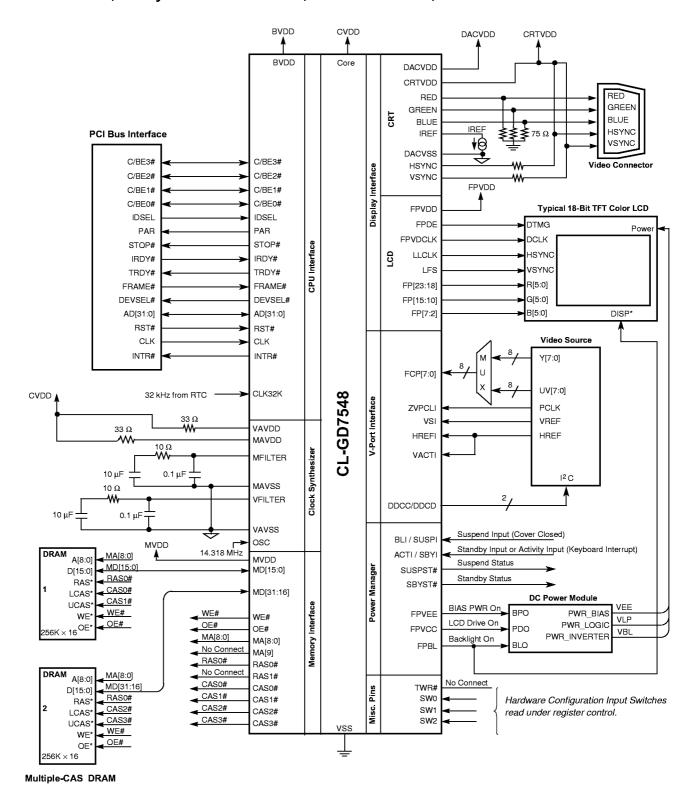

|    | 1.3.6       | PCI Bus, 1-Mbyte 256K × 16 DRAM, 18-Bit TFT Color, V-Port™ Interface                                                            |     |

|    | 1.3.7       | PCI Bus, 1-Mbyte 256K × 16 DRAM, 18-Bit TFT Color, Feature Connector Interface                                                  |     |

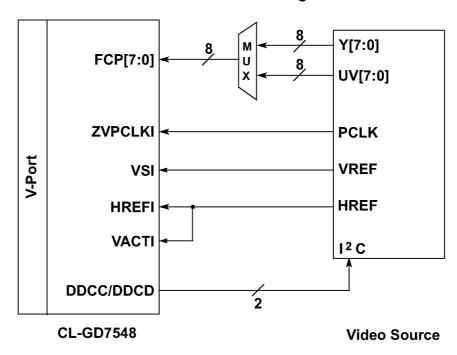

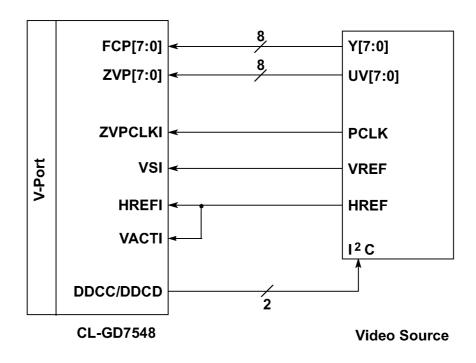

|    | 1.3.8       | V-Port™ Interfaces for VESA VL-Bus and PCI Bus Systems                                                                          |     |

| 2. | וח ואום     | ESCRIPTIONS                                                                                                                     |     |

| ۷. | 2.1         | Host CPU Bus Interface Pins                                                                                                     |     |

|    | 2.1.1       | CL-GD7548 CPU Host Bus Interface Pins to '486 or VESA® VL-Bus™ Local Bus                                                        |     |

|    | 2.1.1       | CL-GD7548 CPU Host Bus Interface Pins to PCI Bus                                                                                |     |

|    | 2.1.2       | LCD Interface Pins                                                                                                              |     |

|    | 2.3         | CRT Interface Pins                                                                                                              |     |

|    | 2.4         | NTSC and PAL Interface Pins                                                                                                     |     |

|    | 2.5         | Dual-Frequency Synthesizer Interface Pins                                                                                       |     |

|    | 2.6         | Display Memory Interface Pins                                                                                                   |     |

|    | 2.7         | Configuration Input Pins                                                                                                        |     |

|    | 2.8         | Switch and Miscellaneous Configuration Input Pins                                                                               |     |

|    | 2.9         | Feature Connector Pins                                                                                                          |     |

|    | 2.10        | V-Port Pins                                                                                                                     |     |

|    | 2.11        | Power-Management Pins                                                                                                           |     |

|    | 2.12        | Ground Pins                                                                                                                     |     |

|    | 2.13        | Power Pins                                                                                                                      |     |

| 3. | <b>FUNC</b> | TIONAL DESCRIPTION                                                                                                              | .63 |

|    | 3.1         | Introduction                                                                                                                    | 63  |

|    | 3.1.1       | Features Common with the CL-GD7543                                                                                              | 64  |

|    | 3.1.2       | Enhanced Features over the CL-GD7543                                                                                            |     |

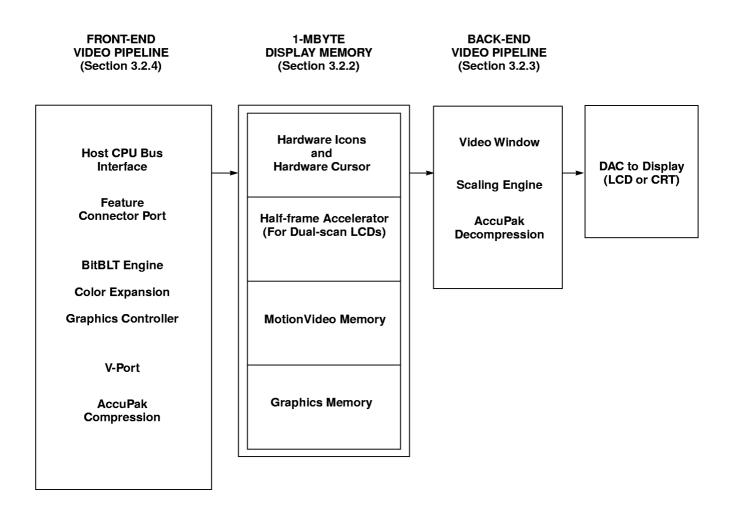

|    | 3.2         | Enhanced MotionVideo Acceleration (MVA™)                                                                                        | 66  |

|    | 3.2.1       | Overview                                                                                                                        | 66  |

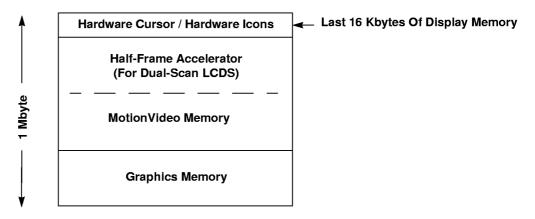

|    | 3.2.2       | MotionVideo™ Memory                                                                                                             | 69  |

|    | 3.2.3       | Back-End Video Pipeline                                                                                                         | 73  |

|    | 3.2.4       | Front-End Video Pipeline                                                                                                        |     |

|    | 3.3         | Support for 1024 x 768 (XGA) TFT LCD Panels                                                                                     | 87  |

|    | 3.3.1       | XGA TFT LCD Mode of Operation                                                                                                   | 88  |

|    | 3.3.2       | XGA TFT LCD Interface                                                                                                           | 92  |

|    | 3.4         | Video Overlay Mode                                                                                                              |     |

|    | 3.4.1       | Video Overlay Mode Application Examples                                                                                         |     |

|    | 3.5         | Functional Blocks                                                                                                               | 97  |

5

|    | 3.5.1      | Host CPU Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97                                |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|

|    | 3.5.2      | Host CPU Write Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 100                               |

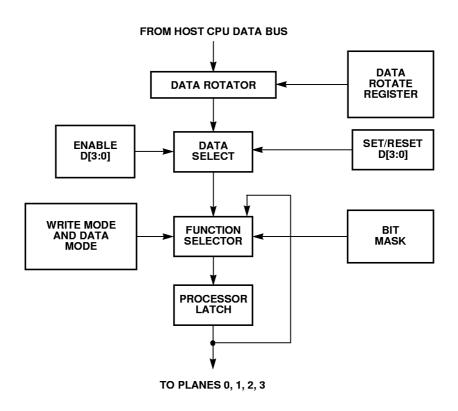

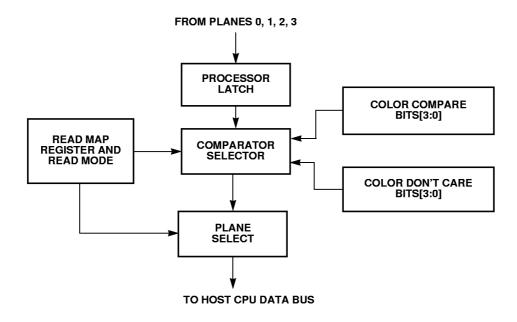

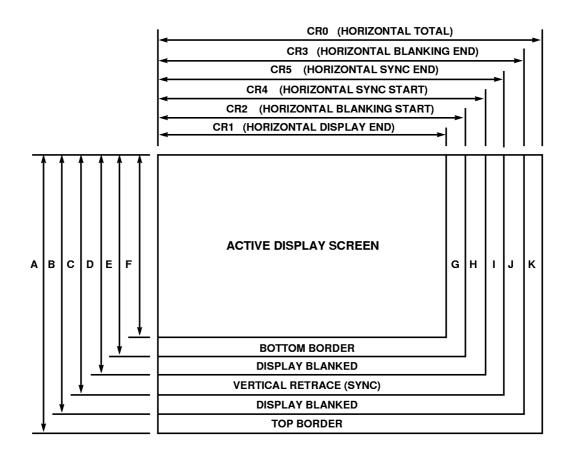

|    | 3.5.3      | Graphics Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 100                               |

|    | 3.5.4      | Color Expansion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 102                               |

|    | 3.5.5      | Bit Block Transfer (BitBLT) Engine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102                               |

|    | 3.5.6      | Memory Arbitrator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                   |

|    | 3.5.7      | Memory Sequencer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                   |

|    | 3.5.8      | CRT FIFO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 104                               |

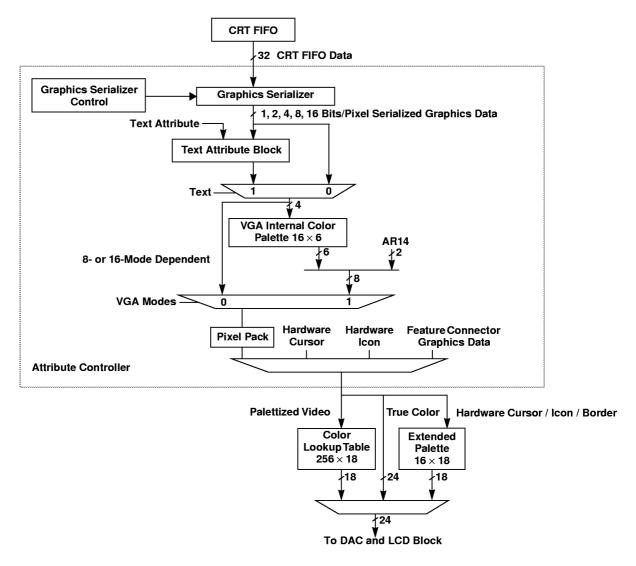

|    | 3.5.9      | Attribute Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105                               |

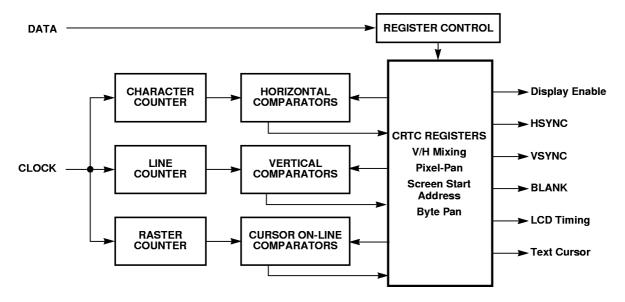

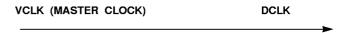

|    | 3.5.10     | CRT Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 106                               |

|    | 3.5.11     | Hardware Cursor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107                               |

|    | 3.5.12     | Hardware Pop-up Icons                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |

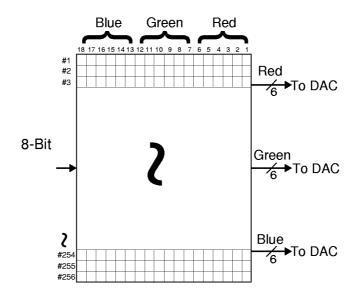

|    | 3.5.13     | Color Palette                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |

|    | 3.5.14     | Extended Palette RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |

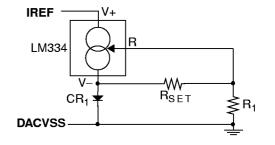

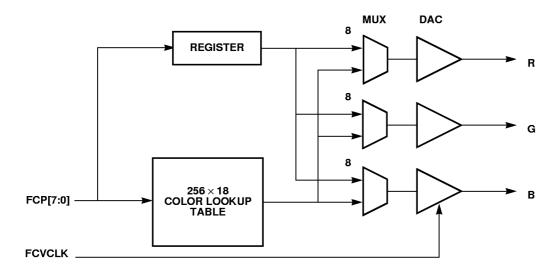

|    | 3.5.15     | Triple DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111                               |

|    | 3.5.16     | TV-Out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |

|    | 3.5.17     | Half-Frame Accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                   |

|    | 3.5.18     | LCD Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                   |

|    | 3.5.19     | Frame Rate Modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                   |

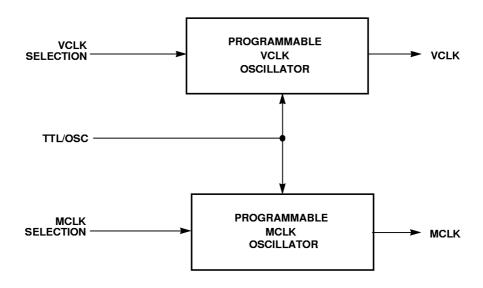

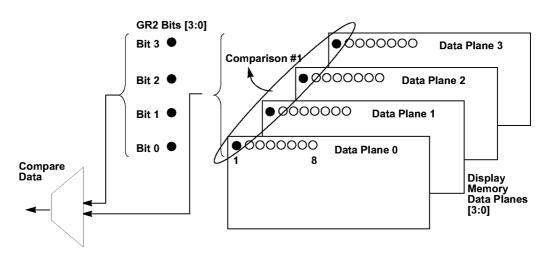

|    | 3.5.20     | Frequency Synthesizer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 121                               |

|    | 3.6        | Controller Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                   |

|    | 3.6.1      | Power Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 122                               |

|    | 3.6.2      | Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 123                               |

|    | 3.6.3      | RAMDAC Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 124                               |

|    | 3.6.4      | Programmable Core Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 125                               |

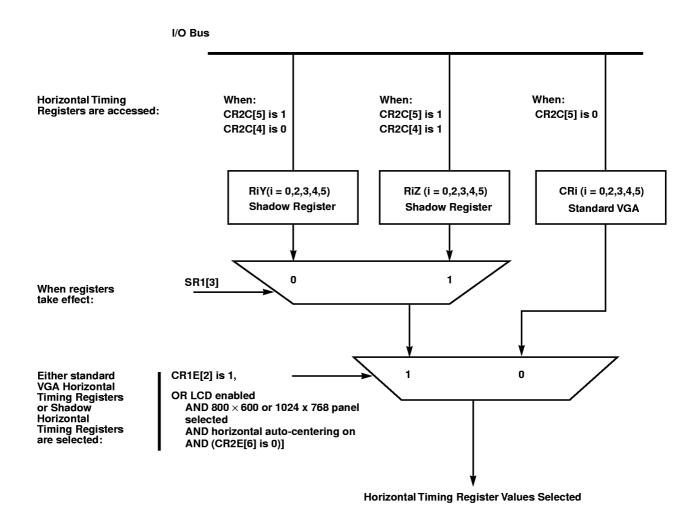

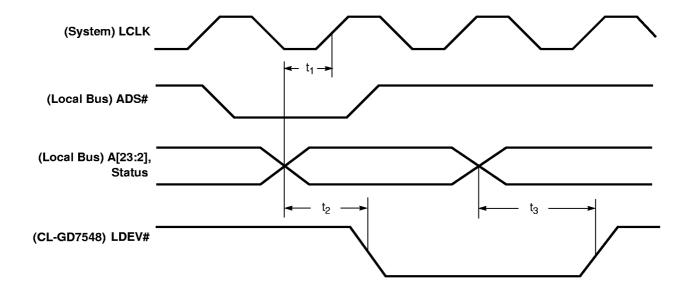

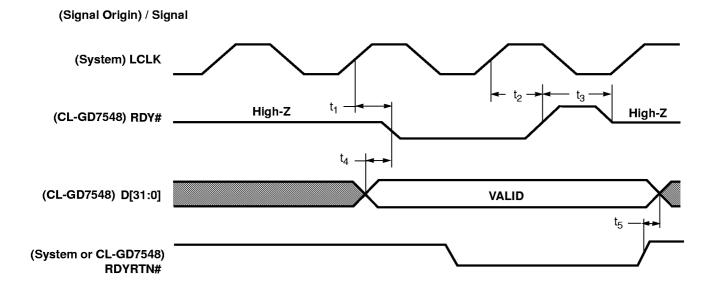

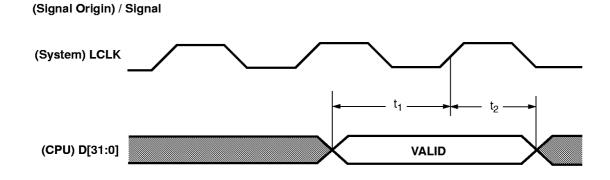

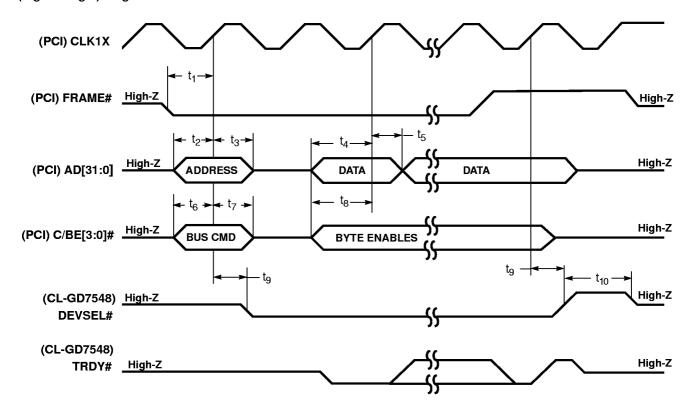

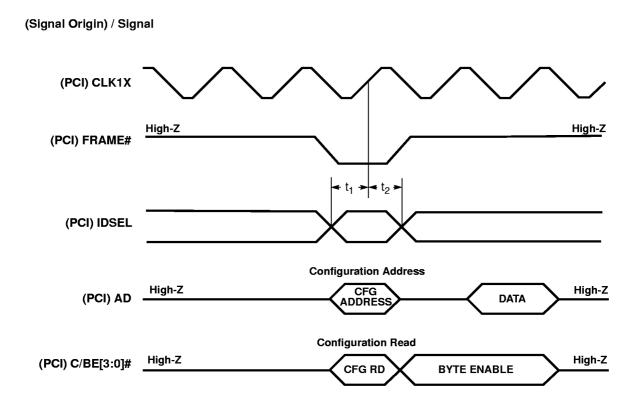

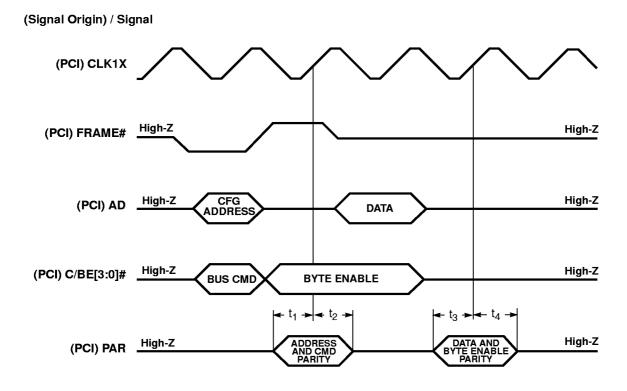

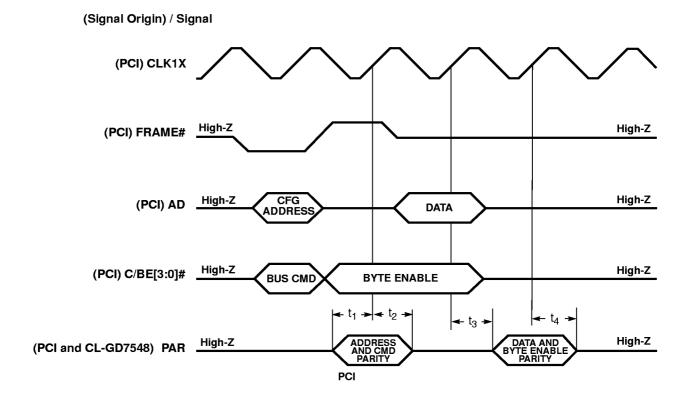

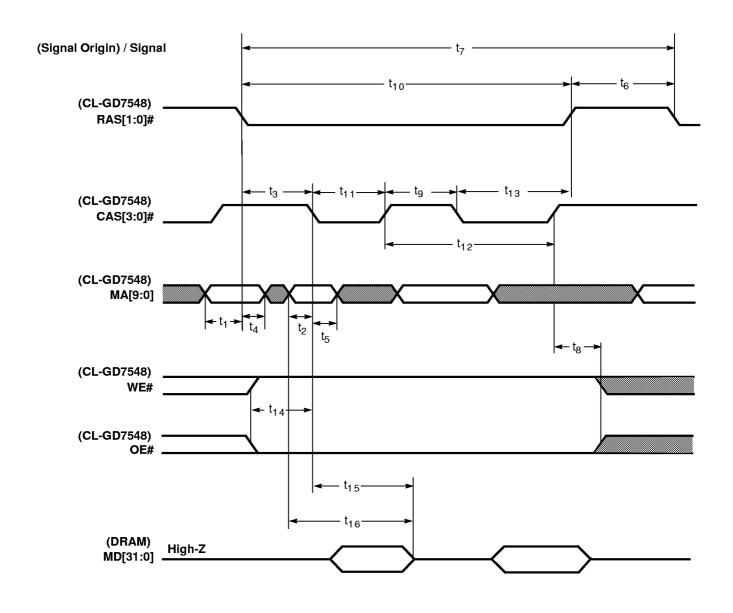

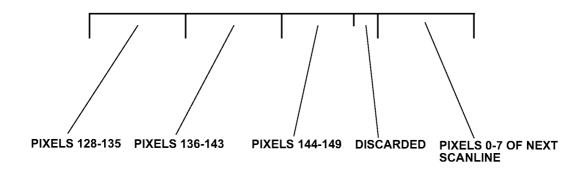

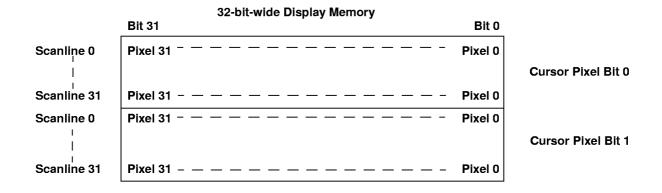

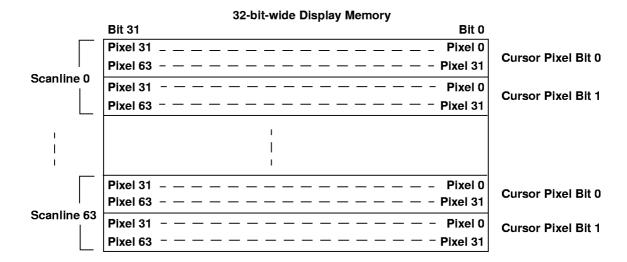

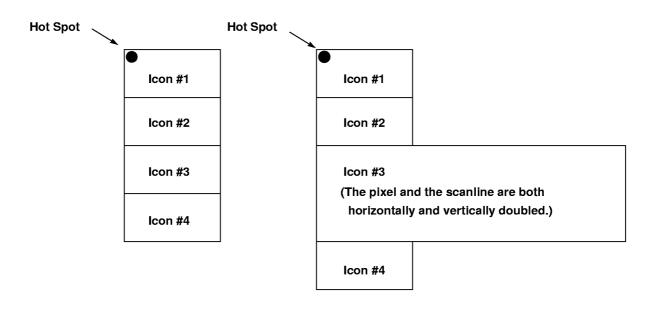

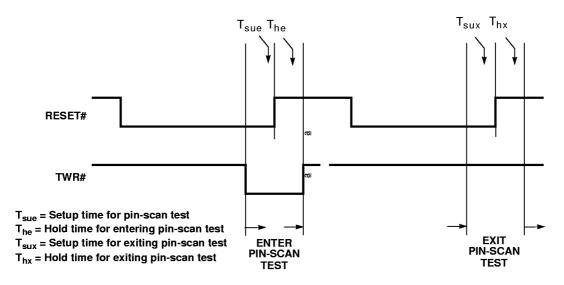

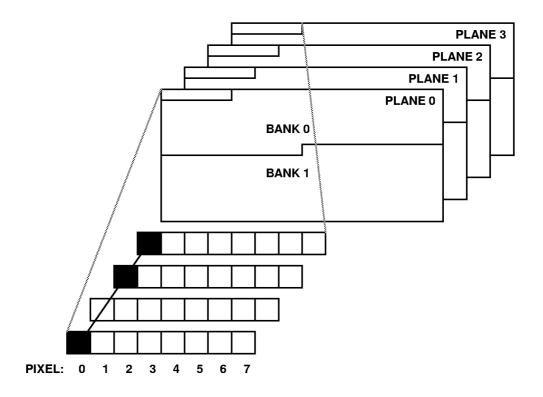

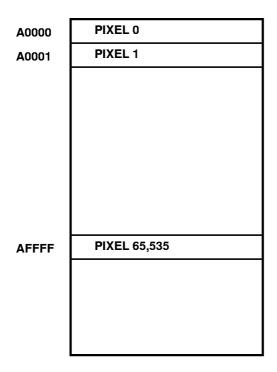

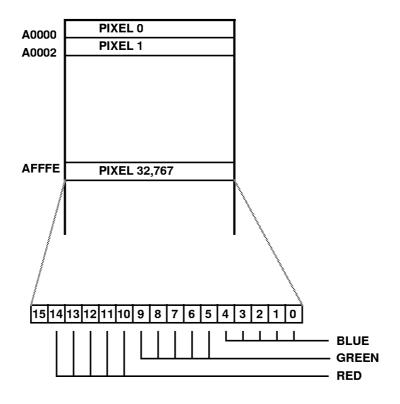

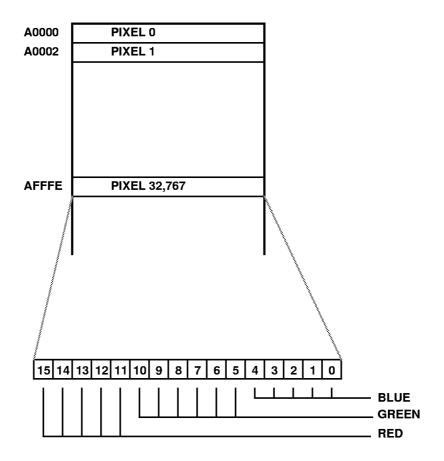

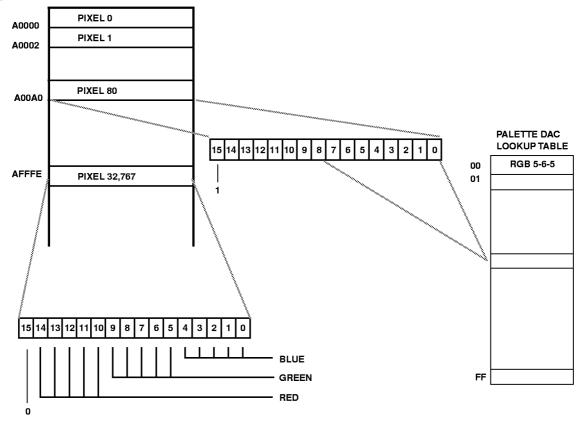

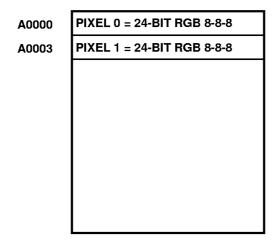

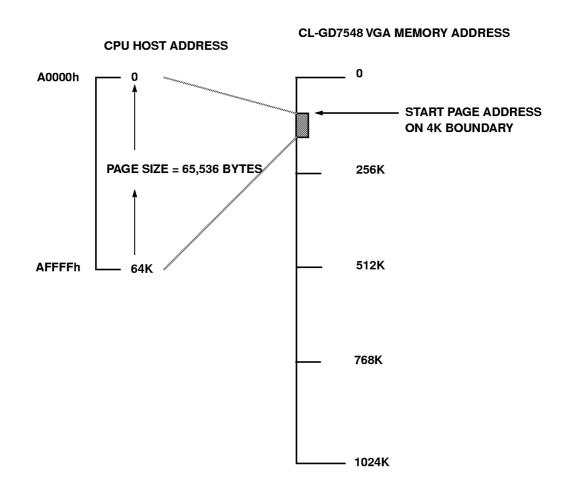

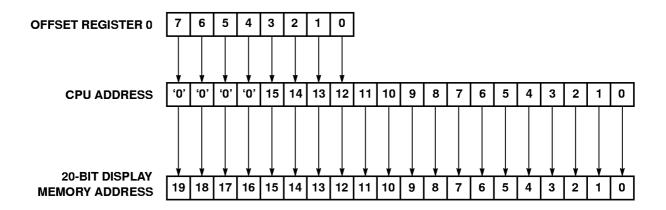

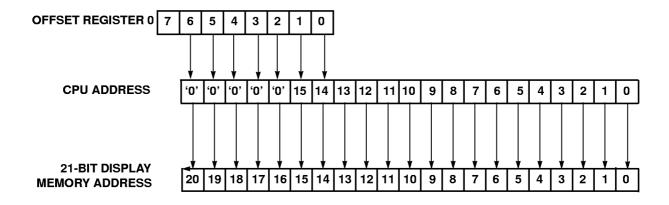

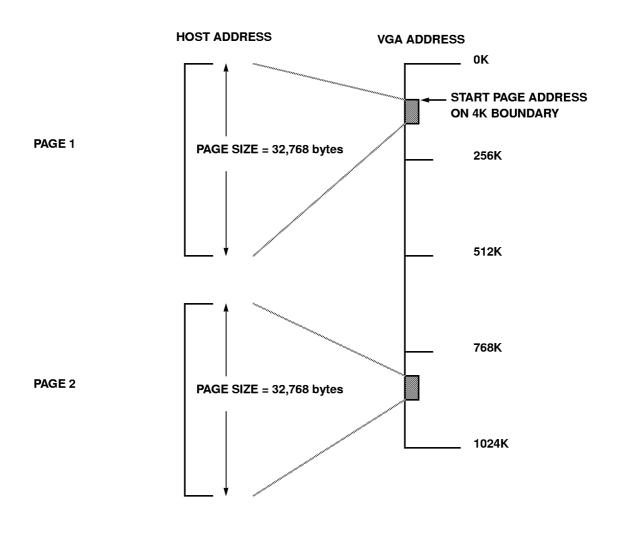

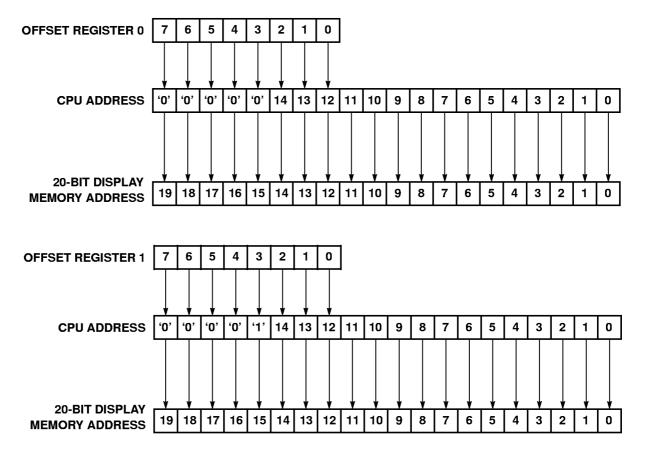

|    | 3.6.5      | Compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125                               |