# Comlinear CLC503 180MHz, Differential-Output Amplifier

## **General Description**

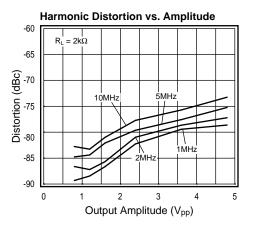

The Comlinear CLC503 is a single-ended to differential amplifier. It utilizes a pair of closed-loop transconductance amplifiers to provide wideband, high fidelity, differential output signals. Internal resistors set the differential gain to 2V/V. With a ground-centered  $2V_{pp}$  input signal, the CLC503 will produce a  $4V_{pp}$  differential output signal. This differential output signal is centered around an adjustable common mode voltage. An independent input controls the common mode output voltage. The CLC503 has harmonic distortion products of -77dBc or less, and a signal to noise ratio of 72dB. The output stage is optimized for loads with signal ranges between +0.7 and +3.9 volts, such as those found on single supply CMOS ADCs. Overdrive recovery time of the CLC503 and following circuitry is optimized by the output limiting of the CLC503. The power down pin (P<sub>DN</sub>) allows for power savings in applications where unused circuitry is placed in a low power mode.

The CLC503 is an ideal amplifier to drive the differential inputs of the Comlinear CLC949, 12-bit, 20MSPS, analog-to-digital converter. It is tailored for driving single supply, differential input, analog-to-digital converters which require fast settling, high fidelity inputs.

### Features

- -77dBc distortion (10MHz, 4V<sub>pp</sub>)

- 72dB SNR (4V<sub>pp</sub>)

- 15ns settling (0.1%)

- 180MHz bandwidth

## **Applications**

- Single-to-differential conversion

- Single supply ADC signal conditioner

August 1996

| <b>Electrical Characteristics</b> ( $V_{CC}$ = + 5V, $V_{EE}$ = - 5V, $V_{cm}$ = 2.25V, $C_L$ = 5pF, $V_o$ = 4V <sub>pp</sub> unless specified) |                                                    |           |             |             |                   |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------|-------------|-------------|-------------------|-------|

| PARAMETERS                                                                                                                                      | CONDITIONS                                         | TYP       | MIN/MAX     | RATINGS     | UNITS             | NOTES |

| Ambient Temperature                                                                                                                             | CLC503                                             | +25°C     | +25°C       | -40 to 85°C |                   |       |

| FREQUENCY DOMAIN RESPONSE                                                                                                                       |                                                    |           |             |             |                   |       |

| Differential Amp                                                                                                                                |                                                    |           |             |             |                   |       |

| large signal bandwidth                                                                                                                          | $V_{0} < 4.0 V_{pp}$                               | 180       | 80          | 70          | MHz               |       |

| gain flatness                                                                                                                                   | V <sub>o</sub> < 4.0V <sub>pp</sub><br>DC to 10MHz | 0.3       | 0.5         | 0.5         | dB                |       |

| Common-Mode Amp                                                                                                                                 |                                                    |           |             |             |                   |       |

| -3dB bandwidth                                                                                                                                  | $V_o < 4.0 V_{pp}$                                 | 15        | 10          | 10          | MHz               |       |

| TIME DOMAIN RESPONSE                                                                                                                            | ··-                                                |           |             |             |                   |       |

| Differential Amp                                                                                                                                |                                                    |           |             |             |                   |       |

| rise and fall time                                                                                                                              | 2V step                                            | 2.1       | 2.5         | 3.0         | ns                |       |

| settling time to 0.1%                                                                                                                           | 2V step                                            | 15        | 22          | 25          | ns                |       |

| overshoot                                                                                                                                       | 2V step                                            | 0         |             |             | %                 |       |

| slew rate                                                                                                                                       | 2V step                                            | 800       | 500         | 500         | V/µs              |       |

| Common-Mode Amp                                                                                                                                 | ·                                                  |           |             |             |                   |       |

| recovery from power down                                                                                                                        | 0.1% output settling                               | 40        | 100         | 100         | ns                |       |

| DISTORTION AND NOISE RESPONSE                                                                                                                   |                                                    |           |             |             |                   |       |

| 2 <sup>nd</sup> harmonic distortion                                                                                                             | 4V <sub>pp</sub> , 1MHz                            | -78       | -74         | -70         | dBc               | В     |

|                                                                                                                                                 | 4V <sub>pp</sub> , 10MHz                           | -75       | -71         | -71         | dBc               | В     |

| 3 <sup>rd</sup> harmonic distortion                                                                                                             | $4\sqrt{1}$ 1MHz                                   | -85       | -80         | -79         | dBc               | В     |

|                                                                                                                                                 | $4V_{pp}^{pp}$ , 10MHz                             | -77       | -72         | -72         | dBc               | В     |

| SNR                                                                                                                                             | $4V_{pp}$ , 10MHz<br>$4V_{pp}$                     | 72        | 71          | 70          | dB                |       |

| integrated output noise voltage                                                                                                                 | $R_s = 50\Omega$                                   |           |             | -           | -                 |       |

| 5 1 5                                                                                                                                           | 10kHz – 500MHz                                     | 325       | 380         | 460         | μV <sub>rms</sub> |       |

| STATIC DC PERFORMANCE                                                                                                                           |                                                    |           |             |             |                   |       |

| Differential Amp                                                                                                                                |                                                    |           |             |             |                   |       |

| gain                                                                                                                                            | V <sub>o</sub> (Diff)/V <sub>in</sub>              | 2         | 1.75 - 2.25 | 1.75 - 2.25 | V/V               | A     |

| output offset voltage                                                                                                                           | $V_{in} = 0$                                       | 10        | 90          | 100         | mV                | A     |

| INL                                                                                                                                             |                                                    | 0.015     | 0.03        | 0.05        | %                 | A     |

| R <sub>in</sub>                                                                                                                                 |                                                    | 2         | 1.6 - 2.4   | 1.6 - 2.4   | kΩ                |       |

| Common-Mode Amp                                                                                                                                 |                                                    |           |             |             |                   |       |

| gain                                                                                                                                            | V <sub>ocm</sub> /V <sub>cm</sub>                  | 0.97      | 0.9 - 1.1   | 0.9 - 1.1   | V/V               |       |

| output offset voltage                                                                                                                           |                                                    | 100       | 200         | 200         | mV                | A     |

| R <sub>in</sub>                                                                                                                                 |                                                    | 10        | 5           | 5           | MΩ                |       |

| input voltage range                                                                                                                             |                                                    | 1.5 - 3.5 |             |             | V                 |       |

| power supply rejection ratio                                                                                                                    | DC                                                 | 50        | 30          | 30          | dB                | A     |

| supply current                                                                                                                                  | R <sub>L</sub> = ∞                                 | 25        | 30          | 30          | mA                | A     |

| supply current, power down                                                                                                                      | -                                                  | 4.5       | 6           | 6           | mA                | A     |

| MISCELLANEOUS PERFORMANCE                                                                                                                       |                                                    |           |             |             |                   |       |

| power down input                                                                                                                                | CMOS levels                                        | 0.5 - 4.8 |             |             | V                 | С     |

| VIL                                                                                                                                             | on                                                 | 1         |             |             | V                 | _     |

| VIH                                                                                                                                             | off                                                | 4.5       |             |             | V                 | С     |

| power down dissipation                                                                                                                          | P <sub>DN</sub> = "Hi"                             | 45        | 60          | 60          | mW                | A     |

| output voltage range                                                                                                                            | single output                                      | 0.7 - 3.9 | 0.85 - 3.7  | 0.9 - 3.5   | V                 |       |

| differential output resistance                                                                                                                  |                                                    | 500       | 400 - 600   | 375 - 625   | Ω                 |       |

Min/max ratings are based on product characterization and simulation. Individual parameters are tested as noted. Outgoing quality levels are determined from tested parameters.

| Absolute Maximum Ratings                    |                      |  |  |

|---------------------------------------------|----------------------|--|--|

| supply voltage                              | ±6V                  |  |  |

| maximum input range                         | ±6V                  |  |  |

| maximum output range (±V)                   | 0 to V <sub>CC</sub> |  |  |

| maximum operating temperature range         | -40°C to +85°C       |  |  |

| maximum junction temperature                | +175°C               |  |  |

| maximum storage temperature range           | -65°C to +150°C      |  |  |

| maximum lead temperature (soldering 10 sec) | +300°C               |  |  |

| ESD rating (human body model)               | 500V                 |  |  |

## Recommended Operating Conditions

| supply voltage            | ±4.5 to ±5.5Vdc |

|---------------------------|-----------------|

| input voltage             | ±1V             |

| output voltage            | +0.8 to +3.75V  |

| ambient temperature range | -40°C to +85°C  |

## Notes

A) J-level: spec is 100% tested at +25°C, sample tested at +85°C. LC/MC-level: spec is 100% wafer probed at +25°C.

B) J-level: spec is sample tested at +25°C.

C) **POWER DOWN** must be 1V higher than  $V_{cm}$ .

| Ordering Information |                   |             |  |

|----------------------|-------------------|-------------|--|

| Model                | Temperature Range | Description |  |

| CLC503AJE            | -40°C to +85°C    | 8-pin SOIC  |  |

| Package Thermal Resistance |                 |                 |  |

|----------------------------|-----------------|-----------------|--|

| Package                    | θ <sub>JC</sub> | θ <sub>JA</sub> |  |

| SOIC (AJE)                 | 65°C/W          | 90°C/W          |  |

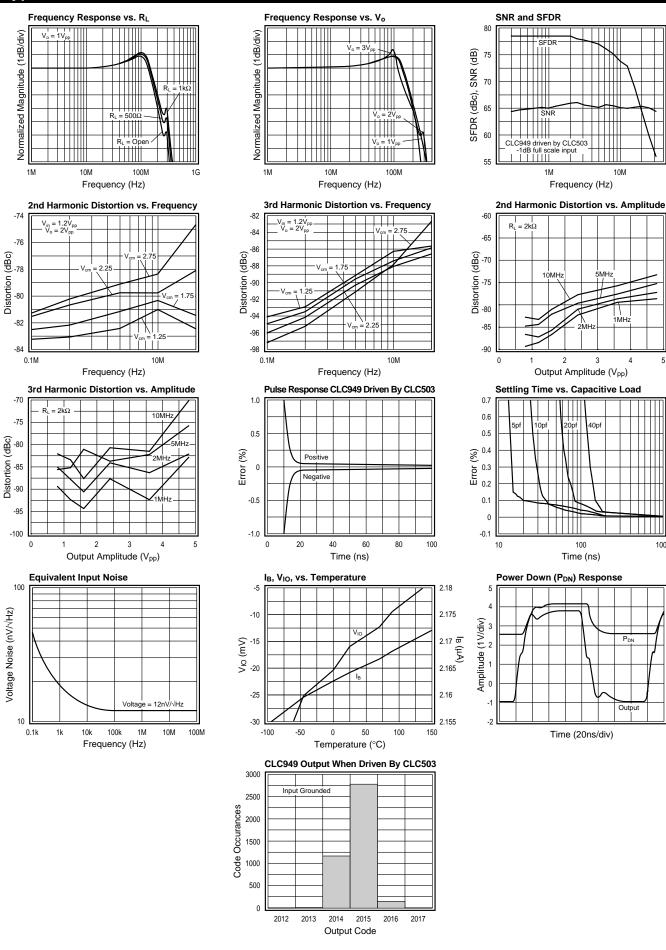

# Typical Performance Characteristics (V<sub>CC</sub> = + 5V, V<sub>EE</sub> = - 5V, V<sub>cm</sub> = 2.25V, C<sub>L</sub> = 5pF, V<sub>o</sub> = 4V<sub>pp</sub> unless specified)

http://www.national.com

10M

4

5

1000

PDN

Output

## **CLC503 APPLICATIONS**

#### APPLICATION CONSIDERATIONS

#### Theory of Operation

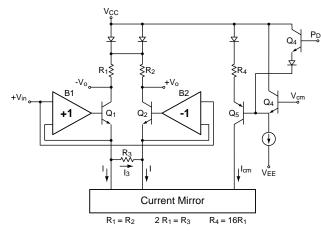

Figure 1 is a simplified schematic of the CLC503.

Figure 1: Simplified Block Diagram

The input voltage drives a unity gain buffer, B<sub>1</sub>, and an inverting buffer, B<sub>2</sub>. These buffers drive emitter followers, Q<sub>1</sub> and Q<sub>2</sub>. Resistor, R<sub>3</sub>, is the gain set resistor. The combination of B<sub>1</sub>, B<sub>2</sub>, Q<sub>1</sub>, Q<sub>2</sub> and R<sub>3</sub> form a transconductance stage. The input voltage across R<sub>3</sub> is converted to an in-phase and out-ofphase current through the collectors of Q<sub>1</sub> and Q<sub>2</sub>. The current through R<sub>3</sub> is:

$$I_{3} = \frac{2V_{in}}{R_{3}}$$

$$V_{odiff} = I_{3}R_{1} + I_{3}R_{2} \qquad R_{1} = R_{2}$$

$$V_{odiff} = I_{3}(2R_{1})$$

$$V_{odiff} = \frac{2V_{in}}{R_{3}}(2R_{1}) \qquad 2R_{1} = R_{3}$$

$$V_{odiff} = 2V_{in}$$

The common mode voltage across  $R_4$  is converted to a current. Transistor  $Q_5$  has a collector current equal to:

$$I_{cm} \approx \frac{V_{CC} - V_{cm} - V_{diode}}{R_4} \qquad R_4 = 16R_1$$

The common mode current is scaled and mirrored back to  $Q_1$  and  $Q_2$ . These currents, I, are converted back to a voltage at the collector load resistors,  $R_1$  and  $R_2$ . This forms the common-mode output voltage.

$$\frac{I = V_{CC} - V_{cm} - V_{diode}}{R_1}$$

$$V_{ocm} = V_{CC} - V_{diode} - R_1 I$$

$$I = 16I_{cm}$$

$$V_{ocm} = V_{cm}$$

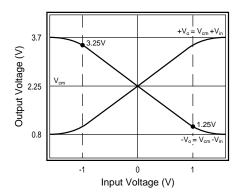

Figure 2 depicts the differential output voltage limits of the CLC503.

#### Figure 2: Differential Output Voltage

Centered around  $V_{\rm cm},$  the outputs are derived from the following equations.

$$\begin{aligned} +V_{o} &= V_{cm} + V_{in} \\ -V_{o} &= V_{cm} - V_{in} \\ V_{odiff} &= +V_{o} - (-V_{o}) = 2V_{in} \end{aligned}$$

The input to output relationship is shown in Figure 3.

| V <sub>in</sub>  | V <sub>odiff</sub> |

|------------------|--------------------|

| ±1V              | ±2V                |

| 2V <sub>pp</sub> | 4V <sub>pp</sub>   |

| ±1.4V max        | ±2.8V max          |

Figure 3: Input vs. Output Relationship

Pulling the power down line ( $P_{DN}$ ) high decreases the quiescent supply current. This turns off the current flowing in  $Q_5$ , and therefore  $Q_1$  and  $Q_2$ , allowing the output voltages to drift high, to approximately 4.3V. Since the signal is not significantly attenuated,  $P_{DN}$  does not effectively isolate the input from the output. This part is not recommended for use as a multiplexer. Refer to *Pin Descriptions - Power Down pin* - section. No damage occurs to the device when  $P_{DN}$  is high and the input is driven to the supply voltage.

#### **Pin Descriptions**

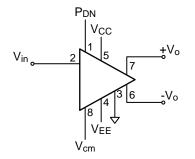

Figure 4: CLC503 Functional Pin Descriptions

#### ■ Pin 1

**Power Down (P<sub>DN</sub>):** The power down pin takes CMOS input levels. Use this to decrease the power from 250mW to 40mW. This is not a signal disable pin. A CMOS gate will drive this input. The quiescent supply current will be decreased when  $P_{DN}$  is at least 1V higher than  $V_{cm}$ . When the current is turned off, the output voltage  $V_o$ , will go to approximately 4.3V. An internal pull down resistor of 10k allows  $P_{DN}$  to be left open when not used.

#### Pin 2

**Input Voltage (V**<sub>in</sub>): This is the signal input. The recommended input range is  $\pm 1V$ . The linear operating range is approximately  $\pm 1.4V$  This input controls the differential output voltage. Because of the closed loop nature of the transconductance stage, the transfer function is highly linear. Refer to *Output Voltage* pin for output signal limitations.

### ■ Pin 3

Ground (GND): Tie to low impedance analog ground.

### Pins 4 and 5

**Power Supplies (V**<sub>EE</sub> and V<sub>CC</sub>): For optimum performance, use linear  $\pm 5V$  power supplies. Use bypass capacitors of  $0.1\mu$ F and  $6.8\mu$ F on the power supply lines to decrease any noise that could be injected into the circuit by the power supplies. Place the bypass capacitors as close to the device pins as possible. Remove the ground plane from the board underneath the device to eliminate parasitic capacitance. Refer to *Printed Circuit Board Layout* section for more layout suggestions.

#### Pins 6 and 7

**Output Voltage (-V<sub>o</sub> and +V<sub>o</sub>):** These are the differential signal output pins. The output voltage at these pins is limited to 0.7V to 3.9V. The output recovery time after exceeding these limits is approximately 40ns. The output voltage can be defined as:

$$\begin{aligned} +V_{o} &= V_{cm} + V_{in} \\ -V_{o} &= V_{cm} - V_{in} \\ V_{odiff} &= +V_{o} - (-V_{o}) = 2V_{in} \\ V_{ocm} &= \frac{+V_{o} - (-V_{o})}{2} = V_{cm} \end{aligned}$$

## ■ Pin 8

**Common-Mode Voltage (V<sub>cm</sub>):** This input sets the common-mode output operating points. The common mode input voltage can range from 1.5V to 3.5V. Refer to **Output Voltage** pin discussion for limitations on the output range.

## **Design Information**

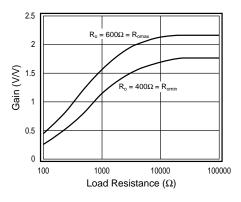

**Load:** The CLC503 is intended to drive high speed CMOS analog-to-digital converters, such as the CLC949. Resistive loading will affect the gain and common mode offset. It is not recommended to drive resistive loads below  $10k\Omega$  with this part. See Figure 5 for gain vs. load with specified range in device output resistance.

Figure 5: Gain vs. Resistive Load

**Settling Time:** The CLC503 settles to 0.1% in 15ns with a 5pF load, the input capacitance of the CLC949. Refer to the **Settling Time vs. Capacitive Load** plot in the **Typical Performance Characteristics** section.

### **Power Dissipation**

To calculate the power dissipation,  $P_T$ , for the CLC503, use the following equation:

$$P_{T} = I_{CC} \left( V_{CC} - V_{EE} \right)$$

## **Printed Circuit Board Layout**

The performance of the CLC503 is strongly dependent on proper layout, and adequate power supply decoupling. The parasitic capacitance at the output of the CLC503 and the input to the CLC949, or any other analog-to-digital converter, must be kept to a minimum. Consider the following guidelines:

- Use a ground plane.

- Bypass power supply pins with monolithic capacitors of 0.1µF and with 6.8µF tantalum capacitors. Place the capacitors less than 0.1" (3mm) from the pin.

- Remove the ground plane underneath the device and 0.1" (3mm) from all input/output pads.

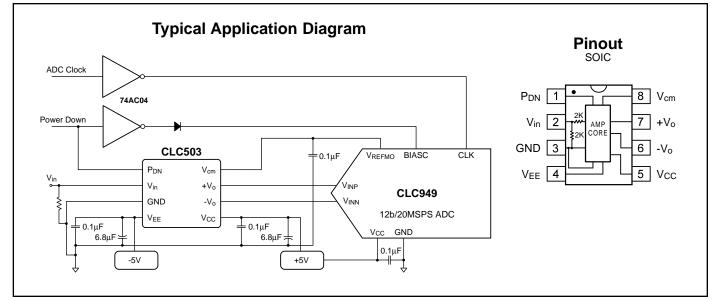

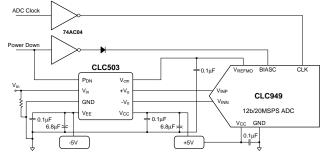

#### Interfacing the CLC503 with the CLC949

The CLC503 can be easily interfaced with the CLC949 as shown in Figure 6. An evaluation board is available for proto-typing and measurements.

#### Figure 6: Interfacing the CLC503 with the CLC949

#### Extended Use Considerations

Designed to drive the CLC949, the CLC503 can be used with other analog-to-digital converters. The user will want to consider the following parameters of the device that the CLC503 will drive.

- Input impedance of the A/D. Refer to Figure 5 for the Gain vs. Resistive Load. The CLC503 operates best when driving resistive loads greater than 10kΩ and capacitive loads of less than 10pF.

- Resistive loading will affect the gain and common mode offset. The gain setting resistors are fixed internally. The voltage gain equation is:

$$\mathsf{A}_{\mathsf{V}_{\mathsf{new}}} = \mathsf{A}_{\mathsf{V}_{\mathsf{old}}} \left( \frac{500\Omega \,||\,\mathsf{R}_{\mathsf{L}}}{500\Omega} \right)$$

where  $R_L$  equals the input resistance of the A/D. The impact of lower values of  $R_L$  is shown in Figure 5. The tolerance on the 500 $\Omega$  is ±20%.

Capacitive loading will affect the settling time. The settling time equation is:

$$t_{settle} = R_s \cdot C_L \cdot ln\left(\frac{100\%}{\% settling}\right)$$

where  $R_s = 250\Omega \pm 15\%$  and %settling  $\ge 0.1\%$ . Refer to the *Settling Time vs. Capacitive Load* plot in the *Typical Performance Characteristics* section.

- Other considerations

- Output signal swing must be within the specified output range.

- Common mode range must meet the specified common mode range.

- Distortion will be affected when V<sub>in</sub> and V<sub>cm</sub> drive the output out of the linear operating range.

#### **Customer Design Applications Support**

National Semiconductor is committed to design excellence. For sales, literature and technical support, call the National Semiconductor Customer Response Group at **1-800-272-9959** or fax **1-800-737-7018**.

#### Life Support Policy

National's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of National Semiconductor Corporation. As used herein:

- 1. Life support devices or systems are devices or systems which, a) are intended for surgical implant into the body, or b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe Fax: (+49) 0-180-530 85 86 E-mail: europe.support.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Francais Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block Ocean Centre, 5 Canton Road Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960

National Semiconductor

Japan Ltd.

Tel: 81-043-299-2309

Fax: 81-043-299-2408

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.