# CMX7045

## COMMUNICATION SEMICONDUCTORS AIS SART Processor

D/7045FI-1.x/4 February 2013

#### DATASHEET

Advance Information

#### 7045FI-1.x Marine AIS SART Processor

#### Features:

- Tx AIS GMSK Modem

- AIS SART Formatted Data

- Battery Monitor

- Flexible Tx Interface

- Configurable by Function Image™

- Two Auxiliary Clock Generators

- Two-Input Auxiliary (10-bit) ADC

- Four Auxiliary (10-bit) DACs

- Conforms to IEC 61097-14

- Integration Roadmap

- Low-Power (3.0V to 3.6V) Operation

- Low Profile 48-pin LQFP or VQFN

- 2-Point or I/Q Modulation

#### **Applications:**

- Automatic Identification System (AIS) Search And Rescue (SART) for Marine Safety

- Man Overboard (MOB) maritime survivor location device

- Personal Locator Beacon (PLB) tracking transmitter

#### 1 Brief Description

The CMX7045 is a dedicated processor for marine Automatic Identification System (AIS), Search and Rescue Transmitter (SART) operation, fully meeting the requirements of IEC 61097-14.

This highly integrated and flexible device includes a 9600 baud GMSK modem for transmission of formatted data. Additional auxiliary functions are also provided to further support the system host, these include: a two-input 10-bit Auxiliary ADC, four 10-bit Auxiliary DACs, two system clock outputs and four GPIOs

The CMX7045 offers low power sleep modes to ensure maximum system battery life and is available in a in a small 48-pin LQFP or VQFN package.

This Datasheet is the first part of a two-part document comprising Datasheet and User Manual: the User Manual can be obtained by registering your interest in this product with your local CML representative.

#### **CONTENTS**

| PIOCK DIS      | gram                                                  |  |

|----------------|-------------------------------------------------------|--|

| Signal/Pi      | 1 List                                                |  |

|                | nal Definitions                                       |  |

|                |                                                       |  |

| Recomme        | ended External Components                             |  |

| PCB Layo       | out Guidelines and Power Supply Decoupling            |  |

|                | Description                                           |  |

|                | rview                                                 |  |

| 6.2 AIS        | System Formats                                        |  |

| Detailed I     | Description                                           |  |

|                | k Source                                              |  |

|                | t Interface                                           |  |

|                | ction Image™ Load and Activation                      |  |

| 7.3.1          | FI Loading from Host Controller                       |  |

|                | tem Description and Tasks                             |  |

| 7.4.1          | Signal Routing                                        |  |

| 7.4.2          | Operating Modes                                       |  |

| 7.4.3          | Modem and Data Units                                  |  |

| 7.4.4          | Timing and Synchronisation                            |  |

| 7.4.5          | Tx Timing                                             |  |

| 7.4.6          | AuxADC1-2                                             |  |

| 7.4.7          | AuxDAC1-4                                             |  |

| 7.4.8          | Interrupt Operation                                   |  |

| 7.4.9          | Deep Sleep Mode                                       |  |

| 7.5 Ope        | ration of Tasks                                       |  |

| 7.5.1          | Tx Task Operation  Registers and Buffers for Tx Tasks |  |

| 7.5.2          | Write Data Registers                                  |  |

| 7.5.3<br>7.5.4 | Data Tasks                                            |  |

| 7.5.4<br>7.5.5 | Modem Tasks and Codes                                 |  |

|                | nsmission Format                                      |  |

| 7.6.1          | Transmit Tasks                                        |  |

| 7.6.1          | AIS Burst Mode Transmit                               |  |

| 7.6.2          | Transmit Example                                      |  |

| 7.6.4          | AIS Raw Mode Transmit                                 |  |

| 7.6.5          | Transmitter Timing Control                            |  |

| 7.6.6          | Modulation Formats                                    |  |

|                | figuration Tasks and Codes                            |  |

|                | tem Clock Synthesisers                                |  |

|                | versave                                               |  |

|                | US Register Summary                                   |  |

| Performa       | nce Specification                                     |  |

|                | trical Performance                                    |  |

| 8.1.1          | Absolute Maximum Ratings                              |  |

| 8.1.2          | Operating Limits                                      |  |

| 8.1.3          | Operating Characteristics                             |  |

|                | Parametric Performance                                |  |

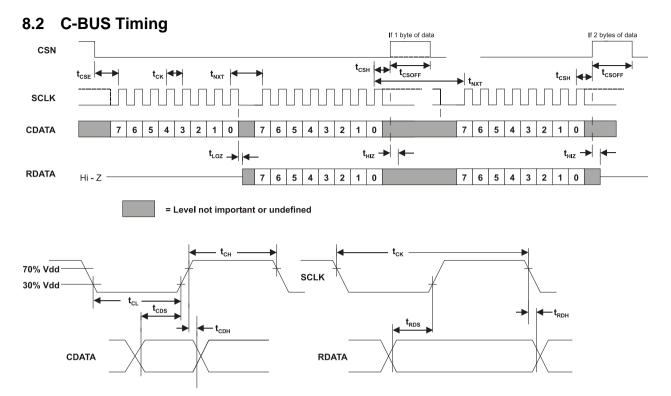

| 8.2 C-BUS Timing                                          | 34 |

|-----------------------------------------------------------|----|

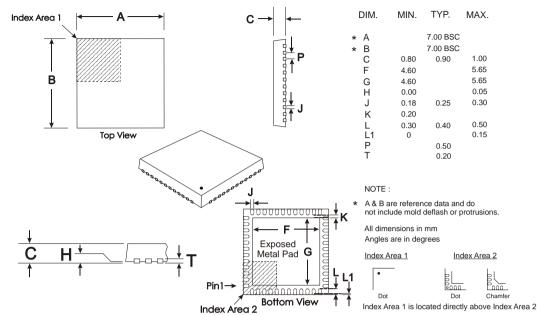

| 8.3 Packaging                                             | 35 |

|                                                           |    |

| TABLES                                                    |    |

| Table 1 Definition of Power Supply and Reference Voltages | 8  |

| Table 2 Component Values                                  | 9  |

| Table 3 Data Tasks                                        | 20 |

| Table 4 Modem Tasks                                       | 20 |

| Table 5 AIS Burst Transmit Example                        | 22 |

| Table 6 Tx Sequence events                                | 23 |

| Table 7 Example Tx Event Sequence Setup                   | 24 |

| Table 8 Tx Spectrum Masks                                 | 25 |

| Table 9 Configuration Tasks                               | 26 |

| Table 10 C-BUS Registers                                  | 28 |

|                                                           |    |

| FIGURES                                                   |    |

| Figure 1 Block Diagram                                    | 5  |

| Figure 2 Recommended External Components                  | g  |

| Figure 3 Power Supply Connections and De-coupling         | 10 |

| Figure 4 C-BUS Transactions                               | 12 |

| Figure 5 FI Loading from Host                             | 14 |

| Figure 6 State Diagram                                    | 15 |

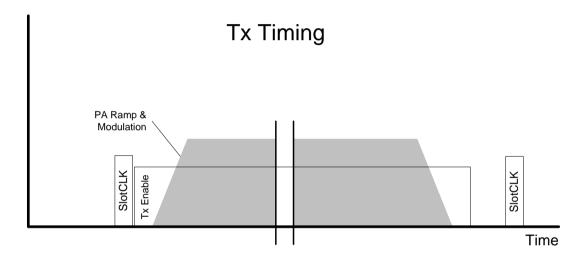

| Figure 7 Tx Burst Timing                                  | 17 |

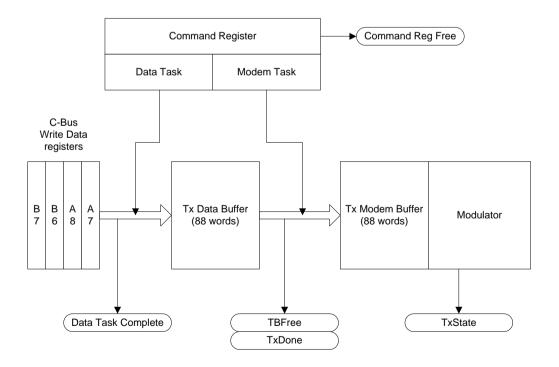

| Figure 8 Tx Task Operation                                | 18 |

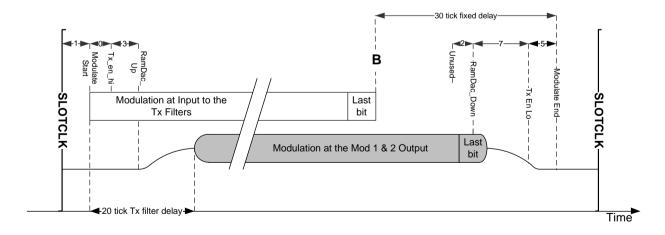

| Figure 9 Typical AIS Transmission                         | 23 |

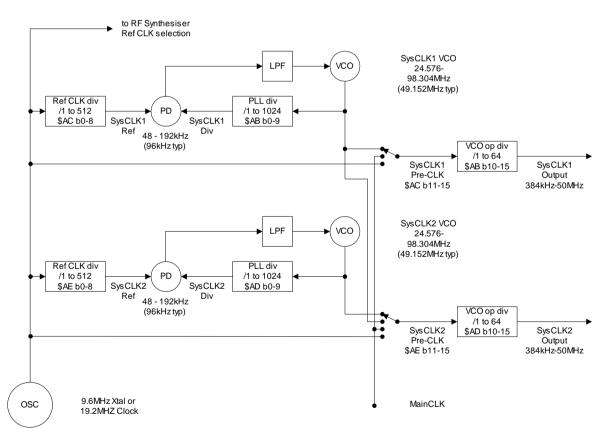

| Figure 10 System Clock Generation                         | 26 |

| Figure 11 C-BUS Timing                                    | 34 |

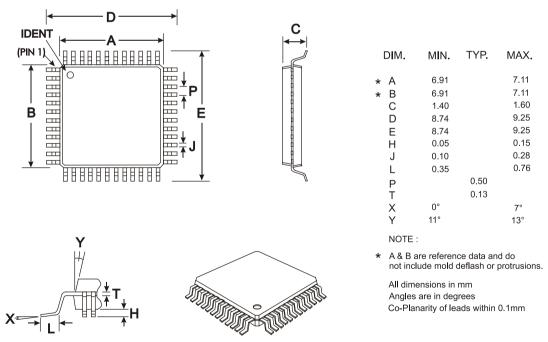

| Figure 12 Mechanical Outline for 48-pad VQFN Package (Q3) | 35 |

| Figure 13 Mechanical Outline for 48-pin LQFP Package (L4) | 35 |

It is always recommended that you check for the latest product datasheet version from the Datasheets page of the CML website: [www.cmlmicro.com].

#### **HISTORY**

| Version | Changes                                                                                                                                                                                                                      | Date     |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4       | New State Diagram (Fig.6)                                                                                                                                                                                                    | Feb 2012 |

|         | <ul> <li>Updated supporting text in Section 7.4.2, Operating Modes</li> </ul>                                                                                                                                                |          |

|         | General reset description enhanced                                                                                                                                                                                           |          |

|         | <ul> <li>Deep Sleep mode description enhanced and described as a<br/>configuration mode</li> </ul>                                                                                                                           |          |

|         | Status 2 description updated                                                                                                                                                                                                 |          |

|         | <ul> <li>Man Overboard (MOB) and Personal Locator Beacon (PLB) added to list<br/>of applications at front of datasheet.</li> </ul>                                                                                           |          |

|         | <ul> <li>System diagram on first page of datasheet edited to show correct signal direction for battery monitor</li> </ul>                                                                                                    |          |

|         | <ul> <li>SLOTCLKOP added to Timing and Synchronisation description, Section<br/>7.4.4</li> </ul>                                                                                                                             |          |

|         | <ul> <li>DataWordWriteN_Tx task added to Table 3 (Data Tasks)</li> </ul>                                                                                                                                                     |          |

|         | <ul> <li>Section 7.5.5 (Modem tasks and Codes), reference to Rx modem tasks<br/>removed.</li> </ul>                                                                                                                          |          |

|         | <ul> <li>Section 9.12 (Command Register) sub-paragraph levels restructured to improve clarity</li> </ul>                                                                                                                     |          |

|         | Minor editorial changes and correction of typographical errors                                                                                                                                                               |          |

| 3       | Clarification of "Leave Deep Sleep" command                                                                                                                                                                                  | Oct 2012 |

|         | <ul> <li>Clarify that CMX7045 is capable of I/Q or 2-point modulation</li> </ul>                                                                                                                                             |          |

|         | <ul> <li>Added a state-transition diagram (new Fig 6)</li> </ul>                                                                                                                                                             |          |

|         | <ul> <li>Removal of CSTDMA operation from section 9.10</li> </ul>                                                                                                                                                            |          |

|         | Correction of minor typographical errors                                                                                                                                                                                     | 1 0010   |

| 2       | <ul> <li>Section 7.5.4, Table 3. Rows of table relating to Rx data buffer deleted.</li> <li>Section 7.6.1: Description of Transmit AIS Burst - Sense of bit 5 in the Command register (\$C8) changed from 0 to 1.</li> </ul> | Aug 2012 |

|         | <ul> <li>Section 7.6.5; Transmitter Timing Control – new Figure 8 replaces<br/>previous version.</li> </ul>                                                                                                                  |          |

|         | <ul> <li>Section 7.6.5: Transmitter Timing Control, Table 6. Delay from end of<br/>modulation corrected from 20 ticks to 30 ticks.</li> </ul>                                                                                |          |

|         | <ul> <li>Section 7.6.5; Transmitter Timing Control, Table 7. Total delay times<br/>corrected.</li> </ul>                                                                                                                     |          |

|         | Section 9.12: Command Register \$C8, Modem Tasks:                                                                                                                                                                            |          |

|         | <ul> <li>\$2B changed to \$2A, sense of bit 0 changed from 1 to 0</li> </ul>                                                                                                                                                 |          |

|         | <ul> <li>\$0B changed to \$2B, sense of bit 5 changed from 0 to 1</li> </ul>                                                                                                                                                 |          |

| 1       | Initial release                                                                                                                                                                                                              | Oct 2011 |

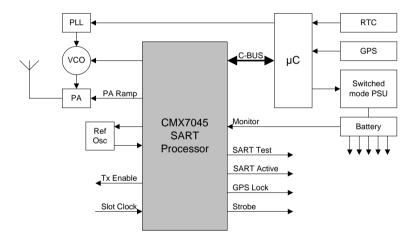

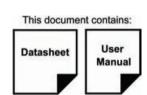

#### 2 Block Diagram

Figure 1 Block Diagram

### 3 Signal/Pin List

| CMX7045<br>Q3 or L4 | Pin<br>Name | Туре | Description                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------------|-------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1                   | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 2                   | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 3                   | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 4                   | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 5                   | -           | IP   | Connect to DV <sub>DD.</sub>                                                                                                                                                                                                                                                                   |  |  |  |  |

| 6                   | -           | IP   | Connect to DV <sub>DD.</sub>                                                                                                                                                                                                                                                                   |  |  |  |  |

| 7                   | DVSS        | PWR  | Digital Ground.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 8                   | IRQN        | OP   | C-BUS: A 'wire-ORable' output for connection to the Interrupt Request input of the host. Pulled down to DVss when active and is high impedance when inactive. An external pull-up resistor (R1) is required.                                                                                   |  |  |  |  |

| 9                   | VDEC        | PWR  | Internally generated 2.5V digital supply voltage. Must be decoupled to DVSS by capacitors mounted close to the device pins. No other connections allowed.                                                                                                                                      |  |  |  |  |

| 10                  | SLOTCLK     | ΙP   | Slot clock from host (37.5Hz).                                                                                                                                                                                                                                                                 |  |  |  |  |

| 11                  | CS-SYNC     | OP   | Slot Sync.                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 12                  | SLTCLKOP    | OP   | Slot clock output.                                                                                                                                                                                                                                                                             |  |  |  |  |

| 13                  | SYSCLK1     | OP   | Synthesised Digital System Clock Output 1.                                                                                                                                                                                                                                                     |  |  |  |  |

| 14                  | DVSS        | PWR  | Digital Ground.                                                                                                                                                                                                                                                                                |  |  |  |  |

| 15                  | TXENA       | OP   | Enable for external Tx hardware.                                                                                                                                                                                                                                                               |  |  |  |  |

| 16                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 17                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 18                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 19                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 20                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 21                  | -           | NC   | reserved – do not connect.                                                                                                                                                                                                                                                                     |  |  |  |  |

| 22                  | AVSS        | PWR  | Analogue Ground.                                                                                                                                                                                                                                                                               |  |  |  |  |

| 23                  | MOD1        | OP   | Modulator 1 output.                                                                                                                                                                                                                                                                            |  |  |  |  |

| 24                  | MOD2        | OP   | Modulator 2 output.                                                                                                                                                                                                                                                                            |  |  |  |  |

| 25                  | VBIAS       | OP   | Internally generated bias voltage of about AV <sub>DD</sub> /2, except when the device is in 'Powersave' mode when V <sub>BIAS</sub> will discharge to AV <sub>SS</sub> . Must be decoupled to AV <sub>SS</sub> by a capacitor mounted close to the device pins. No other connections allowed. |  |  |  |  |

| 26                  | -           | NC   | reserved- do not connect this pin.                                                                                                                                                                                                                                                             |  |  |  |  |

| CMX7045<br>Q3 or L4  | Pin<br>Name | Туре  | Description                                                                                                                                                                                |  |  |  |

|----------------------|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 27                   | -           | NC    | reserved- do not connect.                                                                                                                                                                  |  |  |  |

| 28                   | -           | NC    | reserved – do not connect.                                                                                                                                                                 |  |  |  |

| 29                   | ADC1        | IP    | AuxADC input 1.                                                                                                                                                                            |  |  |  |

| 30                   | ADC2        | IP    | AuxADC input 2.                                                                                                                                                                            |  |  |  |

| 31                   | AVDD        | PWR   | Analogue +3.3V supply rail. Levels and thresholds within the device are proportional to this voltage. This pin should be decoupled to AVSS by capacitors mounted close to the device pins. |  |  |  |

| 32                   | DAC1        | OP    | AuxDAC1 output/RAMDAC.                                                                                                                                                                     |  |  |  |

| 33                   | DAC2        | OP    | AuxDAC2 output.                                                                                                                                                                            |  |  |  |

| 34                   | AVSS        | PWR   | Analogue Ground.                                                                                                                                                                           |  |  |  |

| 35                   | DAC3        | OP    | AuxDAC3 output3.                                                                                                                                                                           |  |  |  |

| 36                   | DAC4        | OP    | AuxDAC4 output4.                                                                                                                                                                           |  |  |  |

| 37                   | DVSS        | PWR   | Digital Ground.                                                                                                                                                                            |  |  |  |

| 38                   | VDEC        | PWR   | Internally generated 2.5V supply voltage. Must be decoupled to DVSS by capacitors mounted close to the device pins.                                                                        |  |  |  |

| 39                   | XTAL/CLK    | IP    | 19.2MHz input from the external clock source or 9.6MHz Xtal.                                                                                                                               |  |  |  |

| 40                   | XTALN       | OP    | The output of the on-chip 9.6MHz Xtal oscillator inverter. NC if 19.2MHz clock is used.                                                                                                    |  |  |  |

| 41                   | DVDD        | PWR   | Digital +3.3V supply rail. This pin should be decoupled to DVSS by capacitors mounted close to the device pins.                                                                            |  |  |  |

| 42                   | CDATA       | IP    | C-BUS: Command Data. Serial data input from the μC.                                                                                                                                        |  |  |  |

| 43                   | RDATA       | TS OP | C-BUS: Reply Data. A 3-state C-BUS serial data output to the $\mu$ C. This output is high impedance when not sending data to the $\mu$ C.                                                  |  |  |  |

| 44                   | -           | NC    | reserved – do not connect this pin.                                                                                                                                                        |  |  |  |

| 45                   | DVSS        | PWR   | Digital Ground.                                                                                                                                                                            |  |  |  |

| 46                   | SCLK        | IP    | C-BUS: The C-BUS serial clock input from the μC.                                                                                                                                           |  |  |  |

| 47                   | SYSCLK2     | OP    | Synthesised Digital System Clock Output 2.                                                                                                                                                 |  |  |  |

| 48                   | CSN         | IP    | C-BUS: The C-BUS chip select input from the μC.                                                                                                                                            |  |  |  |

| EXPOSED<br>METAL PAD | SUB         | ~     | The central metal pad may be connected to Analogue Ground (AVSS) or left unconnected.  No other electrical connection is permitted.                                                        |  |  |  |

#### Notes:

IP = Input (+PU/PD = internal pullup/pulldown resistor)

OP = Output

TS OP = 3-state Output

PWR = Power Supply Connection

NC = No Connection

### 3.1 Signal Definitions

#### Table 1 Definition of Power Supply and Reference Voltages

| Signal<br>Name    | Pins  | Usage                                                                            |

|-------------------|-------|----------------------------------------------------------------------------------|

| AV <sub>DD</sub>  | AVDD  | Power supply for analogue circuits.                                              |

| DV <sub>DD</sub>  | DVDD  | Power supply for digital circuits.                                               |

| V <sub>DEC</sub>  | VDEC  | Power supply for core logic, derived from DV <sub>DD</sub> by on-chip regulator. |

| V <sub>BIAS</sub> | VBIAS | Internal analogue reference level, derived from AV <sub>DD</sub> .               |

| AV <sub>SS</sub>  | AVSS  | Ground for all analogue circuits.                                                |

| DV <sub>SS</sub>  | DVSS  | Ground for all digital circuits.                                                 |

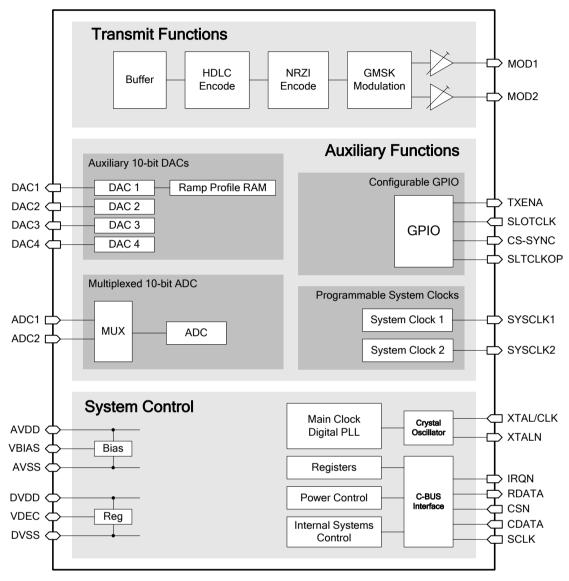

#### 4 Recommended External Components

Figure 2 Recommended External Components

#### **Table 2 Component Values**

| R1 | 100k $\Omega$ | C2 | 18pF  | C17 | 10µF | C22 | 10nF       |

|----|---------------|----|-------|-----|------|-----|------------|

| R2 | 220k $Ω$      | C3 | 10nF  | C18 | 10nF | C23 | 10nF       |

| R3 | 100k $\Omega$ | C7 | 100nF | C19 | 10nF | C24 | 10μF       |

| R4 | 100k $\Omega$ | C8 | 100pF | C20 | 10µF | X1  | 9.6MHz     |

| C1 | 18pF          | C9 | 100pF | C21 | 10nF |     | See note 1 |

Resistors  $\pm 5\%$ , capacitors and inductors  $\pm 20\%$  unless otherwise stated.

#### Notes:

- 1. X1 can be a 9.6MHz crystal or a 19.2MHz external clock generator. The tracks between the crystal and the device pins should be as short as possible to achieve maximum stability and best start up performance.

- 2. A single 10µF electrolytic capacitor (C24, fitted as shown) may be used for smoothing the power supply to both VDEC pins, providing they are connected together on the pcb with an adequate width power supply trace. Alternatively, separate smoothing capacitors should be connected to each VDEC pin. High frequency decoupling capacitors (C3 and C23) must always be fitted as close as possible to both VDEC pins.

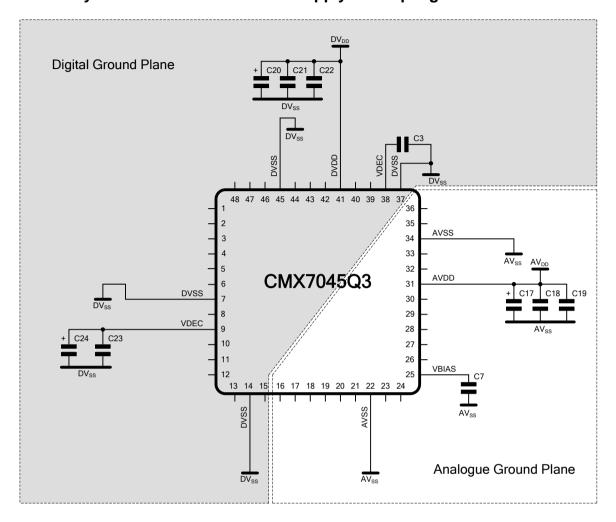

#### 5 PCB Layout Guidelines and Power Supply Decoupling

Figure 3 Power Supply Connections and De-coupling

Component values as per Table 2.

#### Notes:

- The supply decoupling capacitors should be as close as possible to the CMX7045. It is therefore

recommended that the printed circuit board is laid out with separate ground planes for the AV<sub>SS</sub> and DV<sub>SS</sub>

supplies in the area of the CMX7045, with provision to make links between them, close to the CMX7045.

Use of a multi-layer printed circuit board will facilitate the provision of ground planes on separate layers.

- 2. The central metal pad on the 'Q3' package may be electrically unconnected or, alternatively, may be connected to Analogue Ground ( $AV_{SS}$ ). No other electrical connection is permitted.

- 3. V<sub>BIAS</sub> is used as an internal reference for detecting and generating the various analogue signals. It must be carefully decoupled to ensure its integrity so, apart from the decoupling capacitor shown, no other loads should be connected. If V<sub>BIAS</sub> needs to be used to set the discriminator mid-point reference, it must be buffered with an external high input impedance buffer.

#### 6 General Description

#### 6.1 Overview

#### **Tx Modem Functions**

- AIS 25kHz channel (GMSK, 9600bps, 2.4kHz deviation, BT = 0.4)

- AIS Burst mode with full AIS frame formatting (HDLC-type)

- Bit stuffing

- NRZI coding

- Training sequence and start/stop flag insertion

- CRC generation

- AIS Raw mode (for greater flexibility)

- o Supports arbitrary data streams for user-defined protocols

- 160-byte (equivalent to 5 AIS slots) Tx Data Buffer

- Flexible Tx Interface

- Two-point modulation outputs, with independent gain and polarity controls

#### **Analogue I/O Functions**

- Auxiliary ADC system

- A two-input 10-bit successive approximation ADC with integrated sample and hold AuxADC1-2

- Auxiliary DAC system

- Four general purpose auxiliary 10-bit DACs, AuxDAC1-4

- Ramping auxiliary DAC, RAMDAC (using AuxDAC1)

- RAMDAC steps through a user-configured sequence of DAC output values to develop a specific rising/falling output signal. This is useful for ramping an RF PA, and can be configured to operate automatically at the start and end of a burst.

#### **System Functions**

- All internal subsystems are controlled via a single serial host interface to reduce host μC pin count and simplify external host driver complexity.

- Transaction oriented command/response logical host interface executes tasks supporting normal operation, device configuration, and functions to assist manufacturing calibration trimming of external circuits.

- Internal system clock derived from reference oscillator and eliminates the need for additional XTAL or baseband clock oscillator.

- System Clock Synthesisers generate two clocks for external use to support peripheral devices.

- Function Image<sup>™</sup> is loaded directly from the host µC via C-BUS.

- Integrated 2.5V regulator can develop 2.5V from required 3.3V supply.

- Powersave facilities minimise total system power.

#### 6.2 AIS System Formats

The AIS system uses two basic channel access mechanisms: Self Organising Time Division Multiple Access (SOTDMA) and Carrier-Sensing Time Division Multiple Access (CSTDMA). The CMX7045 is compatible with both systems and offers additional features which simplify the implementation of an AIS SART device conforming to IEC 61097-14.

The relevant International standards are:

| [0] | ITU-R M.1371-4                 |

|-----|--------------------------------|

| [1] | IEC 61993-2 Class A            |

| [2] | IEC 62287-1 Class B CSTDMA     |

| [3] | IEC 62287-2 Class B SOTDMA     |

| [4] | IEC 62320-1 Base Station       |

| [5] | IEC 62320-2 Aids to Navigation |

| [6] | IEC 61097-14 AIS-SART          |

|     |                                |

#### 7 **Detailed Description**

#### **Clock Source**

The CMX7045 can be used with either a 9.6MHz xtal or a 19.2MHz oscillator.

#### 7.2 Host Interface

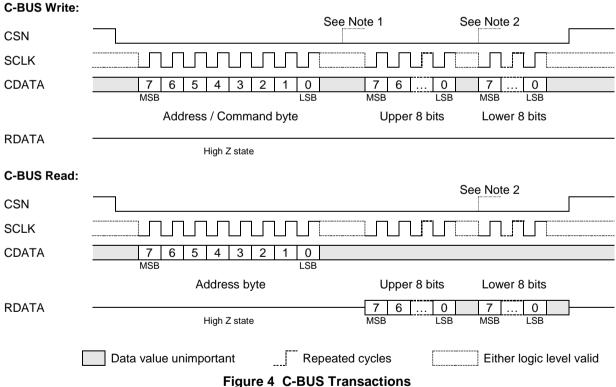

This section provides a general description of the C-BUS serial interface protocol used to transfer data. control and status information between the CMX7045 and its host.

C-BUS is a serial interface, similar to SPI, that uses a simple transaction-oriented command/response protocol with addressing to access specific registers within the CMX7045. Each C-BUS transaction consists of a single Register Address/Command byte (A/C byte) sent from the µC which may be followed by one or more data byte(s) sent from the µC to be written into one of the CMX7045's Write Only registers, or one or more data byte(s) read out from one of the CMX7045's Read Only registers, as illustrated in Figure 4.

Data sent from the uC on the CDATA line is clocked into the CMX7045 on the rising edge of the SCLK input. RDATA sent from the CMX7045 to the uC is valid when the SCLK is high. The CSN line must be held low during a data transfer and kept high between transfers. The C-BUS interface is compatible with most common µC serial interfaces and may also be easily implemented with general purpose µC I/O pins controlled by a simple software routine.

The number of data bytes following an A/C byte is dependent on the value of the A/C byte. The most significant bit of the address or data is sent first. For detailed timings see section 8.2.

#### Notes:

- For Command byte transfers only the first 8 bits are transferred. 1.

- For single byte data transfers only the first 8 bits of the data are transferred. 2.

- The CDATA and RDATA lines are never active at the same time. The Address byte determines the data 3. direction for each C-BUS transfer.

- The SCLK input can be high or low at the start and end of each C-BUS transaction. 4.

- The gaps shown between each byte on the CDATA and RDATA lines in the above diagram are optional, the host may insert gaps or concatenate the data as required.

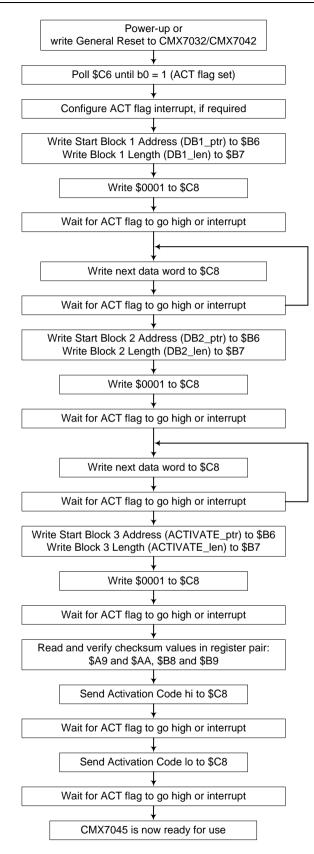

#### 7.3 Function Image™ Load and Activation

The Function Image™ (FI) file, which defines the operational capabilities of the device, may be obtained from the CML Technical Portal, following registration. This is in the form of a 'C' header file which can be included into the host controller software. The Function Image™ data file is no more than 24kbytes.

Once the FI has been loaded, the CMX7045 performs these actions:

- (1) The product identification code (\$7045) is reported in C-BUS register \$C5

- (2) The FI version code is reported in C-BUS register \$C9

- (3) The two 32-bit FI checksums are reported in C-BUS register pairs \$A9, \$AA and \$B8, \$B9

- (4) The device waits for the host to load the 32-bit Device Activation Code to C-BUS register \$C8

- (5) Once activated, the device initialises fully, enters Deep Sleep mode and becomes ready for use. The Activation Register Ready (ACT) flag (bit 0 of the Status register) will be set

- (6) Once the Deep Sleep bit (Status2 b:13) has been set, the host may then power down the Analogue sections of the device to minimise power consumption (typically while the host is waiting for the external GPS to output a valid position fix)

- (7) When the host decides that the device should be returned to active mode in order to configure the device or transmit an AIS burst, it should first power-up the Analogue sections and then send the "Leave Deep Sleep" command.

The checksums should be verified against the published values to ensure that the FI has loaded correctly. Once the FI has been activated, the checksum, product identification and version code registers are cleared and these values are no longer available. If an invalid Activation code is loaded, the device will report the value \$DEAD in register \$A9 and become unresponsive to all further host commands (including General Reset). A power-on reset is required to recover from this state.

Both the Device Activation Code and the checksum values are available from the CML Technical Portal.

Following a General Reset, reloading of the FI is required.

#### 7.3.1 FI Loading from Host Controller

The FI is downloaded into the CMX7045 at power-up over the C-BUS interface. Wait for the ACT flag to be set (Status register \$C6 bit 0), then the data can then be sent directly over the C-BUS to the CMX7045.

Each time the device is powered up or reset, its FI must first be loaded and then activated. These two steps assign internal device resources and determine all device features. The device does not operate until the FI is loaded and activated.

The download time is limited by the clock frequency of the C-BUS, with a 5MHz SCLK, it should take less than 500ms to complete.

Figure 5 FI Loading from Host

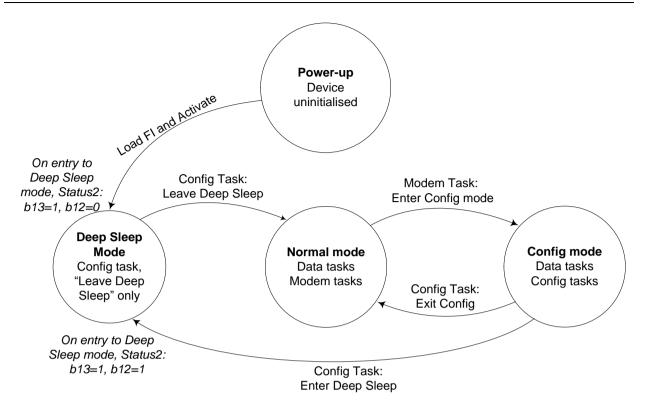

Figure 6 State Diagram

#### 7.4 System Description and Tasks

This section describes the operation of main sections of the CMX7045 and the task-oriented logical interface provided to the external host device.

#### 7.4.1 Signal Routing

The Tx Modulation output signals may be configured to be suitable for two-point modulation circuits. Signal levels on both output pins, MOD1 and MOD2, can be set to within 0.2dB using a Configuration Task. I/Q modulation circuits are also supported, see section 9.12.2.1 in the User Manual.

#### 7.4.2 Operating Modes

The CMX7045 operates in either:

- Deep Sleep Mode

- Configuration mode

- Normal mode

Deep Sleep mode puts the device into a low-power standby mode to minimize power consumption. Whilst in this mode the host can switch off unneeded analogue functionality. Once the device has been activated, it will enter Deep Sleep mode automatically. "Leave Deep Sleep" is a Configuration Task that switches the device to Normal mode. To go back to Deep Sleep mode it is necessary to issue the Modem Task, "Enter Config Mode" and then, from Configuration mode, issue Configuration Task "Enter Deep Sleep mode".

Configuration mode is used to set up various operating parameters of the CMX7045 subsystems, e.g. Transmit format, timing parameters etc. following a power-up or reset. The modem section is disabled when the device is in Configuration mode. Configuration mode uses dedicated tasks that are not valid whilst in Normal mode.

Normal mode is used when actively running the CMX7045 modem and other subsystems. Normal mode uses dedicated tasks that are not valid whilst in Configuration mode.

"Enter Config Mode" is a Modem Task that switches the device from Normal to Configuration mode. "Exit Config Mode" is a Configuration Task that switches the device from Configuration to Normal mode, as shown in Figure 6.

.

#### 7.4.3 Modem and Data Units

The CMX7045 is logically divided into two main units which can accept and perform tasks separately:

- Modem Unit

- Data Unit

The Modem Unit is primarily responsible for processing tx data from the internal Tx Data Buffer, presenting it on the MOD1 and MOD2 pins.

The Data Unit is primarily responsible for transferring data between the internal Tx Data Buffers or subsystems and the C-BUS Write/Read Data registers, from where they can be accessed by the host  $\mu$ C.

When the device is in Normal mode, the Command register, \$C8, is a 16-bit C-BUS write register that contains task fields for both Data and Modem units. A task is invoked by writing its code into the Data Task or Modem Task fields. A single C-BUS write transaction will change all Command register fields. Often, the host will only want to issue either a Data or Modem Task, in which case it should ensure that the other task field is set to all zeroes, corresponding to a null/idle task. Sometimes it is useful to issue Data and Modem Tasks simultaneously, in which case, the Data Task will always be completed before the Modem Task is started.

Certain internal subsystems can be directly accessed and controlled via C-BUS transactions, without issuing a specific task/command.

#### 7.4.4 Timing and Synchronisation

The CMX7045 requires a Slot Clock (SLOTCLK) input from the host  $\mu$ C. This should be a pulse at least 50 $\mu$ s long, whose rising edge is aligned to the AIS Slot boundary. An edge is required at the start of every AIS slot or frame, hence the frequency of this signal is 37.5Hz or 0.5Hz<sup>1</sup>. The internal SLOTCLK is output as a pulse on the SLOTCLKOP pin.

The CMX7045 has several features to assist the host  $\mu$ C with timing, which are detailed below. All of these features are based on the SLOTCLK signal, provided by the host to the CMX7045's SLOTCLK pin. All timings are defined as a number of 24kHz "ticks" referenced to the rising edge of the SLOTCLK signal.

#### 7.4.5 Tx Timing

The CMX7045 can be configured to perform a sequence of events when a TXB or TDBS task (transmit burst) is issued. The events are: start and end of modulation, ramping the RAMDAC up and down, asserting and releasing a digital output pin (intended as a Tx Enable) and CSTDMA sensing. Each of these can be configured to happen with specified delays from the rising edge of the SLOTCLK. The timings are set up with the Configuration Mode task, Tx\_Sequence. See User Manual section 9.12.2.3 for details.

Figure 7 Tx Burst Timing

#### 7.4.6 AuxADC1-2

The ADC is available for user defined functions. The AuxADC runs continuously, the input is selected by the ADC Input Select bits in the C-BUS Mode register, \$C1 and the results of the conversion are presented in ADC Data C-BUS register \$C9. This register also includes a bit field to indicate which input was selected when this conversion was executed.

#### 7.4.7 AuxDAC1-4

The four DACs can be updated in any combination using the DAC\_Write Data Task. See User Manual 9.12. In addition, AuxDAC1 can be configured as a RAMDAC to output a series of values as part of the transmit timing sequence. The values and the rate at which they change are set-up using a Configuration mode task.

#### 7.4.8 Interrupt Operation

The CMX7045 will issue an interrupt on the IRQN line when the IRQ bit (bit 15) of the Status register and the IRQ Mask bit (bit 15) are both set to 1. User Manual section 9.14 describes the situations which

<sup>&</sup>lt;sup>1</sup> If the host supplies a 0.5Hz signal, this should be aligned to the even UTC second and the selection of X1 should be chosen to maintain correct timing between SLOTCLK pulses.

cause the IRQ bit to change from a 0 to a 1. The IRQN pin is an open collector output that requires an external pull-up resistor.

#### 7.4.9 Deep Sleep Mode

Deep Sleep mode (entered through Configuration mode or after the Activation code has been successfully loaded) puts the device into a static state where all signal processing and clocks are stopped and only the C-BUS remains active. In this mode, the  $I_{DD}$  drops to the lowest level, as specified in section 8.1.3, and is thus suitable for use in AIS SART, where it is essential for the host  $\mu C$  to switch off the CMX7045 at known times. See User Manual section 9.12.2.6.

#### 7.5 Operation of Tasks

This section describes Modem and Data Tasks. Understanding their operation requires knowledge of the internal buffering of the CMX7045.

Tx data is double buffered. The Tx channel has a Tx Data Buffer. The host µC accesses the Tx Data Buffer via the C-BUS Write Data registers and the modulator directly accesses the Tx Data Buffer. Tasks transfer data between the Tx Data Buffer and the C-BUS registers.

#### 7.5.1 Tx Task Operation

Typical stages of Tx task operation are depicted in Figure 8 and occur as follows:

- 1. The host writes up to 4 words of data for transmission into the C-BUS Write Data registers.

- 2. The host writes the Command register, specifying a Data Task. This results in transfer of the data from the Write Data registers into the Tx Data Buffer.

- 3. Steps 1 and 2 can be repeated to load the Tx Data Buffer with a large block of data.

- 4. A Modem Task can then be used to instruct the Tx Modulator to transmit the data in the Tx Data Buffer. This causes the content of the Tx Data Buffer to be coded and CRC'd (if in burst mode) and transmitted to the MOD1 and MOD2 output pins.

- 5. Once the system is up and running any Modem Task may potentially take some time to execute as it may have to wait for the previous task to complete.

Figure 8 Tx Task Operation

#### 7.5.2 Registers and Buffers for Tx Tasks

- Command register: Contains Data and Modem Task fields as described above.

- Status register: Contains bits that indicate when tasks are complete, which can interrupt the host:

- o Command Reg Free

- o TBFREE

- o TxDONE

- Config Task Complete

- Data Task Complete.

- Interrupt Mask: Host write register to specify which status bit can cause an interrupt.

- Write Data registers 0-3: Contain data written from host μC to transmit via the Tx Modulator.

- **Tx Data Buffer**: The Tx data is double buffered, which allows the host µC to write to the Tx Data Buffer while the modulator is simultaneously transmitting data it reads from the Tx Modem Buffer. Each buffer is capable of holding one full (5-slot) AIS message.

#### 7.5.3 Write Data Registers

An array of four, 16 bit, C-BUS write registers form the C-BUS Write Data registers.

The device reads and acts upon the content of the Write Data registers as instructed by the Data Task bits of the Command register while in transmit mode. Generally, they may be written at any time by the host  $\mu$ C with no effect on internal device operation. When a Data task is issued the Write Data registers will be read by the device and so should not be modified by the host  $\mu$ C until the Data Task Complete bit is set in the Status register.

Data Tasks access the Write Data registers as a number of words (1 to 4) or as a number of bits (1 to 16 in \$A7), however if a bit-format Data Task is used it must be the final Data Task issued in a multi-data transfer from the host. The next Data Task issued should be a DataWordResetN\_Tx or DataBitResetN\_Tx to re-initialise the Tx Data Buffer pointer (a bit-format Data Task is usually used as the last transfer of a data block that is not a complete number of words in length).

#### Word-format:

| Bit:          | 15 | 14                                                       | 13 | 12 | 11      | 10        | 9        | 8       | 7        | 6       | 5      | 4          | 3 | 2 | 1 | 0 |

|---------------|----|----------------------------------------------------------|----|----|---------|-----------|----------|---------|----------|---------|--------|------------|---|---|---|---|

| Register \$A7 |    | Data write from host μC to device word 1(MSB sent first) |    |    |         |           |          |         |          |         |        |            |   |   |   |   |

| Bit:          | 15 | 14                                                       | 13 | 12 | 11      | 10        | 9        | 8       | 7        | 6       | 5      | 4          | 3 | 2 | 1 | 0 |

| Register \$A8 |    | Data write from host µC to device word 2(MSB sent first) |    |    |         |           |          |         |          |         |        |            |   |   |   |   |

| Bit:          | 15 | 14                                                       | 13 | 12 | 11      | 10        | 9        | 8       | 7        | 6       | 5      | 4          | 3 | 2 | 1 | 0 |

| Register \$B6 |    |                                                          |    |    | Data wi | rite fron | n host į | JC to d | levice v | vord 3( | MSB se | ent first) | ) |   |   |   |

| Bit:          | 15 | 14                                                       | 13 | 12 | 11      | 10        | 9        | 8       | 7        | 6       | 5      | 4          | 3 | 2 | 1 | 0 |

| Register \$B7 |    | Data write from host µC to device word 4(MSB sent first) |    |    |         |           |          |         |          |         |        |            |   |   |   |   |

#### Bit-format:

| Bit:          | 15 | 14 | 13 | 12     | 11        | 10     | 9       | 8      | 7       | 6        | 5       | 4       | 3        | 2 | 1 | 0 |

|---------------|----|----|----|--------|-----------|--------|---------|--------|---------|----------|---------|---------|----------|---|---|---|

| Register \$A7 |    |    |    | Data v | write fro | om hos | t μC to | device | bits 0- | 15, (bit | 15 trar | nsmitte | d first) |   |   |   |

#### 7.5.4 Data Tasks

Data Tasks are used to:

- Load data from the Write Data registers into the Tx Data Buffer while in normal or configuration modes

- Load data from the Tx Data Buffer to the AuxDACs

- Write or operate subsystems by passing data using the Write Data registers.

#### Table 3 Data Tasks

| Name              | Description                                                                                      |

|-------------------|--------------------------------------------------------------------------------------------------|

| NULL              | Null system task – takes no action.                                                              |

| DataWordResetN_Tx | Reset Tx Data Buffer pointer.                                                                    |

|                   | Copy N words (1 to 4) from Write Data registers to Tx Data Buffer.                               |

|                   | Increment the Tx Data Buffer pointer.                                                            |

| DataWordWriteN_Tx | Copy N words (1 to 4) from Write Data registers to Tx Data Buffer.                               |

|                   | Increment Tx Data Buffer pointer.                                                                |

| DataBitWriteN_Tx  | Copy N bits (1 to 15) from Write Data register 0 to Tx Data Buffer.                              |

|                   | Increment Tx Data Buffer pointer.                                                                |

| DataBitResetN_Tx  | Reset Tx Data Buffer pointer.                                                                    |

|                   | Copy N bits (1 to 15) from Write Data register 0 to Tx Data Buffer                               |

|                   | Increment Tx Data Buffer pointer.                                                                |

| DAC_Write         | Interprets each of the first 1 to 4 words in the Write Data registers as a write command for the |

|                   | AuxDACs.                                                                                         |

#### 7.5.5 Modem Tasks and Codes

Modem Tasks transmit data on the MOD1 and MOD2 output pins. Modem Tasks also coordinate data transfer between the Tx Data Buffer and the modem.

**Table 4 Modem Tasks**

| Name           |                                                                                       | Description    |                                                                                     |

|----------------|---------------------------------------------------------------------------------------|----------------|-------------------------------------------------------------------------------------|

| NULL           | No command – takes no action                                                          | -              |                                                                                     |

| AbortTx        |                                                                                       |                |                                                                                     |

| ECM            | Enter Configuration mode                                                              |                |                                                                                     |

| Tx Tasks       |                                                                                       |                |                                                                                     |

| Tx Raw bit = 0 |                                                                                       | Tx Raw bit = 1 |                                                                                     |

| TXB            | Code and transmit AIS message using contents of Tx Data Buffer. Start on next SLOTCLK | TDBS           | Transmit contents of Tx Data Buffer. Start on next SLOTCLK                          |

|                |                                                                                       | TDB            | Transmit N data bits from the Tx Data<br>Buffer. Start as soon as modulator is free |

|                |                                                                                       | PRBS           | Transmit pseudorandom bit sequence                                                  |

|                |                                                                                       | TRW            | Repeatedly transmit one word                                                        |

|                |                                                                                       | HCT            | Hardware Control                                                                    |

#### 7.6 Transmission Format

The CMX7045 is capable of transmitting AIS data in either raw mode or burst mode.

In AIS raw mode, data is passed directly from the Tx Data Buffer to the GMSK modulator, so the  $\mu$ C will be responsible for sending any necessary training sequences and performing HDLC processing and NRZI coding.

In AIS burst mode, the CMX7045 uses an internal message buffer to assemble an entire message (up to 5 slots) to which it automatically adds the training sequence, start/stop flags, CRC, bit stuffing and NRZI coding prior to transmission.

After setting up the appropriate registers, transmission is initiated by issuing a Tx Burst or Tx Raw task.

#### 7.6.1 Transmit Tasks

#### AbortTx:

This causes the current task on the Tx channel to abort. It also clears the Tx Modem Buffer.

#### • TXB: Transmit AIS Burst

This task can only be executed if the Tx Raw bit (bit 5 in the command register) is cleared to 0. This causes the CMX7045 to take the contents of the Tx Data buffer, apply AIS data coding and transmit the resulting AIS message. The transmit sequence will start on the next SLOTCLK edge.

The following five transmit tasks can only be executed if the Tx Raw bit is set to 1:

#### TDBS: Transmit Data Buffer on SLOTCLK

This causes the CMX7045 to transmit the Tx Data Buffer contents using AIS modulation. No data coding is applied, the Transmit Sequence will start on the next SLOTCLK edge, at which point the CS-SYNC output will become active. It will become de-active on the next SLOTCLK edge.

#### TDB: Transmit Data Buffer

This causes the CMX7045 to transmit the Tx Data Buffer contents using AIS modulation. No data coding is applied. The data will be transmitted as the modulator is available (Transmit Sequence is ignored).

#### • PRBS: Transmit Pseudorandom Bit Sequence

This task causes the CMX7045 to transmit an internally generated pseudorandom bit sequence. The sequence is 511 bits in length, but will repeat indefinitely until aborted using the AbortTx task, (Transmit Sequence is ignored).

#### • TRW: Transmit Repeated Word

This task causes the CMX7045 to repeatedly transmit the first word currently in the data buffer. Transmission will start immediately and will continue until an Abort Tx task is issued, (Transmit Sequence is ignored).

#### HCT: Hardware Control Task

Allows manual control of ancillary hardware functions.

#### 7.6.2 AIS Burst Mode Transmit

In AIS burst mode, the CMX7045 responds to a TXB task by performing bit stuffing, NRZI encoding and the addition of training sequence, start/stop flags and CRC checksum as required by AIS. Note: in AIS burst mode, the data words are automatically transmitted *least significant bit first* as required by the AIS specification.

A number of error conditions are checked for during AIS burst mode transmit, each of which causes transmission to be aborted and a Tx Done interrupt to be generated. The associated Tx states are:

#### • Tx Aborted, message too long:

This occurs if the internal message buffer is not big enough for the HDLC coded data (should not happen in normal operation, as the message buffer is big enough for a 5-slot message). This condition requires the  $\mu$ C to issue an AbortTx task.

#### Tx Aborted, buffer not ready:

This occurs in burst mode if the internal data coding has not completed before the timing\_start value expires.

#### 7.6.3 Transmit Example

The following detailed example describes the process of loading and transmitting an AIS message in Burst mode.

Table 5 AIS Burst Transmit Example

|     | Description                                                                                                                                                                                                                   | Cmd<br>Reg<br>Free | Data<br>Task | TBFREE | TxDONE |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------|--------|--------|

| 1.  | The host should ensure that the TBFREE, Data Task Complete and CmdReg Free bits are set.                                                                                                                                      | 1                  | 1            | 1      | 1      |

| 2.  | The host loads the first N(typically 4) data words into the Write Data registers.                                                                                                                                             | 1                  | 1            | 1      | 1      |

| 3.  | The host issues a DataWordResetN_Tx Data Task.                                                                                                                                                                                | 0                  | 1            | 1      | 1      |

| 4.  | Device reads the Command register & notes task types.                                                                                                                                                                         | 1                  | 0            | 1      | 1      |

| 5.  | Device carries out the Data Task by copying the N data words as the first N data words of the data buffer.                                                                                                                    | 1                  | 1            | 1      | 1      |

| 6.  | The steps above may be repeated (Using DataWordWriteN_Tx tasks) to load many words until the data buffer contains enough data to carry out the desired modem task.                                                            |                    |              |        |        |

| 7.  | The host writes a TXB task to the Command register to start the Tx process.                                                                                                                                                   | 0                  | 1            | 1      | 1      |

| 8.  | Device reads the Command register.                                                                                                                                                                                            | 1                  | 1            | 0      | 1      |

| 9.  | Device codes the data. Tx state changes from Idle to Tx Pending                                                                                                                                                               | 1                  | 1            | 1      | 0      |

| 10. | When the transmit point arrives (SLOTCLK), the Tx State changes to <i>Tx in progress</i> and the TxSequence is activated.                                                                                                     |                    |              |        |        |

| 11. | The Tx Data Buffer will gradually empty as the Tx Modulator continues transmitting.                                                                                                                                           | 1                  | 1            | 1      | 1      |

| 12. | When the transmission ends the TxDone bit in the Status register will be set, generating an interrupt if enabled. The host should then check the Tx state bits in the Status2 register to see if transmission was successful. | 1                  | 1            | 1      | 1      |

#### 7.6.4 AIS Raw Mode Transmit

In AIS raw mode, transmit data is passed directly from the Tx Data Buffer to the GMSK modulator. The  $\mu$ C must calculate the entire transmitted message including the training sequence, HDLC processing (start/stop flags, bit stuffing, and CRC insertion) and NRZI coding. Note: In AIS raw mode, data words written to the CMX7045 are transmitted *most significant bit first*. The AIS message structure, however, requires each message byte to be output *least significant bit first*. The  $\mu$ C must therefore ensure that during the process of HDLC processing and NRZI coding that the resulting data bytes are correctly reversed.

#### 7.6.5 Transmitter Timing Control

The CMX7045 can be configured to control the timing of transmission events whenever a Tx Burst Modem task is executed. This includes the enabling of external RF circuits (e.g. synthesisers and power amplifier), as well as the time at which internal data modulation begins. The flexibility of this timing control allows the CMX7045 to be simply adapted to the characteristics of the RF transmit circuits. The control of the external RF transmit circuits is performed using the TXENA pin and the AuxDAC1 ramping function.

A typical AIS transmission is shown in Figure 9. The CMX7045 starts timing relative to the rising edge of SLOTCLK. At the end of a transmission, a sequence of "power-down" actions is performed which are timed relative to the last message bit having been modulated, shown as point B in Figure 9. In this way differences in message length due to bit stuffing are automatically accommodated.

The relative timings of the transmit sequence events are configured as a table of values that are loaded into the CMX7045 using a Configuration Task operation (User Manual section 9.12.2.3) – this operation **must** be performed before any transmissions are attempted. Typically, this will only need to be done once as part of an initialization routine. All timings are measured in units of "ticks", each of which lasts for 1/24000Hz ( $\cong 41.666\mu$ s). There are 2.5 ticks per transmitted bit.

The transmit sequence consists of two initial setting values followed by a number of different event types. These are:

- Initial delay from the SLOTCLK edge

- Initial state of the TXENA pin

- Changes to the external hardware, via the TXENA pin (typically used to turn the Tx on/off) and the AuxDAC1 ramp up/down

- Timing triggers for the start and end of the data modulation

- A dummy event in case any of the above are not required in the application.

The transmit event sequence is programmed using a Configuration task, see User Manual section 9.12.2.3.

| b3 | b2 | b1 | b0 | Event id       | Description                                                                                                                         |

|----|----|----|----|----------------|-------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | 0  | dummy          | Do nothing                                                                                                                          |

| 0  | 0  | 0  | 1  | -              | reserved                                                                                                                            |

| 0  | 0  | 1  | 0  | -              | reserved                                                                                                                            |

| 0  | 0  | 1  | 1  | Tx_en_hi       | Pin TXENA is set high                                                                                                               |

| 0  | 1  | 0  | 0  | RAMDAC_UP      | AuxDAC1 will start executing a Ramp up                                                                                              |

| 0  | 1  | 0  | 1  | MODULATE_START | Defines the start of data modulation                                                                                                |

| 0  | 1  | 1  | 0  | MODULATE_END   | Delay from the end of modulation (based on the last data bit loaded into modem - includes a 30 tick delay for the internal filters) |

| 0  | 1  | 1  | 1  | RAMDAC_DOWN    | AuxDAC1 will start executing a Ramp down                                                                                            |

| 1  | 0  | 0  | 0  | Tx_en_lo       | Pin TXENA is set low                                                                                                                |

| 1  | 0  | 0  | 1  | dummy          | Do nothing                                                                                                                          |

**Table 6 Tx Sequence events**

When calculating the MODULATE\_START timing value, the delay through the CMX7045's internal transmit filters and any external components must be taken into account to ensure that data bits appear on-air at the correct time (the filter delays are specified in section 8.1.4). The MODULATE\_END event has an in-built delay of 30 ticks to allow the last bit to make its way out of the transmit filter and external components. Allowance must be made for this built-in delay, as well as for the delay through any external components, when calculating the timing of the transmit power down events.

An explanation of the information shown in Figure 9 is given in Table 7 (the order of events and timings shown are for illustrative purposes only).

Figure 9 Typical AIS Transmission

| Table 7 Example Tx Event Sequence Set |

|---------------------------------------|

|---------------------------------------|

| Parameter      | Event ID | Delay | Total | Explanation                                                                                                                                                                                              |

|----------------|----------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dummy          | 0        | 0     | 20    | Do nothing                                                                                                                                                                                               |

| MODULATE_START | 5        | 1     | 21    | Start feeding data to the transmit modulator and filters (this allows for the 20 tick storage delay in the Tx filters so that modulated data appears at the end of the RAMDAC ramp_up period – tick 21). |

| dummy          | 0        | 0     | 21    | Do nothing                                                                                                                                                                                               |

| Tx_en_hi       | 3        | 0     | 21    | Set TXENA line high                                                                                                                                                                                      |

| RAMDAC_UP      | 4        | 3     | 24    | Insert 3 tick delay then initiate the RAMDAC ramp-up (for AIS, the transmitted signal will be carrier only at this point)                                                                                |

At this point during a transmission the CMX7045 feeds the entire message to the transmit modulator bit-by-bit. All subsequent transmit events are timed relative to the end of the last message bit, indicated by the MODULATE\_END event.

| RAMDAC_DOWN  | 7 | 2 | 0  | Initiate the RAMDAC ramp-down immediately                                             |  |

|--------------|---|---|----|---------------------------------------------------------------------------------------|--|

| Tx_en_lo     | 8 | 7 | 9  | Insert 7 tick delay (to allow RAMDAC to fully ramp down) then set the TXENA line low. |  |

| MODULATE_END | 6 | 5 | 14 | Allows for process delays                                                             |  |

#### Notes

- 1. MODULATE\_START must appear in the first group of timed events (table entries 1–5), MODULATE\_END must appear in the final group (table entries 6-8).

- 2. It is feasible to place the RAMDAC\_DOWN task *before* the MODULATE\_END task if it is desired to continue modulation during the Ramp down period.

Assuming that the timing\_start value has been set to 0 (see User Manual section 9.12.2.3) and the RAMDAC is set to its default values (312µs), this sequence approximates to the SART timing with ideal hardware (RAMDAC starts 5bits / 12 ticks after SLOTCLK).

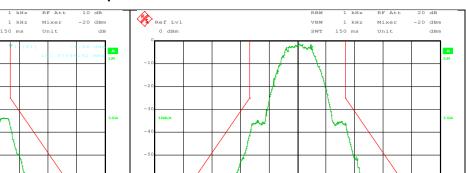

#### 7.6.6 Modulation Formats

The CMX7045 can be configured to drive either a two-point VCO and Reference modulator or an I/Q modulator, see section 9.12.2.1.

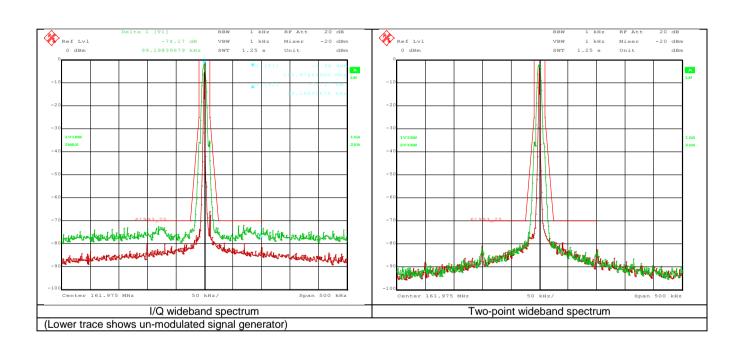

Typical Tx spectrum plots for both modes are shown below (generated by modulating a signal generator with the outputs of MOD1 and MOD2 and then analysing the signal on a spectrum analyser). Note that these plots represent the steady-state transmission and so are shown with the Class A and Class B-SOTDMA spectrum mask (-70dBc). The Class B-CSTDMA standard specifies a slotted transmission with a mask at -60dBc.

Two-point Tx spectrum mask

rhouse Hypester

**Table 8 Tx Spectrum Masks**

Mile Joseph Land

VBW

I/Q Tx spectrum mask

#### 7.7 Configuration Tasks and Codes

The device executes Configuration Tasks while in configuration mode. (See section 7.4.2 for a description of device operating modes and how to change between them, and User Manual section 9.12 for more details on a particular task). These tasks and their data are used to configure device subsystems.

Data required for the Configuration Task is loaded into the device using a Data Task, which can be executed at the same time as the Configuration Task if it requires less than four words.

Ref Lvl

for the state of the

upit (Vol.

| Configuration Task | Words   | Description                                       | User Manual section |

|--------------------|---------|---------------------------------------------------|---------------------|

| NULL               | 0       | Do nothing                                        |                     |

| Exit Config        | 0       | Return to Normal mode                             |                     |

| Tx I/Q or 2-point  | 1       | Sets MOD1 and MOD2 output format (2-point or I/Q) | 9.12.2.1            |

| Tx MOD levels      | 1       | Sets output levels on MOD1 and MOD2 signal pins   | 9.12.2.2            |

| Tx_sequence        | 18      | Loads Tx sequence commands                        | 9.12.2.3            |

| RAMDAC load        | 3 or 67 | Configures RAMDAC and loads data table            | 9.12.2.4            |

| Device Ident       | 2       | Reads back the Device Ident and Version number    | 9.12.2.5            |

| Enter Deep Sleep   | 0       | Enter Deep Sleep mode                             | 9.12.2.6            |

| Leave Deep Sleep   | 0       | Leave Deep Sleep mode                             | 9.12.2.7            |

| Reference clock    | 1       | 0 = 19.2MHz, 1 = 9.6MHz                           | 9.12.2.8            |

**Table 9 Configuration Tasks**

#### 7.8 System Clock Synthesisers

Two System Clock outputs, SYSCLK1 and SYSCLK2, are available to drive additional circuits, as required. These are phase locked loop (PLL) clocks that can be programmed via the System Clock registers with suitable values chosen by the user. The System Clock PLL Configuration registers (\$AB and \$AD) control the values of the VCO Output divider and Main Divide registers, while the System Clock Ref. Configuration registers (\$AC and \$AE) control the values of the Reference Divider and signal routing configurations. The PLLs are designed for a reference frequency of 96kHz.