# 5V, 250mA Voice Coil Motor Driver with H-bridge and Programmable Head Retract, Bandwidth and Power Fault Detection

## Description

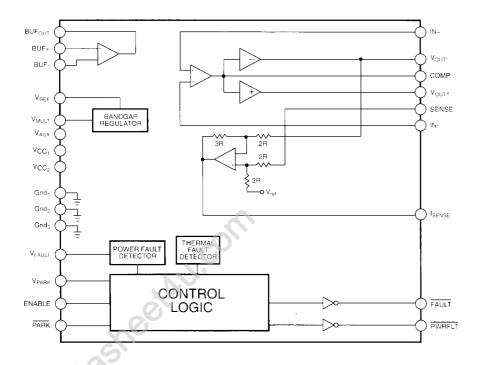

The CS-7105 is a voice coil power driver intended for use in 5V 2.5 inch Hard Disk servo systems. The CS-7105 contains the complete H-Bridge power amplifier, including the 4 power transistors, and all

control functions. Head retraction circuitrv is provided to allow for a controlled shutdown of the drive. Power Fault, and Thermal Fault Detection are also included.

#### Absolute Maximum Ratings

| V <sub>CC1</sub> , V <sub>CC2</sub> , | 10V                      |

|---------------------------------------|--------------------------|

| Auxiliary Supply, V <sub>AUX</sub>    | 17V                      |

| Logic Input Voltage                   | 0.3V to V <sub>AUX</sub> |

| Logic Output Voltage                  |                          |

| Maximum Junction Temperature          |                          |

| Maximum Power Dissipation             |                          |

| H-Bridge Output Current               |                          |

| Storage Temperature                   |                          |

| Operating Temperature                 |                          |

|                                       |                          |

#### **Block Diagram**

### Features

Single 5 Volt Power Supply

Full 250mA H-Bridge

On Chip Transient Protection

**Low System Offset** Current (<1mA)

Low Supply Current (6mA)

Low Current Standby Mode

All Amplifiers internally Compensated

**No Crossover Distortion**

**Programmable Functions:**

$V_{REF}$ **Retract Voltage** System Bandwidth **Power Fault Detector Transconductance**

On Chip Thermal Protection

### **Package Options**

Cherry Semiconductor Corporation 2000 South County Trail East Greenwich, Rhode Island 02818 Tel: (401)885-3600 Fax (401)885-5786 Telex WUI 6817157

| Electrical C                                                                      | haracteristics: $V_{CC} = 4.5V$ to 5.5V, $T_A$ | = 0 to 70°C, Unless | otherwise sp | ecified     |            |

|-----------------------------------------------------------------------------------|------------------------------------------------|---------------------|--------------|-------------|------------|

| PARAMETER                                                                         | TEST CONDITIONS                                | MIN                 | TYP          | MAX         | UN         |

| Power Supply                                                                      |                                                |                     |              |             |            |

| Supply Voltage Range $V_{CC_1}$ and $V_{CC_2}$                                    |                                                | 4.5                 | 5.0          | 5.5         | V          |

| Total Supply Current (I <sub>CC</sub> + I <sub>AUX</sub> )                        |                                                |                     |              |             |            |

| $V_{\rm ENABLE} = 2.0 V$<br>(Track Following)<br>$V_{\rm ENABLE} = 0.8 V$         |                                                |                     | 6.0          | 25.0<br>2.0 | m.<br>m.   |

| Auxiliary Voltage, V <sub>AUX</sub>                                               |                                                | 2.0                 |              | 15.0        | V          |

| Auxiliary Current, $I_{AUX}$<br>$V_{CC} = 0$ , $V_{AUX} = 5.0V$                   |                                                |                     |              | 15.0        | m          |

| Logic I/O                                                                         |                                                |                     |              |             |            |

| Logic HI Input Current                                                            | $V_{IN} = 2.0V$                                |                     |              | 100         | μA         |

| Logic LOW Input Current                                                           | $V_{IN} = 0.8V$                                |                     |              | -100        | μ <i>Α</i> |

| Logic HI Input Voltage                                                            |                                                |                     | 1.5          | 2.0         | V          |

| Logic LOW Input Voltage                                                           |                                                | 0.8                 | 1.5          |             | V          |

| FAULT                                                                             | $I_{OUT} = 100 \mu A$                          |                     |              | 0.4         | V          |

| PWRFLT                                                                            | $I_{OUT} = 100 \mu A$                          |                     |              | 0.4         | V          |

| Voltage Reference                                                                 |                                                |                     |              |             |            |

| $V_{REF}$                                                                         | $R_{MULT} = 20k\Omega$                         | 2.40                | 2.50         | 2.60        | V          |

| Output Current                                                                    | $R_{REF} = 20k\Omega$                          | 2.0                 |              |             | m          |

| PSRR                                                                              | e e e                                          | 40                  |              |             | dI         |

| Closed Loop System (R <sub>SENS</sub>                                             | $_{\mathrm{SE}}$ = $2\Omega$ )                 |                     |              |             |            |

| Transconductance<br>(Buffer amplifier set for Gair                                | n = 1.0                                        |                     |              |             |            |

| $(T_A = 25^{\circ}C)$                                                             |                                                |                     |              |             |            |

| $I_{OUT} = 200 \text{mA}$                                                         | $R_f = 20k\Omega$                              | 190                 | 200          | 210         | m          |

| $(T_A = 0 \text{ to } 70^{\circ}\text{C})$<br>$I_{OUT} = 200\text{mA}$            |                                                | 186                 | 200          | 214         | m          |

| Output Offset Current                                                             | $T_A = 25^{\circ}C$                            |                     |              | 1.00        | m          |

| Output Offset Current                                                             | $T_A = 0$ to $70^{\circ}$ C                    |                     |              | 1.25        | m          |

| Input Voltage Range                                                               |                                                | 0.00                |              | 3.50        | V          |

| Frequency Response                                                                |                                                | 30                  |              |             | kF         |

| H-Bridge Amplifier                                                                |                                                |                     |              |             |            |

| Voltage Gain                                                                      |                                                |                     | 14           |             | V,         |

| Frequency Response                                                                |                                                | 60                  |              |             | kŀ         |

| Bridge Output Current                                                             |                                                | 250                 |              |             | m          |

| Quiescent Bias Current<br>(per Side)                                              |                                                |                     | . 2          |             | m          |

| Bridge Saturation Voltage, $I_{OUT} = 100 \text{mA}$ , $T_A = 25^{\circ}\text{C}$ |                                                |                     |              | 0.25        | V          |

| Bridge Saturation Voltage,<br>I <sub>OUT</sub> = 200mA, T <sub>A</sub> = 25°C     |                                                |                     |              | 0.50        | V          |

| Electrical Characteristics: continued                        |                                |      |      |      |                 |

|--------------------------------------------------------------|--------------------------------|------|------|------|-----------------|

| PARAMETER                                                    | TEST CONDITIONS                | MIN  | ТҮР  | MAX  | CS-7105<br>UNIT |

| ■ H-Bridge Amplifier (con                                    | itinued)                       |      |      |      |                 |

| Bridge Saturation Voltage $I_{OUT}$ =200mA, ( $T_A$ = 0 to 2 |                                |      |      | 0.60 | V               |

| Thermal Shutdown Temp                                        | o.                             |      | 150  |      | °C              |

| ■ Buffer Amplifier                                           |                                |      |      |      |                 |

| Open Loop Gain                                               |                                | 60   |      |      | dB              |

| Input Offset Voltage                                         |                                |      |      | 5    | mV              |

| Input Bias Current                                           |                                |      |      | 5.0  | μΑ              |

| Unity Gain Bandwidth                                         |                                | 300  | 500  |      | $kH_Z$          |

| PSRR                                                         |                                | 50   |      |      | dB              |

| Input Common Mode Ra                                         | nge                            | 0    |      | 3.5  | V               |

| Output Voltage Range                                         |                                | 0.1  |      | 3.5  | V               |

| ■ Current Sensing Amplif                                     | ier                            |      |      |      |                 |

| Closed Loop Gain                                             | $V_{IN} = (V_{OUT}) - (SENSE)$ | 1.45 | 1.50 | 1.55 | V/V             |

| Input Offset Voltage                                         |                                |      |      | 5    | mV              |

| ■ Power Fault Level                                          |                                |      |      |      |                 |

| $V_{FAULT}$                                                  | $R_{PWR_H} = 30k\Omega$        | 3.75 | 4.00 | 4.25 | V               |

| V <sub>FAULT</sub> Hysteresis                                | $R_{PWR_L} = 50k\Omega$        |      | 100  | 200  | mV              |

| ■ Head Park                                                  |                                |      |      |      |                 |

| $V_{PARK}$                                                   | $R_{PARK} = 5k\Omega$          | 0.4  | 0.5  | 0.6  | V               |

| Output Current                                               |                                | 10   |      |      | mA              |

|                                                              |                                |      |      |      |                 |

### Package Pin Description

| PACKAGE PIN # | PIN SYMBOL         | FUNCTION                                                                                                                                            |

|---------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 24 Lead SO    |                    |                                                                                                                                                     |

| 15            | $V_{CC_1}$         | Positive power supply, 4.5V to 5.5V.                                                                                                                |

| 11            | $Gnd_1$            | Analog ground.                                                                                                                                      |

| 5             | $V_{AUX}$          | Auxiliary power supply for head park during supply line failure.                                                                                    |

| 1             | $V_{CC_2}$         | Positive power supply for the H-Bridge driver.                                                                                                      |

| 4             | $Gnd_2$            | Ground for the H-Bridge driver.                                                                                                                     |

| 21            | $Gnd_3$            | Ground for the H-Bridge driver.                                                                                                                     |

| 7             | $V_{ m REF}$       | Internal voltage reference for external DAC.                                                                                                        |

| 6             | $V_{PARK}$         | Voltage that is programmed by an external resistor and is applied across the VCM during park.                                                       |

| 10            | BUF <sub>OUT</sub> | Output of the buffer amplifier and input to the transconductance amplifier.                                                                         |

| 8             | BUF-               | Negative input to the buffer amplifier.                                                                                                             |

| 9             | BUF+               | Positive input to the buffer amplifier.                                                                                                             |

| 20            | ENABLE             | Digital input to select standby of full power mode.                                                                                                 |

| 23            | FAULT              | A digital output signaling an over velocity, a power fault, or a thermal fault condition. Reset by the ENABLE pin. May also be used for spin brake. |

| 19            | <b>PWRFLT</b>      | Open Collector NPN output. Low indicates power fault.                                                                                               |

| 18            | PARK               | Logic input for park.                                                                                                                               |

| 17            | $I_{SENSE}$        | Output of the amplifier sensing the VCM current.                                                                                                    |

| 12            | IN-                | Negative input of the transconductance amplifier.                                                                                                   |

| 13            | IN+                | Positive input of the transconductance amplifier.                                                                                                   |

| 2             | $V_{OUT}$ -        | Negative output of H-Bridge.                                                                                                                        |

| 24            | $V_{OUT}$ +        | Positive output of H-Bridge.                                                                                                                        |

| 16            | SENSE              | Current sense input from the current sense resistor.                                                                                                |

| 14            | COMP               | Compensation node of the transconductance amplifier.                                                                                                |

| 22            | $V_{MULT}$         | Programming pin for V <sub>REF</sub> .                                                                                                              |

| 3             | $V_{FAULT}$        | Programming pin for power fault.                                                                                                                    |

#### Power Supply

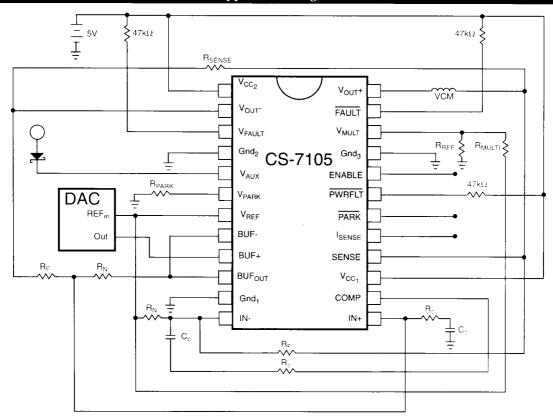

Power supply pins  $V_{CC_1}$  and  $V_{CC_2}$  must be connected together externally.  $V_{aux}$  can be connected to  $V_{CC}$  or to a Park voltage source. During normal operation where the Park source is not active, the  $V_{AUX}$  is internally powered from the  $V_{CC}$  line.  $Gnd_1$ ,  $Gnd_2$ , and  $Gnd_3$  must all be connected to system ground.

The current sensing amplifier provides a voltage which is 1.5 times the voltage across  $R_{SENSE}$  and is referenced to  $V_{REF}$ . The gain of this amplifier is set by internal resistors.

#### Vollage Reference

A bandgap voltage source is used to provide the reference for the power fault detector and for the transconductance reference voltage. The reference voltage is programmed by external resistors.

#### Power Fault Detector

The power fault detector monitors the voltage supply line. Should an undervoltage condition occur, the FAULT line will switch low and a head park will occur. If the power recovers, the fault condition will be cleared. The power fault level is programmable by external resistors.

#### Transconductance Loop

The transconductance loop consists of a full H-Bridge output stage, a low offset error amplifier, and an input buffer amplifier. The transconductance is programmed by external resistors.

The buffer amplifier is a low offset operational amplifier which can be configured as a gain stage or as a second order low pass filter.

The error amplifier is a low offset operational amplifier which can be configured as a gain stage or as a second order low pass filter.

The power amplifier is a full H-Bridge with 250mA capability, and built in transient protection diodes. The differential voltage gain is 14. Class AB bias is used to eliminate crossover distortion.

The power amplifier is protected from overload by thermal shutdown circuitry. Should a thermal overload occur, the H-Bridge amplifier will turn off until the ENABLE line is toggled low then high.

The ENABLE pin is used to select full power mode or standby mode. When ENABLE is high, the circuit is in the full power mode. When ENABLE is low, the circuit is in a standby mode with only the logic powered.

The FAULT line is an open collector NPN transistor which is intended to provide a system reset. This line will switch low if a power fault or a thermal fault is detected. This line may also be used to drive a spin brake.

#### **Application Diagram**

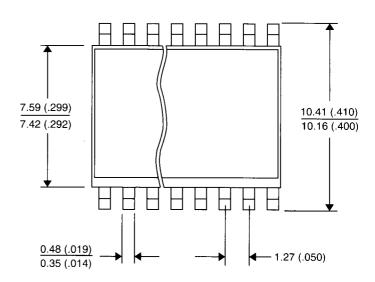

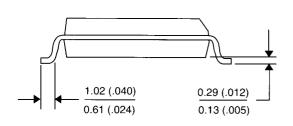

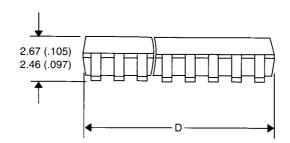

#### Package Specification

#### PACKAGE DIMENSIONS IN mm (INCHES)

#### PACKAGE THERMAL DATA

|            | D      |       |         |      |

|------------|--------|-------|---------|------|

| Lead Count | Metric |       | English |      |

| _          | Max    | Min   | Max     | Min  |

| 24 Lead SO | 15.54  | 15.29 | .612    | .602 |

| Thermal Data   |     | 24 Lead |      |

|----------------|-----|---------|------|

|                |     | SODW    |      |

| $R\Theta_{JC}$ | typ | 16      | °C/W |

| $R\Theta_{JA}$ | typ | 80      | °C/W |

#### 24 Lead SO

### **Ordering Information**

Part Number CS-7105DW24 **Description** SO Wide

#### Preliminary

This product is in the preproduction stages of the design process. The data sheet contains preliminary data. CSC reserves the right to make changes to the specifications without notice. Please contact CSC for the latest available information.

Cherry Semiconductor Corporation 2000 South County Trail East Greenwich, Rhode Island 02818 Tel: (401)885-3600 Fax (401)885-5786 Telex WUI 6817157

© 1992 Cherry Semiconductor Corporation