# **Secondary Side Post** Regulator for AC/DC and **DC/DC** Multiple Output **Converters**

The CS5101 is a bipolar monolithic secondary side post regulator (SSPR) which provides tight regulation of multiple output voltages in AC/DC or DC/DC converters. Leading edge pulse width modulation is used with the CS5101.

The CS5101 is designed to operate over an 8.0 V to 45 V supply voltage (V<sub>CC</sub>) range and up to a 75 V drive voltage (V<sub>C</sub>).

The CS5101 features include a totem pole output with 1.5 A peak output current capability, externally programmable overcurrent protection, an on chip 2.0% precision 5.0 V reference, internally compensated error amplifier, externally synchronized switching frequency, and a power switch drain voltage monitor. It is available in a 14 lead plastic DIP or a 16 lead wide body SOIC package.

#### **Features**

- 1.5 A Peak Output (Grounded Totem Pole)

- 8.0 V to 75 V Gate Drive Voltage

- 8.0 V to 45 V Supply Voltage

- 300 ns Propagation Delay

- 1.0% Error Amplifier Reference Voltage

- Lossless Turn On and Turn Off

- Sleep Mode: < 100 μA

- Overcurrent Protection with Dedicated Differential Amp

- Synchronization to External Clock

- External Power Switch Drain Voltage Monitor

- Pb-Free Packages are Available\*

### ON Semiconductor®

http://onsemi.com

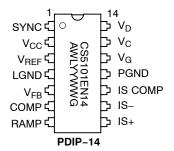

PDIP-14 **N SUFFIX CASE 646**

**SO-16WB DW SUFFIX CASE 751G**

#### **MARKING DIAGRAMS AND PIN ASSIGNMENTS**

= Assembly Location

WL = Wafer Lot VV = Year WW = Work Week = Pb-Free Package

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 5 of this data sheet.

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

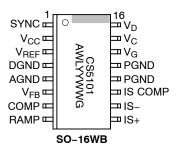

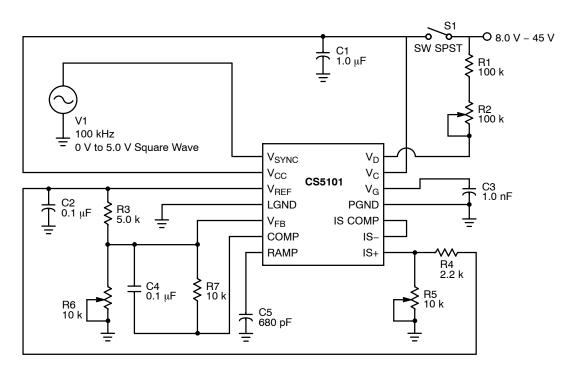

Figure 1. Application Diagram

### **MAXIMUM RATINGS**

| F                                                                                                | Value                                                                             | Unit                 |    |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|----------------------|----|

| Power Supply Voltage, V <sub>CC</sub>                                                            |                                                                                   | -0.3 to 45           | V  |

| $V_{SYNC}$ and Output Supply Voltages, $V_C$ , $V_G$ , $V_{SYN}$                                 | NC, VD                                                                            | -0.3 to 75           | V  |

| V <sub>IS+</sub> , V <sub>IS-</sub> (V <sub>CC</sub> – 4.0 V, up to 24 V)                        |                                                                                   | -0.3 to 24           | V  |

| V <sub>REF</sub> , V <sub>FB</sub> , V <sub>COMP</sub> , V <sub>RAMP</sub> , V <sub>ISCOMP</sub> |                                                                                   | -0.3 to 10           | V  |

| Operating Junction Temperature, T <sub>J</sub>                                                   |                                                                                   | -40 to +150          | °C |

| Operating Temperature Range                                                                      |                                                                                   | -40 to +85           | °C |

| Storage Temperature Range                                                                        |                                                                                   | -65 to +150          | °C |

| Output Energy (Capacitive Load Per Cycle)                                                        |                                                                                   | 5.0                  | μЈ |

| ESD Human Body                                                                                   |                                                                                   | 2.0                  | kV |

| Lead Temperature Soldering                                                                       | Wave Solder (through hole styles only) (Note 1) Reflow (SMD styles only) (Note 2) | 260 peak<br>230 peak | °C |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. 10 second maximum

- 2. 60 second maximum above 183°C

**ELECTRICAL CHARACTERISTICS** ( $-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}$ ,  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$ ,  $10 \text{ V} < V_{CC} < 45 \text{ V}$ ,  $8.0 \text{ V} < V_{C} < 75 \text{ V}$ ; unless otherwise specified.)

| Characteristic                                                           | Test Conditions                                                                | Min  | Тур  | Max                   | Unit |

|--------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|-----------------------|------|

| Error Amplifier                                                          |                                                                                |      | l .  | l                     | I    |

| Input Voltage Initial Accuracy                                           | V <sub>FB</sub> = V <sub>COMP</sub> , V <sub>CC</sub> = 15 V, T = 25°C, Note 3 | 1.98 | 2.00 | 2.02                  | V    |

| Input Voltage                                                            |                                                                                |      | 2.00 | 2.06                  | V    |

| Input Bias Current                                                       |                                                                                |      | _    | 500                   | nA   |

| Open Loop Gain                                                           | 1.5 V < V <sub>COMP</sub> < 3.0 V                                              | 60   | 70   | -                     | dB   |

| Unity Gain Bandwidth                                                     | 1.5 V < V <sub>COMP</sub> < 3.0 V, Note 3                                      | 0.7  | 1.0  | -                     | MHz  |

| Output Sink Current                                                      | V <sub>COMP</sub> = 2.0 V, V <sub>FB</sub> = 2.2 V                             | 2.0  | 8.0  | -                     | mA   |

| Output Source Current                                                    | V <sub>COMP</sub> = 2.0 V, V <sub>FB</sub> = 1.8 V                             | 2.0  | 6.0  | -                     | mA   |

| V <sub>COMP</sub> High                                                   | V <sub>FB</sub> = 1.8 V                                                        | 3.3  | 3.5  | 3.7                   | V    |

| V <sub>COMP</sub> Low                                                    | V <sub>FB</sub> = 2.2 V                                                        | 0.85 | 1.0  | 1.15                  | V    |

| PSRR                                                                     | 10 V < V <sub>CC</sub> < 45 V, V <sub>FB</sub> = V <sub>COMP</sub> , Note 3    | 60   | 70   | -                     | dB   |

| Voltage Reference                                                        | ,                                                                              |      |      |                       | 1    |

| Output Voltage Initial Accuracy                                          | V <sub>CC</sub> = 15 V, T = 25°C, Note 3                                       | 4.9  | 5.0  | 5.1                   | V    |

| Output Voltage                                                           | 0 A < I <sub>REF</sub> < 8.0 mA                                                | 4.8  | 5.0  | 5.2                   | V    |

| Line Regulation                                                          | 10 V < V <sub>CC</sub> < 45 V, I <sub>REF</sub> = 0 A                          | _    | 10   | 60                    | mV   |

| Load Regulation                                                          | 0 A < I <sub>REF</sub> < 8.0 mA                                                | _    | 20   | 60                    | mV   |

| Current Limit                                                            | V <sub>REF</sub> = 4.8 V                                                       | 10   | 50   | -                     | mA   |

| V <sub>REF</sub> OK FAULT V                                              | V <sub>SYNC</sub> = 5.0 V, V <sub>REF</sub> = V <sub>LOAD</sub>                | 4.10 | 4.40 | 4.60                  | V    |

| V <sub>REF</sub> OK V                                                    | V <sub>SYNC</sub> = 5.0 V, V <sub>REF</sub> = V <sub>LOAD</sub>                | 4.30 | 4.50 | 4.80                  | V    |

| V <sub>REF</sub> _OK Hysteresis                                          | -                                                                              | 40   | 100  | 250                   | mV   |

| Current Sense Amplifier                                                  |                                                                                | ı    | l .  | ı                     | I    |

| IS COMP High V                                                           | IS+ = 5.0 V, IS- = IS COMP                                                     | 4.7  | 5.0  | 5.3                   | V    |

| IS COMP Low V                                                            | IS+ = 0 V, IS- = IS COMP                                                       | 0.5  | 1.0  | 1.3                   | V    |

| Source Current                                                           | IS+ = 5.0 V, IS- = 0 V                                                         | 2.0  | 10   | -                     | mA   |

| Sink Current                                                             | IS- = 5.0 V, IS+ = 0 V                                                         | 10   | 20   | -                     | mA   |

| Open Loop Gain                                                           | 1.5 V ≤ $V_{COMP}$ ≤ 4.5 V, $R_L$ = 4.0 kΩ                                     | 60   | 80   | -                     | dB   |

| CMRR                                                                     | Note 3                                                                         | 60   | 80   | -                     | dB   |

| PSRR                                                                     | 10 V < V <sub>CC</sub> < 45 V, Note 3                                          | 60   | 80   | -                     | dB   |

| Unity Gain Bandwidth                                                     | 1.5 V ≤ $V_{COMP}$ ≤ 4.5 V, $R_L$ = 4.0 kΩ, Note 3                             | 0.5  | 0.8  | -                     | MHz  |

| Input Offset Voltage                                                     | $V_{IS}$ + = 2.5 V, $V_{IS}$ - = $V_{ISCOMP}$                                  | -8.0 | 0    | 8.0                   | mV   |

| Input Bias Currents                                                      | $V_{IS}$ + = $V_{IS}$ - = 0 V, $I_{IS}$ flows out of pins                      | _    | 20   | 250                   | nA   |

| Input Offset Current (IS+, IS-)                                          | -                                                                              | -250 | 0    | 250                   | nA   |

| Input Signal Voltage Range                                               | Note 3                                                                         | -0.3 | -    | V <sub>CC</sub> - 4.0 | V    |

| RAMP/SYNC Generator                                                      |                                                                                |      |      |                       |      |

| RAMP Source Current Initial Accuracy                                     | V <sub>SYNC</sub> = 5.0 V, V <sub>RAMP</sub> = 2.5 V, T = 25°C, Note 3         | 0.18 | 0.20 | 0.22                  | mA   |

| RAMP Source Current V <sub>SYNC</sub> = 5.0 V, V <sub>RAMP</sub> = 2.5 V |                                                                                | 0.16 | 0.20 | 0.24                  | mA   |

| RAMP Sink Current                                                        | RAMP Sink Current V <sub>SYNC</sub> = 0 V, V <sub>RAMP</sub> = 2.5 V           |      | 4.0  | -                     | mA   |

| RAMP Peak Voltage V <sub>SYNC</sub> = 5.0 V                              |                                                                                | 3.3  | 3.5  | 3.7                   | V    |

| RAMP Valley Voltage                                                      |                                                                                |      | 1.5  | 1.6                   | V    |

| RAMP Dynamic Range                                                       | V <sub>RAMPDR</sub> = V <sub>RAMPPK</sub> - V <sub>RAMPVY</sub>                | 1.7  | 2.0  | 2.3                   | V    |

| RAMP Sleep Threshold Voltage                                             | V <sub>RAMP</sub> @ V <sub>REF</sub> < 2.0 V                                   | 0.3  | 0.6  | 1.0                   | V    |

| SYNC Threshold                                                           | V <sub>SYNC</sub> @ V <sub>RAMP</sub> > 2.5 V                                  | 2.3  | 2.5  | 2.7                   | V    |

| SYNC Input Bias Current                                                  | V <sub>SYNC</sub> = 0 V, I <sub>SYNC</sub> flows out of pin                    | -    | 1.0  | 20                    | μΑ   |

|                                                                          |                                                                                |      |      |                       |      |

Guaranteed by design. Not 100% tested in production.

$\textbf{ELECTRICAL CHARACTERISTICS} \ (-40^{\circ}\text{C} \le T_{A} \le 85^{\circ}\text{C}, \ -40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}, \ 10 \ V < V_{CC} < 45 \ V, \ 8.0 \ V < V_{C} < 75 \ V; \ unless otherwise specified.)$

| Characteristic                                                                | Test Conditions                                                                                       | Min | Тур  | Max | Unit |

|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|------|-----|------|

| Output Stage                                                                  |                                                                                                       |     |      |     |      |

| V <sub>G</sub> , High                                                         | $V_{SYNC} = 5.0 \text{ V}, IV_G = 200 \text{ mA}, V_C - V_G$                                          |     | 1.6  | 2.5 | V    |

| V <sub>G</sub> , Low                                                          | V <sub>SYNC</sub> = 0 V, IV <sub>G</sub> = 200 mA                                                     | _   | 0.9  | 1.5 | V    |

| V <sub>G</sub> Rise Time                                                      | Switch $V_{SYNC}$ High, $C_G$ = 1.0 nF, $V_{CC}$ = 15 V, measure 2.0 V to 8.0 V                       | _   | 30   | 75  | ns   |

| V <sub>G</sub> Fall Time                                                      | Switch V <sub>SYNC</sub> Low, C <sub>G</sub> = 1.0 nF, V <sub>CC</sub> = 15 V, measure 8.0 V to 2.0 V | -   | 40   | 100 | ns   |

| V <sub>G</sub> Resistance to GND                                              | Remove supplies, V <sub>G</sub> = 10 V                                                                | _   | 50   | 100 | kΩ   |

| V <sub>D</sub> Resistance to GND                                              |                                                                                                       |     | 1500 | _   | Ω    |

| General                                                                       |                                                                                                       |     |      |     |      |

| I <sub>CC</sub> , Operating                                                   | CC, Operating V <sub>SYNC</sub> = 5.0 V                                                               |     | 12   | 18  | mA   |

| I <sub>CC</sub> in UVL                                                        | V <sub>CC</sub> = 6.0 V                                                                               |     | 300  | 500 | μА   |

| I <sub>CC</sub> in Sleep Mode High                                            | Sleep Mode High V <sub>RAMP</sub> = 0 V, V <sub>CC</sub> = 45 V                                       |     | 80   | 200 | μА   |

| I <sub>CC</sub> in Sleep Mode Low                                             | in Sleep Mode Low V <sub>RAMP</sub> = 0 V, V <sub>CC</sub> = 10 V                                     |     | 20   | 50  | μА   |

| I <sub>C</sub> , Operating High                                               | erating High $V_{SYNC} = 5.0 \text{ V}, V_{FB} = V_{IS} - = 0 \text{ V}, V_C = 75 \text{ V}$          |     | 4.0  | 8.0 | mA   |

| I <sub>C</sub> , Operating Low                                                | V <sub>SYNC</sub> = 5.0 V, V <sub>FB</sub> = V <sub>IS</sub> - = 0 V, V <sub>C</sub> = 8.0 V          | _   | 3.0  | 6.0 | mA   |

| UVLO Start Voltage –                                                          |                                                                                                       | 7.4 | 8.0  | 9.2 | V    |

| JVLO Stop Voltage –                                                           |                                                                                                       | 6.4 | 7.0  | 8.3 | V    |

| UVLO Hysteresis                                                               | /LO Hysteresis –                                                                                      |     | 1.0  | 1.2 | V    |

| Leading Edge, $t_{DELAY}$ $V_{SYNC} = 2.5 \text{ V to } V_G = 8.0 \text{ V}$  |                                                                                                       | -   | 280  | -   | ns   |

| Trailing Edge, $t_{DELAY}$ $V_{SYNC} = 2.5 \text{ V to } V_G = 2.0 \text{ V}$ |                                                                                                       | _   | 750  | _   | ns   |

### PACKAGE PIN DESCRIPTION

| PACKAGE LEAD # |         |                  |                                                      |  |  |

|----------------|---------|------------------|------------------------------------------------------|--|--|

| PDIP-14        | SO-16WB | LEAD SYMBOL      | FUNCTION                                             |  |  |

| 1              | 1       | SYNC             | Synchronization input.                               |  |  |

| 2              | 2       | V <sub>CC</sub>  | Logic supply (10 V to 45 V).                         |  |  |

| 3              | 3       | V <sub>REF</sub> | 5.0 V voltage reference.                             |  |  |

| 4              | -       | LGND             | Logic level ground (analog and digital ground tied). |  |  |

| 5              | 6       | V <sub>FB</sub>  | Error amplifier inverting input.                     |  |  |

| 6              | 7       | COMP             | Error amplifier output and compensation.             |  |  |

| 7              | 8       | RAMP             | RAMP programmable with the external capacitor.       |  |  |

| 8              | 9       | IS+              | Current sense amplifier non-inverting input.         |  |  |

| 9              | 10      | IS-              | Current sense amplifier inverting input.             |  |  |

| 10             | 11      | IS COMP          | Current sense amplifier compensation and output.     |  |  |

| 11             | 12, 13  | PGND             | Power ground.                                        |  |  |

| 12             | 14      | V <sub>G</sub>   | External power switch gate drive.                    |  |  |

| 13             | 15      | V <sub>C</sub>   | Output power stage supply voltage (8.0 V to 75 V).   |  |  |

| 14             | 16      | V <sub>D</sub>   | External FET DRAIN voltage monitor.                  |  |  |

| -              | 5       | AGND             | Analog ground.                                       |  |  |

| -              | 4       | DGND             | Digital ground.                                      |  |  |

### **ORDERING INFORMATION**

| Device        | Package                | Shipping <sup>†</sup> |  |

|---------------|------------------------|-----------------------|--|

| CS5101EN14    | PDIP-14                |                       |  |

| CS5101EN14G   | PDIP-14<br>(Pb-Free)   | 25 Units / Rail       |  |

| CS5101EDW16   | SOIC-16WB              |                       |  |

| CS5101EDW16G  | SOIC-16WB<br>(Pb-Free) | 47 Units / Rail       |  |

| CS5101EDWR16  | SOIC-16WB              |                       |  |

| CS5101EDWR16G | SOIC-16WB<br>(Pb-Free) | 1000 / Tape & Reel    |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

### **CIRCUIT DESCRIPTION**

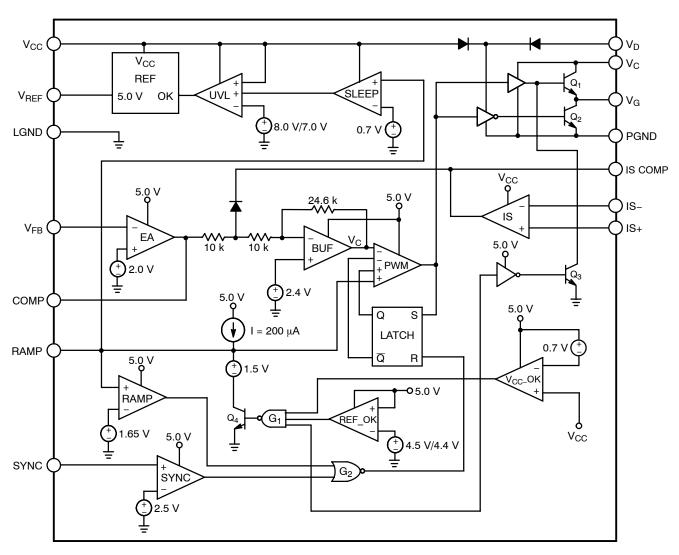

Figure 2. Block Diagram

#### **Theory of Operation**

The CS5101 is designed to regulate voltages in multiple output power supplies. Functionally, it is similar to a magnetic amplifier, operating as a switch with a delayed turn-on. It can be used with both single ended and dual ended topologies.

The  $V_{FB}$  voltage is monitored by the error amplifier EA. It is compared to an internal reference voltage and the amplified differential signal is fed through an inverting amplifier into the buffer, BUF. The buffered signal is compared at the PWM comparator with the ramp voltage generated by capacitor  $C_R$ . When the ramp voltage  $V_R$ , exceeds the control voltage  $V_C$ , the output of the PWM comparator goes high, latching its state through the LATCH, the output stage transistor  $Q_1$  turns on, and the external power switch, usually an N-FET, turns on.

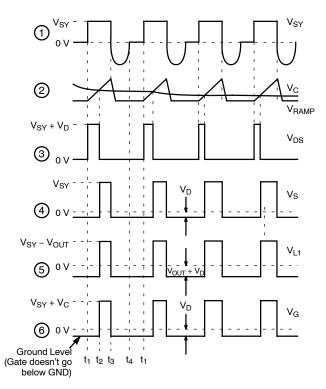

#### **SYNC Function**

The SYNC circuit is activated at time  $t_1$  (Figure 3) when the voltage at the SYNC pin exceeds the threshold level (2.5V) of the SYNC comparator. The external ramp capacitor  $C_R$  is allowed to charge through the internal current source I (200  $\mu$ A). At time  $t_2$ , the ramp voltage intersects with the control voltage  $V_C$  and the output of the PWM comparator goes high, turning on the output stage and the external power switch. At the same time, the PWM comparator is latched by the RS latch, LATCH.

Figure 3. Waveforms for CS5101. The Number to the Left of Each Curve Refers to a Node On the Application Diagram on Page 2.

The logic state of the LATCH can be changed only when both the voltage level of the trailing edge of the power pulse at the SYNC pin is less than the threshold voltage of the SYNC comparator (2.5 V) and the RAMP voltage is less than the threshold voltage of the RAMP comparator (1.65 V). On the negative going transition of the secondary side pulse V<sub>SY</sub>, gate G<sub>2</sub> output goes high, resetting the latch at time t<sub>3</sub>. Capacitor C<sub>R</sub> is discharged through transistor Q<sub>4</sub>. C<sub>R</sub>'s output goes low disabling the output stage, and the external power switch (an N–FET) is turned off.

#### **RAMP Function**

The value of the ramp capacitor  $C_R$  is based on the switching frequency of the regulator and the maximum duty cycle of the secondary pulse  $V_{SY}$ .

If the RAMP pin is pulled externally to 0.3 V or below, the SSPR is disabled. Current drawn by the IC is reduced to less than  $100 \,\mu\text{A}$ , and the IC is in SLEEP mode.

#### **FAULT Function**

The voltage at the  $V_{CC}$  pin is monitored by the undervoltage lockout comparator with hysteresis. When  $V_{CC}$  falls below the UVL threshold, the 5.0 V reference and all the circuitry running off of it is disabled. Under this condition the supply current is reduced to less than 500  $\mu$ A.

The  $V_{CC}$  supply voltage is further monitored by the  $V_{CC}$ OK comparator. When  $V_{CC}$  is reduced below  $V_{REF}$  – 0.7 V, a fault signal is sent to gate  $G_1$ . This fault signal, which determines if  $V_{CC}$  is absent, works in conjunction with the ramp signal to disable the output, but only after the current cycle has finished and the RS latch is reset. Therefore this fault will not cause the output to turn off during the middle of an on pulse, but rather will utilize lossless turn–off. This feature protects the FET from overvoltage stress. This is accomplished through gate  $G_1$  by driving transistor  $O_4$  on.

An additional fault signal is derived from the REF\_OK comparator.  $V_{REF}$  is monitored so to disable the output through gate  $G_1$  when the  $V_{REF}$  voltage falls below the OK threshold. As in the  $V_{CC}$ \_OK fault, the REF\_OK fault disables the output after the current cycle has been completed. The fault logic will operate normally only when  $V_{REF}$  voltage is within the specification limits of REF\_OK.

#### **DRAIN Function**

The drain pin,  $V_D$  monitors the voltage on the drain of the power switch and derives energy from it to keep the output stage in an off state when  $V_C$  or  $V_{CC}$  is below the minimum specified voltage.

Figure 4. CS5101 Bench Test on DIP-14 Package

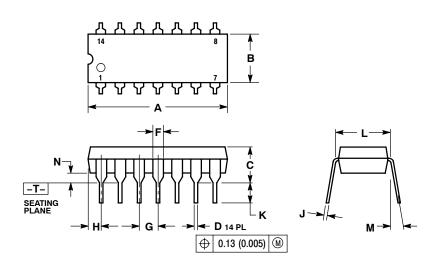

### **PACKAGE DIMENSIONS**

PDIP-14 CASE 646-06 ISSUE P

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEADS WHEN FORMED PARALLEL.

4. DIMENSION B DOES NOT INCLUDE MOLD FLASH.

5. ROUNDED CORNERS OPTIONAL.

|     | INC       | HES   | MILLIN   | IETERS |

|-----|-----------|-------|----------|--------|

| DIM | MIN       | MAX   | MIN      | MAX    |

| Α   | 0.715     | 0.770 | 18.16    | 19.56  |

| В   | 0.240     | 0.260 | 6.10     | 6.60   |

| С   | 0.145     | 0.185 | 3.69     | 4.69   |

| D   | 0.015     | 0.021 | 0.38     | 0.53   |

| F   | 0.040     | 0.070 | 1.02     | 1.78   |

| G   | 0.100 BSC |       | 2.54 BSC |        |

| Н   | 0.052     | 0.095 | 1.32 2.4 |        |

| J   | 0.008     | 0.015 | 0.20     | 0.38   |

| K   | 0.115     | 0.135 | 2.92     | 3.43   |

| L   | 0.290     | 0.310 | 7.37     | 7.87   |

| М   |           | 10 °  |          | 10 °   |

| N   | 0.015     | 0.039 | 0.38     | 1.01   |

#### PACKAGE DIMENSIONS

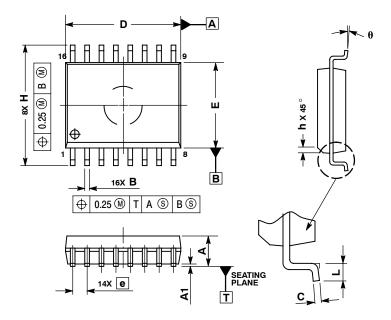

SOIC-16WB CASE 751G-03 **ISSUE C**

#### NOTES:

- 1. DIMENSIONS ARE IN MILLIMETERS.

2. INTERPRET DIMENSIONS AND TO SERVICE AND TO S INTERPRET DIMENSIONS AND TOLERANCES PER ASME Y14.5M. 1994.

- DIMENSIONS D AND E DO NOT INLCUDE

- MOLD PROTRUSION.

MAXIMUM MOLD PROTRUSION 0.15 PER SIDE.

DIMENSION B DOES NOT INCLUDE DAMBAR

PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13 TOTAL IN EXCESS OF THE B DIMENSION AT MAXIMUM MATERIAL CONDITION.

|     | MILLIMETERS |       |  |  |

|-----|-------------|-------|--|--|

| DIM | MIN         | MAX   |  |  |

| Α   | 2.35        | 2.65  |  |  |

| A1  | 0.10        | 0.25  |  |  |

| В   | 0.35        | 0.49  |  |  |

| С   | 0.23        | 0.32  |  |  |

| D   | 10.15       | 10.45 |  |  |

| Ε   | 7.40        | 7.60  |  |  |

| е   | 1.27        | BSC   |  |  |

| Н   | 10.05       | 10.55 |  |  |

| h   | 0.25        | 0.75  |  |  |

| L   | 0.50        | 0.90  |  |  |

| q   | 0 °         | 7 °   |  |  |

#### **PACKAGE THERMAL DATA**

| Parameter       |         | PDIP-14 | SOIC-16WB | Unit |

|-----------------|---------|---------|-----------|------|

| $R_{	heta JC}$  | Typical | 23      | 48        | °C/W |

| $R_{\theta JA}$ | Typical | 105     | 85        | °C/W |

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

Phone: 81-3-5773-3850

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative