# CS5320/21/22

# 24-Bit Variable Bandwidth A/D Converter Chipset

# Features

- CMOS A/D Converter Chipset

- Dynamic Range

- 130 dB @ 25 Hz Bandwidth

- 121 dB @ 411 Hz Bandwidth

- Delta-Sigma Architecture

- Fourth-Order Modulator

- Variable Oversampling: 64X to 4096X

- Internal Track-and-Hold Amplifier

- CS5321 Signal-to-Distortion: 115 dB

- Clock Jitter Tolerant Architecture

- Input Voltage Range: +4.5 V

- Flexible Filter Chip

- Hardware or Software Selectable Options

- Seven Selectable Filter Corners (-3 dB) Frequencies: 25, 51, 102, 205, 411, 824 and 1650 Hz

- Low Power Dissipation: <100 mW

# Description

The CK5320 and CK5321 Chipsets function as a unique A/D converter intended for very high resolution measurement of signals below 1500 Hz. The CK5320 Chipset is a cost effective commercial grade solution for applications which require a high dynamic range A/D converter. The chipsets perform sampling, A/D conversion, and anti-alias filtering.

The CS5320 and CS5321 use Delta-Sigma modulation to produce highly accurate conversions. The  $\Delta\Sigma$  modulator oversamples, virtually eliminating the need for external analog anti-alias filters. The CS5322 linear-phase FIR digital filter decimates the output to any one of seven selectable update periods: 16, 8, 4, 2, 1, 0.5 and 0.25 milliseconds. Data is output from the digital filter in a 24-bit serial format.

#### **ORDERING INFORMATION\***

| Chip Sets             | Kits       |

|-----------------------|------------|

| CS5320-KL & CS5322-KL | CK5320-KL1 |

| CS5321-BL & CS5322-KL | CK5321-KL1 |

| CS5321-BL & CS5322-BL | CK5321-BL1 |

\* Refer to Table 5

Preliminary Product Information

This document contains information for a new product. Cirrus Logic reserves the right to modify this product without notice.

**EIRRUS LOGIC**<sup>®</sup> P.O. Box 17847, Austin, Texas 78760 (512) 445 7222 FAX: (512) 445 7581

http://www.cirrus.com

Copyright © Cirrus Logic, Inc. 1999 (All Rights Reserved) OCT '99 DS454PP1

#### TABLE OF CONTENTS

| 1. CHARACTERISTICS AND SPECIFICATIONS              | 4  |

|----------------------------------------------------|----|

| CS5320 AND CS5321 ANALOG CHARACTERISTICS           |    |

| CS5320 AND CS5321 SWITCHING CHARACTERISTICS        | 6  |

| CS5320 AND CS5321 DIGITAL CHARACTERISTICS          | 7  |

| CS5320 AND CS5321 RECOMMENDED OPERATION CONDITIONS | 7  |

| CS5320 AND CS5321 ABSOLUTE MAXIMUM RATINGS         |    |

| CS5322 FILTER CHARACTERISTICS                      | 8  |

| CS5322 POWER SUPPLY                                |    |

| CS5322 SWITCHING CHARACTERISTICS                   | 10 |

| CS5322 DIGITAL CHARACTERISTICS                     |    |

| CS5322 RECOMMENDED OPERATION CONDITIONS            | 15 |

| CS5322 ABSOLUTE MAXIMUM RATINGS                    | 15 |

| 2. GENERAL DESCRIPTION                             | 16 |

| 2.1. Analog Input                                  |    |

| 2.2. The OFST Pin                                  |    |

| 2.3. Input Range and Overrange Conditions          |    |

| 2.4. Voltage Reference                             |    |

| 2.5. Clock Source                                  |    |

| 2.6. Low Power Mode                                |    |

| 2.7. Digital Interface and Data Format             |    |

| 2.8. Performance                                   |    |

| 2.9. Power Supply Considerations                   |    |

| 2.10. Power Supply Rejection Ratio                 |    |

| 2.11. RESET Operation                              |    |

| 2.12. Power-down Operation                         |    |

| 2.13. SYNC Operation                               |    |

| 2.14. Serial Read Operation                        |    |

| 2.15. Serial Write Operation                       |    |

| 2.16. Offset Calibration Operation                 |    |

| 2.17. Status Bits                                  |    |

| 2.18. Board Layout Considerations                  |    |

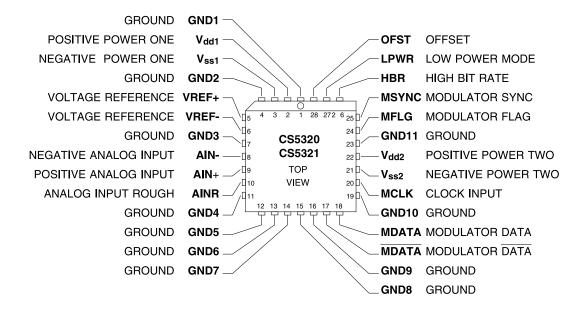

| 3. CS5320/21 PIN DESCRIPTIONS                      |    |

| Power Supplies                                     |    |

| Analog Inputs                                      |    |

| Digital Inputs                                     |    |

| Digital Outputs                                    | 30 |

#### **Contacting Cirrus Logic Support**

For a complete listing of Direct Sales, Distributor, and Sales Representative contacts, visit the Cirrus Logic web site at: http://www.cirrus.com/corporate/contacts/

Preliminary product information describes products which are in production, but for which full characterization data is not yet available. Advance product information describes products which are in development and subject to development changes. Cirrus Logic, Inc. has made best efforts to ensure that the information contained in this document is accurate and reliable. However, the information is subject to change without notice and is provided "AS IS" without warranty of any kind (express or implied). No responsibility is assumed by Cirrus Logic, Inc. for the use of this information, no for infringements of patents or other rights of third parties. This document is the property of Cirrus Logic, Inc. and implies no license under patents, copyrights, trademarks, or trade secrets. No part of this publication may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Items from any Cirrus Logic website or disk may be printed for use by the user. However, no part of the printout or electronic files may be copied, reproduced, stored in a retrieval system, or transmitted, in any form or by any means (electronic, mechanical, photographic, or otherwise) without the prior written consent of Cirrus Logic, Inc. Furthermore, no part of this publication may be used as a basis for manufacture or sale of any items without the prior written consent of Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or ofher vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trademarks and service marks can be found at http://www.cirrus.com.

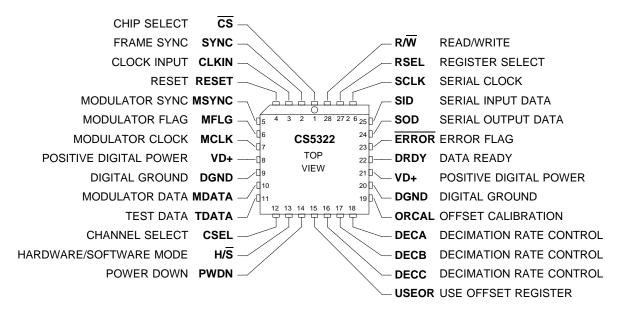

| 4. | CS5322 PIN DESCRIPTIONS |  |

|----|-------------------------|--|

|    | Power Supplies          |  |

|    | Digital Outputs         |  |

|    | Digital Inputs          |  |

| 5. | ORDERING INFORMATION    |  |

| 6. | PARAMETER DEFINITIONS   |  |

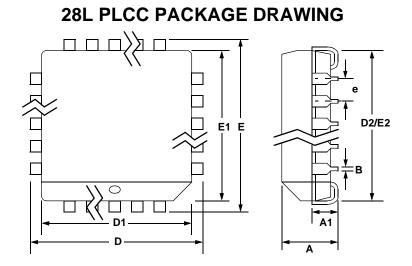

| 7. | PACKAGE DIMENSIONS      |  |

# LIST OF FIGURES

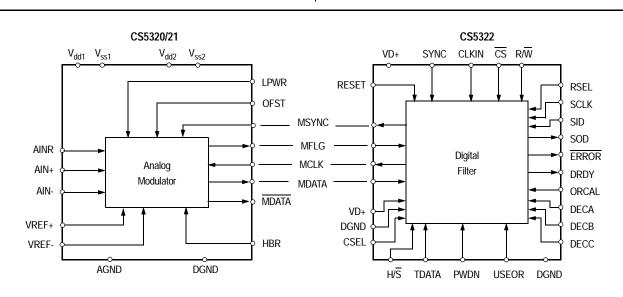

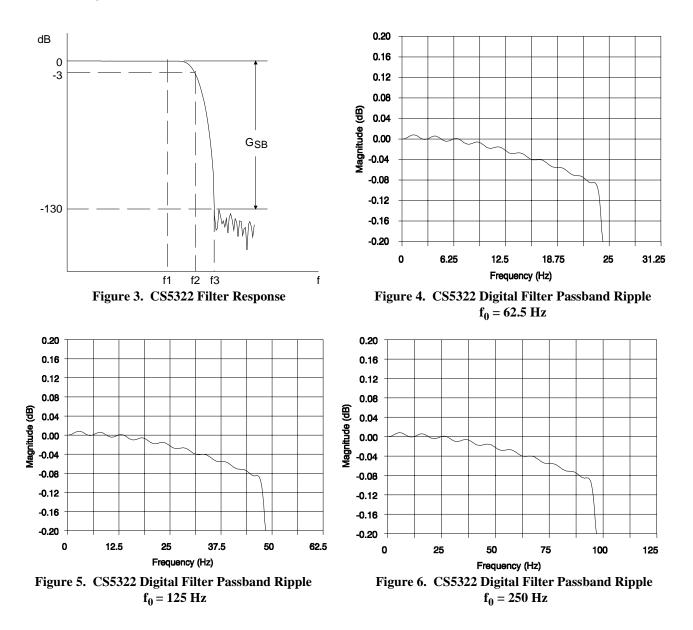

| Figure 4. CS5322 Digital Filter Passband Ripple $f_0 = 62.5$ Hz8Figure 5. CS5322 Digital Filter Passband Ripple $f_0 = 125$ Hz8Figure 6. CS5322 Digital Filter Passband Ripple $f_0 = 500$ Hz8Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500$ Hz9Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000$ Hz9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000$ Hz9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000$ Hz9Figure 11. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 12. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5322 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                  | Figure 1. Rise and Fall Times                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

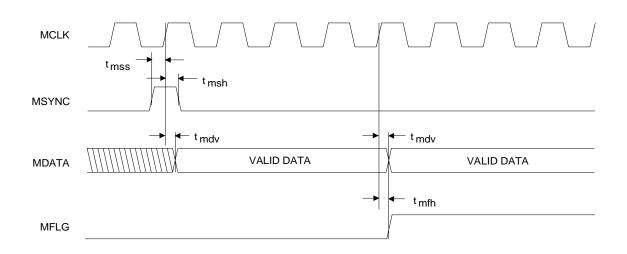

| Figure 3. CS5322 Filter Response8Figure 4. CS5322 Digital Filter Passband Ripple $f_0 = 62.5$ Hz8Figure 5. CS5322 Digital Filter Passband Ripple $f_0 = 125$ Hz8Figure 6. CS5322 Digital Filter Passband Ripple $f_0 = 500$ Hz8Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500$ Hz9Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000$ Hz9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000$ Hz9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000$ Hz9Figure 11. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 12. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5322 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22 | Figure 2. CS5320 and CS5321 Interface Timing, HBR=1                                   |

| Figure 5. CS5322 Digital Filter Passband Ripple $f_0 = 125 \text{ Hz}$ 8Figure 6. CS5322 Digital Filter Passband Ripple $f_0 = 250 \text{ Hz}$ 8Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500 \text{ Hz}$ 9Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000 \text{ Hz}$ 9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000 \text{ Hz}$ 9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$ 9Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$ 9Figure 12. CS5322 Serial Port Timing11Figure 13. CS5322 Serial Port Timing12Figure 14. TDATA Setup/Hold Timing13Figure 15. DRDY Timing13Figure 16. RESET Timing14Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5322 Block Diagram16Figure 20. System Connection Diagram17Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                | Figure 3. CS5322 Filter Response                                                      |

| Figure 6. CS5322 Digital Filter Passband Ripple $f_0 = 250$ Hz8Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500$ Hz9Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000$ Hz9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000$ Hz9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000$ Hz9Figure 11. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 12. CS5322 Impulse Response $f_0 = 1000$ Hz9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram17Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                              | Figure 4. CS5322 Digital Filter Passband Ripple $f_0 = 62.5 \text{ Hz}$               |

| Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500 \text{ Hz}$ 9Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000 \text{ Hz}$ 9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000 \text{ Hz}$ 9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$ 9Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$ 9Figure 12. CS5322 Serial Port Timing11Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram17Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                             | Figure 5. CS5322 Digital Filter Passband Ripple $f_0 = 125 \text{ Hz}$                |

| Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000 \text{ Hz}$ 9Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000 \text{ Hz}$ 9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$ 9Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$ 9Figure 12. CS5322 Impulse Response $f_0 = 1000 \text{ Hz}$ 9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                               | Figure 6. CS5322 Digital Filter Passband Ripple $f_0 = 250 \text{ Hz}$                |

| Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000 \text{ Hz}$ 9Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$ 9Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$ 9Figure 12. CS5322 Impulse Response $f_0 = 1000 \text{ Hz}$ 9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                        | Figure 7. CS5322 Digital Filter Passband Ripple $f_0 = 500 \text{ Hz}$                |

| Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$ 9Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$ 9Figure 12. CS5322 Impulse Response $f_0 = 1000 \text{ Hz}$ 9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                 | Figure 8. CS5322 Digital Filter Passband Ripple $f_0 = 1000 \text{ Hz}$               |

| Figure 11. CS5322 Impulse Response $f_0 = 62.5$ Hz9Figure 12. CS5322 Impulse Response $f_0 = 1000$ Hz9Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Figure 9. CS5322 Digital Filter Passband Ripple $f_0 = 2000 \text{ Hz}$               |

| Figure 12. CS5322 Impulse Response f <sub>0</sub> = 1000 Hz       9         Figure 13. CS5322 Serial Port Timing       11         Figure 14. TDATA Setup/Hold Timing       12         Figure 15. DRDY Timing       13         Figure 16. RESET Timing       13         Figure 17. CS5320/21/CS5322 Interface Timing       14         Figure 18. CS5320/21/CS5322 Interface Timing       16         Figure 19. CS5322 Block Diagram       16         Figure 20. System Connection Diagram       19         Figure 21. 4.5 Voltage Reference with two filter options       20         Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages       22                                                                                                                                                                                                                                                                                                                     | Figure 10. CS5322 Digital Filter Passband Ripple $f_0 = 4000 \text{ Hz}$              |

| Figure 13. CS5322 Serial Port Timing11Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 19. CS5322 Block Diagram17Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Figure 11. CS5322 Impulse Response $f_0 = 62.5 \text{ Hz}$                            |

| Figure 14. TDATA Setup/Hold Timing12Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 19. CS5322 Block Diagram17Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 12. CS5322 Impulse Response $f_0 = 1000 \text{ Hz}$                            |

| Figure 15. DRDY Timing13Figure 16. RESET Timing13Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 19. CS5322 Block Diagram17Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Figure 13. CS5322 Serial Port Timing 11                                               |

| Figure 16. RESET Timing13Figure 17. CS5320/21/CS5322 Interface Timing14Figure 18. CS5320/21 Block Diagram16Figure 19. CS5322 Block Diagram17Figure 20. System Connection Diagram19Figure 21. 4.5 Voltage Reference with two filter options20Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 14. TDATA Setup/Hold Timing 12                                                 |

| Figure 17. CS5320/21/CS5322 Interface Timing       14         Figure 18. CS5320/21 Block Diagram       16         Figure 19. CS5322 Block Diagram       17         Figure 20. System Connection Diagram       19         Figure 21. 4.5 Voltage Reference with two filter options       20         Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 15. DRDY Timing 13                                                             |

| Figure 18. CS5320/21 Block Diagram       16         Figure 19. CS5322 Block Diagram       17         Figure 20. System Connection Diagram       19         Figure 21. 4.5 Voltage Reference with two filter options       20         Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Figure 16. RESET Timing 13                                                            |

| Figure 19. CS5322 Block Diagram       17         Figure 20. System Connection Diagram       19         Figure 21. 4.5 Voltage Reference with two filter options       20         Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages       22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Figure 17. CS5320/21/CS5322 Interface Timing 14                                       |

| Figure 20. System Connection Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Figure 18. CS5320/21 Block Diagram16                                                  |

| Figure 21. 4.5 Voltage Reference with two filter options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Figure 19. CS5322 Block Diagram 17                                                    |

| Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 20. System Connection Diagram 19                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 21. 4.5 Voltage Reference with two filter options 20                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Figure 22. 1024 Point FFT Plot with -20 dB Input, 100 Hz Input, ten averages 22       |

| Figure 23. 1024 Point FFT Plot with Full Scale Input, 100 Hz Input, ten averages 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 23. 1024 Point FFT Plot with Full Scale Input, 100 Hz Input, ten averages 22   |

| Figure 24. 1024 Point FFT Plot with Full Scale Input, 100 Hz Input, ten averages 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Figure 24. 1024 Point FFT Plot with Full Scale Input, 100 Hz Input, ten averages $22$ |

# LIST OF TABLES

| Table 1. | Output Coding for the CS5320/21 and CS5322 Combination | . 21 |

|----------|--------------------------------------------------------|------|

| Table 2. | Configuration Data Bits                                | . 24 |

| Table 3. | Status Data (from the SOD Pin)                         | . 26 |

| Table 4. | Bandwidth Selection: Truth Table                       | . 27 |

| Table 5. | Detailed Ordering Information                          | . 34 |

# 1. CHARACTERISTICS AND SPECIFICATIONS

**CS5320 AND CS5321 ANALOG CHARACTERISTICS** ( $T_A = (\text{See Note 1}); V_{ss1}, V_{ss2} = -5V; V_{dd1}, V_{dd2} = +5V; VD+ = 5V; AGND = DGND = 0V; HBR = V_{dd} LPWR = 0, MCLK = 1.024 MHz; Device connected as shown in Figure 20, CS5322 used for filtering; Logic 1 = VD+, Logic 0 = 0V; unless otherwise specified.)$

|                            |                          |                   |     | CS5320 |     |     | CS5321 |     |        |

|----------------------------|--------------------------|-------------------|-----|--------|-----|-----|--------|-----|--------|

| Paramet                    | er*                      | Symbol            | Min | Тур    | Мах | Min | Тур    | Max | Unit   |

| Dynamic Performance        |                          |                   |     |        |     | I   |        |     |        |

| Dynamic Range              | (Note 2)                 | DR                |     |        |     |     |        |     |        |

| HBR = 1                    | f <sub>O</sub> = 4000 Hz |                   | -   | 103    | -   | -   | 103    | -   | dB     |

| OFST = 1                   | f <sub>O</sub> = 2000 Hz |                   | -   | 118    | -   | -   | 118    | -   | dB     |

|                            | f <sub>O</sub> = 1000 Hz |                   | 113 | 121    | -   | 116 | 121    | -   | dB     |

|                            | f <sub>O</sub> = 500 Hz  |                   | -   | 124    | -   | -   | 124    | -   | dB     |

|                            | f <sub>O</sub> = 250 Hz  |                   | -   | 127    | -   | -   | 127    | -   | dB     |

|                            | f <sub>O</sub> = 125 Hz  |                   | -   | 129    | -   | -   | 129    | -   | dB     |

|                            | f <sub>O</sub> = 62.5 Hz |                   | -   | 130    | -   | -   | 130    | -   | dB     |

| HBR = 0                    | f <sub>O</sub> = 4000 Hz |                   | -   | 99     | -   | -   | 99     | -   | dB     |

| OFST = 1                   | f <sub>O</sub> = 2000 Hz |                   | -   | 115    | -   | -   | 115    | -   | dB     |

|                            | f <sub>O</sub> = 1000 Hz |                   | -   | 118    | -   | -   | 118    | -   | dB     |

|                            | f <sub>O</sub> = 500 Hz  |                   | -   | 121    | -   | -   | 121    | -   | dB     |

|                            | f <sub>O</sub> = 250 Hz  |                   | -   | 124    | -   | -   | 124    | -   | dB     |

|                            | f <sub>O</sub> = 125 Hz  |                   | -   | 126    | -   | -   | 126    | -   | dB     |

|                            | f <sub>O</sub> = 62.5 Hz |                   | -   | 127    | -   | -   | 127    | -   | dB     |

| Signal-to-Distortion       | (Note 3)                 | SDR               |     |        |     |     |        |     |        |

|                            | HBR = 1                  |                   | 100 | 110    | -   | 100 | 115    | -   | dB     |

|                            | HBR = 0                  |                   | -   | 120    | -   | 110 | 120    | -   | dB     |

| Intermodulation Distortion | (Note 4)                 | IMD               | -   | 105    | -   | -   | 110    | -   | dB     |

| dc Accuracy                |                          |                   |     |        |     |     |        |     |        |

| Full Scale Error           | (Note 5)                 | FSE               | -   | 1      | -   | -   | 1      | -   | %      |

| Full Scale Drift           | (Note 5,6)               | TC <sub>FS</sub>  | -   | 5      | -   | -   | 5      | -   | ppm/°C |

| Offset                     | (Note 5)                 | V <sub>ZSE</sub>  | -   | 10     | -   | -   | 10     | -   | mV     |

| Offset after Calibration   | (Note 7)                 |                   | -   | ±100   | -   | -   | ±100   | -   | μV     |

| Offset Calibration Range   | (Note 8)                 |                   | -   | 100    | -   | -   | 100    | -   | %F.S.  |

| Offset Drift               | (Note 5,6)               | TC <sub>ZSE</sub> | -   | 60     | -   | -   | 60     | -   | µV/°C  |

Notes: 1. CS5320-KL and CS5322-KL are guaranteed from 0° to 70° C. CS5322-BL is guaranteed from -40° to +85° C. CS5321-BL is guaranteed from -55° to +85° C.

2. f<sub>O</sub> = CS5322 output word rate. Refer to "CS5322 FILTER CHARACTERISTICS" on page 8 for details on the FIR Filter.

- 3. Characterized with full scale input signal of 50 Hz; fo = 500 Hz.

- 4. Characterized with input signals of 30 Hz and 50 Hz, each 6 dB down from full scale with fo = 1000 Hz.

- 5. Specification is for the parameter over the specified temperature range and is for the CS5320/21 device only (VREF = +4.5 V). It does not include the effects of external components; OFST = 0.

- 6. Drift specifications are guaranteed by design and/or characterization.

The offset after calibration specification applies to the effective offset voltage for a ±4.5 volt input to the CS5320/21 modulator, but is relative to the output digital codes from the CS5322 after ORCAL and USEOR have been made active.

The CS5322 offset calibration is performed digitally and includes ± full scale (±4.5 volts into CS5320/21). Calibration of offsets greater than ±5% of full scale will begin to subtract from the dynamic range.

# CS5320 AND CS5321 ANALOG CHARACTERISTICS (Continued)

|                                                  |                  |      | CS5320/2 | 1    |       |

|--------------------------------------------------|------------------|------|----------|------|-------|

| Parameter*                                       | Symbol           | Min  | Тур      | Max  | Unit  |

| Input Characteristics                            | •                | •    |          |      |       |

| Input Signal Frequencies (Note 9)                | BW               | dc   | -        | 1500 | Hz    |

| Input Voltage Range (Note 10)                    | V <sub>IN</sub>  | -4.5 | -        | +4.5 | V     |

| Input Overrange Voltage (Note 10)                | I <sub>OVR</sub> | -    | -        | 5    | %F.S. |

| Power Supplies                                   | •                | •    |          |      |       |

| DC Power Supply Currents (Note 11)               |                  |      |          |      |       |

| LPWR = 0 Positive Supplies                       |                  | -    | 5.5      | 7.5  | mA    |

| Negative Supplies                                |                  | -    | 5.5      | 7.5  | mA    |

| LPWR = 1 Positive Supplies                       |                  |      | 3.0      | 4.5  | mA    |

| Negative Supplies                                |                  |      | 3.0      | 4.5  | mA    |

| Power Consumption (Note 11)                      |                  |      |          |      |       |

| Normal Operating Mode (Note12)                   | P <sub>DN</sub>  | -    | 55       | 75   | mW    |

| Lower Power Mode (Note 13)                       | P <sub>DL</sub>  | -    | 30       | 45   | mW    |

| Power Down                                       | PD               | -    | 2        | -    | mW    |

| Power Supply Rejection (dc to 128 kHz) (Note 14) | PSR              | -    | 60       | -    | dB    |

Notes: 9. The upper bandwidth limit is determined by the CS5322 digital filter.

- 10. This input voltage range is for the configuration shown in Figure 20, the System Connection Diagram, and applies to signal from dc to f3 Hz. Refer to CS5322 Filter Characteristics for the values of f3.

- 11. All outputs unloaded. All logic inputs forced to  $V_{dd}\, or \, GND$  respectively.

- 12. LPWR = 0.

- 13. The CS5321 power dissipation can be reduced under the following conditions:

- a) LPWR=1; MCLK=512kHz, HBR=1

- b) LWPR=1; MCLK=1.024MHz, HBR=0

- 14. Characterized with a 100 mVp-p sine wave applied separately to each supply.

\* Refer to Parameter Definitions (immediately following pin descriptions at the end of this data sheet).

Specifications are subject to change without notice.

# CS5320 AND CS5321 SWITCHING CHARACTERISTICS (T<sub>A</sub> = (See Note 1); $V_{dd1}$ , $V_{dd2}$ =

$5V \pm 5\%$ ; V<sub>ss1</sub>, V<sub>ss2</sub> = -5V ± 5%; Inputs: Logic 0 = 0V Logic 1 = V+; C<sub>L</sub> = 50 pF (Note 15))

|                        | Parameter                               |           | Symbol                                      | Min   | Тур     | Max        | Units    |

|------------------------|-----------------------------------------|-----------|---------------------------------------------|-------|---------|------------|----------|

| MCLK Frequency         |                                         | (Note 16) | f <sub>c</sub>                              | 0.250 | 1.024   | 1.2        | MHz      |

| MCLK Duty Cycle        |                                         |           |                                             | 40    | -       | 60         | %        |

| MCLK Jitter (In-band)  |                                         |           |                                             | -     | -       | 300        | ps       |

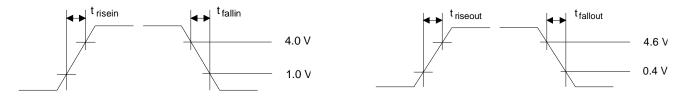

| Rise Times:            | Any Digital Input<br>Any Digital Output | (Note 17) | t <sub>risein</sub><br>t <sub>riseout</sub> | -     | -<br>50 | 100<br>200 | ns<br>ns |

| Fall Times:            | Any Digital Input<br>Any Digital Output | (Note 17) | t <sub>fallin</sub><br>t <sub>fallout</sub> | -     | -<br>50 | 100<br>200 | ns<br>ns |

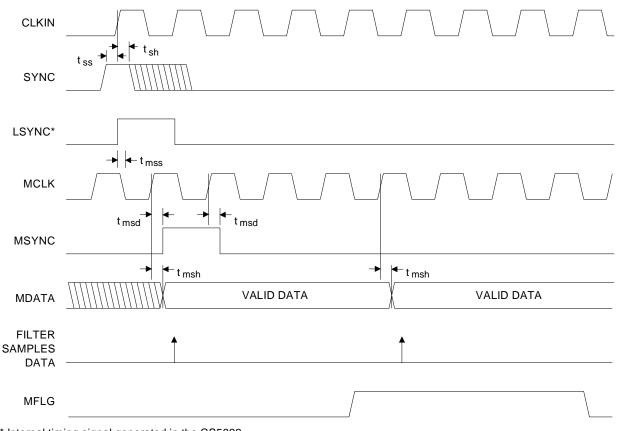

| MSYNC Setup Time t     | o MCLK rising                           |           | t <sub>mss</sub>                            | 20    | -       | -          | ns       |

| MSYNC Hold Time af     | ter MCLK rising                         |           | t <sub>msh</sub>                            | 20    | -       | -          | ns       |

| MCLK rising to Valid I | MFLG                                    |           | t <sub>mfh</sub>                            | -     | 140     | 255        | ns       |

| MCLK rising to Valid I | MDATA                                   |           | t <sub>mdv</sub>                            | -     | 170     | 300        | ns       |

Notes: 15. Guaranteed by design, characterization, or test.

- 16. If MCLK is removed, the modulator will enter the power down mode.

- 17. Excludes MCLK input. MCLK should be driven with a signal having rise and fall times of 25 ns or faster.

Figure 1. Rise and Fall Times

# CS5320 AND CS5321 DIGITAL CHARACTERISTICS ( $T_A = (See Note 1); V_{dd1} = V_{dd2} = V_{dd2}$

$5.0V \pm 5\%$ ; GND = 0V; measurements performed under static conditions)

| Parameter                               |           | Symbol           | Min                    | Тур | Max | Units |

|-----------------------------------------|-----------|------------------|------------------------|-----|-----|-------|

| High-Level Input Drive Voltage          | (Note 18) | V <sub>IH</sub>  | (V <sub>dd</sub> )-0.6 | -   | -   | V     |

| Low-Level Input Drive Voltage           | (Note 18) | V <sub>IL</sub>  | -                      | -   | 1.0 | V     |

| High-Level Output Voltage IOUT = -40 µA | (Note 19) | V <sub>OH</sub>  | (V <sub>dd</sub> )-0.3 | -   | -   | V     |

| Low-Level Output Voltage IOUT = +40 µA  | (Note 19) | V <sub>OL</sub>  | -                      | -   | 0.3 | V     |

| Input Leakage Current                   |           | I <sub>LKG</sub> | -                      | -   | ±10 | μA    |

| Digital Input Capacitance               |           | C <sub>IN</sub>  | -                      | 9   | -   | pF    |

| Digital Output Capacitance              |           | C <sub>OUT</sub> | -                      | 9   | -   | pF    |

Notes: 18. Device is intended to be driven with CMOS logic levels.

19. Device is intended to be interfaced to CMOS logic. Resistive loads are not recommended on these pins.

# CS5320 AND CS5321 RECOMMENDED OPERATION CONDITIONS (Voltages with

respect to GND = 0V, See Note 20)

| Parameter                         | Symbol                             | Min   | Тур  | Max   | Units |

|-----------------------------------|------------------------------------|-------|------|-------|-------|

| DC Supply: Positive               | V <sub>dd1</sub> ,V <sub>dd2</sub> | 4.75  | 5.0  | 5.25  | V     |

| Negative                          | $V_{ss1}, V_{ss2}$                 | -4.75 | -5.0 | -5.25 | V     |

| Ambient Operating Temperature -KL | Τ <sub>Α</sub>                     | 0     | -    | +70   | °C    |

| -BL                               | T <sub>A</sub>                     | -55   | -    | +85   | °C    |

Notes: 20. The maximum voltage differential between the Positive Supply of the CS5320/21 and the Positive Digital Supply of the CS5322 must be less than 0.25V.

# CS5320 AND CS5321 ABSOLUTE MAXIMUM RATINGS \* (Voltages with respect to

| GND = 0V |  |

|----------|--|

|----------|--|

| Parameter                              |           | Symbol                             | Min  | Max                    | Units |

|----------------------------------------|-----------|------------------------------------|------|------------------------|-------|

| DC Supply:                             | Positive  | V <sub>dd1</sub> ,V <sub>dd2</sub> | -0.3 | 6.0                    | V     |

|                                        | Negative  | $V_{ss1}, V_{ss2}$                 | +0.3 | -6.0                   | V     |

| Input Current, Any Pin Except Supplies | (Note 21) | l <sub>in</sub>                    | -    | ±10                    | mA    |

| Output Current                         |           | I <sub>out</sub>                   | -    | 25                     | mA    |

| Total Power (all supplies and outputs) |           | Pt                                 | -    | 1                      | W     |

| Digital Input Voltage                  |           | V <sub>IND</sub>                   | -0.3 | (V <sub>dd</sub> )+0.3 | V     |

| Storage Temperature                    |           | T <sub>stg</sub>                   | -65  | 150                    | °C    |

Notes: 21. Transient currents of up to 100 mA will not cause SCR latch up.

\*WARNING: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

# **CS5322 FILTER CHARACTERISTICS** ( $T_A = (See Note 1); VD + = 5.0V; GND = 0V;$

CLKIN = 1.024 MHz; transfer function shown in Figure 3; unless otherwise specified.)

| Output Word Rate<br>f <sub>0</sub> (Hz) | Passband f1<br>(Hz) | Passband Flatness<br>R <sub>PB</sub> (dB) | -3dB Freq. f2<br>(Hz) | Stopband f3 (Hz)<br>(Note 22) | Group Delay<br>(ms) |

|-----------------------------------------|---------------------|-------------------------------------------|-----------------------|-------------------------------|---------------------|

| 4000                                    | 1500                | 0.2                                       | 1652.5                | 2000                          | 7.25                |

| 2000                                    | 750                 | 0.04                                      | 824.3                 | 1000                          | 14.5                |

| 1000                                    | 375                 | 0.08                                      | 411.9                 | 500                           | 29                  |

| 500                                     | 187.5               | 0.1                                       | 205.9                 | 250                           | 58                  |

| 250                                     | 93.8                | 0.1                                       | 102.9                 | 125                           | 116                 |

| 125                                     | 46.9                | 0.1                                       | 51.5                  | 62.5                          | 232                 |

| 62.5                                    | 23.4                | 0.1                                       | 25.7                  | 31.25                         | 464                 |

Notes: 22.  $G_{SB} = -130 \text{ dB}$  for all Output Word Rates.

# CS5320/21/22

# CS5322 POWER SUPPLY (T<sub>A</sub> = (See Note 1); VD+ = 5V; CLKIN = 1.024 MHz)

|                       |      |           | CS5322-K |     |     | CS5322-B |     |     |      |

|-----------------------|------|-----------|----------|-----|-----|----------|-----|-----|------|

| Parame                | eter |           | Min      | Тур | Мах | Min      | Тур | Мах | Unit |

| Power Supply Current: | ID+  | (Note 11) | -        | 2.2 | 4   | -        | 2.2 | 4   | mA   |

| Power Dissipation:    |      | (Note 11) |          |     |     |          |     |     |      |

|                       |      | PWDN Low  | -        | 11  | 20  | -        | 11  | 20  | mW   |

|                       |      | PWDN High | -        | 0.6 | 2.5 | -        | 0.6 | 2.5 | mW   |

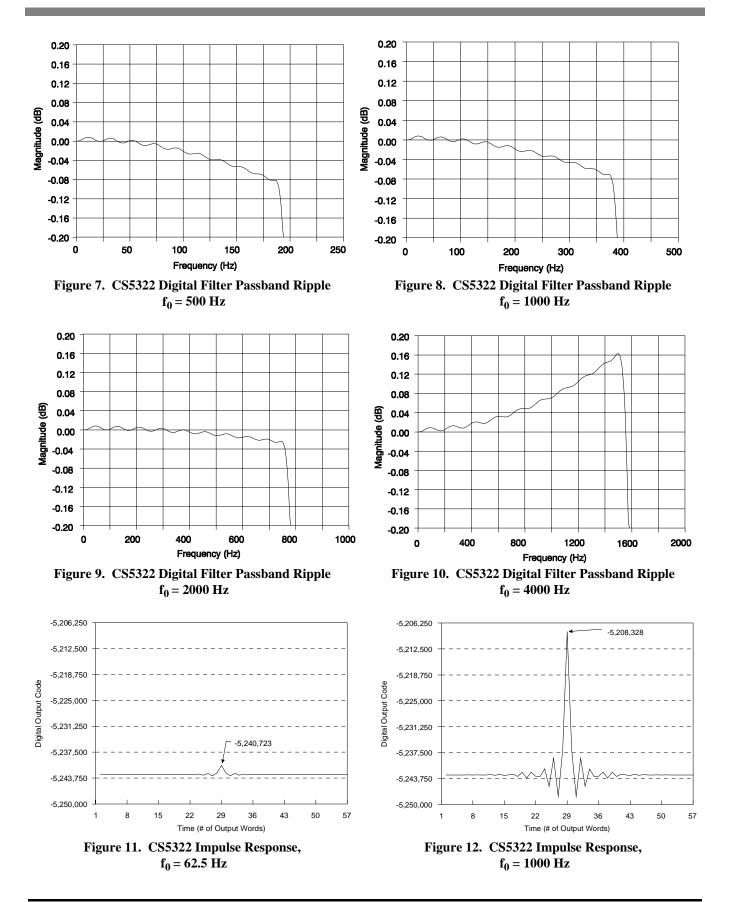

# **CS5322 SWITCHING CHARACTERISTICS** ( $T_A = (\text{See Note 1}); VD + = 5V \pm 5\%; DGND = 0V;$ Inputs: Logic 0 = 0V Logic 1 = VD+; $C_L = 50 \text{ pF}$ (Note 23)

|                                           | Parameter                               | Symbol                               | Min   | Тур     | Мах        | Units    |

|-------------------------------------------|-----------------------------------------|--------------------------------------|-------|---------|------------|----------|

| CLKIN Frequency                           |                                         | f <sub>c</sub>                       | 0.512 | 1.024   | 1.2        | MHz      |

| CLKIN Duty Cycle                          |                                         |                                      | 40    | -       | 60         | %        |

| Rise Times:                               | Any Digital Input<br>Any Digital Output | t <sub>rise</sub>                    | -     | -<br>50 | 100<br>100 | ns<br>ns |

| Fall Times:                               | Any Digital Input<br>Any Digital Output | t <sub>fall</sub>                    | -     | -<br>50 | 100<br>100 | ns<br>ns |

| Serial Port Read Til                      | ming                                    |                                      |       |         |            |          |

| DRDY to Data Valid                        |                                         | t <sub>ddv</sub>                     | -     | -       | 25         | ns       |

| RSEL Setup Time be                        | efore Data Valid                        | t <sub>rss</sub>                     | 50    | -       | -          | ns       |

| Read Setup before C                       | CS Active                               | t <sub>rsc</sub>                     | 20    | -       | -          | ns       |

| Read Active to Data                       | Valid                                   | t <sub>rdv</sub>                     | -     | -       | 50         | ns       |

| SCLK rising to New S                      | SOD bit                                 | t <sub>rdd</sub>                     | -     | -       | 50         | ns       |

| SCLK Pulse Width H                        | ligh                                    | t <sub>rph</sub>                     | 30    | -       | -          | ns       |

| SCLK Pulse Width L                        | ow                                      | t <sub>rpl</sub>                     | 30    | -       | -          | ns       |

| SCLK Period                               |                                         | t <sub>rsp</sub>                     | 100   | -       | -          | ns       |

| SCLK falling to DRD                       | Y falling                               | t <sub>rst</sub>                     | -     | -       | 50         | ns       |

| CS High to Output H                       | i-Z                                     | t <sub>rch</sub>                     | -     | -       | 20         | ns       |

| Read Hold Time afte                       | r CS Inactive                           | t <sub>rhc</sub>                     | 20    | -       | -          | ns       |

| Read Select Setup to                      | o SCLK falling                          | t <sub>rds</sub>                     | 20    | -       | -          | ns       |

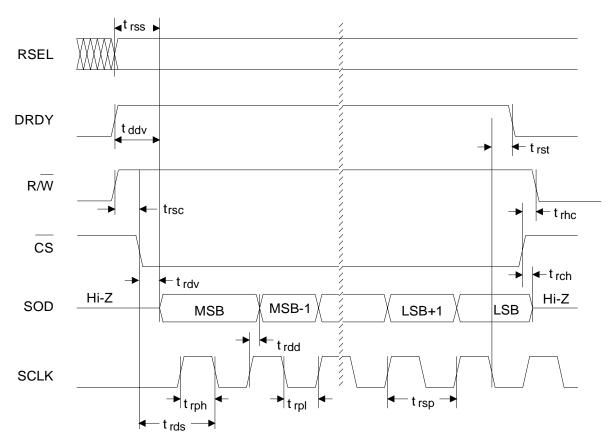

| Serial Port Write Til                     | ming                                    |                                      |       |         |            |          |

| Write Setup Before C                      | CS Active                               | t <sub>wsc</sub>                     | 20    | -       | -          | ns       |

| SCLK Pulse Width L                        | ow                                      | t <sub>wpl</sub>                     | 30    | -       | -          | ns       |

| SCLK Pulse Width H                        | ligh                                    | t <sub>wph</sub>                     | 30    | -       | -          | ns       |

| SCLK Period                               |                                         | t <sub>wsp</sub>                     | 100   | -       | -          | ns       |

| Write Setup Time to First SCLK falling    |                                         | t <sub>wws</sub>                     | 20    | -       | -          | ns       |

| Data Setup Time to F                      | Data Setup Time to First SCLK falling   |                                      | 20    | -       | -          | ns       |

| Write Select Hold Time after SCLK falling |                                         | t <sub>wds</sub><br>t <sub>wwh</sub> | 20    | -       | -          | ns       |

| Write Hold Time afte                      | r CS Inactive                           | t <sub>whc</sub>                     | 20    | -       | -          | ns       |

| Data Hold Time after                      | SCLK falling                            | t <sub>wdh</sub>                     | 20    | -       | -          | ns       |

|                                           |                                         |                                      |       |         |            |          |

23. Guaranteed by design, characterization and/or test.

Serial Port Read Timing  $(R/\overline{W} = 1, CS = 0, RSEL = 1 DRDY Does not toggle if reading status, RSEL = 0)$

Serial Port Write Timing

Figure 13. CS5322 Serial Port Timing

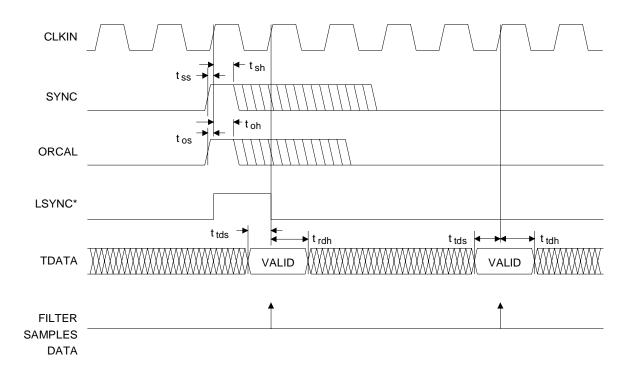

# CS5322 SWITCHING CHARACTERISTICS (continued)

| Parameter                                   | Symbol           | Min | Тур | Max | Units |

|---------------------------------------------|------------------|-----|-----|-----|-------|

| Test Data (TDATA) Timing                    |                  |     |     | 1   |       |

| SYNC Setup Time to CLKIN rising             | t <sub>ss</sub>  | 20  | -   | -   | ns    |

| SYNC Hold Time after CLKIN rising           | t <sub>sh</sub>  | 20  | -   | -   | ns    |

| TDATA Setup Time to CLKIN rising after SYNC | t <sub>tds</sub> | -   | 20  | -   | ns    |

| TDATA Hold Time after CLKIN rising          | t <sub>tdh</sub> | -   | 150 | -   | ns    |

| ORCAL Setup Time to CLKIN rising            | t <sub>os</sub>  | 20  | -   | -   | ns    |

| ORCAL Hold Time after CLKIN rising          | t <sub>oh</sub>  | 20  | -   | -   | ns    |

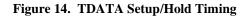

| DRDY Timing                                 | ·                |     |     |     |       |

| CLKIN rising to DRDY falling                | t <sub>df</sub>  | -   | 140 | -   | ns    |

| CLKIN falling to DRDY rising                | t <sub>dr</sub>  | -   | 150 | -   | ns    |

| CLKIN rising to ERROR change                | t <sub>ec</sub>  | -   | 140 | -   | ns    |

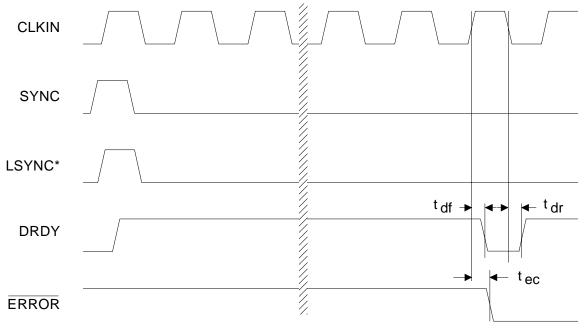

| RESET Timing                                | ·                |     |     |     |       |

| RESET Setup Time to CLKIN rising            | t <sub>rs</sub>  | 20  | -   | -   | ns    |

| RESET Hold Time after CLKIN rising          | t <sub>rh</sub>  | 20  | -   | -   | ns    |

| SYNC Setup Time to CLKIN rising             | t <sub>ss</sub>  | 20  | -   | -   | ns    |

| SYNC Hold Time after CLKIN rising           | t <sub>sh</sub>  | 20  | -   | -   | ns    |

\*Note: For overwrite case, DRDY will remain high.

Figure 15. DRDY Timing

Figure 16. RESET Timing

# CS5322 SWITCHING CHARACTERISTICS (continued)

| Parameter                  |                                         |           | Symbol            | Min   | Тур     | Max        | Units    |

|----------------------------|-----------------------------------------|-----------|-------------------|-------|---------|------------|----------|

| MCLK Frequency             |                                         | (Note 24) | f <sub>c</sub>    | 0.512 | 1.024   | 1.1        | MHz      |

| MCLK Duty Cycle            |                                         |           |                   | 40    | -       | 60         | %        |

| Rise Times:                | Any Digital Input<br>Any Digital Output | (Note 25) | t <sub>rise</sub> | -     | -<br>50 | 100<br>200 | ns<br>ns |

| Fall Times:                | Any Digital Input<br>Any Digital Output | (Note 25) | t <sub>fall</sub> | -     | -<br>50 | 100<br>200 | ns<br>ns |

| SYNC Setup Time to         | CLKIN rising                            |           | t <sub>ss</sub>   | 20    | -       | -          | ns       |

| SYNC Hold Time after       | er CLKIN rising                         |           | t <sub>sh</sub>   | 20    | -       | -          | ns       |

| CLKIN edge to MCLK edge    |                                         |           | t <sub>mss</sub>  | -     | 30      | -          | ns       |

| MCLK rising to Valid MDATA |                                         |           | t <sub>msh</sub>  | -     | 50      | -          | ns       |

| MSYNC Delay from N         | MCLK rising                             | (Note 26) | t <sub>msd</sub>  | -     | 90      | -          | ns       |

Notes: 24. If MCLK is removed, the modulator will enter the power down mode.

25. Excludes MCLK input. MCLK should be driven with a signal having rise and fall times of 25 ns or faster.26. Only the rising edge of MSYNC relative to MCLK is used to synchronize the device. MSYNC can return

low at any time as long as it remains high for at least one MCLK cycle.

\* Internal timing signal generated in the CS5322

#### Figure 17. CS5320/21/CS5322 Interface Timing

# **CS5322 DIGITAL CHARACTERISTICS** ( $T_A = (\text{See Note 1}); VD + = 5.0V \pm 5\%; GND = 0V;$

measurements performed under static conditions)

| Parameter                                   |           | Symbol           | Min       | Тур | Max | Units |

|---------------------------------------------|-----------|------------------|-----------|-----|-----|-------|

| High-Level Input Drive Voltage              |           | V <sub>IH</sub>  | (VD+)-0.3 | -   | -   | V     |

| Low-Level Input Drive Voltage               |           | V <sub>IL</sub>  | -         | -   | 0.3 | V     |

| High-Level Input Threshold                  | (Note 27) |                  | (VD+)-1.0 | -   | -   | V     |

| Low-Level Input Threshold                   | (Note 27) |                  | -         | -   | 1.0 | V     |

| High-Level Output Voltage IOUT = -40µA      | (Note 28) | V <sub>OH</sub>  | (VD+)-0.6 | -   | -   | V     |

| Low-Level Output Voltage IOUT = +1.6 mA     | (Note 28) | V <sub>OL</sub>  | -         | -   | 0.4 | V     |

| Input Leakage Current All pins except MFLG, | SOD       | I <sub>LKG</sub> | -         | -   | ±10 | μA    |

| Three-State Leakage Current                 |           | I <sub>OZ</sub>  | -         | -   | ±10 | μA    |

| Digital Input Capacitance                   |           | C <sub>IN</sub>  | -         | 9   | -   | pF    |

| Digital Output Capacitance                  |           | C <sub>OUT</sub> | -         | 9   | -   | pF    |

<sup>Notes: 27. Device is intended to be driven with CMOS logic levels.

28. Device is intended to be interfaced to CMOS logic. Resistive loads are not recommended on these pins.</sup>

# **CS5322 RECOMMENDED OPERATION CONDITIONS** (Voltages with respect to GND=0V)

|                                          | Parameter            |                                  | Symbol     | Min           | Тур         | Max           | Units  |

|------------------------------------------|----------------------|----------------------------------|------------|---------------|-------------|---------------|--------|

| DC Supply:                               |                      | (Note 29)                        |            |               |             |               |        |

|                                          | Positive<br>Negative |                                  | VD+<br>VD- | 4.75<br>-4.75 | 5.0<br>-5.0 | 5.25<br>-5.25 | V<br>V |

| Ambient Operating Temperature -KL<br>-BL |                      | T <sub>A</sub><br>T <sub>A</sub> | 0<br>-40   | -<br>-        | +70<br>+85  | °C<br>℃       |        |

Notes: 29. The maximum voltage differential between the Positive Supply of the CS5320/21 and the Positive Digital Supply of the CS5322 must be less than 0.25V.

# **CS5322 ABSOLUTE MAXIMUM RATINGS** \* (Voltages with respect to GND = 0V)

| Parameter                                        | Symbol           | Min  | Тур | Max       | Units |

|--------------------------------------------------|------------------|------|-----|-----------|-------|

| DC Supply: (Note 29)                             |                  |      |     |           |       |

| Positive                                         | VD+              | -0.3 | -   | (VD+)+0.3 | V     |

| Negative                                         | VD-              | 0.3  | -   | -6.0      | V     |

| Input Current, Any Pin Except Supplies (Note 30) | l <sub>in</sub>  | -    | -   | ±10       | mA    |

| Digital Input Voltage                            | VIND             | -0.3 | -   | (VD+)+0.3 | V     |

| Storage Temperature                              | T <sub>stg</sub> | -65  | -   | 150       | °C    |

Notes: 30. Transient currents of up to 100 mA will not cause SCR latch up.

\*WARNING: Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

## 2. GENERAL DESCRIPTION

The CS5320 and CS5321 are fourth-order CMOS monolithic analog modulators designed specifically for very high resolution measurement of signals between dc and 1500 Hz. Configuring the CS5320 or CS5321 with the CS5322 FIR filter results in a high resolution A/D converter system that performs sampling and A/D conversion with dynamic range exceeding 120 dB.

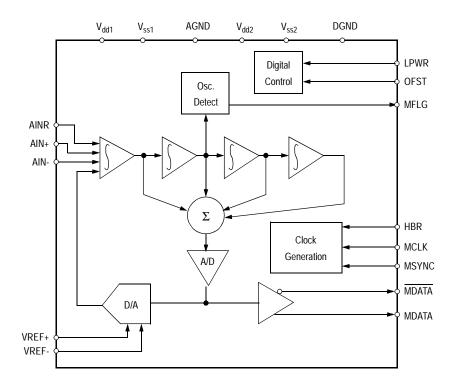

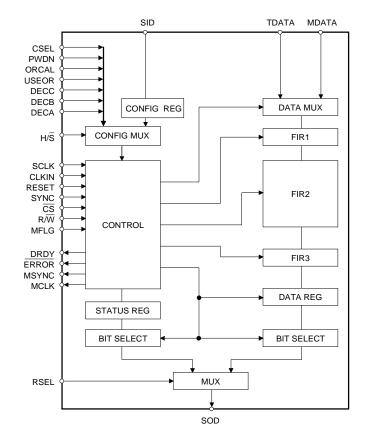

The CS5320 and CS5321 use a fourth-order oversampling architecture to achieve high resolution A/D conversion. The modulator consists of a 1-bit A/D converter embedded in a negative feedback loop. The modulator provides an oversampled serial bit stream at 256 kbits per second (HBR=1) and 128 kbits per second (HBR=0) operating with a clock rate of 1.024 MHz. Figure 18 illustrates the CS5320/CS5321 Block Diagram. The CS5322 is a monolithic digital Finite Impulse Response (FIR) filter with programmable decimation. The CS5322 and CS5320/CS5321 are intended to be used together to form a unique high dynamic range ADC chipset. The CS5322 provides the digital anti-alias filter for the CS5320/CS5321 modulator output. The CS5322 consists of: a multistage FIR filter, four registers (status, data, offset, and configuration), a flexible serial input and output port, and a 2-channel input data multiplexer that selects data from the CS5320/CS5321 (MDA-TA) or user test data (TDATA). The CS5322 decimates (64x to 4096x) the output to any of seven selectable up-date periods: 16, 8, 4, 2, 1, 0.5 and 0.25 milliseconds. Data is output from the digital filter in a 24-bit serial format. Figure 19 illustrates the CS5322 Block Diagram.

Figure 18. CS5320/21 Block Diagram

Figure 19. CS5322 Block Diagram

# 2.1 Analog Input

The CS5320 and CS5321 modulators use a switched capacitor architecture for its signal and voltage reference inputs. The signal input uses three pins; AINR, AIN+, and AIN-. The AIN- pin acts as the return pin for the AINR and AIN+ pins. The AINR pin is a switched capacitor "rough charge" input for the AIN+ pin. The input impedance for the rough charge pin (AINR) is 1/fC where f is two times the modulator sampling clock rate and C is the internal sampling capacitor (about 40 pF). Using a 1.024 MHz master clock (HBR = 1) yields an input impedance of about 1/(512 kHz)X(40 pF) or about 50 k $\Omega$ . Internal to the chip the rough charge input pre-charges the sampling capacitor used on the AIN+ input, therefore the effective input impedance on the AIN+ pin is orders of magnitude above the impedance seen on the AINR pin.

The analog input structure inside the VREF+ pin is very similar to the AINR pin but includes additional circuitry whose operating current can change over temperature and from device to device. Therefore, if gain accuracy is important, the VREF+ pin should be driven from a low source impedance. The current demand of the VREF+ pin will produce a voltage drop of approximately 45 mV across the 200  $\Omega$  source resistor of Figure 20 and Figure 21 Option A with MCLK = 1.024 MHz, HBR = 1, and temperature = 25°C.

When the CS5320/21 modulator is operated with a 4.5 V reference it will accept a 9 V p-p input signal, but modulator loop stability can be adversely affected by high frequency out-of-band signals. Therefore, input signals must be band-limited by an input filter. The -3 dB corner of the input filter must be equal to the modulator sampling clock divided by 64. The modulator sampling clock is MCLK/4 when HBR = 1 or MCLK/8 when HBR = 0. With MCLK = 1.024 MHz, HBR = 1, the modulator sampling clock is 256 kHz which requires an input filter with a -3 dB corner of 4 kHz. The bandlimit-

ing may be accomplished in an amplifier stage ahead of the CS5320/21 modulator or with the RC input filter at the AIN+ and AINR input pins. The RC filter at the AIN+ and AINR pins is recommended to reduce the "charge kick" that the driving amplifier sees as the switched capacitor sampling is performed.

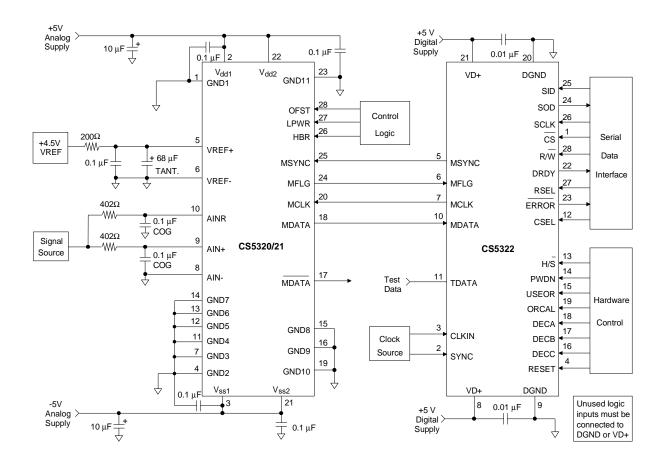

Figure 20 illustrates the CS5320/21 and CS5322 system connections. The input components on AINR and AIN+ should be identical values for optimum performance. In choosing the components the capacitor should be a minimum of 0.1 µF (COG dielectric ceramic preferred). For minimum board space, the RC components on the AINR input can be removed, but this will force the driving amplifier to source the full dynamic charging current of the AINR input. This can increase distortion in the driving amplifier and reduce system performance. In choosing the RC filter components, increasing C and minimizing R is preferred. Increasing C reduces the instantaneous voltage change on the pin, but may require paralleling capacitors to maintain smaller size (the recommended 0.1 µF C0G ceramic capacitor is larger than other similar-valued capacitors with different dielectrics). Larger resistor values will increase the voltage drop across the resistor as the recharging current charges the switched capacitor input.

# 2.2 The OFST Pin

The CS5320/21 modulator can produce "idle tones" which occur in the passband when the input signal is steady state dc signal within about

$\pm 50$  mV of bipolar zero. In the CS5320/21 these tones are about 135 dB down from full scale. The user can force these idle tones "out-of-band" by adding 100 mV of dc offset to the signal at the AIN input. Alternately, if the user circuitry has a low offset voltage such that the input signal is within  $\pm 50$  mV of bipolar zero when no AC signal is present, the OFST pin on the CS5320/21 can be activated. When OFST = 1, +100 mV of input re-

ferred offset will be added internal to the CS5320/21 and guarantee that any idle tones present will lie out-of-band. The user should be certain that when OFST is active (OFST =1) that the offset voltage generated by the user circuitry does not negate the offset added by the OFST pin.

# 2.3 Input Range and Overrange Conditions

The analog input is applied to the AIN+ and AINR pins with the AIN- pin connected to GND. The input is fully differential but for proper operation the AIN- pin must remain at GND potential.

The analog input span is defined by the voltage applied between the VREF+ and VREF- input pins. See the Voltage Reference section of this data sheet for voltage reference requirements. The modulator is a fourth order delta-sigma and is therefore conditionally stable. The modulator may go into an oscillatory condition if the analog input is overranged. Input signals which exceed either plus or minus full scale by more than 5 % can introduce instability in the modulator. If an unstable condition is detected, the modulator will be reduced to a first order system until loop stability is achieved. If this occurs the MFLG pin will transition from a low to a high will result in an error bit being set in the CS5322. The input signal must be reduced to within the full scale range of the converter for at least 32 MCLK cycles for the modulator to recover from this error condition.

Figure 20. System Connection Diagram

## 2.4 Voltage Reference

The CS5320/21 is designed to operate with a voltage reference in the range of 4.0 to 4.5 volts. The voltage reference is applied to the VREF+ pin with the VREF- pin connected to the GND. A 4.5 V reference will result in the best S/N performance but most 4.5 V references require a power supply voltage greater than 5.0 V for operation. A 4.0 V reference can be used for those applications which must operate from only 5.0 V supplies, but will yield a S/N slightly lower (1-2 dB) than when using a 4.5 V reference. The voltage reference should be designed to yield less than  $2 \mu V$  rms of noise in band at the VREF+ pin of the CS5320/21. The CS5322 filter selection will determine the bandwidth over which the voltage reference noise will affect the CS5320/21/22 dynamic range.

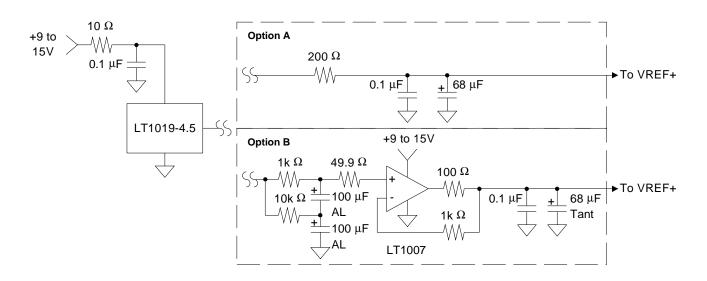

For a 4.5 V reference, the LT1019-4.5 voltage reference yields low enough noise if the output is filtered with a low pass RC filter as shown in Figure 21 Option A. The filter in Figure 21 Option A is acceptable for most spectral measurement applications, but a buffered version with lower source impedance (Figure 21 Option B) may be preferred

for dc-measurement applications. Due to its dynamic (switched-capacitor) input the input impedance of the +VREF pin of the CS5320/21 will change any time MCLK or HBR is changed. Therefore the current required from the voltage reference will change any time MCLK or HBR is changed. This can affect gain accuracy due to the high source impedance of the filter resistor in Figure 20 and Figure 21 Option A. If gain error is to be minimized, especially when MCLK or HBR is changed, the voltage reference should have lower output impedance. The buffer of Figure 21 Option B offers lower output impedance and will exhibit better system gain stability.

## 2.5 Clock Source

For proper operation, the CS5320/21 must be provided with a CMOS-compatible clock on the MCLK pin. The MCLK for the CS5320/21 is usually provided by the CS5322 filter. MCLK is usually 1.024 MHz to set the seven selectable output word rates from the CS5322. The MCLK frequency can be as low as 250 kHz and as high as 1.2 MHz. The choice of clock frequency can affect performance; see the Performance section of the data

Figure 21. 4.5 Voltage Reference with two filter options

sheet. The clock must have less than 300 ps jitter to maintain data sheet performance from the device. The CS5320/21 is equipped with loss of clock detection circuitry which will cause the CS5320/21 to enter a powered-down state if the MCLK is removed or reduced to a very low frequency. The HBR pin on the CS5320/21 modifies the sampling clock rate of the modulator. When HBR = 1, the modulator sampling clock will be at MCLK/4; with HBR = 0 the modulator sampling clock will be at MCLK/8. The chip set will exhibit about 3 dB less S/N performance when the HBR pin is changed from a logic "1" to a logic "0" for the same output word rate from the CS5322.

## 2.6 Low Power Mode

The CS5320/21 includes a low power operating mode (LPWR =1). When operated with LPWR = 1, the CS5320/21 modulator sampling clock must be restricted to rates of 128 kHz or less. Operating in low power mode with modulator sample rates greater than 128 kHz will greatly degrade performance.

# 2.7 Digital Interface and Data Format

The MCLK signal (normally 1.024 MHz) is divided by four, or by eight inside the CS5320/21 to generate the modulator oversampling clock. The HBR pin determines whether the clock divider inside the CS5320/21 divides by four (HBR =1) or by eight (HBR = 0). The modulator outputs a ones density bit stream from its MDATA and MDATA pins proportional to the analog input signal, but at a bit rate determined by the modulator over sampling clock.

For proper synchronization of the bitstream, the CS5320/21 must be furnished with an MSYNC signal prior to data conversion. The MSYNC signal, generated by the CS5322, resets the MCLK counter-divider in the CS5320/21 to the correct phase so that the bitstream can be properly sampled by the CS5322 digital filter.

When operated with the CS5322 digital filter the output codes from the CS5320/21/22 will range from approximately decimal -5,242,880 to +5,242,879 for an input to the CS5320/21 of  $\pm$ 4.5 V. Table 1 illustrates the output coding for various input signal amplitudes. Note that with a signal input defined as a full scale signal (4.5 V with VREF+ = 4.5 V) the CS5320/22 and CS5321/22 chipsets does not output a full scale digital code of 8,388,607 but is scaled to a lower value to allow some overrange capability. Input signals can exceed the defined full scale by up to 5% and still be converted properly.

| Modulator Input | CS5322 Filter<br>Output Code |          |  |  |

|-----------------|------------------------------|----------|--|--|

| Signal          | HEX                          | Decimal  |  |  |

| > (+VREF + 5%)  | Error Flag Possible          |          |  |  |

| ≈ (+VREF + 5%)  | 53FFFF(H)                    | +5505023 |  |  |

| +VREF           | 4FFFFF(H)                    | +5242879 |  |  |

| 0V              | 000000(H)                    | 0        |  |  |

| -VREF           | B00000(H)                    | -5242880 |  |  |

| ≈ - (+VREF +5%) | AC0000(H)                    | -5505024 |  |  |

| > - (+VREF +5%) | Error Flag Possible          |          |  |  |

Table 1. Output Coding for the CS5320/21 andCS5322 Combination

# 2.8 Performance

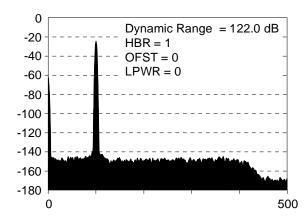

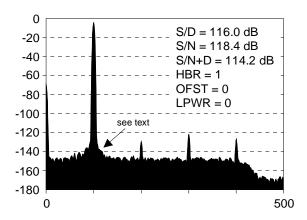

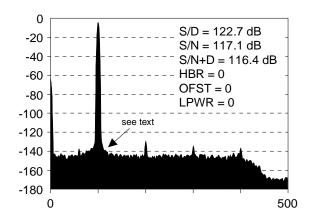

Figure 22, 23 and 24 illustrate the spectral performance of the CS5321/22 and CS5320/22 chipsets when operating from a 1.024 MHz master clock. Ten 1024 point FFTs were averaged to produce the plots.

Figure 22 illustrates the chip set with a 100 Hz, -20 dB input signal. The sample rate was set at 1 kHz. Dynamic range is 122 dB.

The dynamic range calculated by the test soft-ware is reduced somewhat in Figures 23 and 24 because of jitter in the signal test oscillator. Jitter in the 100 Hz signal source is interpreted by the signal processing software to be increased noise.

The choice of master clock frequency will affect performance. The CS5320/21 will exhibit the best Signal/ Distortion performance with slower modulator sampling clock rates as slower sample rates allow more time for amplifier settling.

For lowest offset drift, the CS5320/21 should be operated with MCLK = 1.024 MHz and HBR = 1. Slower modulator sampling clock rates will exhibit more offset drift. Changing MCLK to 512 kHz (HBR = 1) or changing HBR to zero (MCLK =1.024 MHz) will cause the drift rate to double. Offset drift is not linear over temperature so it is difficult to specify an exact drift rate. Offset drift characteristics vary from part to part and will vary as the power supply voltages vary. Therefore, if the CS5320/21 is to be used in precision dc measurement applications where offset drift is to be minimized, the power supplies should be well regulated. The CS5320/21 will exhibit about 6 ppm/°C of offset drift with MCLK = 1 and HBR = 1.