# Geode<sup>™</sup> CS5530A I/O Companion Multi-Function South Bridge

# **General Description**

The CS5530A I/O companion is designed to work in conjunction with a GX-series processor (i.e., GX1, GXLV, GXm); all members of the National Semiconductor<sup>®</sup> Geode<sup>TM</sup> family of products. Together, the Geode processor and CS5530A provide a system-level solution well suited for the high performance needs of a host of devices which include digital set-top boxes and thin client devices. Due to the low power consumption of the GX-series processors, this solution satisfies the needs of battery powered devices such as National's WebPAD<sup>TM</sup> system, and thermal design is eased allowing for fanless system design.

The CS5530A I/O companion is a PCI-to-ISA bridge (South Bridge), ACPI-compliant chipset that provides AT/ISA style functionality. The device contains state-of-the-art power management that enables systems, especially battery powered systems, to significantly reduce power consumption.

Audio is supported through PCI bus master engines which connect to an AC97 compatible codec such as the National Semiconductor LM4548. If industry standard audio is required, a combination of hardware and software called Virtual System Architecture<sup>®</sup> (VSA<sup>™</sup>) technology is provided.

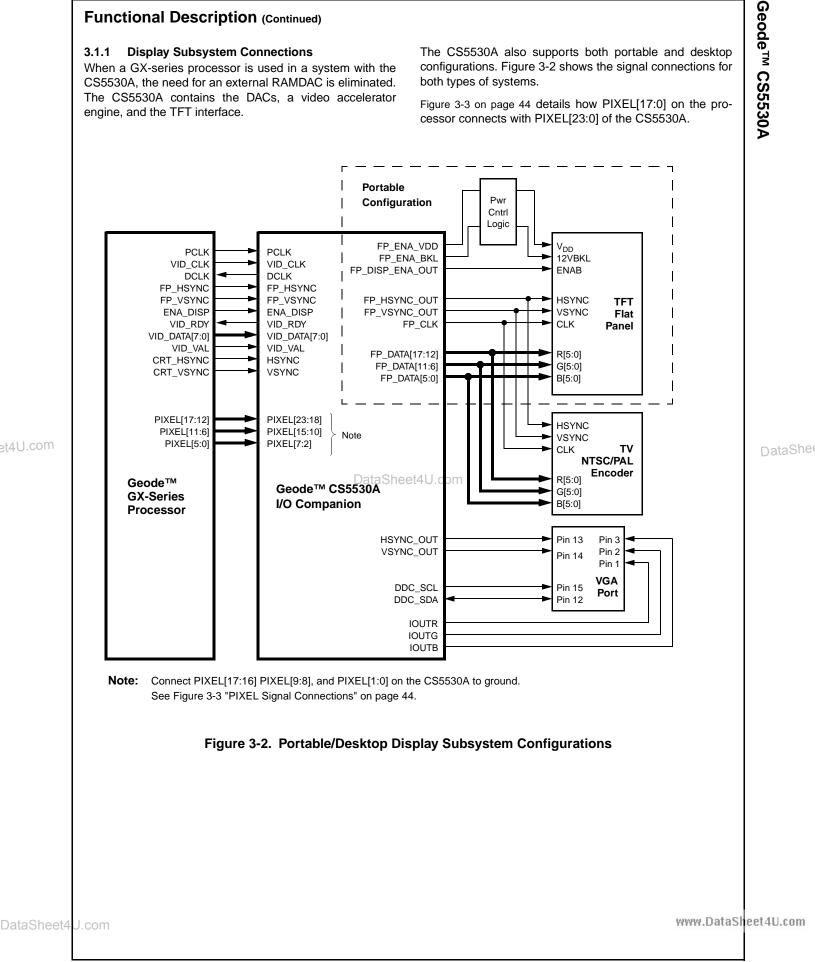

The Geode GX-series processors' graphics/video output is connected to the CS5530A. The CS5530A graphics/video support includes a PLL that generates the DOT clock for the GX-series processors (where the graphics controller is located), video acceleration hardware, gamma RAM plus three DACs for RGB output to CRT, and digital RGB that can be directly connected to TFT panels or NTSC/PAL encoders. The digital RGB output can also be connected to the National Semiconductor Geode CS9211 graphics companion (a flat panel display controller) for DSTN panel support.

Geode<sup>™</sup> CS5530A I/O Companion Multi-Function South Bridge

© 2001 National Semiconductor Corporation

et4U.com

Two bus mastering IDE controllers are included for support of up to four ATA-compliant devices. A two-port Universal Serial Bus (USB) provides high speed, Plug & Play expansion for a variety of consumer peripheral devices such as a keyboard, mouse, printer, and digital camera. If additional functions are required like real-time clock, floppy disk, PS2 keyboard, and PS2 mouse, a SuperI/O such as the National PC97317 can be easily connected to the CS5530A.

## Features

### **General Features**

- Designed for use with National's Geode GX-series processors

- 352 PBGA (Plastic Ball Grid Array) package

- 3.3V or 5.0V PCI bus compatible

- 5.0V tolerant on all inputs

- 3.3V core

### PCI-to-ISA Bridge

- PCI 2.1 compliant

- Supports PCI initiator-to-ISA and ISA master-to-PCI cycle translations

- PCI master for audio I/O and IDE controllers

- Subtractive agent for unclaimed transactions

- PCI-to-ISA interrupt mapper/translator

### **AT Compatibility**

- Two 8259A-equivalent interrupt controllers

- 8254-equivalent timer

- Two 8237-equivalent DMA controllers

- Boot ROM and keyboard chip select

- Extended ROM to 16 MB

### **Bus Mastering IDE Controllers**

- Two controllers with support for up to four IDE devices

- Independent timing for master and slave devices for both channels

- PCI bus master burst reads and writes

- Ultra DMA/33 (ATA-4) support

- Multiword DMA support

- Programmed I/O (PIO) Modes 0-4 support

### **Power Management**

- Intelligent system controller supports multiple power management standards:

- Full ACPI and Legacy (APM) support

- Directly manages all GX-series processors' power states (including automatic Suspend modulation for optimal performance/thermal balancing)

- I/O traps and idle timers for peripheral power management

- Up to eight GPIOs for system control:

All eight are configurable as external wakeup events

- Dedicated inputs for keyboard and mouse wakeup events

### **XpressAUDIO**

- Provides "back-end" hardware support via six buffered PCI bus masters

- AC97 codec interface:

- Specification Revision 1.3, 2.0, and 2.1 compliant interface. Note that the codec (e.g., LM4548) must have SRC (sample rate conversion) support

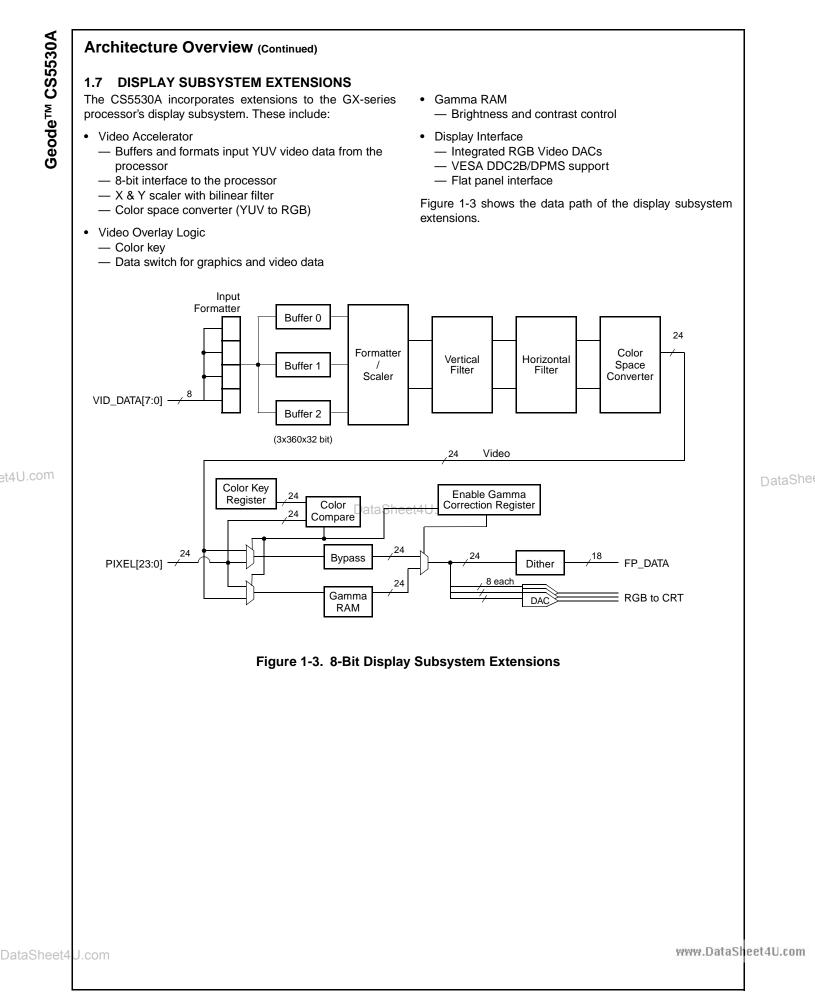

### **Display Subsystem Extensions**

- Complements the GX-series processors' graphics and video capabilities:

- Three independent line buffers for accelerating video data streams

- Handles asynchronous video and graphics data

- DataSheet4U.costreams concurrently from the processor

- YUV to RGB conversion hardware

- Arbitrary X & Y interpolative scaling

- Color keying for graphics/video overlay

- VDACs / Display interface:

- Three integrated DACs

- Gamma RAM:

- Provides gamma correction for graphics data streams

- Provides brightness/contrast correction for video data streams

- Integrated DOT clock generator

- Digital RGB interface drives TFT panels or standard NTSC/PAL encoders

- Up to 1280x1024 @ 85 Hz

### **Universal Serial Bus**

- Two independent USB interfaces:

- Open Host Controller Interface (OpenHCI) specification compliant

- Second generation proven core design

DataSheet4 J.com

www.DataSheet4U.com

|     |       | Table of Contents                                                                                                     |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------|

| 1.0 | Arch  | itecture Overview                                                                                                     |

|     | 1.1   | PCI BUS INTERFACE                                                                                                     |

|     | 1.2   | ISA BUS INTERFACE                                                                                                     |

|     | 1.3   | AT COMPATIBILITY LOGIC                                                                                                |

|     |       | 1.3.1 DMA Controller                                                                                                  |

|     |       | 1.3.2 Programmable Interval Timer                                                                                     |

|     |       | 1.3.3 Programmable Interrupt Controller                                                                               |

|     | 1.4   | IDE CONTROLLERS                                                                                                       |

|     | 1.5   | POWER MANAGEMENT                                                                                                      |

|     |       | 1.5.1 GPIO Interface                                                                                                  |

|     | 1.6   | XPRESSAUDIO                                                                                                           |

|     |       | 1.6.1 AC97 Codec Interface                                                                                            |

|     |       | 1.6.2 VSA Technology Support Hardware                                                                                 |

|     | 1.7   | DISPLAY SUBSYSTEM EXTENSIONS                                                                                          |

|     | 1.8   | CLOCK GENERATION                                                                                                      |

|     | 1.9   | UNIVERSAL SERIAL BUS                                                                                                  |

|     | 1.10  | PROCESSOR SUPPORT                                                                                                     |

|     |       |                                                                                                                       |

| 2.0 | Signa | al Definitions                                                                                                        |

|     | 2.1   | PIN ASSIGNMENTS                                                                                                       |

|     | 2.2   | SIGNAL DESCRIPTIONS                                                                                                   |

|     |       | 2.2.1 Reset Interface                                                                                                 |

|     |       | 2.2.2 Clock Interface                                                                                                 |

|     |       | 2.2.3 CPU Interface DataSheet4U.com                                                                                   |

|     |       | 2.2.4 PCI Interface                                                                                                   |

|     |       | 2.2.5 ISA Bus Interface                                                                                               |

|     |       | 2.2.6 ROM Interface                                                                                                   |

|     |       | 2.2.7         IDE Interface         32           2.2.8         USB Interface         33                               |

|     |       | 2.2.0       USB Intenace         2.2.9       Game Port and General Purpose I/O Interface                              |

|     |       | 2.2.9         Game Fort and General Fulpose //O menace         34           2.2.10         Audio Interface         34 |

|     |       | 2.2.10 Addio menace                                                                                                   |

|     |       | 2.2.12 DCLK PLL                                                                                                       |

|     |       | 2.2.13 Power, Ground, and No Connects                                                                                 |

|     |       | 2.2.14 Internal Test and Measurement                                                                                  |

| 3.0 | Funa  | stional Description 44                                                                                                |

| 3.0 |       |                                                                                                                       |

|     | 3.1   | PROCESSOR INTERFACE                                                                                                   |

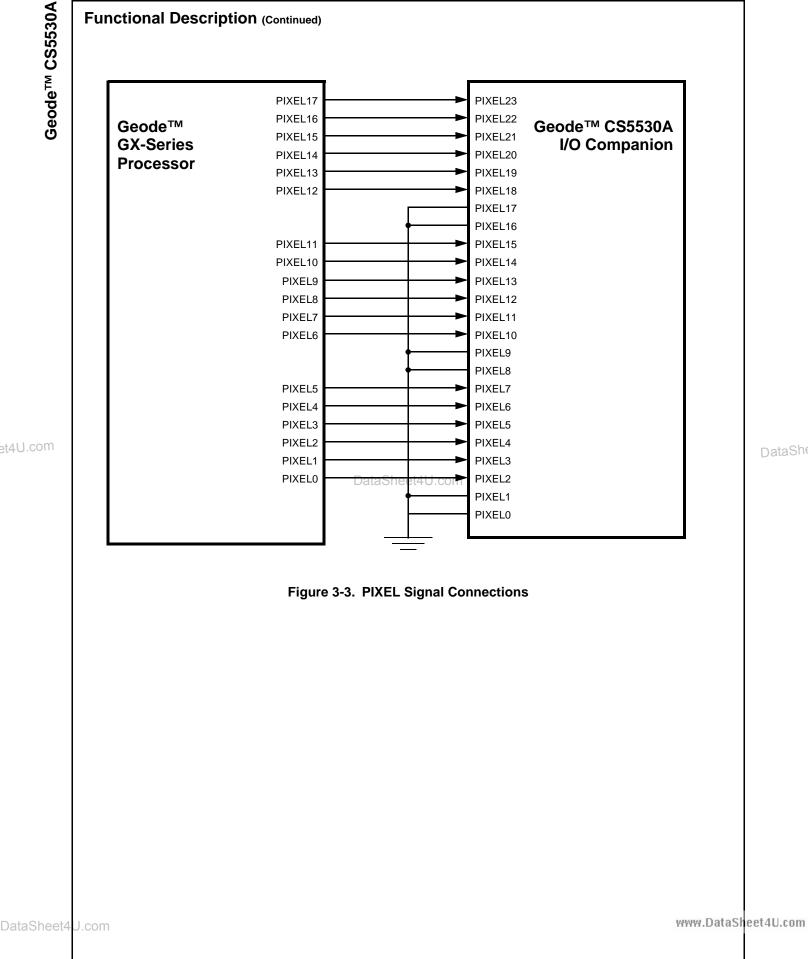

|     |       | 3.1.1       Display Subsystem Connections       43         3.1.2       PSERIAL Pin Interface       45                 |

|     |       | 3.1.2         PSERIAL Pin Interface         45           3.1.2.1         Video Retrace Interrupt         45           |

|     | 3.2   | PCI BUS INTERFACE                                                                                                     |

|     | J.Z   | 3.2.1 PCI Initiator                                                                                                   |

|     |       | 3.2.2 PCI Target                                                                                                      |

|     |       | 3.2.2         PCF raiget         47           3.2.3         Special Bus Cycles–Shutdown/Halt         48               |

|     |       | 3.2.4 PCI Bus Parity                                                                                                  |

|     |       |                                                                                                                       |

|     |       | 3.2.5 PCI Interrupt Routing Support                                                                                   |

om

3

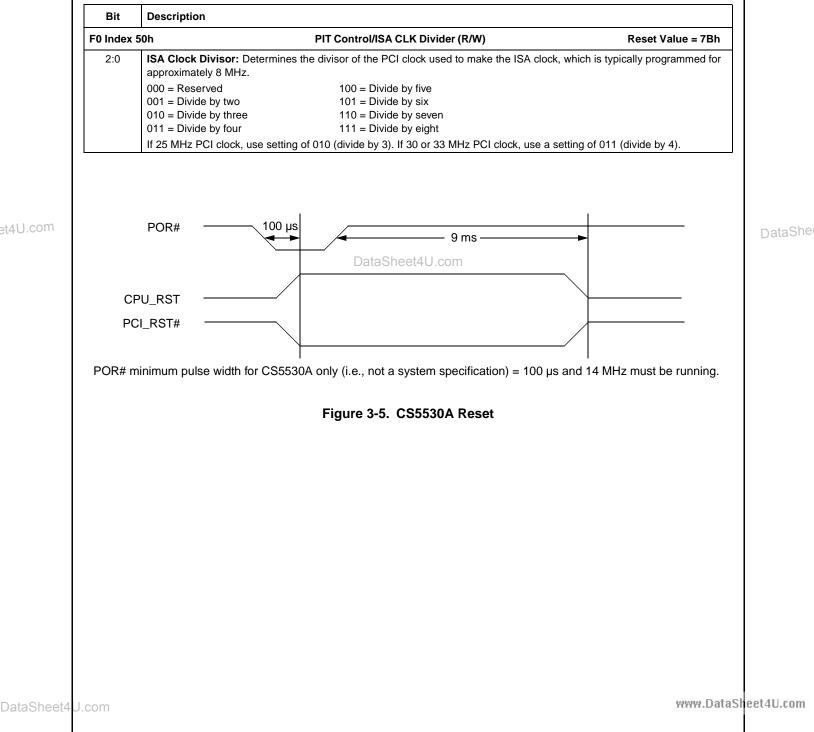

| 3.3 | RESET  | S AND CLOCKS                                                                                            |

|-----|--------|---------------------------------------------------------------------------------------------------------|

|     | 3.3.1  | Resets                                                                                                  |

|     | 3.3.2  | ISA Clock                                                                                               |

|     | 3.3.3  | DOT Clock                                                                                               |

|     | 01010  | 3.3.3.1 DCLK Programming                                                                                |

| 3.4 | POWE   | R MANAGEMENT                                                                                            |

| 0.1 | 3.4.1  | CPU Power Management                                                                                    |

|     | 0.4.1  | 3.4.1.1 On                                                                                              |

|     |        | 3.4.1.2 Active Idle                                                                                     |

|     |        | 3.4.1.3 Suspend                                                                                         |

|     |        | 3.4.1.4 3 Volt Suspend                                                                                  |

|     |        | 3.4.1.5 Off                                                                                             |

|     |        | 3.4.1.6 Suspend Modulation                                                                              |

|     | 240    | 3.4.1.7 Save-to-Disk/Save-to-RAM                                                                        |

|     | 3.4.2  | APM Support                                                                                             |

|     | 3.4.3  | Peripheral Power Management                                                                             |

|     |        | 3.4.3.1       Device Idle Timers and Traps       6         3.4.3.2       General Purpose Timers       7 |

|     |        | 3.4.3.3 ACPI Timer Register                                                                             |

|     |        | 3.4.3.4 General Purpose I/O Pins                                                                        |

|     |        | 3.4.3.5 Power Management SMI Status Reporting Registers                                                 |

|     |        | 3.4.3.6 Device Power Management Register Programming Summary                                            |

| 3.5 | PC/AT  | COMPATIBILITY LOGIC                                                                                     |

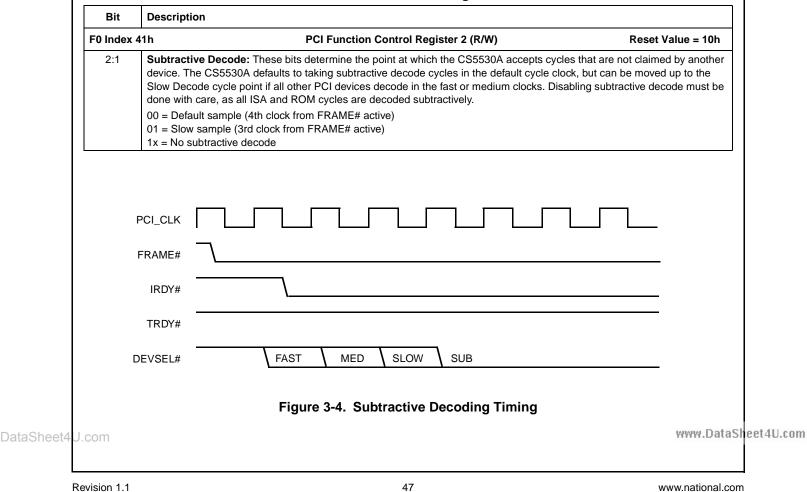

|     | 3.5.1  | ISA Subtractive Decode                                                                                  |

|     | 3.5.2  | ISA Bus Interface                                                                                       |

|     |        | 3.5.2.1 Delayed PCI Transactions                                                                        |

|     |        | 3.5.2.2 Limited ISA and ISA Master Modes                                                                |

|     |        | 3.5.2.3 ISA Bus Data Steering                                                                           |

|     |        | 3.5.2.4 I/O Recovery Delays                                                                             |

|     | 3.5.3  | 3.5.2.5 ISA DMA                                                                                         |

|     | 3.5.4  | Megacells                                                                                               |

|     | 5.5.4  | 3.5.4.1 Direct Memory Access (DMA)                                                                      |

|     |        | 3.5.4.2 Programmable Interval Timer                                                                     |

|     |        | 3.5.4.3 Programmable Interrupt Controller                                                               |

|     |        | 3.5.4.4 PCI Compatible Interrupts10                                                                     |

|     | 3.5.5  | I/O Ports 092h and 061h System Control10                                                                |

|     |        | 3.5.5.1 I/O Port 092h System Control                                                                    |

|     |        | 3.5.5.2 I/O Port 061h System Control                                                                    |

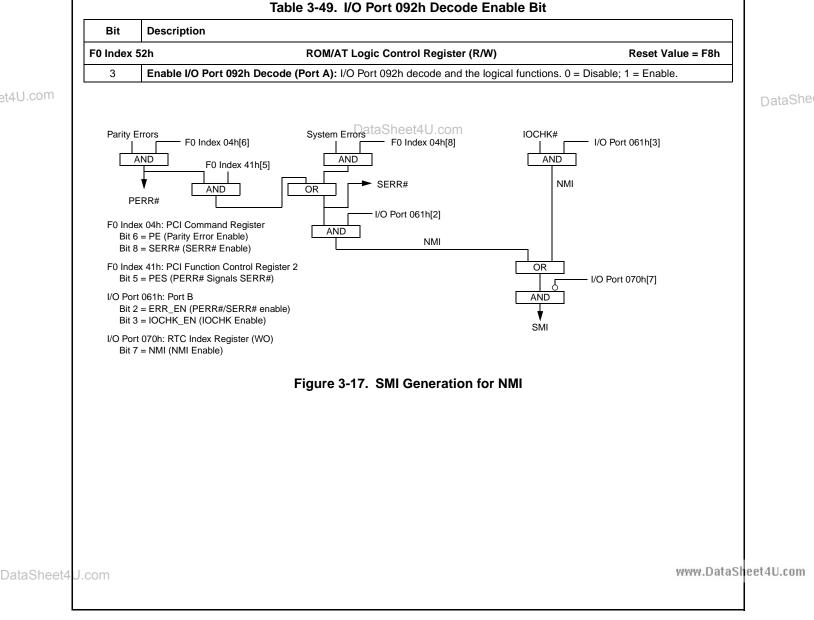

|     |        | 3.5.5.3 SMI Generation for NMI                                                                          |

|     | 3.5.6  | Keyboard Interface Function10                                                                           |

|     |        | 3.5.6.1 Fast Keyboard Gate Address 20 and CPU Reset                                                     |

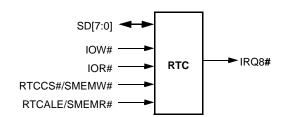

|     | 3.5.7  | External Real-Time Clock Interface10                                                                    |

| 3.6 | IDE CO | NTROLLER                                                                                                |

|     | 3.6.1  | IDE Interface Signals10                                                                                 |

|     | 3.6.2  | IDE Configuration Registers                                                                             |

|     |        | 3.6.2.1 PIO Mode                                                                                        |

|     |        | 3.6.2.2 Bus Master Mode                                                                                 |

|     |        | 3.6.2.3 Ultra DMA/33 Mode11                                                                             |

DataSheet4U.com

www.DataSheet4U.com

4

|     | 3.7 | XPRESSAUDIO                                                                                                  |

|-----|-----|--------------------------------------------------------------------------------------------------------------|

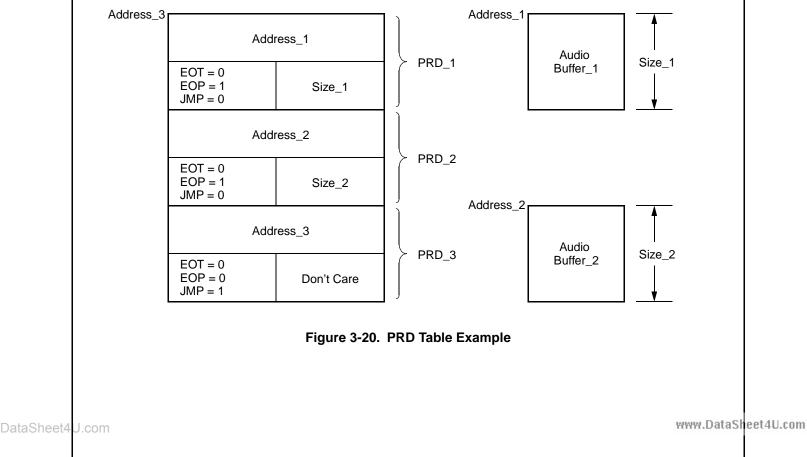

|     |     | 3.7.1 Subsystem Data Transport Hardware116                                                                   |

|     |     | 3.7.1.1 Audio Bus Masters                                                                                    |

|     |     | 3.7.1.2 Physical Region Descriptor Table Address                                                             |

|     |     | 3.7.1.3 Physical Region Descriptor Format                                                                    |

|     |     | 3.7.1.4 Programming Model                                                                                    |

|     |     | 3.7.1.5 AC97 Codec Interface                                                                                 |

|     |     | 3.7.2 VSA Technology Support Hardware                                                                        |

|     |     | 3.7.2.1         VSA Technology         123           3.7.2.2         Audio SMI Related Registers         123 |

|     |     | 3.7.2.2 Addio Sim Related Registers                                                                          |

|     | 3.8 | DISPLAY SUBSYSTEM EXTENSIONS                                                                                 |

|     | 0.0 | 3.8.1 Video Interface Configuration Registers                                                                |

|     |     | 3.8.2         Video Accelerator         132                                                                  |

|     |     | 3.8.2 Video Accelerator                                                                                      |

|     |     | 3.8.2.1 Line Buffers                                                                                         |

|     |     | 3.8.2.3 Video Format                                                                                         |

|     |     | 3.8.2.4 X and Y Scaler / Filter                                                                              |

|     |     | 3.8.2.5 Color-Space-Converter                                                                                |

|     |     | 3.8.3 Video Overlay                                                                                          |

|     |     | 3.8.4 Gamma RAM                                                                                              |

|     |     | 3.8.5 Display Interface                                                                                      |

|     |     | 3.8.5.1 Video DACs                                                                                           |

|     |     | 3.8.5.2 VESA DDC2B / DPMS                                                                                    |

|     |     | 3.8.5.3 Flat Panel Support                                                                                   |

|     | 3.9 | UNIVERSAL SERIAL BUS SUPPORT                                                                                 |

|     |     | 3.9.1 USB PCI Controller . DataSheet4U.com                                                                   |

|     |     | 3.9.2 USB Host Controller                                                                                    |

|     |     | 3.9.3 USB Power Management                                                                                   |

| 4.0 | Reg | ister Descriptions                                                                                           |

|     | 4.1 | PCI CONFIGURATION SPACE AND ACCESS METHODS141                                                                |

|     | 4.2 | REGISTER SUMMARY142                                                                                          |

|     | 4.3 | CHIPSET REGISTER SPACE                                                                                       |

|     | -   | 4.3.1 Bridge Configuration Registers - Function 0                                                            |

|     |     | 4.3.2 SMI Status and ACPI Timer Registers - Function 1                                                       |

|     |     | 4.3.3 IDE Controller Registers - Function 2                                                                  |

|     |     | 4.3.4 XpressAUDIO Registers - Function 3                                                                     |

|     |     | 4.3.5 Video Controller Registers - Function 4                                                                |

|     | A A | 4.5.5 Video Controller Registers - Function 4                                                                |

|     | 4.4 |                                                                                                              |

|     | 4.5 | CS5530A ISA LEGACY I/O REGISTER SPACE                                                                        |

|     | 4.6 | V-ACPI I/O REGISTER SPACE                                                                                    |

|     |     |                                                                                                              |

|     |     |                                                                                                              |

| 5.0   | Electrical Specifications.                                                |

|-------|---------------------------------------------------------------------------|

| •••   | 5.1 ELECTRICAL CONNECTIONS                                                |

|       | 5.1.1 Pull-Up Resistors                                                   |

|       | 5.1.2 Unused Input Pins                                                   |

|       | 5.1.3 NC-Designated Pins                                                  |

|       | 5.1.4 Power/Ground Connections and Decoupling                             |

|       | 5.2 ABSOLUTE MAXIMUM RATINGS                                              |

|       | <ul><li>5.3 OPERATING CONDITIONS</li><li>5.4 DC CHARACTERISTICS</li></ul> |

|       | 5.4 De CHARACTERISTICS                                                    |

|       | 5.5 AC CHARACTERISTICS                                                    |

|       | 5.6 DISPLAY CHARACTERISTICS                                               |

|       |                                                                           |

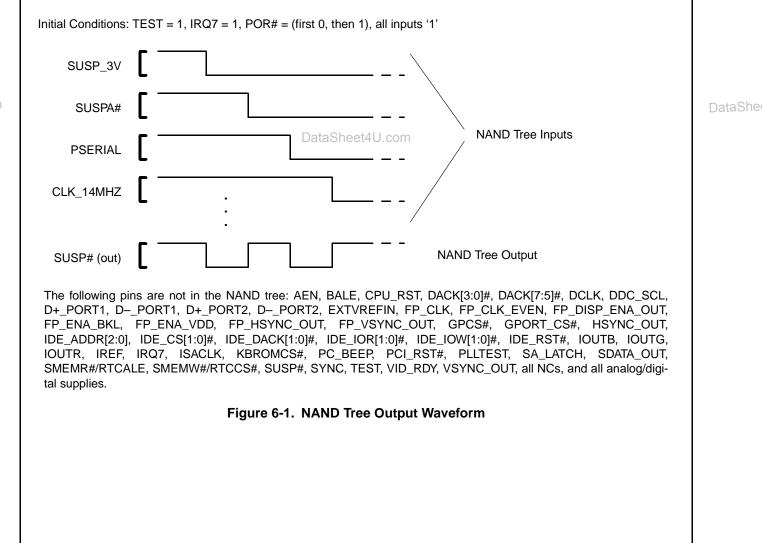

| 6.0   | Test Mode Information                                                     |

|       | 6.1 NAND TREE TEST MODE                                                   |

|       | 6.2 I/O TEST                                                              |

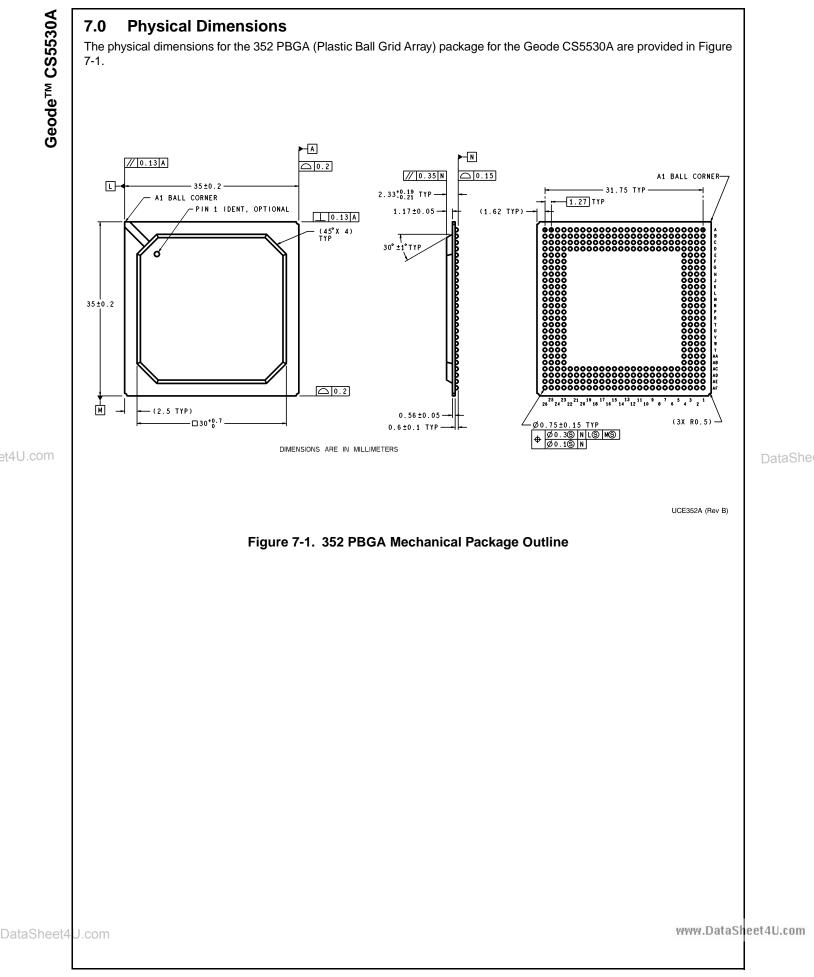

| 7.0   | Physical Dimensions                                                       |

| Ann   | endix A Support Documentation                                             |

| , .PP | A.1 REVISION HISTORY                                                      |

| ••    |                                                                           |

|       |                                                                           |

|       |                                                                           |

|       | DataSheet4U.com                                                           |

www.DataSheet4U.com

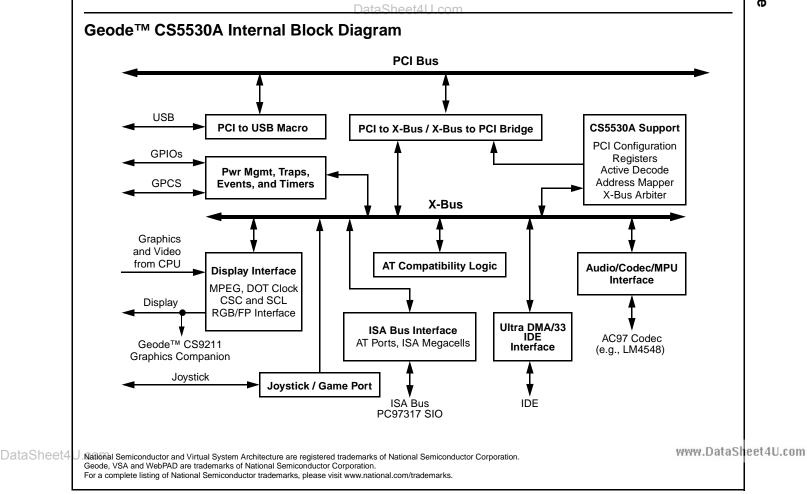

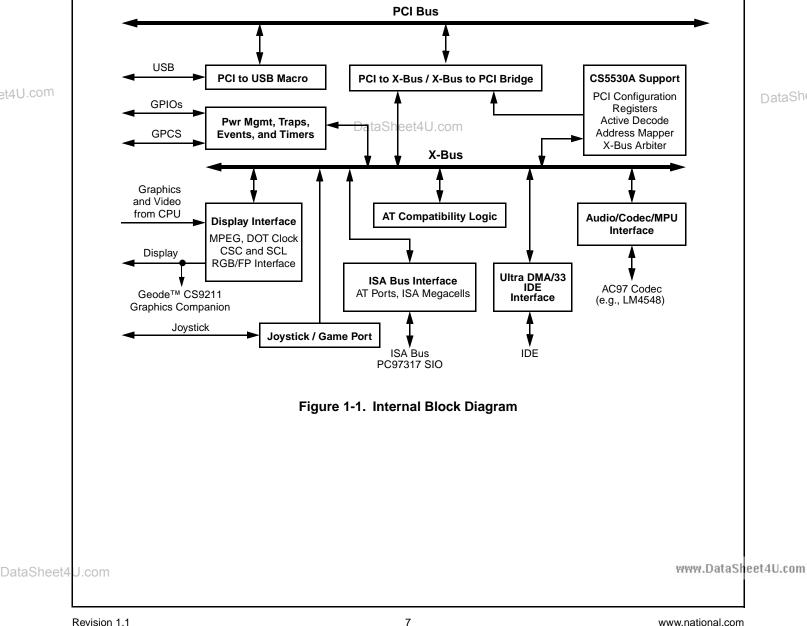

### 1.0 **Architecture Overview**

The Geode CS5530A can be described as providing the functional blocks shown in Figure 1-1.

- PCI bus master/slave interface

- ISA bus interface

- AT compatibility logic

- **IDE** controllers

- Power management

- GPIO interfaces

- Traps, Events, Timers

- Joystick/Game Port interface

- Virtual audio support hardware

- Video display, which includes MPEG accelerator, RAMDAC, and video ports

- USB controller

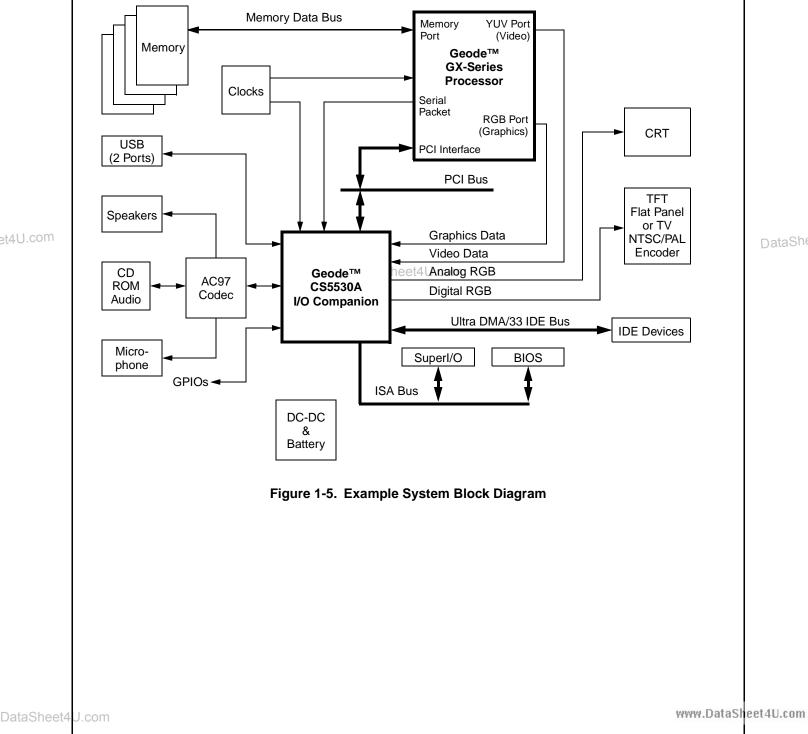

For CPU interface connection refer to Figure 1-5 "Example System Block Diagram" on page 12.

### 1.1 PCI BUS INTERFACE

The CS5530A provides a PCI bus interface that is both a slave for PCI cycles initiated by the CPU or other PCI master devices, and a non-preemptable master for DMA transfer cycles. The chip also is a standard PCI master for the IDE controllers and audio I/O logic. The CS5530A supports positive decode for configurable memory and I/O regions and implements a subtractive decode option for unclaimed PCI accesses. The CS5530A also generates address and data parity and performs parity checking. The CS5530A does not include the PCI bus arbiter, which is located in the processor.

Configuration registers are accessed through the PCI interface using the PCI Bus Type 1 configuration mechanism as described in the PCI 2.1 Specification.

Geode<sup>™</sup> CS5530A

et4U.com

# Architecture Overview (Continued)

# 1.2 ISA BUS INTERFACE

The CS5530A provides an ISA bus interface for unclaimed memory and I/O cycles on PCI. The CS5530A is the default subtractive decoding agent and forwards all unclaimed memory and I/O cycles to the ISA interface; however, the CS5530A may be configured to ignore either I/O, memory, or all unclaimed cycles (subtractive decode disabled).

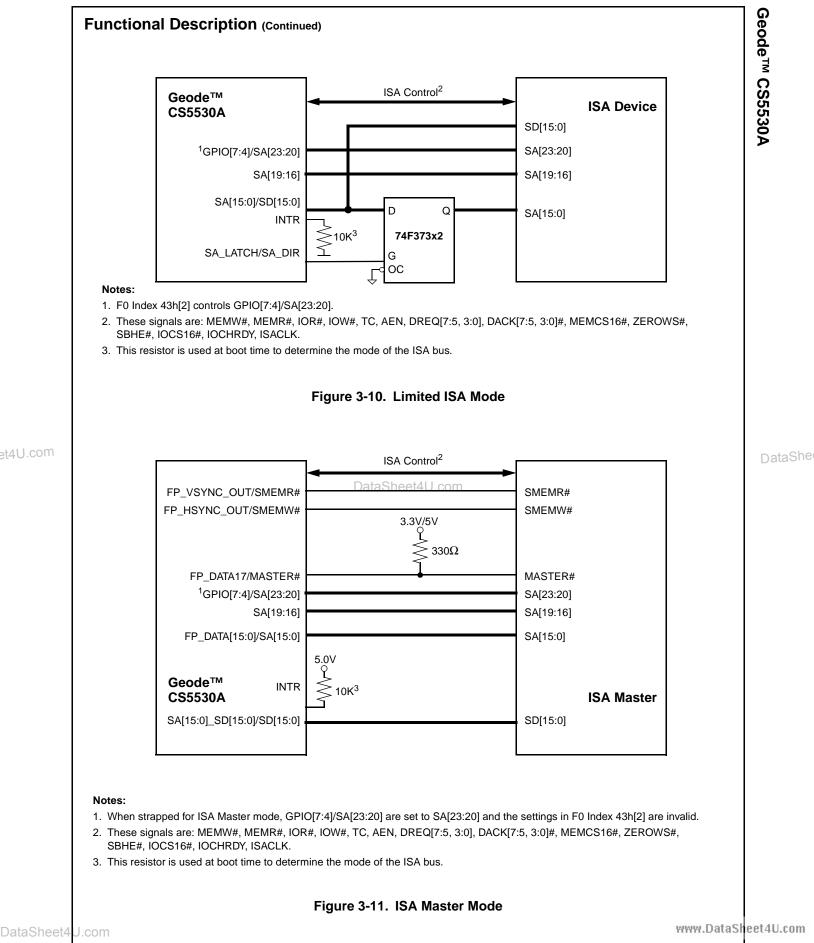

The CS5530A supports two modes on the ISA interface. The default mode, Limited ISA Mode, supports the full memory and I/O address range without ISA mastering. The address and data buses are multiplexed together, requiring an external latch to latch the lower 16 bits of address of the ISA cycle. The signal SA\_LATCH is generated when the data on the SA/SD bus is a valid address. Additionally, the upper four address bits, SA[23:20], are multiplexed on GPIO[7:4].

The second mode, ISA Master Mode, supports ISA bus masters and requires no external circuitry. When the CS5530A is placed in ISA Master Mode, a large number of pins are redefined. In this mode, the CS5530A cannot support TFT flat panels or TV controllers since most of the signals used to support these functions have been redefined. This mode is required if ISA slots or ISA masters are used. ISA master cycles are only passed to the PCI bus if they access memory. I/O accesses are left to complete on the ISA bus.

For further information regarding mode selection and operational details refer to Section 3.5.2.2 "Limited ISA and ISA Master Modes" on page 90.

# 1.3 AT COMPATIBILITY LOGIC

The CS5530A integrates:

- Two 8237-equivalent DMA controllers with full 32-bit addressing

- Two 8259-equivalent interrupt controllers providing 13 individually programmable external interrupts

- An 8254-equivalent timer for refresh, timer, and speaker logic

- NMI control and generation for PCI system errors and all parity errors

- Support for standard AT keyboard controllers

- Positive decode for the AT I/O register space

- Reset control

# 1.3.1 DMA Controller

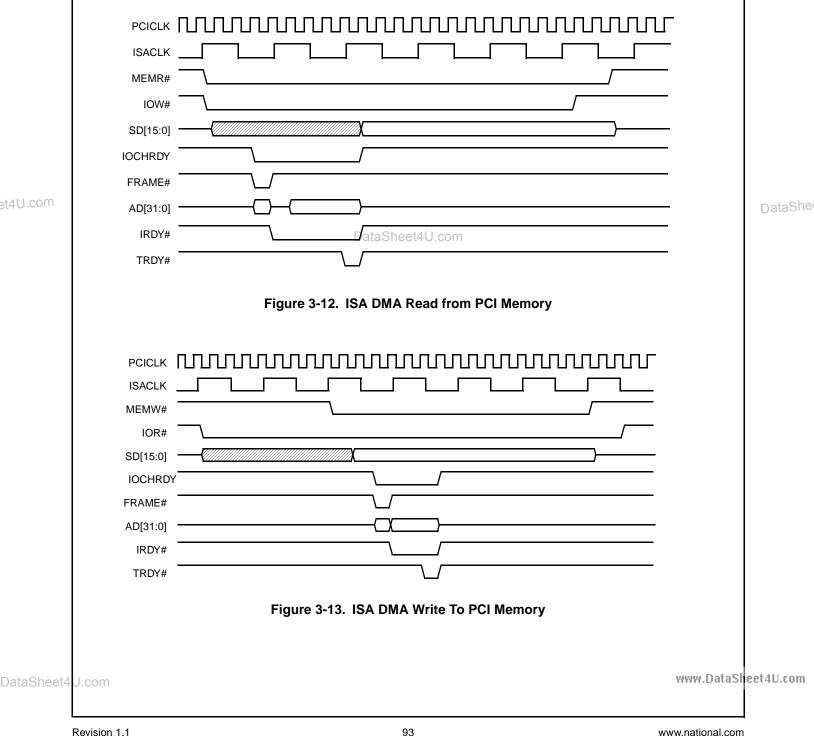

The CS5530A supports the industry standard DMA architecture using two 8237-compatible DMA controllers in cascaded configuration. CS5530A-supported DMA functions include:

- Standard seven-channel DMA support

- 32-bit address range support via high page registers

- IOCHRDY extended cycles for compatible timing transfers

- ISA bus master device support using cascade mode

### 1.3.2 Programmable Interval Timer

The CS5530A contains an 8254-equivalent programmable interval timer. This device has three timers, each with an input frequency of 1.193 MHz.

### 1.3.3 Programmable Interrupt Controller

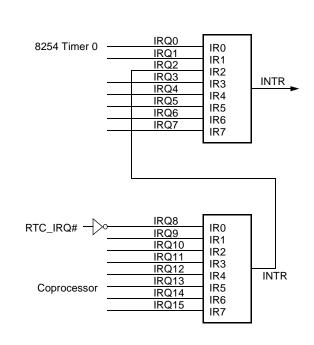

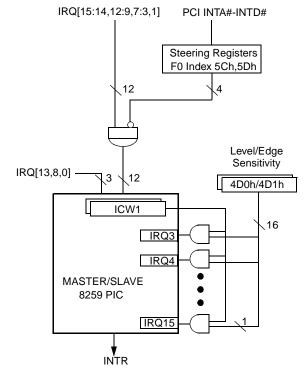

The CS5530A contains two 8259-equivalent programmable interrupt controllers (PICs), with eight interrupt request lines each, for a total of 16 interrupts. The two controllers are cascaded internally, and two of the interrupt request inputs are connected to the internal circuitry. This allows a total of 13 externally available interrupt requests.

Each CS5530A IRQ signal can be individually selected as edge- or level-sensitive. The PCI interrupt signals are routed internally to the PICs IRQs.

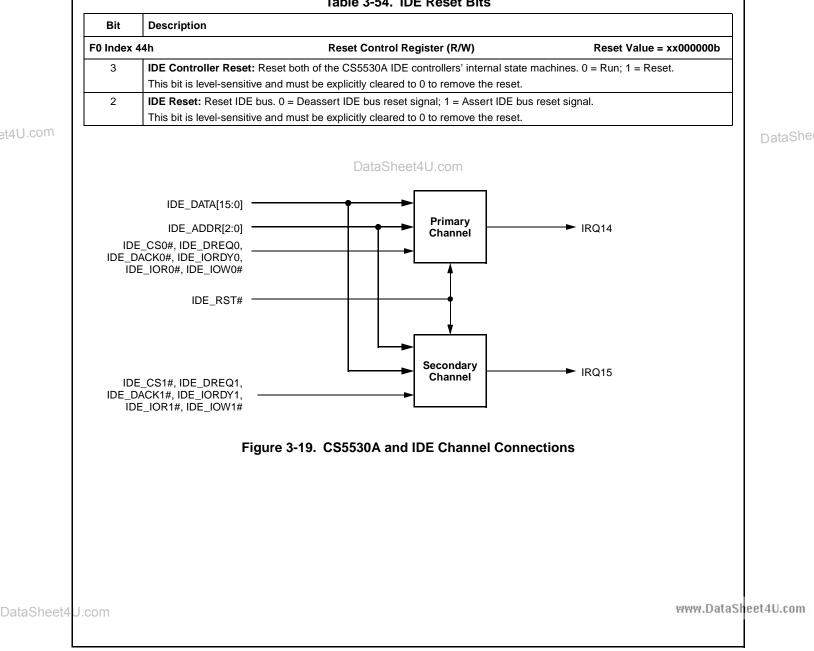

# 1.4 IDE CONTROLLERS

The CS5530A integrates two PCI bus mastering, ATA-4 compatible IDE controllers. These controllers support Ultra DMA/33 (enabled in Microsoft Windows 95 and Windows NT by using a driver provided by National Semiconductor), Multiword DMA, and Programmed I/O (PIO) modes. Two devices are supported on each controller. The data-transfer speed for each device on each controller can be independently programmed. This allows high-speed IDE peripherals to coexist on the same channel as lower speed devices. Faster devices must be ATA-4 compatible.

DataShe

DataSheet4J.com

### Architecture Overview (Continued)

### 1.5 POWER MANAGEMENT

The CS5530A integrates advanced power management features including:

- · Idle timers for common system peripherals

- Address trap registers for programmable address ranges for I/O or memory accesses

- Up to eight programmable GPIOs

- Clock throttling with automatic speedup for the CPU clock

- Software CPU stop clock

- Save-to-Disk/RAM with peripheral shadow registers

- Dedicated serial bus to/from the GX-series processor providing CPU power management status

The CS5530A is an ACPI (Advanced Control and Power Interface) compliant chipset. An ACPI compliant system is one whose underlying BIOS, device drivers, chipset and peripherals conform to revision 1.0 or newer of the ACPI specification. The "Fixed Feature" and "General Purpose" registers are virtual. They are emulated by the SMI handling code rather than existing in physical hardware. To the ACPI compliant operating system, the SMI-base virtualization is transparent; however, to eliminate unnecessary latencies, the ACPI timer exists in physical hardware.

The CS5530A V-ACPI (Virtual ACPI) solution provides the bus mas following support: DataSheet4U.com

- CPU States C1, C2

- Sleep States S1, S2, S4, S4BIOS, S5

- Embedded Controller (Optional) SCI and SWI event inputs.

- General Purpose Events Fully programmable GPE0 Event Block registers.

### 1.5.1 GPIO Interface

Eight GPIO pins are provided for general usage in the system. GPIO[3:0] are dedicated pins and can be configured as inputs or outputs. GPIO[7:4] can be configured as the upper addresses of the ISA bus, SA[23:20]. All GPIOs can also be configured to generate an SMI on input edge transitions.

### 1.6 XPRESSAUDIO

XpressAUDIO in the CS5530A offers a combined hardware/software support solution to meet industry standard audio requirements. XpressAUDIO uses VSA technology along with additional hardware features to provide the necessary support for industry standard 16-bit stereo synthesis and OPL3 emulation.

The hardware portion of the XpressAUDIO subsystem can broadly be divided into two categories. Hardware for:

- Transporting streaming audio data to/from the system memory and an AC97 codec.

- VSA technology support.

### 1.6.1 AC97 Codec Interface

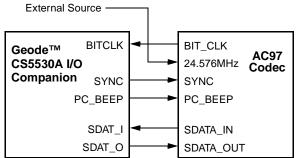

The CS5530A provides an AC97 Specification Revision 1.3, 2.0, and 2.1 compatible interface. Any AC97 codec which supports an independent input and output sample rate conversion interface (e.g., National Semiconductor LM4548) can be used with the CS5530A. This type of codec allows for a design which meets the requirements for PC97 and PC98-compliant audio as defined by Microsoft Corporation. Figure 1-2 shows the codec and CS5530A signal connections. For specifics on the serial interface, refer to the appropriate codec manufacturer's data sheet.

Low latency audio I/O is accomplished by a buffered PCI bus mastering controller.

DataShe

External Source BITCLK Geode™ CS5530A SYNC PC\_BEEP SDAT\_I BIT\_CLK 24.576 MHz SYNC PC\_BEEP Codec SDAT\_I

### Figure 1-2. AC97 Codec Signal Connections

SDATA\_OUT

### 1.6.2 VSA Technology Support Hardware

SDAT\_O

The CS5530A I/O companion incorporates the required hardware in order to support VSA technology for the capture and playback of audio using an external codec. This eliminates much of the hardware traditionally associated with industry standard audio functions.

XpressAUDIO software provides 16-bit compatible sound. This software is available to OEMs for incorporation into the system BIOS ROM.

et4U.com

### Architecture Overview (Continued)

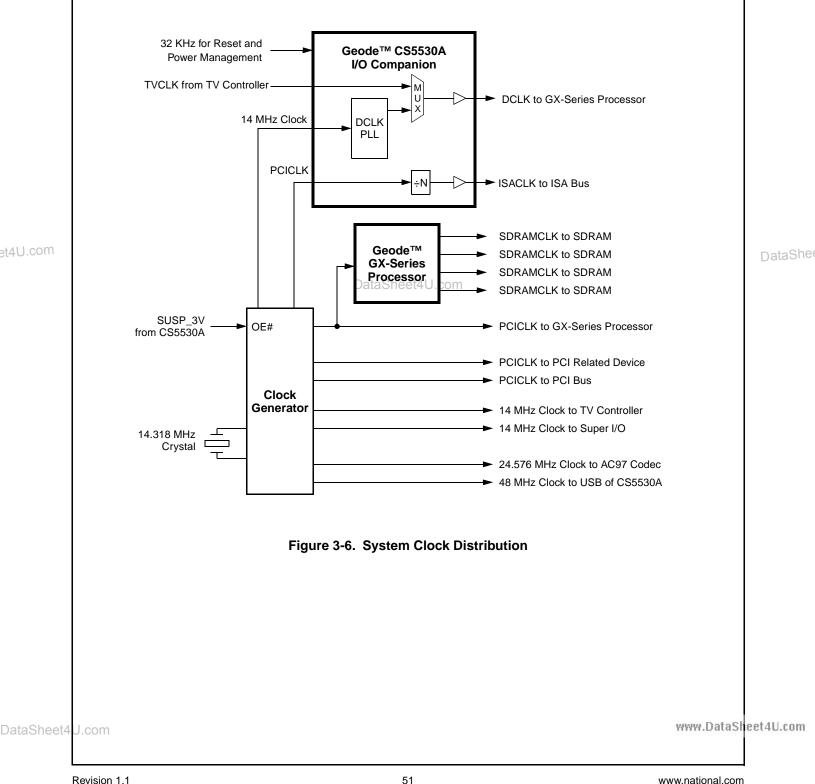

### 1.8 CLOCK GENERATION

In a CS5530A/GX-series processor based system, the CS5530A generates only the video DOT clock (DCLK) for the CPU and the ISA clock. All other clocks are generated by an external clock chip.

The ISACLK is created by dividing the PCICLK. For ISA compatibility, the ISACLK nominally runs at 8.33 MHz or less. The ISACLK dividers are programmed via F0 Index 50h[2:0].

DCLK is generated from the 14.31818 MHz input (CLK\_14MHZ). A combination of a phase locked loop (PLL), linear feedback shift register (LFSR) and divisors are used to generate the desired frequencies for the DCLK. The divisors and LFSR are configurable through the F4BAR+Memory Offset 24h. For applications that do not use the GX-series processor's graphics subsystem, this is an available clock for general purpose use.

Figure 1-4 shows a block diagram for clock generation within the CS5530A.

### 1.9 UNIVERSAL SERIAL BUS

The CS5530A provides two complete, independent USB ports. Each port has a Data "--" and a Data "+" pin.

The USB controller is a compliant Open Host Controller Interface (OpenHCI). The OpenHCI specification provides a register-level description for a host controller, as well as a common industry hardware/software interface and drivers (see OpenHCI Specification, Revision 1.0, for description).

DataSheet4U.com

et4U.com

DataShe

Geode<sup>™</sup> CS5530A

et4U.com

### Architecture Overview (Continued)

### 1.10 PROCESSOR SUPPORT

The traditional south bridge functionality included in the CS5530A I/O companion chip has been designed to support the GX-series of processors. When combined with a GX-series processor, the CS5530A provides a bridge which supports a standard ISA bus and system ROM. As part of the video subsystem, the CS5530A provides MPEG video acceleration and a digital RGB interface, to allow direct connection to TFT LCD panels. This chip also inte-

grates a gamma RAM and three DACs, allowing for direct connection of a CRT monitor. Figure 1-5 shows a typical system block diagram.

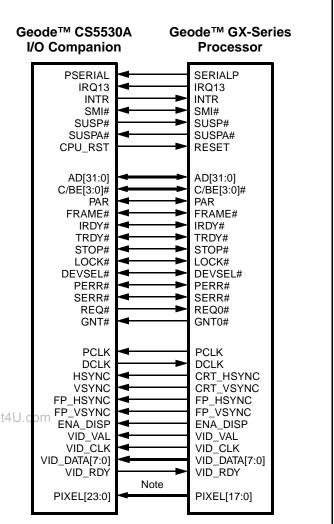

For detailed information regarding processor signal connections refer to Section 3.1 "Processor Interface" on page 42.

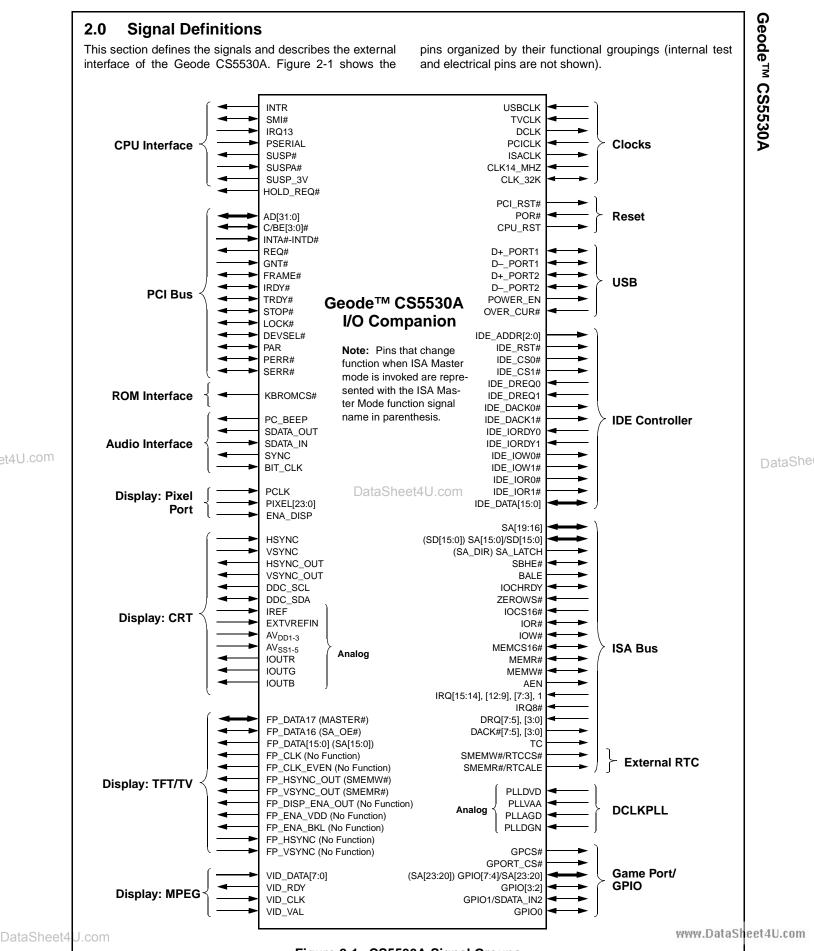

# Figure 2-1. CS5530A Signal Groups

### 2.1 PIN ASSIGNMENTS

The tables in this section use several common abbreviations. Table 2-1 lists the mnemonics and their meanings.

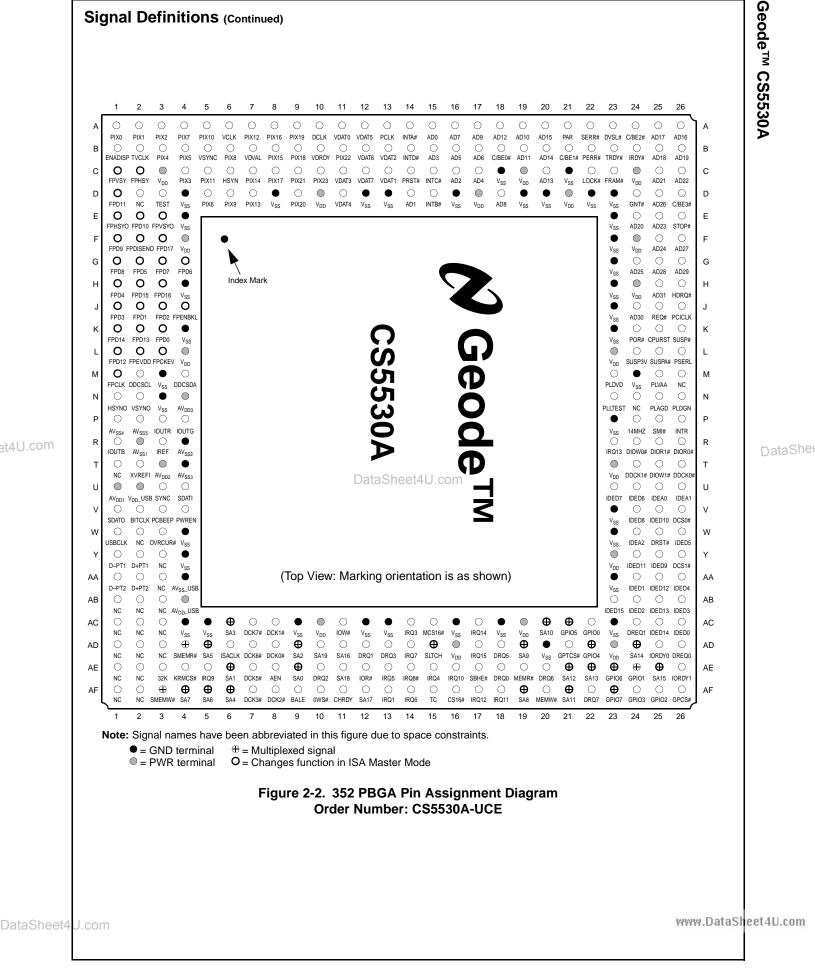

Figure 2-2 shows the pin assignment for the CS5530A with Tables 2-2 and 2-3 listing the pin assignments sorted by pin number and alphabetically by signal name, respectively.

In Section 2.2 "Signal Descriptions" on page 23 a description of each signal within its associated functional group is provided.

In the signal definitions, references to F0-F4, F1BAR, F2BAR, F3BAR, F4BAR, and PCIUSB are made. These terms relate to designated register spaces. Refer to Table 4-1 "PCI Configuration Address Register (0CF8h)" on page 141 for details regarding these register spaces and their access mechanisms.

| Mnemonic              | Definition                                                                                                                                                                                                                                                        |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I                     | Input pin <sup>1</sup>                                                                                                                                                                                                                                            |

| I/O                   | Bidirectional pin <sup>1,2</sup>                                                                                                                                                                                                                                  |

| 0                     | Output pin <sup>1, 2</sup>                                                                                                                                                                                                                                        |

| OD                    | Open-drain output structure that<br>allows multiple devices to share the<br>pin in a wired-OR configuration                                                                                                                                                       |

| PU                    | Pull-up resistor                                                                                                                                                                                                                                                  |

| SMT                   | Schmitt Trigger                                                                                                                                                                                                                                                   |

| V <sub>DD</sub> (PWR) | Power pin                                                                                                                                                                                                                                                         |

| V <sub>SS</sub> (GND) | Ground pin                                                                                                                                                                                                                                                        |

| #                     | The "#" symbol at the end of a signal<br>name indicates that the active, or<br>asserted state occurs when the signal<br>is at a low voltage level. When "#" is<br>not present after the signal name, the<br>signal is asserted when at a high volt-<br>age level. |

Table 2-1. Pin Type Definitions

1. All buffers are 5 volt tolerant.

2. All digital bidirectional and output pins can be TRI-STATE signals unless a weak pull-up is enabled.

DataSheet4U.com

Geode<sup>TM</sup> CS5530A

et4U.com

DataShe

DataSheet4 J.com

Geode<sup>TM</sup> CS5530A

### Table 2-2. 352 PBGA Pin Assignments - Sorted by Pin Number \_

| Ŭ<br>⊻     |            | Signal Name         |                    |

|------------|------------|---------------------|--------------------|

| Geode™ (   | Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |

| Ge         | A1         | PIXEL0              |                    |

| •          | A2         | PIXEL1              |                    |

|            | A3         | PIXEL2              |                    |

|            | A4         | PIXEL7              |                    |

|            | A5         | PIXEL10             |                    |

|            | A6         | VID_CLK             |                    |

|            | A7         | PIXEL12             |                    |

|            | A8         | PIXEL16             |                    |

|            | A9         | PIXEL19             |                    |

|            | A10        |                     |                    |

|            | A11        | VID_DATA0           |                    |

|            | A12        |                     |                    |

|            | A13        |                     |                    |

|            | A14        |                     |                    |

|            | A15        | AD0                 |                    |

|            | A16        |                     |                    |

|            | A17        | AD9                 |                    |

|            | A18        | AD12                |                    |

|            | A19        | AD10                |                    |

|            | A20        | AD15                |                    |

| et4U.com   | A21        | PAR                 |                    |

|            | A22        |                     |                    |

|            | A23        |                     |                    |

|            | A24        | C/BE2#              |                    |

|            | A25        | AD17                |                    |

|            | A26        | AD16                |                    |

|            | B1         | ENA_DISP            |                    |

|            | B2         | TVCLK               |                    |

|            | B3         | PIXEL4              |                    |

|            | B4         | PIXEL5              |                    |

|            | B5         | VSYNC               |                    |

|            | B6         | PIXEL8              |                    |

|            | B7         | VID_VAL<br>PIXEL15  |                    |

|            | B8<br>B9   | PIXEL15<br>PIXEL18  |                    |

|            | B9<br>B10  | VID_RDY             |                    |

|            | B10        | PIXEL22             |                    |

|            | B11<br>B12 | VID_DATA6           |                    |

|            | B12<br>B13 | VID_DATA8           |                    |

|            | B13<br>B14 | INTD#               |                    |

|            | B14<br>B15 | AD3                 |                    |

|            | B15<br>B16 | AD5                 |                    |

|            | B10        | AD5<br>AD6          |                    |

|            | B17<br>B18 | C/BE0#              |                    |

|            | B10        | AD11                |                    |

|            | B19<br>B20 | AD14                |                    |

|            | B20        | C/BE1#              |                    |

|            | B21        | PERR#               |                    |

|            | B23        | TRDY#               |                    |

|            | B24        | IRDY#               |                    |

| DataSheet4 | U.COB25    | AD18                |                    |

|            |            | -                   |                    |

|            | Signal Name             |                    |  |

|------------|-------------------------|--------------------|--|

| Pin<br>No. | Limited<br>ISA Mode     | ISA Master<br>Mode |  |

| B26        | AD19                    | 4                  |  |

| C1         | FP_VSYNC                | No Function        |  |

| C2         | FP_HSYNC                | No Function        |  |

| C3         | V <sub>DD</sub>         | -1                 |  |

| C4         | PIXEL3                  |                    |  |

| C5         | PIXEL11                 |                    |  |

| C6         | HSYNC                   |                    |  |

| C7         | PIXEL14                 |                    |  |

| C8         | PIXEL17                 |                    |  |

| C9         | PIXEL21                 |                    |  |

| C10        | PIXEL23                 |                    |  |

| C11        | VID DATA3               |                    |  |

| C12        | VID_DATA7               |                    |  |

| C13        | VID DATA1               |                    |  |

| C14        | PCI_RST#                |                    |  |

| C15        | INTC#                   |                    |  |

| C16        | AD2                     |                    |  |

| C17        | AD4                     |                    |  |

| C18        | V <sub>SS</sub>         |                    |  |

| C19        | V <sub>DD</sub>         |                    |  |

| C19        | AD13                    |                    |  |

| C20        | V <sub>SS</sub>         |                    |  |

| C21        | LOCK#aSheet4U           | Lcom               |  |

| C22        | FRAME#                  |                    |  |

| C23        |                         |                    |  |

| C24        | V <sub>DD</sub><br>AD21 |                    |  |

| C25        | AD21<br>AD22            |                    |  |

| D1         | FP DATA11               | SA11               |  |

| D1<br>D2   | NC                      | SATT               |  |

| D2<br>D3   | TEST                    |                    |  |

| -          |                         |                    |  |

| D4         | V <sub>SS</sub>         |                    |  |

| D5         | PIXEL6                  |                    |  |

| D6         | PIXEL9                  |                    |  |

| D7         | PIXEL13                 |                    |  |

| D8         |                         |                    |  |

| D9         | PIXEL20                 |                    |  |

| D10        | V <sub>DD</sub>         |                    |  |

| D11        | VID_DATA4               |                    |  |

| D12        | V <sub>SS</sub>         |                    |  |

| D13        | V <sub>SS</sub>         |                    |  |

| D14        | AD1                     |                    |  |

| D15        | INTB#                   |                    |  |

| D16        | V <sub>SS</sub>         |                    |  |

| D17        | V <sub>DD</sub>         |                    |  |

| D18        | AD8                     |                    |  |

| D19        | V <sub>SS</sub>         |                    |  |

| D20        | V <sub>SS</sub>         |                    |  |

| D21        | V <sub>DD</sub>         |                    |  |

| D22        | V <sub>SS</sub>         |                    |  |

| D23        | V <sub>SS</sub>         |                    |  |

| D24        | GNT#                    |                    |  |

|            | Signal Na           | ime                |                |

|------------|---------------------|--------------------|----------------|

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |                |

| D25        | AD26                |                    |                |

| D26        | C/BE3#              |                    |                |

| E1         | FP_HSYNC_OUT        | SMEMW#             |                |

| E2         | FP_DATA10           | SA10               |                |

| E3         | FP_VSYNC_OUT        | SMEMR#             |                |

| E4         | V <sub>SS</sub>     |                    |                |

| E23        | V <sub>SS</sub>     |                    |                |

| E24        | AD20                |                    |                |

| E25        | AD23                |                    |                |

| E26        | STOP#               |                    |                |

| F1         | FP_DATA9            | SA9                |                |

| F2         | FP_DISP_ENA_OUT     | No Function        |                |

| F3         | FP_DATA17           | MASTER#            |                |

| F4         | V <sub>DD</sub>     |                    |                |

| F23        | V <sub>SS</sub>     |                    |                |

| F24        | V <sub>DD</sub>     |                    |                |

| F25        | AD24                |                    |                |

| F26        | AD27                |                    |                |

| G1         | FP_DATA8            | SA8                |                |

| G2         | FP_DATA5            | SA5                |                |

| G3         | FP_DATA7            | SA7                | DataShe        |

| G4         | FP_DATA6            | SA6                |                |

| G23        | V <sub>SS</sub>     |                    |                |

| G24        | AD25                |                    | ]              |

| G25        | AD28                |                    |                |

| G26        | AD29                |                    |                |

| H1         | FP_DATA4            | SA4                | ]              |

| H2         | FP_DATA15           | SA15               |                |

| H3         | FP_DATA16           | SA_OE#             |                |

| H4         | V <sub>SS</sub>     |                    |                |

| H23        | V <sub>SS</sub>     |                    |                |

| H24        | V <sub>DD</sub>     |                    |                |

| H25        | AD31                |                    |                |

| H26        | HOLD_REQ#           | -                  |                |

| J1         | FP_DATA3            | SA3                |                |

| J2         | FP_DATA1            | SA1                |                |

| J3         | FP_DATA2            | SA2                |                |

| J4         | FP_ENA_BKL          | No Function        |                |

| J23        | V <sub>SS</sub>     |                    |                |

| J24        | AD30                |                    |                |

| J25        | REQ#                |                    |                |

| J26        | PCICLK              |                    |                |

| K1         | FP_DATA14           | SA14               |                |

| K2         | FP_DATA13           | SA13               | 11             |

| K3         |                     | SA0                | 11             |

| K4         | V <sub>SS</sub>     |                    |                |

| K23        | V <sub>SS</sub>     |                    |                |

| K24        | POR#                |                    |                |

| K25        | CPU_RST             |                    |                |

| K26        | SUSP#               | Dat.               | Choot All some |

| L1         | FP_DATA12           | SA12               | Sheet4U.com    |

### DataShe

www.national.com

| <b>Geode</b> <sup>1</sup> |

|---------------------------|

| SSD M                     |

| 530A                      |

## Table 2-2. 352 PBGA Pin Assignments - Sorted by Pin Number (Continued)

|       | Signal Name              |             |  |  |

|-------|--------------------------|-------------|--|--|

| Pin   | Limited                  | ISA Master  |  |  |

| No.   | ISA Mode                 | Mode        |  |  |

| L2    | FP_ENA_VDD               | No Function |  |  |

| L3    | FP_CLK_EVEN              | No Function |  |  |

| L4    | V <sub>DD</sub>          |             |  |  |

| L23   | V <sub>DD</sub>          |             |  |  |

| L24   | SUSP_3V                  |             |  |  |

| L25   | SUSPA#                   |             |  |  |

| L26   | PSERIAL                  |             |  |  |

| M1    | FP_CLK                   | No Function |  |  |

| M2    | DDC_SCL                  |             |  |  |

| М3    | V <sub>SS</sub>          |             |  |  |

| M4    |                          |             |  |  |

| M23   | PLLDVD                   |             |  |  |

| M24   | V <sub>SS</sub>          |             |  |  |

| M25   | PLLVAA                   |             |  |  |

| M26   |                          |             |  |  |

| N1    | HSYNC_OUT                |             |  |  |

| N2    | VSYNC_OUT                |             |  |  |

| N3    | V <sub>SS</sub>          |             |  |  |

| N4    |                          |             |  |  |

| N23   | PLLTEST                  |             |  |  |

| N24   |                          |             |  |  |

| N25   | PLLAGD                   |             |  |  |

| N26   |                          |             |  |  |

| P1    |                          |             |  |  |

| P2    | AV <sub>SS4</sub> (ICAP) |             |  |  |

|       | AV <sub>SS5</sub> (DAC)  |             |  |  |

| P3    | IOUTR                    |             |  |  |

| P4    | IOUTG                    |             |  |  |

| P23   | V <sub>SS</sub>          |             |  |  |

| P24   | CLK_14MHZ                |             |  |  |

| P25   | SMI#                     |             |  |  |

| P26   | INTR                     |             |  |  |

| R1    | IOUTB                    |             |  |  |

| R2    | AV <sub>SS1</sub> (DAC)  |             |  |  |

| R3    | IREF                     |             |  |  |

| R4    | 002 ( )                  |             |  |  |

| R23   | IRQ13                    |             |  |  |

| R24   | IDE_IOW0#                |             |  |  |

| R25   | IDE_IOR1#                |             |  |  |

| R26   | IDE_IOR0#                |             |  |  |

| T1    | NC                       |             |  |  |

| T2    | EXTVREFIN                |             |  |  |

| Т3    | AV <sub>DD2</sub> (VREF) |             |  |  |

| T4    | AV <sub>SS3</sub> (VREF) |             |  |  |

| T23   | V <sub>DD</sub>          |             |  |  |

| T24   | IDE_DACK1#               |             |  |  |

| T25   | IDE_IOW1#                |             |  |  |

| T26   | IDE_DACK0#               |             |  |  |

| U1    | AV <sub>DD1</sub> (DAC)  |             |  |  |

| U2    | V <sub>DD</sub> USB      |             |  |  |

| U3    | SYNC                     |             |  |  |

| COIO4 | SDATA_IN                 |             |  |  |

Signal Definitions (Continued)

|            | Signal Name         |                    |  |

|------------|---------------------|--------------------|--|

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |  |

| U23        | IDE_DATA7           | •                  |  |

| U24        | IDE_DATA6           |                    |  |

| U25        | IDE_ADDR0           |                    |  |

| U26        | IDE_ADDR1           |                    |  |

| V1         | SDATA_OUT           |                    |  |

| V2         | BIT_CLK             |                    |  |

| V3         | PC_BEEP             |                    |  |

| V4         | POWER_EN            |                    |  |

| V23        | V <sub>SS</sub>     |                    |  |

| V24        | IDE_DATA8           |                    |  |

| V25        | IDE_DATA10          |                    |  |

| V26        | IDE_CS0#            |                    |  |

| W1         | USBCLK              |                    |  |

| W2         | NC                  |                    |  |

| W3         | OVER_CUR#           |                    |  |

| W4         |                     |                    |  |

| W23        |                     |                    |  |

| W24        |                     |                    |  |

| W25        | IDE RST#            |                    |  |

| W26        | -                   |                    |  |

| Y1         | DPORT1              |                    |  |

| Y2         | D+_PORT1            |                    |  |

| Y3         | NC)ataSheet4U.      | com                |  |

| Y4         |                     | COITI              |  |

| Y23        | V <sub>SS</sub>     |                    |  |

| Y24        | 66                  |                    |  |

| Y25        | IDE_DATA9           |                    |  |

| Y26        |                     |                    |  |

| AA1        | IDE_CS1#<br>DPORT2  |                    |  |

| AA1<br>AA2 |                     |                    |  |

| AA2<br>AA3 |                     |                    |  |

| AA3        | -                   |                    |  |

|            |                     |                    |  |

| AA23       | 00                  |                    |  |

| AA24       |                     |                    |  |

| AA25       |                     |                    |  |

| AA26       |                     |                    |  |

| AB1        | NC                  |                    |  |

| AB2        |                     |                    |  |

| AB3        |                     |                    |  |

| AB4        | DD=                 |                    |  |

| AB23       |                     |                    |  |

| AB24       |                     |                    |  |

| AB25       | IDE_DATA13          |                    |  |

| AB26       |                     |                    |  |

| AC1        | NC                  |                    |  |

| AC2        | NC                  |                    |  |

| AC3        |                     |                    |  |

| AC4        | V <sub>SS</sub>     |                    |  |

| AC5        | V <sub>SS</sub>     |                    |  |

| AC6        | SA3/SD3             | SD3                |  |

| AC7        | DACK7#              |                    |  |

| nber (C    | Continued)          |                    | , Tv            |

|------------|---------------------|--------------------|-----------------|

|            | Signal Na           | ,<br>,             |                 |

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode | ™ CS5530,       |

| AC8        | DACK1#              | •                  | l Ö             |

| AC9        | V <sub>SS</sub>     |                    |                 |

| AC10       | V <sub>DD</sub>     |                    |                 |

| AC11       | IOW#                |                    |                 |

| AC12       | V <sub>SS</sub>     |                    |                 |

| AC13       | V <sub>SS</sub>     |                    |                 |

| AC14       | IRQ3                |                    |                 |

| AC15       | MEMCS16#            |                    |                 |

| AC16       | V <sub>SS</sub>     |                    |                 |

| AC17       | IRQ14               |                    |                 |

| AC18       | V <sub>SS</sub>     |                    |                 |

| AC19       | V <sub>DD</sub>     |                    |                 |

| AC20       | SA10/SD10           | SD10               |                 |

| AC21       | GPIO5/SA21          | SA21               |                 |

| AC22       | GPIO0               |                    |                 |

| AC23       | V <sub>SS</sub>     |                    |                 |

| AC24       | IDE_DREQ1           |                    |                 |

| AC25       | IDE_DATA14          |                    |                 |

| AC26       | IDE_DATA0           |                    |                 |

| AD1        | NC                  |                    |                 |

| AD2        | NC                  |                    | DataShe         |

| AD3        | NC                  |                    |                 |

| AD4        | SMEMR#/RTCALE       |                    |                 |

| AD5        | SA5/SD5             | SD5                |                 |

| AD6        | ISACLK              |                    |                 |

| AD7        | DACK6#              |                    |                 |

| AD8        | DACK0#              |                    |                 |

| AD9        | SA2/SD2             | SD2                |                 |

| AD10       | SA19                |                    |                 |

| AD11       | SA16                |                    |                 |

| AD12       | DRQ1                |                    |                 |

| AD13       | DRQ3                |                    |                 |

| AD14       | IRQ7                |                    |                 |

| AD15       | SA_LATCH            | SA_DIR             |                 |

| AD16       | V <sub>DD</sub>     |                    |                 |

| AD17       | IRQ15               |                    |                 |

| AD18       | DRQ5                |                    |                 |

| AD19       | SA9/SD9             | SD9                |                 |

| AD20       | V <sub>SS</sub>     |                    |                 |

| AD21       | GPORT_CS#           | 1                  |                 |

| AD22       | GPIO4/SA20          | SA20               |                 |

| AD23       | V <sub>DD</sub>     | 1                  |                 |

| AD24       | SA14/SD14           | SD14               |                 |

| AD25       | IDE_IORDY0          |                    |                 |

| AD26       | IDE_DREQ0           |                    |                 |

| AE1        | NC                  |                    |                 |

| AE2        | NC                  |                    |                 |

| AE3        | CLK_32K             |                    |                 |

| AE4        | KBROMCS#            |                    |                 |

| AE5        | IRQ9                | www Data           | Sheet4U.com     |

| AE6        | SA1/SD1             | SD1                | 5.000 TO 100011 |

et4U.com

DataShe

DataSheet4U.com

Revision 1.1

DataSheet4

# Geode<sup>TM</sup> CS5530A

### Table 2-2. 352 PBGA Pin Assignments - Sorted by Pin Number (Continued)

|            | Signal Na           | ime                |

|------------|---------------------|--------------------|

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |

| AE7        | DACK5#              |                    |

| AE8        | AEN                 |                    |

| AE9        | SA0/SD0             | SD0                |

| AE10       | DRQ2                |                    |

| AE11       | SA18                |                    |

| AE12       | IOR#                |                    |

| AE13       | IRQ5                |                    |

| AE14       | IRQ8#               |                    |

| AE15       | IRQ4                |                    |

| AE16       | IRQ10               |                    |

| AE17       | SBHE#               |                    |

| AE18       | DRQ0                |                    |

| AE19       | MEMR#               |                    |

| AE20       | DRQ6                |                    |

| AE21       | SA12/SD12           | SD12               |

| AE22       | SA13/SD13           | SD13               |

|            | Signal Name         |                    |  |  |  |  |  |  |

|------------|---------------------|--------------------|--|--|--|--|--|--|

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |  |  |  |  |  |  |

| AE23       | GPIO6/SA22          | SD22               |  |  |  |  |  |  |

| AE24       | GPIO1/SDATA_IN2     | GPIO1/SDATA_IN2    |  |  |  |  |  |  |

| AE25       | SA15/SD15           | SA15/SD15 SD15     |  |  |  |  |  |  |

| AE26       | IDE_IORDY1          |                    |  |  |  |  |  |  |

| AF1        | NC                  |                    |  |  |  |  |  |  |

| AF2        | NC                  |                    |  |  |  |  |  |  |

| AF3        | SMEMW#/RTCCS#       |                    |  |  |  |  |  |  |

| AF4        | SA7/SD7             | SD7                |  |  |  |  |  |  |

| AF5        | SA6/SD6             | SD6                |  |  |  |  |  |  |

| AF6        | SA4/SD4             | SD4                |  |  |  |  |  |  |

| AF7        | DACK3#              |                    |  |  |  |  |  |  |

| AF8        | DACK2#              |                    |  |  |  |  |  |  |

| AF9        | BALE                |                    |  |  |  |  |  |  |

| AF10       | ZEROWS#             | ZEROWS#            |  |  |  |  |  |  |

| AF11       | IOCHRDY             |                    |  |  |  |  |  |  |

| AF12       | SA17                |                    |  |  |  |  |  |  |

|            | Signal Name         |                    |  |  |  |  |  |  |

|------------|---------------------|--------------------|--|--|--|--|--|--|

| Pin<br>No. | Limited<br>ISA Mode | ISA Master<br>Mode |  |  |  |  |  |  |

| AF13       | IRQ1                |                    |  |  |  |  |  |  |

| AF14       | IRQ6                |                    |  |  |  |  |  |  |

| AF15       | TC                  |                    |  |  |  |  |  |  |

| AF16       | IOCS16#             |                    |  |  |  |  |  |  |

| AF17       | IRQ12               |                    |  |  |  |  |  |  |

| AF18       | IRQ11               |                    |  |  |  |  |  |  |

| AF19       | SA8/SD8             | SD8                |  |  |  |  |  |  |

| AF20       | MEMW#               |                    |  |  |  |  |  |  |

| AF21       | SA11/SD11           | SD11               |  |  |  |  |  |  |

| AF22       | DRQ7                |                    |  |  |  |  |  |  |

| AF23       | GPIO7/SA23          | SA23               |  |  |  |  |  |  |

| AF24       | GPIO3               |                    |  |  |  |  |  |  |

| AF25       | GPIO2               |                    |  |  |  |  |  |  |

| AF26       | GPCS#               |                    |  |  |  |  |  |  |

et4U.com

DataSheet4U.com

DataSheet4J.com

www.DataSheet4U.com

|                         |                    |                       |                          |            | 1   |                      |                    | [                     |                          |            |

|-------------------------|--------------------|-----------------------|--------------------------|------------|-----|----------------------|--------------------|-----------------------|--------------------------|------------|

| Signal N                |                    |                       |                          | Dia        |     | Signal Na            |                    | -                     |                          | Dia        |

| Limited ISA<br>Mode     | ISA Master<br>Mode | Pin Type <sup>1</sup> | Buffer Type <sup>2</sup> | Pin<br>No. |     | Limited ISA<br>Mode  | ISA Master<br>Mode | Pin Type <sup>1</sup> | Buffer Type <sup>2</sup> | Pin<br>No. |

| D0                      | ·                  | I/O                   | PCI                      | A15        |     | DACK0#               | 4                  | 0                     | 8 mA                     | AD8        |

| D1                      |                    | I/O                   | PCI                      | D14        |     | DACK1#               |                    | 0                     | 8 mA                     | AC8        |

| 02                      |                    | I/O                   | PCI                      | C16        |     | DACK2#               |                    | 0                     | 8 mA                     | AF8        |

| D3                      |                    | I/O                   | PCI                      | B15        |     | DACK3#               |                    | 0                     | 8 mA                     | AF7        |

| D4                      |                    | I/O                   | PCI                      | C17        |     | DACK5#               |                    | 0                     | 8 mA                     | AE7        |

| D5                      |                    | I/O                   | PCI                      | B16        |     | DACK6#               |                    | 0                     | 8 mA                     | AD7        |

| D6                      |                    | I/O                   | PCI                      | B17        |     | DACK7#               |                    | 0                     | 8 mA                     | AC7        |

| D7                      |                    | I/O                   | PCI                      | A16        |     | DCLK                 |                    | 0                     | DOTCLK                   | A10        |

| D8                      |                    | I/O                   | PCI                      | D18        | 1   | DDC_SCL              |                    | 0                     | 8 mA                     | M2         |

| \D9                     |                    | I/O                   | PCI                      | A17        | 1   | DDC_SDA              |                    | I/O                   | 8 mA                     | M4         |

| D10                     |                    | I/O                   | PCI                      | A19        | 1   | DEVSEL#              |                    | I/O                   | PCI                      | A23        |

| D11                     |                    | I/O                   | PCI                      | B19        | 1   | DPORT1               |                    | I/O                   | USB                      | Y1         |

| AD12                    |                    | I/O                   | PCI                      | A18        | 1   | D+_PORT1             |                    | I/O                   | USB                      | Y2         |

| AD13                    |                    | I/O                   | PCI                      | C20        | 1   | DPORT2               |                    | I/O                   | USB                      | AA1        |

| D14                     |                    | I/O                   | PCI                      | B20        | 1   | D+_PORT2             |                    | 1/O                   | USB                      | AA2        |

| D15                     |                    | I/O                   | PCI                      | A20        | 1   | DRQ0                 |                    | 1                     | 8 mA                     | AE18       |

| D16                     |                    | I/O                   | PCI                      | A26        |     | DRQ1                 |                    | 1                     | 8 mA                     | AD12       |

| D17                     |                    | I/O                   | PCI                      | A25        |     | DRQ2                 |                    |                       | 8 mA                     | AE10       |

| D18                     |                    | 1/O                   | PCI                      | B25        |     | DRQ3                 |                    |                       | 8 mA                     | AD13       |

| D19                     |                    | 1/O                   | PCI                      | B26        |     | DRQ5                 |                    |                       | 8 mA                     | AD18       |

| D20                     |                    | 1/O                   | PCI                      | E24        |     | DRQ6                 |                    |                       | 8 mA                     | AE20       |

| D20                     |                    | 1/O                   | PCI                      | C25        |     | DRQ7                 |                    |                       | 8 mA                     | AF22       |

| D21                     |                    | 1/O                   | PCI D                    | a C26      | eet |                      |                    |                       | 8 mA                     | B1         |

| D23                     |                    | 1/O                   | PCI D                    | E25        | Cel | EXTVREFIN            |                    | I, Analog             |                          | T2         |

| D23                     |                    | 1/O                   | PCI                      | F25        |     | FP_CLK               | No Function        | I, Analog<br>O        | FP_CLK                   | M1         |

| 025                     |                    | 1/O                   | PCI                      | G24        |     | FP_CLK_EVEN          | No Function        | 0                     | 8 mA                     | L3         |

| D25                     |                    | 1/O                   | PCI                      | 024<br>D25 |     | FP_DATA0             | SA0                | 1/0                   | 8 mA                     | K3         |

| 027                     |                    | 1/O<br>1/O            | PCI                      | F26        |     | FP_DATA1             | SA0<br>SA1         | 1/O<br>1/O            | 8 mA                     | J2         |

| D27                     |                    | 1/0                   | PCI                      | G25        |     | FP_DATA1             | SA1<br>SA2         | 1/O<br>1/O            |                          | J2<br>J3   |

|                         |                    | 1/O                   | PCI                      |            |     |                      | SA2<br>SA3         | 1/O<br>1/O            | 8 mA                     |            |

| ND29<br>ND30            |                    | 1/O                   | PCI                      | G26<br>J24 |     | FP_DATA3<br>FP_DATA4 | SA3<br>SA4         | 1/O<br>1/O            | 8 mA                     | J1<br>H1   |

| D30                     |                    | 1/O                   | PCI                      | H25        |     | FP_DATA5             | SA4<br>SA5         | 1/O<br>1/O            | 8 mA<br>8 mA             | G2         |

|                         |                    | 0                     |                          |            |     |                      | +                  |                       |                          |            |

|                         |                    | I, Analog             | 8 mA                     | AE8<br>U1  | -   | FP_DATA6<br>FP_DATA7 | SA6<br>SA7         | I/O<br>I/O            | 8 mA                     | G4<br>G3   |