# **CS8240**

# 500 mA High Side (PNP) Driver with On-Chip Flyback Diode

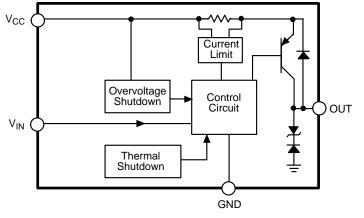

The CS8240 is a fast, PNP high side driver capable of delivering up to 500 mA into a resistive or inductive load in harsh automotive or industrial environments. An internal flyback diode clamp is incorporated for inductive loads. The input (V<sub>IN</sub>) is TTL and CMOS compatible and has hysteresis to minimize the effects of noise. When the input is high, the output is on. When the input is low, the output is off and the supply voltage quiescent current is very low (< 1.0  $\mu$ A, typ). For device protection, the CS8240 incorporates thermal shutdown, short circuit current limiting, overvoltage shutdown, and reverse battery protection. The CS8240 can withstand supply voltage transients of 60 V (min) and –50 V.

The CS8240 is available in an overmolded 5 lead TO-220 package and is a competitive replacement for the LM-1921, LM-1951, LM-1952, MC-3399, and L-9350.

#### Features

- Low Output Saturation Voltage

- 0.22 V at I<sub>OUT</sub> = 125 mA

- 0.33 V at I<sub>OUT</sub> = 225 mA

- Overmolded Package

- On-Chip Flyback Diode

- Fault Protection

- Over Voltage Shutdown (32 V, typ)

- Thermal Shutdown (165°C, typ)

- Short Circuit Limiting (1.1 A typ)

- - 50 V Reverse Transient Protection

- 60 V Load Dump Protection

- Reverse Battery

- Low Quiescent Current (Off State)

- ESD Protected

Figure 1. Block Diagram

## ON Semiconductor™

http://onsemi.com

#### **ORDERING INFORMATION**

| Device       | Package                         | Shipping      |  |

|--------------|---------------------------------|---------------|--|

| CS8240YTQ5   | TO–220<br>FIVE LEAD<br>STRAIGHT | 50 Units/Rail |  |

| CS8240YTQVA5 | TO-220<br>FIVE LEAD<br>VERTICAL | 50 Units/Rail |  |

#### **MAXIMUM RATINGS\***

| Rating                                     |                                                 | Value                 | Unit   |

|--------------------------------------------|-------------------------------------------------|-----------------------|--------|

| Supply Voltage                             |                                                 | 6.0 to 26             | V      |

| Overvoltage Protection                     |                                                 | 60                    | V      |

| Reverse Voltage:                           | DC<br>Transient                                 | -16<br>-50            | V<br>V |

| Internal Power Dissipation                 |                                                 | Internally<br>limited | -      |

| Logic Input Voltage                        |                                                 | -0.3 to +7.0          | V      |

| Junction Temperature Range, T <sub>J</sub> |                                                 | -40 to150             | °C     |

| Storage Temperature Range, T <sub>S</sub>  |                                                 | -55 to +165           | °C     |

| Lead Temperature Soldering:                | Wave Solder (through hole styles only) (Note 1) | 260 peak              | °C     |

| Electrostatic Discharge (Human Body Model) |                                                 | 2.0                   | kV     |

1. 10 second maximum.

\*The maximum package power dissipation must be observed.

### $\label{eq:expectation} \textbf{ELECTRICAL CHARACTERISTICS} \quad (-40^{\circ}C \leq T_A \leq 125^{\circ}C; \ -40^{\circ}C \leq T_J \leq 150^{\circ}C, \ \text{unless otherwise specified.})$

| Characteristic               | Test Conditions                                                                  | Min  | Тур         | Max   | Unit   |

|------------------------------|----------------------------------------------------------------------------------|------|-------------|-------|--------|

| General Characteristics      | ·                                                                                |      |             |       |        |

| Operating Supply Voltage     | √oltage –                                                                        |      | -           | -     | V      |

| Quiescent Current            |                                                                                  | -    | 1.0         | 100   | μΑ     |

|                              | $6.0 V \le V_{CC} \le 20 V$                                                      | -    | 16          | 30    | mA     |

|                              | $20 \text{ V} \le \text{V}_{\text{CC}} \le 24 \text{ V}$                         | -    | 25          | 50    | mA     |

| Output Stage                 |                                                                                  |      |             |       |        |

| Output Saturation Voltage    | $V_{IN} \leq V_{IN(HI)}$ , $V_{CC}$ = 6.0 V, $I_{LOAD}$ = 125 mA                 | -    | 0.22        | 0.5   | V      |

|                              | $V_{CC} = 14$ V, $I_{LOAD} = 225$ mA                                             | -    | 0.33        | 0.7   | V      |

| Output Leakage Current       | Input $\leq$ V <sub>IN(L)</sub> , V <sub>CC</sub> = 12 V, V <sub>OUT</sub> = 0 V | -    | 1.0         | 150   | μA     |

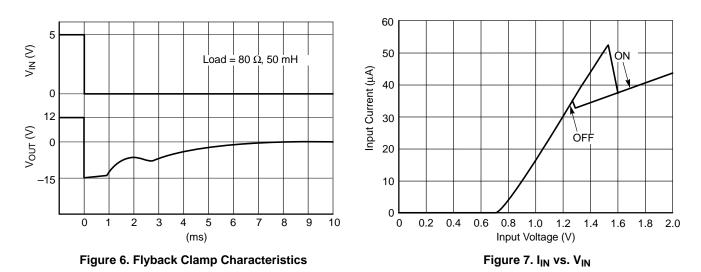

| Negative Output Clamp        | I <sub>CLAMP</sub> = 100 mA, V <sub>CC</sub> = 12 V                              | -18  | -15.5       | -12   | V      |

| Turn On Delay Time           | V <sub>CC</sub> = 12 V, I <sub>LOAD</sub> = 150 mA                               | _    | 5.0         | 20    | μs     |

| Turn Off Delay Time          | V <sub>CC</sub> = 12 V, I <sub>LOAD</sub> = 150 mA                               | _    | 5.0         | 20    | μs     |

| Input Stage                  |                                                                                  |      |             |       | •      |

| Input Voltage                | Logic = High, $V_{CC}$ = 12 V Turn ON                                            | 0.8  | 1.45<br>1.2 | - 2.0 | V<br>V |

|                              | Logic = Low, V <sub>CC</sub> = 12 V Turn OFF                                     | -    | 1.2         | 2.0   | v      |

| Input Current                | $V_{IN} = 5.5 V$                                                                 | -    | 100         | 200   | μA     |

|                              | V <sub>IN</sub> = 0.8 V                                                          | -    | 15          | 50    | μA     |

| Protection Circuitry         |                                                                                  |      |             |       |        |

| Overvoltage Shutdown         | $V_{IN} \ge V_{IN(HI)}$                                                          | 26   | 32          | -     | V      |

| Output Short Circuit Current | $V_{IN} \ge V_{IN(HI)}, V_{CC} = 12 \text{ V}, V_{OUT} = 0 \text{ V}$            | 0.55 | 1.1         | 2.5   | А      |

| Thermal Shutdown             | -                                                                                | 150  | 165         | -     | °C     |

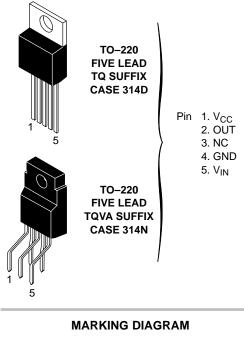

#### PACKAGE PIN DESCRIPTION

| PACKAGE PIN # |                 |                                                                                          |

|---------------|-----------------|------------------------------------------------------------------------------------------|

| 5 Lead TO-220 | PIN SYMBOL      | FUNCTION                                                                                 |

| 1             | V <sub>CC</sub> | Supply Voltage to the IC. Supplies load current through PNP.                             |

| 2             | OUT             | Collector of output PNP, current to load is sourced from this lead.                      |

| 3             | NC              | No connection.                                                                           |

| 4             | GND             | Ground.                                                                                  |

| 5             | V <sub>IN</sub> | Input voltage to control output. Logic high turns output on. Logic low turns output off. |

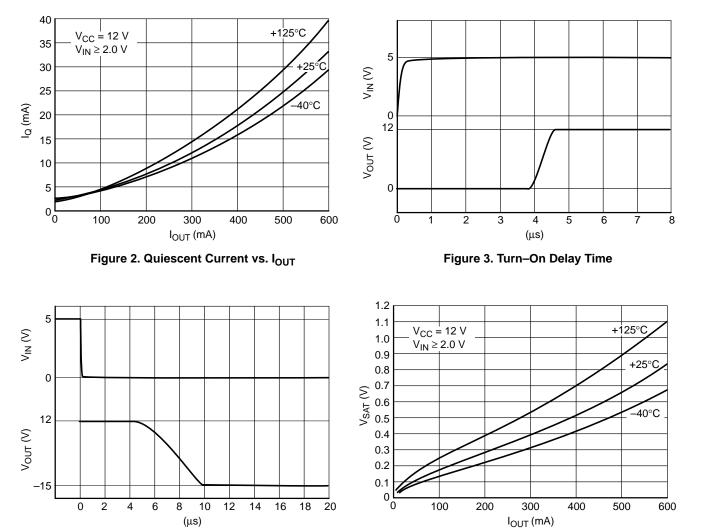

### **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 5. Output Saturation Voltage vs. I<sub>OUT</sub>

#### **CIRCUIT DESCRIPTION**

#### Input Stage

The input stage is a self biased band gap based circuit with a positive going trip point of 1.45 V (typ) and a negative going trip point of 1.20 V (typ) (250 mV of hysteresis). When the input voltage is below the positive trip point, the quiescent current of the supply voltage line is less than 1.0  $\mu$ A, (typ). When the input voltage exceeds the positive trip point (1.45 V, typ), the input stage "wakes up" the rest of the CS8240 circuitry and turns on the output stage.

#### **Output Stage**

The output stage is built around a high current PNP output transistor. A control amplifier monitors the saturation voltage of the output PNP and maintains a balance of low saturation voltage and minimum base drive to the PNP for the given output current. The base drive of the PNP is the dominant component of the quiescent current of the CS8240 and is dependent on the level of output current.

Short circuit protection (1.1 A, typ) is also incorporated in the output stage.

#### **Protection Circuitry**

In addition to the short circuit protection mentioned above, the CS8240 also incorporates a thermal shutdown circuit (165°C, typ) and a high voltage shutdown circuit (33 V, typ), both of which cut off the drive to the PNP output transistor when excessive current is drawn. Inherent in the design of the CS8240 is transient protection to +60 V and -50 V on the supply line. The CS8240 is ESD protected in excess of 2.0 kV (Human Body Model).

## CS8240

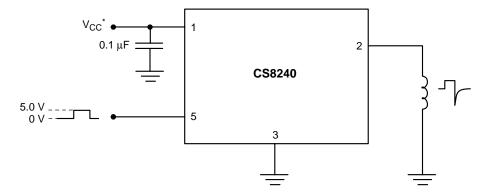

## **TYPICAL APPLICATION CIRCUITS**

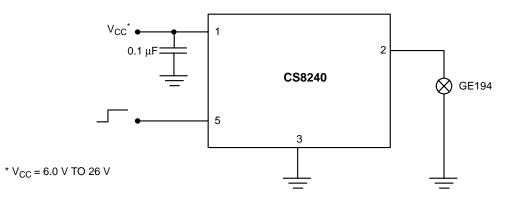

Figure 9. Lamp Driver

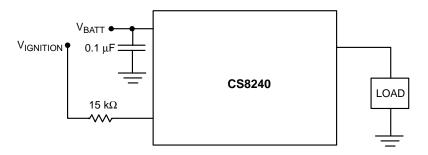

Figure 10. Controlled High Side Switch

#### PACKAGE DIMENSIONS

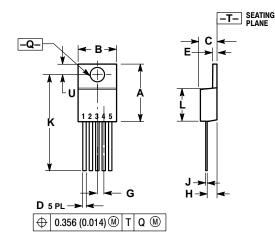

TO-220 **FIVE LEAD TQ SUFFIX** CASE 314D-04 ISSUE E

NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL NOT EVCED 10.92 (0.042) MAXIMUM NOT EXCEED 10.92 (0.043) MAXIMUM.

|     | INCHES    |       | MILLIMETERS |        |

|-----|-----------|-------|-------------|--------|

| DIM | MIN       | MAX   | MIN         | MAX    |

| Α   | 0.572     | 0.613 | 14.529      | 15.570 |

| В   | 0.390     | 0.415 | 9.906       | 10.541 |

| С   | 0.170     | 0.180 | 4.318       | 4.572  |

| D   | 0.025     | 0.038 | 0.635       | 0.965  |

| Е   | 0.048     | 0.055 | 1.219       | 1.397  |

| G   | 0.067 BSC |       | 1.702 BSC   |        |

| Н   | 0.087     | 0.112 | 2.210       | 2.845  |

| ſ   | 0.015     | 0.025 | 0.381       | 0.635  |

| Κ   | 0.990     | 1.045 | 25.146      | 26.543 |

| L   | 0.320     | 0.365 | 8.128       | 9.271  |

| Q   | 0.140     | 0.153 | 3.556       | 3.886  |

| U   | 0.105     | 0.117 | 2.667       | 2.972  |

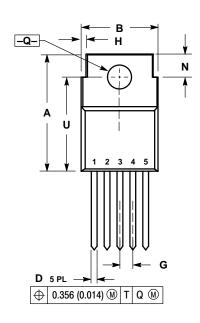

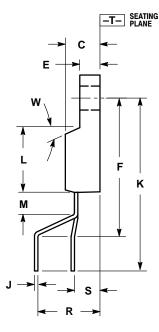

TO-220 **FIVE LEAD TQVA SUFFIX** CASE 314N-01 ISSUE O

- NOTES: 1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH. 3. DIMENSION D DOES NOT INCLUDE INTERCONNECT BAR (DAMBAR) PROTRUSION. DIMENSION D INCLUDING PROTRUSION SHALL NOT EXCEED 10.92 (0.043) MAXIMUM. 4. LEADS MAINTAIN A RIGHT ANGLE WITH RESPECT TO THE PACKAGE BODY TO WITHIN ± 0.015".

|     | INC   | HES   | MILLIMETERS |       |  |

|-----|-------|-------|-------------|-------|--|

| DIM | MIN   | MAX   | MIN         | MAX   |  |

| Α   | 0.604 | 0.614 | 15.34       | 15.60 |  |

| В   | 0.395 | 0.405 | 10.03       | 10.29 |  |

| С   | 0.175 | 0.185 | 4.44        | 4.70  |  |

| D   | 0.027 | 0.037 | 0.69        | 0.94  |  |

| Е   | 0.100 | 0.110 | 2.54        | 2.79  |  |

| F   | 0.712 | 0.727 | 18.08       | 18.47 |  |

| G   | 0.067 | BSC   | 1.70        | BSC   |  |

| н   | 0.020 | 0.030 | 0.51        | 0.76  |  |

| J   | 0.014 | 0.022 | 0.36        | 0.56  |  |

| Κ   | 0.889 | 0.904 | 22.58       | 22.96 |  |

| L   | 0.324 | 0.339 | 8.23        | 8.61  |  |

| М   | 0.115 | 0.130 | 2.92        | 3.30  |  |

| Ν   | 0.115 | 0.125 | 2.92        | 3.17  |  |

| Q   | 0.120 | 0.130 | 3.05        | 3.30  |  |

| R   | 0.292 | 0.342 | 7.42        | 8.69  |  |

| S   | 0.133 | 0.183 | 3.38        | 4.65  |  |

| U   | 0.480 | 0.495 | 12.19       | 12.57 |  |

| W   | 5     | 0     | 5           | 0     |  |

#### PACKAGE THERMAL DATA

| Parameter        |         | TO-220, Five Lead | Unit |

|------------------|---------|-------------------|------|

| R <sub>0JC</sub> | Typical | 4.0               | °C/W |

| R <sub>OJA</sub> | Typical | 50                | °C/W |

**ON Semiconductor** and without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer.

#### PUBLICATION ORDERING INFORMATION

#### Literature Fulfillment:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: ONlit@hibbertco.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

JAPAN: ON Semiconductor, Japan Customer Focus Center 4–32–1 Nishi–Gotanda, Shinagawa–ku, Tokyo, Japan 141–0031 Phone: 81–3–5740–2700 Email: r14525@onsemi.com

ON Semiconductor Website: http://onsemi.com

For additional information, please contact your local Sales Representative.