### **Revision History**

| Rev. No. | History                                          | Issue Date    |

|----------|--------------------------------------------------|---------------|

| 1.0      | New issue                                        | Sep. 26, 2008 |

| 1.1      | Add new package type                             | Dec. 23, 2008 |

|          | Update AC data                                   |               |

|          | Modify Rext vs. lout relation                    |               |

| 1.2      | Add new package type                             | Apr. 6, 2009  |

| 1.3      | Add new package type                             | Oct. 5, 2009  |

|          | Modify Rext vs. lout formula                     |               |

| 1.4      | Updated thermal resistance and power dissipation | Feb. 3, 2010  |

| 1.5      | Format modify                                    | Oct. 19, 2010 |

1

# CS8816(AF/AN/CP/AM/AN-1)

## 16-Bit Constant Current LED Driver with 3.0V to 5.5V Supply Voltage

#### Description

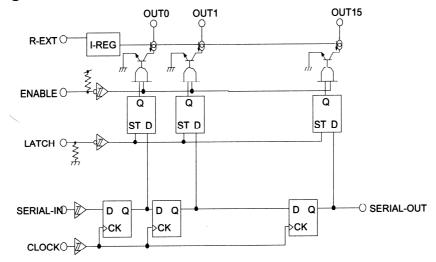

The CS8816 is a 16-Bit constant current LED driver IC which is designed for LED displays. The output current can be adjusted by using an external resistor. All outputs will have the same current drive level which is crucial in LED display application. This driver has built-in 16-bit constant current outputs, a 16-bit shift register, and a 16-bit latch circuit. These drivers have been designed by using CMOS process.

#### Feature

- > Output current capability: 70mA each output

- Constant current range: 5mA to 70mA

- For common anode LED application

- Power supply voltage range VDD=3.0V to 5.5V

- Maximum output drain voltage 7.0V

- Serial data transfer rate: 25MHz(Cascade Connection)

- > Operating temperature range: -40 to 85 degree C

- Output current accuracy:

Between Bits : < +-1.5 % Between ICs: < +-4 %

#### Product Family

CS8816AF ------ 24SSOP(236mil, 1.0mm lead-pitch)

- CS8816AN ------ 24SSOP(150mil, 0.64mm lead-pitch)

- CS8816CP ------ 24Shrink PDIP(300mil, 1.78mm lead-pitch)

- CS8816AM ------ 24SOP(300mil, 1.27mm lead-pitch)

- CS8816AN-1 ------ 24SSOP(150mil, 0.64mm lead-pitch)

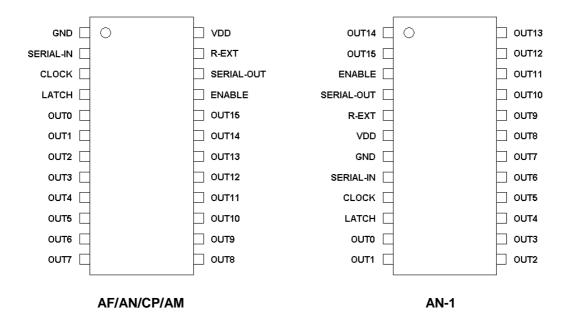

#### Pin Assignment

#### Block Diagram

#### Truth Table

| CLOCK         | LATCH | ENABLE | SERIAL-IN | OUT0OUT7OUT15    | SERIAL-OUT |

|---------------|-------|--------|-----------|------------------|------------|

| Positive edge | Н     | L      | Dn        | /Dn/Dn-7/Dn-15   | Dn-15      |

| Positive edge | L     | L      | Dn+1      | No Change        | Dn-14      |

| Positive edge | Н     | L      | Dn+2      | /Dn+2/Dn-5/Dn-13 | Dn-13      |

| Negative edge | Х     | L      | Dn+3      | /Dn+2/Dn-5/Dn-13 | Dn-13      |

| Negative edge | Х     | Н      | Dn+3      | Off              | Dn-13      |

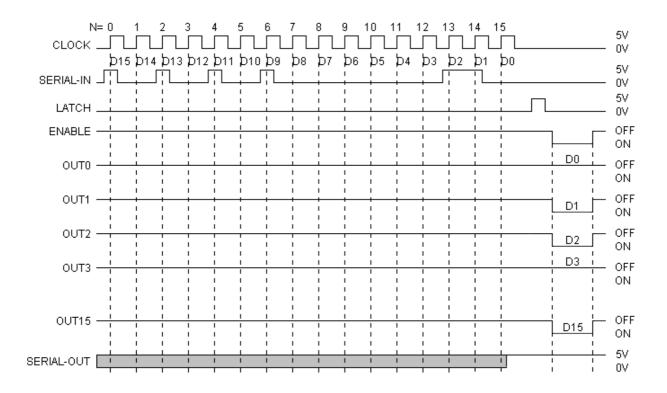

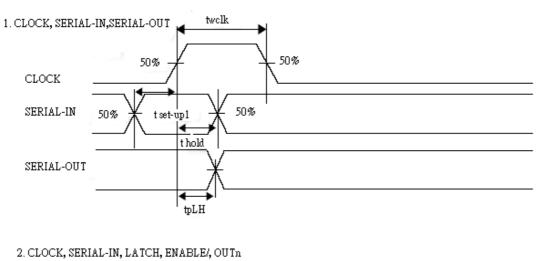

#### Timing Diagram

#### Note:

- 1. The latch circuit is a level-latch, not an edge-triggered latch.

- The latch circuit holds data when LATCH pin low. When the LATCH pin is at high-level, the latch circuit passes the data from input to output. When ENABLE pin is at low-level, the latch is data transferred to the output pin OUT0~OUT15. When ENABLE pin is at high-level, the OUT0~OUT15 is turned off regardless of the latch data.

#### Pin Description

| Pin No. | Pin Name   | Function                                                           |

|---------|------------|--------------------------------------------------------------------|

| 1       | GND        | GND Pin.                                                           |

| 2       | SERIAL-IN  | Serial input data pin.                                             |

| 3       | CLOCK      | Clock input terminal for shift register, rising edge trigger.      |

| 4       | LATCH      | Data latch input pin. When LATCH=High-level, data is passed to     |

|         |            | OUT0~OUT15, when LATCH=Low-level, data is latched.                 |

| 5~20    | OUT0~OUT15 | 16 constant current output pin to drive common anode LEDs.         |

| 21      | ENABLE     | Data output enable pin, when ENABLE=High-level, all OUT0~OUT15 are |

|         |            | turned off, and when ENABLE=Low-level, all OUT0~OUT15 are enabled. |

| 22      | SERIAL-OUT | Serial data output pin for cascade operation.                      |

| 23      | R-EXT      | The external resistor connection pin to adjust the output current. |

| 24      | VDD        | 3.0V~5.5V supply voltage pin.                                      |

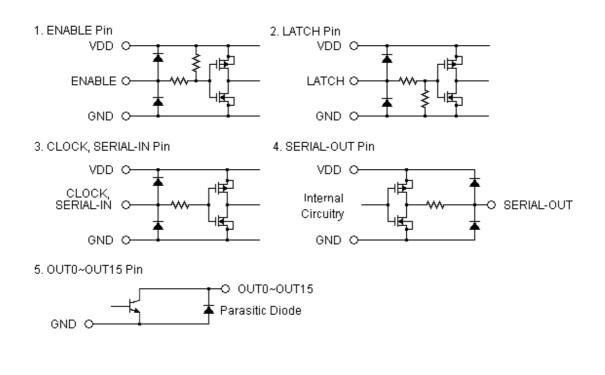

### Equivalent Circuits of I/O Pins

### Absolute Maximum Ratings

| Characteristics                        | Symbol   | Rating                                         | Unit |

|----------------------------------------|----------|------------------------------------------------|------|

| Supply Voltage                         | VDD      | +7.0                                           | V    |

| Input Voltage                          | Vin      | -0.4 to VDD+0.4                                | V    |

| Output Current                         | lout     | +70                                            | mA   |

| Output Voltage                         | Vout     | -0.5 to 7.0                                    | V    |

| GND Pin Current                        | IGND     | 1120                                           | mA   |

| Clock Frequency                        | fCLK     | 25                                             | MHz  |

| Power Dissipation<br>(On PCB, Ta=45C)  | Pd       | AF: 2.36<br>AN: 1.94<br>CP: 1.91<br>AM: 1.76   | W    |

| Thermal Resistance<br>(On PCB, Ta=45C) | Rth(j-a) | AF: 44.4<br>AN: 54.25<br>CP: 55.07<br>AM: 59.6 | °C/W |

| Operating Temperature                  | Тор      | -40 to 85                                      | °C   |

| Storage Temperature                    | Tstg     | -55 to 150                                     | °C   |

## Recommended Operating Condition

| Characteristics       | Symbol  | Condition                    | Min    | Тур | Max     | Unit |

|-----------------------|---------|------------------------------|--------|-----|---------|------|

| Supply Voltage        | VDD     |                              | 3.0    | 5.0 | 5.5     | V    |

| Output Voltage        | VOUT    |                              |        |     | 7.0     | V    |

| Output Current        | IOUT    | OUTn                         |        |     | 70      | mA   |

|                       | IOL     | SERIAL-OUT Vol=0.5V          |        |     | 2.5     |      |

|                       | IOH     | SERIAL-OUT Voh=4.3V          |        |     | -2.0    |      |

| Input Voltage         | VIH     |                              | 0.7VDD |     | VDD+0.3 | V    |

|                       | VIL     |                              | -0.3   |     | 0.3VDD  |      |

| Clock Frequency       | fCLK    | VDD=5.0V, Cascade connection |        |     | 25      | MHz  |

|                       |         | VDD=3.0V, Cascade connection |        |     | 20      |      |

| Latch Pulse Width     | twLatch | VDD=4.5V ~ 5.5V              | 15     |     |         | ns   |

| Clock Pulse Width     | twCLOCK | VDD=4.5V ~ 5.5V              | 15     |     |         | ns   |

| Set-Up Time for Data  | tSETUP3 | VDD=4.5V ~ 5.5V              | 20     |     |         | ns   |

| Set-Up Time for Latch | tSETUP2 | VDD=4.5V ~ 5.5V              | 15     |     |         | ns   |

| Set-Up Time for Clock | tSETUP1 | VDD=4.5V ~ 5.5V              | 20     |     |         | ns   |

| Hold Time for Data    | tHOLD   | VDD=4.5V ~ 5.5V              | 20     |     |         | ns   |

### ■ Electrical Characteristics (Temp=25°C)

| Characteristics      | Symbol   | Condition                | Min  | Тур  | Max  | Unit |

|----------------------|----------|--------------------------|------|------|------|------|

| Supply Voltage       | VDD      |                          | 3.0  | 5.0  | 5.5  | V    |

| Output Current       | IOUT1    | VOUT=1.0V, VDD=5.0V,     |      | 24.6 |      | mA   |

|                      | IOUT2    | R-EXT=700Ohm             |      | 5.0  |      |      |

|                      |          | VOUT=1.0V, VDD=5.0V,     |      |      |      |      |

|                      |          | R-EXT=3450Ohm            |      |      |      |      |

| Output Current Error | IOUT1    | VOUT=1.0V, R-EXT=700Ohm  | -1.5 |      | +1.5 | %    |

| Between Bits         | IOUT2    | VOUT=1.0V, R-EXT=3450Ohm | -1.5 |      | +1.5 |      |

| Output Current Error | ILO3     | VOUT=1.0V, R-EXT=700Ohm  | -4   |      | +4   | %    |

| Between Chips        | IOL4     | VOUT=1.0V, R-EXT=3450Ohm | -4   |      | +4   |      |

| Output Leakage       | ILEAK    | VOUT=5.0V                |      |      | 1    | uA   |

| Current              |          |                          |      |      |      |      |

| Input Voltage Low    | VIL      | VDD=5.0V                 | 0    |      | 1.5  | V    |

| Input Voltage High   | VIH      | VDD=5.0V                 | 3.5  |      | 5.0  | V    |

| Output Voltage SOUT  | VOL      | IOL=+1.5mA, VDD=5.0V     |      |      | 0.5  | V    |

|                      | VOH      | IOH=-1.5mA, VDD=5.0V     | 4.3  |      |      |      |

| Pull-Up Resistor     | R(UP)    | ENABLE Pin               |      |      | 202  | KOhm |

| Pull-Down Resistor   | R(DOWN)  | LATCH Pin                |      |      | 128  | KOhm |

| Supply Current(Off)  | IDD(Off) | VDD=5.0V, R-EXT=700Ohm   |      | 3.7  |      | mA   |

| (OUT0~OUT15 Off)     |          | VDD=5.0V, R-EXT=3450Ohm  |      | 0.9  |      |      |

|                      |          | VDD=5.0V, R-EXT=Open     |      | 0.2  |      |      |

| Supply Current(On)   | IDD(On)  | VDD=5.0V, R-EXT=700Ohm   |      | 3.7  |      | mA   |

| (OUT0~OUT15 On)      |          | VDD=5.0V, R-EXT=3450Ohm  |      | 0.9  |      |      |

| Characteristics   | Symbol     | Condition                       | Min | Тур | Max | Unit |  |  |  |  |  |

|-------------------|------------|---------------------------------|-----|-----|-----|------|--|--|--|--|--|

|                   | tpLH1      | CLK-OUTn, LATCH="H", ENABLE="L" |     | 40  | 60  | ns   |  |  |  |  |  |

|                   | tpLH2      | LATCH-OUTn, ENABLE="L"          |     | 35  | 50  | ns   |  |  |  |  |  |

|                   | tpLH3      | ENABLE-OUTn, LATCH="H"          |     | 20  | 30  | ns   |  |  |  |  |  |

| Propagation Dolov | tpLH       | CLK-SERIAL OUT                  |     | 30  | 40  | ns   |  |  |  |  |  |

| Propagation Delay | tpHL1      | CLK-OUTn, LATCH="H", ENABLE="L" |     | 80  | 125 | ns   |  |  |  |  |  |

|                   | tpHL2      | LATCH-OUTn, ENABLE="L"          |     | 75  | 120 | ns   |  |  |  |  |  |

|                   | tpHL3      | ENABLE-OUTn, LATCH="H"          |     | 130 | 180 | ns   |  |  |  |  |  |

|                   | tpHL       | CLK-SERIAL OUT                  |     | 30  | 40  | ns   |  |  |  |  |  |

|                   | tW(CLOCK)  | CLOCK                           | 15  |     |     | ns   |  |  |  |  |  |

| Pulse Width       | tW(LATCH)  | LATCH                           | 10  |     |     | ns   |  |  |  |  |  |

|                   | tW(ENABLE) | ENABLE                          | 180 |     |     | ns   |  |  |  |  |  |

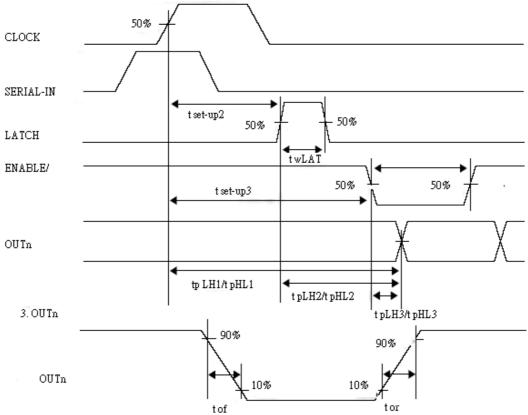

| Output Rise Time  | tor        | Voltage waveform 10%~90%        | 30  | 75  | 150 | ns   |  |  |  |  |  |

| Output Fall Time  | tof        | Voltage waveform 90%~10%        | 10  | 20  | 40  | ns   |  |  |  |  |  |

| Max CLK Rise Time | tr         |                                 |     |     | 480 | ns   |  |  |  |  |  |

| Max CLK Fall Time | tf         |                                 |     |     | 480 | ns   |  |  |  |  |  |

#### **Switching Characteristics** (Temp=25°C, VDD=5V, VIH=3.5V, VIL=0V, R-EXT=860Ohm)

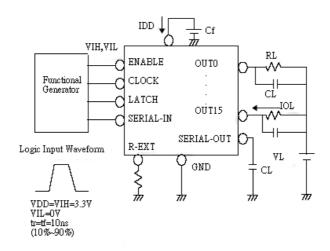

### Test Circuit

(RL=162Ohm, CL=10pf, VL=5.0V)

### Timing Waveform

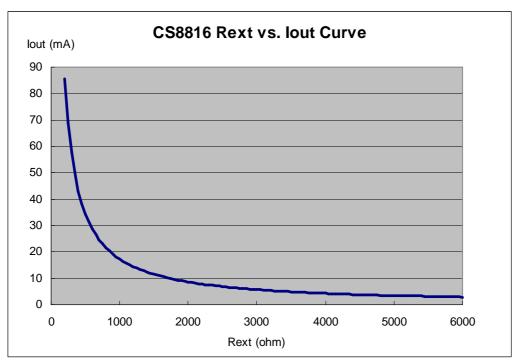

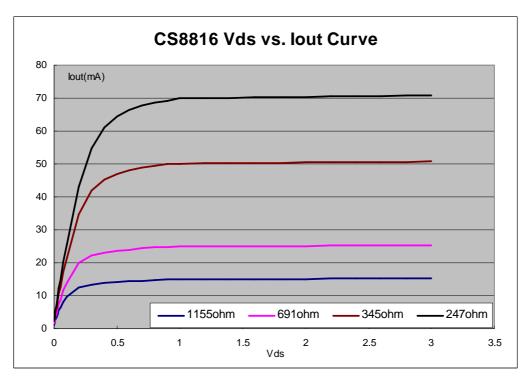

## Output Current vs. R-EXT (VDD=5V)

lout = (1.22/Rext) x 14.62

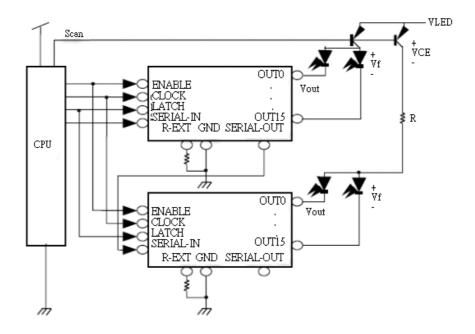

#### Typical Application

LED supply voltage is set-up by following equation:

VLED = VCE + Vf + Vo

To prevent too much power dissipated by driver due to the higher VLED, an additional R can be introduced to reduce the Vo when output is consuming current.

R = (VLED - VCE - Vf - Vo min)/( Io max \* Bit max)

### Order Information

| Part No.   | Package Type          | Lead Pitch |

|------------|-----------------------|------------|

| CS8816AF   | 24SSOP(236mil)        | 1.0mm      |

| CS8816AN   | 24SSOP(150mil)        | 0.64mm     |

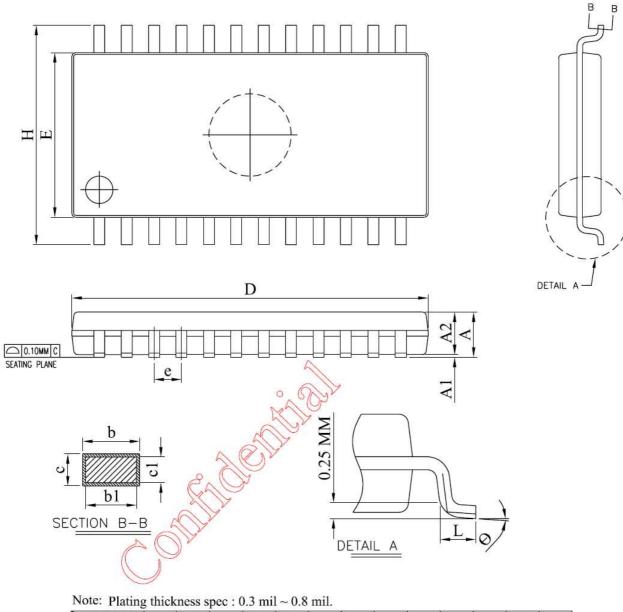

| CS8816CP   | 24Shrink PDIP(300mil) | 1.78mm     |

| CS8816AM   | 24SOP(300mil)         | 1.27mm     |

| CS8816AN-1 | 24SSOP(150mil)        | 0.64mm     |

11

Rev. 1.5

CS8816

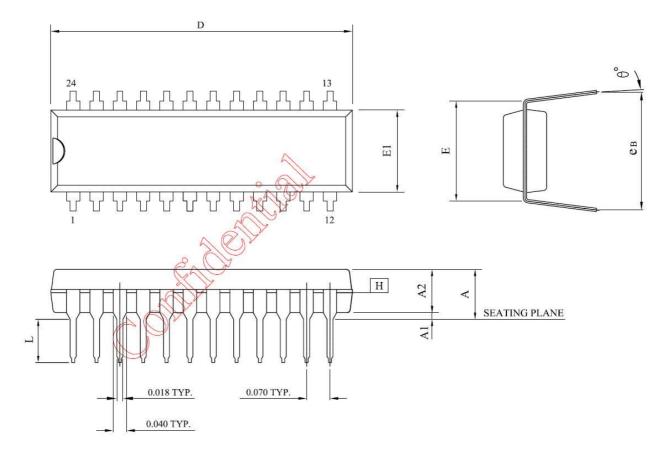

## Title: Package outline for 24 SSOP-236 mil

| Note: | Plating | thickness | spec : | 0.3 | mil~ | 0.8 mil. |   |

|-------|---------|-----------|--------|-----|------|----------|---|

| 5     |         |           |        | 1   |      |          | _ |

| SY<br>UNIT | MBOL | Α    | A1   | A2   | b    | b1   | с    | c1   | D     | e    | E    | Н    | L    | θ° |

|------------|------|------|------|------|------|------|------|------|-------|------|------|------|------|----|

|            | Min. | æ    | 0.05 | 1.30 | 0.30 | 0.30 | 0.10 | 0.10 | 12.80 | 1.00 | 5.80 | 7.70 | 0.25 | 0  |

| mm         | Nom. | =    | 0.10 | 1.50 | 0.40 | 0.40 | 0.15 | 0.15 | 13.00 | 1.00 | 6.00 | 8.00 | 0.45 | æ  |

|            | Max. | 1.90 | 0.15 | 1.70 | 0.52 | 0.50 | 0.27 | 0.25 | 13.20 | BSC  | 6.20 | 8.30 | 0.65 | 10 |

Rev. 1.5

#### Title: Package outline for 24 SSOP-150 mil

#### NOTES:

1.JEDEC OUTLINE : MS-019 AF

2."D","E1" DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH. 3.eB IS MEASURED AT THE LEAD TIPS WITH THE LEADS UNCONSTRAINED.

4.POINTED OR ROUNDED LEAD TIPS ARE PREFERRED TO EASE INSERTION. 5.DISTANCE BETWEEN LEADS INCLUDING DAM BAR PROTRUSIONS TO BE .005 INCH MININUM.

6.DATUM PLANE H COINCIDENT WITH THE BOTTOM OF LEAD, WHERE LEAD EXITS BODY.

7.PLATING THICKNESS : 0.3 ~ 0.8 MIL.

| SY<br>UNIT | MBOL | A     | A1    | A2    | D     | E             | E1    | L     | е <sub>в</sub> | θ°  |

|------------|------|-------|-------|-------|-------|---------------|-------|-------|----------------|-----|

| inch -     | Min. | -     | 0.015 | 0.125 | 0.880 |               | 0.245 | 0.115 | 0.335          | 0°  |

|            | Nom. | -     | 1     | 0.130 | 0.900 | 0.300<br>BSC. | 0.250 | 0.130 | 0.355          | 7°  |

|            | Max. | 0.210 | -     | 0.135 | 0.920 | D3C.          | 0.255 | 0.150 | 0.375          | 10° |

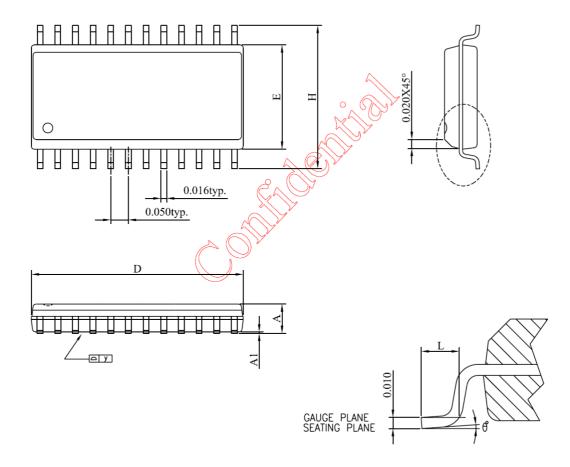

### Title: Package outline for 24L SOP-300mil

| Note: | Plating | thickness | spec | : ( | 0.3 | mil | $\sim$ | 0.8 | mil. |

|-------|---------|-----------|------|-----|-----|-----|--------|-----|------|

|-------|---------|-----------|------|-----|-----|-----|--------|-----|------|

| SYMBOL<br>UNIT |      | А     | <b>A</b> 1 | D     | Е     | Н     | L     | θ° |

|----------------|------|-------|------------|-------|-------|-------|-------|----|

| inch           | Min. | -     | 0.004      | 0.599 | 0.291 | 0.394 | 0.016 | 0  |

|                | Nom. | -     | Ι          | 0.600 | 0.295 | 0.406 | 0.035 | 4  |

|                | Max. | 0.104 | -          | 0.624 | 0.299 | 0.419 | 0.050 | 8  |