### **N-Channel Enhancement MOSFET**

#### **Features**

- Drain-Source Breakdown Voltage V<sub>DSS</sub> 80V

- Drain-Source On-Resistance

R<sub>DS(ON)</sub> 11mΩ, at V<sub>GS</sub>= 10V, I<sub>D</sub>= 40A

- Continuous Drain Current at T<sub>C</sub>=25°C I<sub>D</sub> =55A

- Advanced high cell density Trench Technology

- RoHS Compliance & Halogen Free

# Applications

- DC/DC Converter

- Load Switch

- Power Management

### **Description**

The CTL550NS08-T52 is the N-Channel logic enhancement mode power field effect transistors are produced using high cell density, DMOS trench technology. This high density process is especially tailored to minimize on-state resistance. These devices are particularly suited for low voltage application.

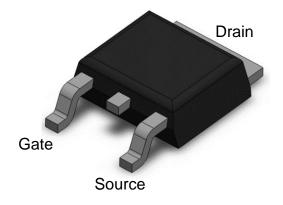

### **Package Outline**

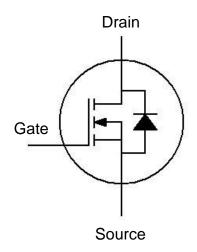

### **Schematic**

# **N-Channel Enhancement MOSFET**

### Absolute Maximum Rating at 25°C

| Symbol | Parameters                           | Test Conditions | Min | Note |

|--------|--------------------------------------|-----------------|-----|------|

| Vos    | Drain-Source Voltage                 | 80              | V   |      |

| Vgs    | Gate-Source Voltage                  | ±20             | V   |      |

| lo     | Continuous Drain Current @Tc=25°C    | 55              | А   | 1    |

| IDM    | Pulsed Drain Current                 | 220             | А   | 1    |

| Po     | Total Power Dissipation @Tc=25°C     | 62.5            | W   | 2    |

| Тѕтс   | Storage Temperature Range            | -55 to 150      | °C  |      |

| TJ     | Operating Junction Temperature Range | -55 to 150      | °C  |      |

### **Thermal Characteristics**

| Symbol | Parameters         | Test Conditions | Min | Тур | Max | Units  | Notes |

|--------|--------------------|-----------------|-----|-----|-----|--------|-------|

| D      | Thermal Resistance |                 |     |     | 2   | 00 444 | 1.4   |

| Rелс   | Junction-Case      |                 |     |     | 2   | °C W   | 1,4   |

# **N-Channel Enhancement MOSFET**

### **Electrical Characteristics** $T_A = 25$ °C (unless otherwise specified)

#### **Static Characteristics**

| Symbol | Parameters                     | Test Conditions              | Min | Тур | Max  | Units | Notes |

|--------|--------------------------------|------------------------------|-----|-----|------|-------|-------|

| Bvdss  | Drain-Source Breakdown Voltage | Vgs= 0V, ID= 250μA           | 80  | -   | -    | V     |       |

| IDSS   | Drain-Source Leakage Current   | VDS = 80V, VGS = 0V          | -   | -   | 1    | μΑ    |       |

| Igss   | Gate-Source Leakage Current    | $Vgs = \pm 20V$ , $Vds = 0V$ | -   | -   | ±100 | nA    |       |

#### **On Characteristics**

| Symbol              | Parameters                    | Test Conditions      | Min | Тур | Max | Units | Notes |

|---------------------|-------------------------------|----------------------|-----|-----|-----|-------|-------|

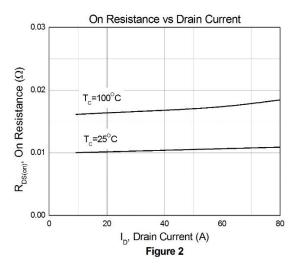

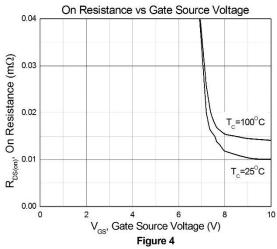

| R <sub>DS(ON)</sub> | Drain-Source On-Resistance    | Vgs = 10V, ID = 40A  | -   | 11  | 13  | mΩ    | 3     |

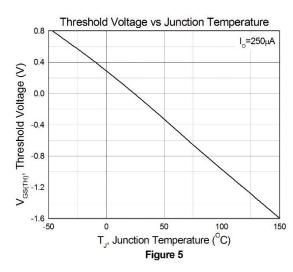

| V <sub>GS(th)</sub> | Gate-Source Threshold Voltage | Vgs = Vds, Id =250µA | 4.0 | -   | 6.5 | V     | 3     |

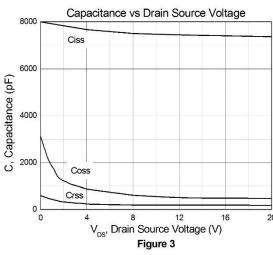

**Dynamic Characteristics**

| Dynamic Grandotorione |                              |                 |     |      |     |       |       |

|-----------------------|------------------------------|-----------------|-----|------|-----|-------|-------|

| Symbol                | Parameters                   | Test Conditions | Min | Тур  | Max | Units | Notes |

| Ciss                  | Input Capacitance            | Vgs =0V,        | -   | 7400 | -   |       |       |

| Coss                  | Output Capacitance           | Vps =20V        | -   | 450  | -   | pF    |       |

| Crss                  | Reverse Transfer Capacitance | f=1MHz          | -   | 140  | -   |       |       |

### **Switching Characteristics**

| Symbol               | Parameters                 | Test Conditions                   | Min | Тур | Max | Units | Notes |

|----------------------|----------------------------|-----------------------------------|-----|-----|-----|-------|-------|

| T <sub>D(ON)</sub>   | Turn-On Delay Time         |                                   | -   | 80  | -   |       |       |

| TR                   | Rise Time                  | $V_{DS} = 30V$ , $R_G = 10\Omega$ | -   | 37  | -   | 20    |       |

| T <sub>D</sub> (OFF) | Turn-Off Delay Time        | $V_{GS} = 10V$ , $RL = 15\Omega$  | -   | 140 | -   | ns    |       |

| TF                   | Fall Time                  |                                   | -   | 27  | -   |       |       |

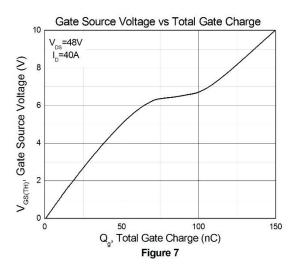

| Q <sub>G</sub>       | Total Gate Charge          | V <sub>DS</sub> = 60V ,           | -   | 120 | -   |       |       |

| Qgs                  | Gate-Source Charge         | $V_{GS} = 10V$ ,                  | -   | 54  | -   | nC    |       |

| Q <sub>GD</sub>      | Gate-Drain (Miller) Charge | I <sub>D</sub> =75A               | -   | 38  | -   |       |       |

### **N-Channel Enhancement MOSFET**

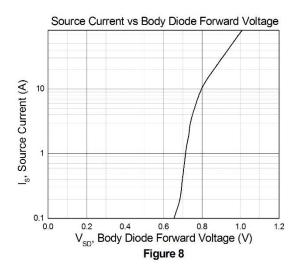

#### **Drain-Source Diode Characteristics**

| Symbol | Parameters                    | Test Conditions    | Min | Тур | Max | Units | Notes |

|--------|-------------------------------|--------------------|-----|-----|-----|-------|-------|

| VsD    | Body Diode Forward Voltage    | Vgs = 0V, Isp = 1A | -   | -   | 1.5 | V     | 1     |

| Isp    | Body Diode Continuous Current |                    | -   | -   | 1   | А     | 1     |

#### Note:

- 1. The power dissipation is limited by 150°C junction temperature.

- 2. The data tested by pulsed , pulse width ≤ 300µs , duty cycle ≤ 2%

- 3. Thermal Resistance follow JESD51-3.

# **N-Channel Enhancement MOSFET**

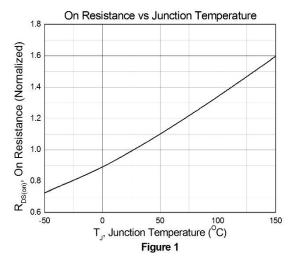

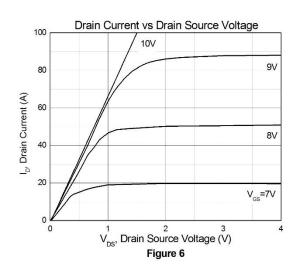

### **Typical Characteristic Curves**

# **N-Channel Enhancement MOSFET**

# **N-Channel Enhancement MOSFET**

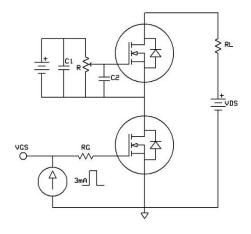

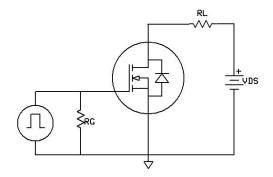

### **Test Circuits & Waveforms**

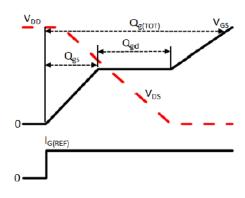

**Figure 9: Gate Charge Test Circuit**

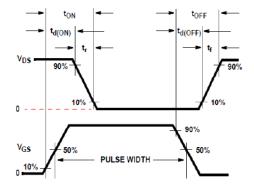

**Figure 11: Switching Time Test Circuit**

Figure 10: Gate Charge Waveform

**Figure 12: Switching Time Waveform**

### **N-Channel Enhancement MOSFET**

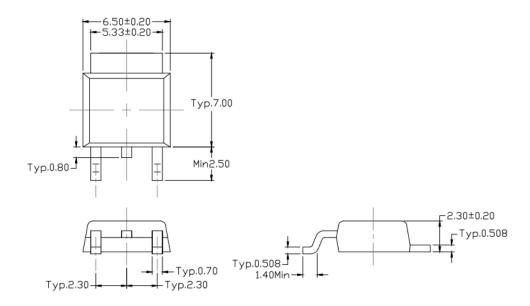

### Package Dimension (TO-252)

Dimensions in mm unless otherwise stated

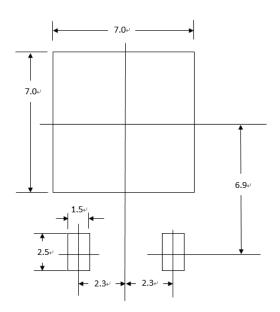

# Recommended pad layout for surface mount leadform

Dimensions in mm unless otherwise stated

# **N-Channel Enhancement MOSFET**

### **Marking Information**

CT : Denotes " CT Micro"

550NS08 : Device Number

Y : Fiscal Year WW : Work Week

A : Production Code

### **Ordering Information**

| Part Number    | Description | Quantity |

|----------------|-------------|----------|

| CTL550NS08-T52 | TO-252 Reel | 2500 pcs |

# **N-Channel Enhancement MOSFET**

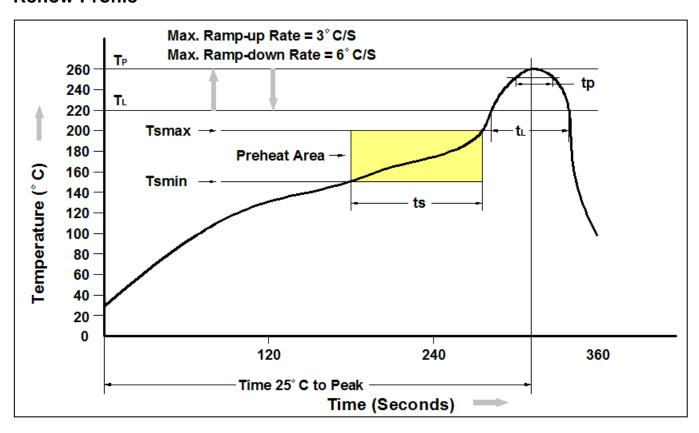

### **Reflow Profile**

| Profile Feature                                           | Pb-Free Assembly Profile |

|-----------------------------------------------------------|--------------------------|

| Temperature Min. (Tsmin)                                  | 150°C                    |

| Temperature Max. (Tsmax)                                  | 200°C                    |

| Time (ts) from (Tsmin to Tsmax)                           | 60-120 seconds           |

| Ramp-up Rate (t∟ to t♭)                                   | 3°C/second max.          |

| Liquidous Temperature (T <sub>L</sub> )                   | 217°C                    |

| Time (t <sub>L</sub> ) Maintained Above (T <sub>L</sub> ) | 60 – 150 seconds         |

| Peak Body Package Temperature                             | 260°C +0°C / -5°C        |

| Time (t <sub>P</sub> ) within 5°C of 260°C                | 30 seconds               |

| Ramp-down Rate (T <sub>P</sub> to T <sub>L</sub> )        | 6°C/second max           |

| Time 25°C to Peak Temperature                             | 8 minutes max.           |

#### **N-Channel Enhancement MOSFET**

#### **DISCLAIMER**

CT MICRO RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. CT MICRO DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

CT MICRO ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT EXPRESS WRITTEN APPROVAL OF CT MICRO INTERNATIONAL CORPORATION.

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instruction for use provided in the labelling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.