www.cellwise-semi.com CW1073-DS V1.6

# CW1073

6~7 battery protection IC

## **Features**

#### ÿOvercharge detection

function • Threshold range 3.750V, 4.175V~4.450V, 25mV step, ± 25mV accuracy©Overdischarge

detection function • Threshold

range 2.100V~3.000V, 100mV step, ± 80mV accuracyÿOvercurrent detection function •

Overcurrent detection 1

Threshold range

0.050V~0.100V, 50mV step,  $\pm$  5mV accuracy• Overcurrent detection 2

Threshold range

0.100V~0.200 V, 100mV step,  $\pm$  5mV accuracy• Short circuit protection

threshold range

0.200V~0.500V, 100mV step, ± 10mV accuracyÿTemperature detection function •

Charging high and low

temperature protection, temperature can be set externally• Discharging high temperature protection,

discharging low

temperature protection optionalÿBalance functionÿAchieve 6 through

SEL terminal 1-cell, 7-cell

battery switch ÿDisconnection detection function ÿLoad detection function

PWM control drive ÿLow

operating current

• Working state 15ÿA (25°C) • Sleep state

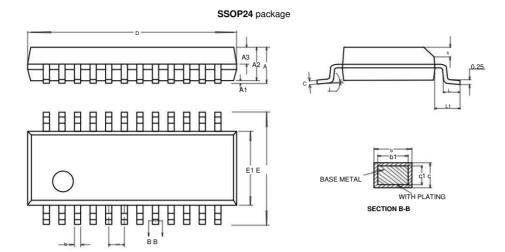

5ÿA (25°C) ÿPackage : SSOP24

# **Application Areas**

ÿPower

toolsÿElectric

bicyclesÿVacuum

cleanersÿLithium - ion and lithium -polymer battery packs

#### **Basic Description**

The CW1073 series is a lithium battery protection chip with built-in highprecision detection circuit and delay circuit, suitable for 6-7 series lithium-ion

batteries or lithium polymer battery packs. It provides overcharge detection, overdischarge detection, over-current detection, balancing, disconnection detection,

and high and low temperature protection for lithium battery packs.

CW1073 has built-in MOSFET driving function and supports external PWM signal to control DO\_PWM terminal output through DCTRL terminal to realize motor speed regulation and soft start function.

© 2017-2019 Cellwise Microelectronics

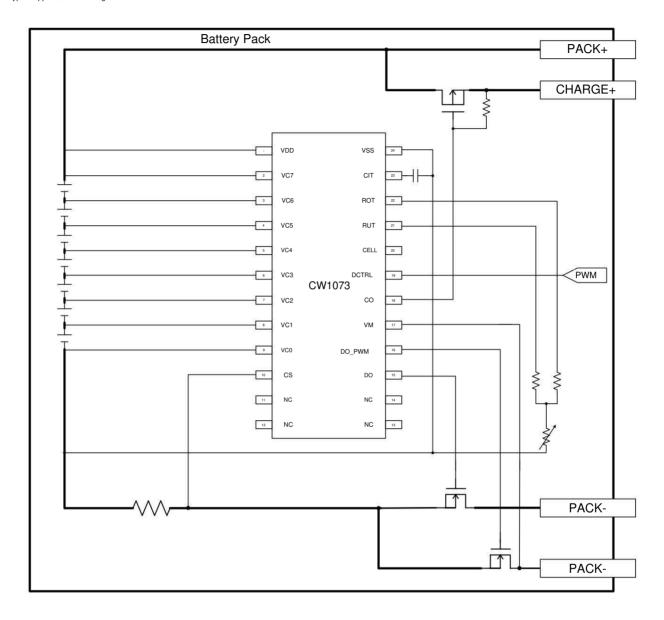

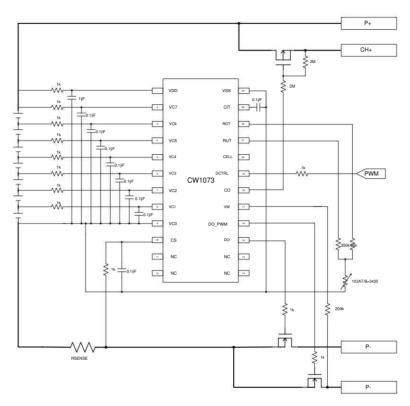

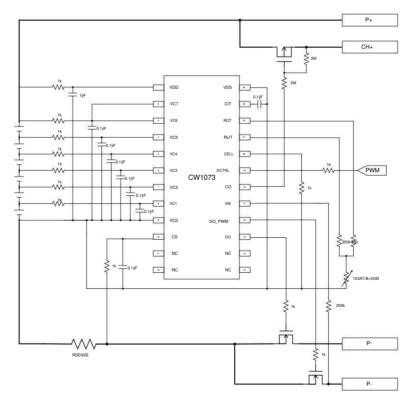

Typical application block diagram

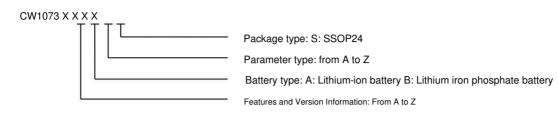

## Product Selection Guide

# Product Catalog

| Product Model | Overcharge threshold [VOC] | Overcharge delay | Overcharge release [VOCR] | Over discharge threshold | Over discharge delay | Over discharge release |

|---------------|----------------------------|------------------|---------------------------|--------------------------|----------------------|------------------------|

| CW1073AAAS    | 4.250V                     | 1s               | 4.150V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AABS    | 4.200V                     | 1s               | 4.100V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AACS    | 4.250V                     | 1s               | 4.150V                    | 2.500V                   | 1s                   | 3.000V                 |

| CW1073AADS    | 4.200V                     | 1s               | 4.100V                    | 2.500V                   | 1s                   | 3.000V                 |

| CW1073AAES    | 4.175V                     | 1s               | 4.075V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073ABCS    | 3.750V                     | 1s               | 3.650V                    | 2.100V                   | 1s                   | 2.400V                 |

| CW1073AAFS    | 4.225V                     | 1s               | 4.125V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AAGS    | 4.175V                     | 1s               | 4.075V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AAJS    | 4.200V                     | 1s               | 4.050V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AAKS    | 4.150V                     | 1s               | 4.000V                    | 2.700V                   | 1s                   | 3.000V                 |

| CW1073AALS    | 4.200V                     | 1s               | 4.050V                    | 2.700V                   | 0.3s                 | 3.000V                 |

| CW1073AAIS    | 4.200V                     | 1s               | 4.100V                    | 2.800V                   | 1s                   | 3.000V                 |

| Product Model | Balance start threshold | Overcurrent 1 threshold | Overcurrent 2 threshold | Short circuit threshold | Discharge low      | Discharge over temperature recovery |

|---------------|-------------------------|-------------------------|-------------------------|-------------------------|--------------------|-------------------------------------|

| Product Model | [VBAL]                  | [VEC1]                  | [VEC2]                  | [VSHR]                  | Thermal protection | Complex load detection              |

| CW1073AAAS    | 4.125V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073AABS    | 4.075V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073AACS    | 4.125V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073AADS    | ·                       | 0.100V                  | 0.200V                  | 0.400V                  | N                  | N                                   |

| CW1073AAES    | 4.050V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073ABCS    | 3.625V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073AAFS    |                         | 0.100V                  | 0.200V                  | 0.400V                  | N                  | N                                   |

| CW1073AAGS    | ·                       | 0.100V                  | 0.200V                  | 0.400V                  | N                  | N                                   |

| CW1073AAJS    | 4.025V                  | 0.100V                  | 0.200V                  | 0.500V                  | N                  | AND                                 |

| CW1073AAKS    | ·                       | 0.050V                  | 0.100V                  | 0.200V                  | N                  | AND                                 |

| CW1073AALS    | 4.025V                  | 0.050V                  | 0.100V                  | 0.200V                  | AND                | AND                                 |

| CW1073AAIS    | 4.075V                  | 0.100V                  | 0.200V                  | 0.500V                  | AND                | N                                   |

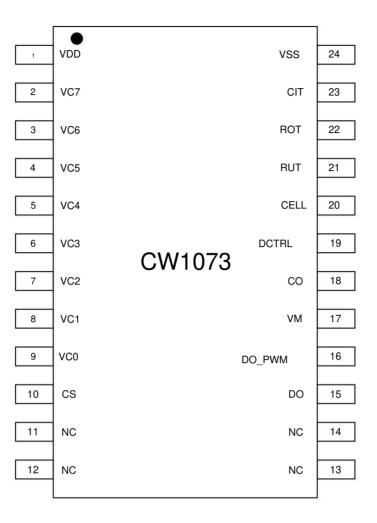

Pin Assignment Diagram

## Pin Definition

| serial number | name | Functional Description                                                                                                                             |

|---------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | VDD  | Chip power supply, connected to the highest potential of the battery pack, if there are 7 batteries, then it is the positive terminal of battery 7 |

| 2             | VC7  | Battery 7 positive terminal                                                                                                                        |

| 3             | VC6  | Battery 6 positive terminal                                                                                                                        |

| 4             | VC5  | Battery 5 positive terminal                                                                                                                        |

| 5             | VC4  | Battery 4 positive terminal                                                                                                                        |

| 6             | VC3  | Battery 3 positive terminal                                                                                                                        |

| 7             | VC2  | Battery 2 positive terminal                                                                                                                        |

| 8             | VC1  | Battery 1 positive terminal                                                                                                                        |

| 9             | VC0  | Battery 1 Negative terminal                                                                                                                        |

| 10            | cs   | Overcurrent detection terminal                                                                                                                     |

| 11            | NC   | No connection                                                                                                                                      |

| 12            | NC   | No connection                                                                                                                                      |

| 13            | NC   | No connection                                                                                                                                      |

| 14            | NC   | No connection                                                                                                                                      |

| 15            | DO   | Discharge protection output terminal, push-pull output, driving NMOS                                                                               |

| 16 | DO_PWM discharge prof | ection output terminal, push-pull output, driving NMOS                |

|----|-----------------------|-----------------------------------------------------------------------|

| 17 | VM                    | P-terminal voltage detection terminal                                 |

| 18 | со                    | Charging protection output terminal, open drain output, driving PMOS  |

| 19 | DCTRL                 | DO_PWN control terminal, PWM signal input                             |

| 20 | CELL                  | 6-cell and 7-cell battery selection terminals                         |

| 21 | RUT                   | Low temperature detection terminal                                    |

| 22 | ROT                   | Over temperature detection terminal                                   |

| 23 | CIT                   | Overcurrent delay setting terminal                                    |

| 24 | VSS                   | Chip ground terminal, connected to the negative terminal of battery 1 |

## Absolute Maximum Ratings

|                        | sco                            |           |         |    |

|------------------------|--------------------------------|-----------|---------|----|

|                        |                                | Minimum M | unit    |    |

| Terminal input voltage | VDDÿVMÿCOÿSELÿCSÿDCTRL VSS-0.3 |           | VSS+40  | V  |

| Terminal input voltage | ROOTÿROOTÿCIT                  | VSS-0.3   | 6       | V  |

| Terminal input voltage | VCXÿDOÿDO_PWM                  | VSS-0.3   | VDD+0.3 | V  |

| Operating temperature  | Т1                             | -30       | 85      | °C |

| Storage temperature    | T2                             | -40       | 125     | °C |

Note: Absolute maximum ratings are the ratings that cannot be exceeded under any conditions. If these ratings are exceeded, product damage may occur. hurt.

## **ESD** Level

|                      |                  |          | Parameter Value | unit |

|----------------------|------------------|----------|-----------------|------|

|                      |                  | HBM Mode | ±4000           | V    |

| V(ESD) level electro | static discharge | CDM Mode | ±1000           | V    |

# Rated operating voltage

| describe               | project          | Min Typ M | ax Unit |      |   |

|------------------------|------------------|-----------|---------|------|---|

| VDD Input Voltage      | VDD              | 4         |         | 31.5 | V |

| VCX input voltage      | VCX              | 0         |         | 4.5  | V |

| Terminal input voltage | VCITÿWANTÿWANTED | 0         | 9       | 5    | V |

Electrical characteristics

## Unless otherwise specified, T=25°C

|                                                     | 1                   | <b>-</b>                         |             |                     |        |    |

|-----------------------------------------------------|---------------------|----------------------------------|-------------|---------------------|--------|----|

| describe                                            | project             | Test conditions                  | Min Typ Max | Unit                |        |    |

| power supply                                        | ×                   |                                  | ×           |                     |        |    |

| Normal operating current                            | IOPR VC1=           | /C2=VC3=VC4=VC5=VC6=VC7=3.7V     |             | 15                  | 20     | ÿA |

| Sleep current                                       | ISLEEP VC1=         | VC2=VC3=VC4=VC5=VC6=VC7=2.0V     |             |                     | 5      | ÿA |

| Channel input current                               | ICELL VC1=          | VC2=VC3=VC4=VC5=VC6=VC7=3.7V     |             |                     | 0.5    | ÿA |

| Voltage, temperature detection and prote            | ection thresholds   |                                  | · ·         |                     |        |    |

|                                                     | VOC* 1              | VC1=VC2=VC3=VC4=VC5=VC6=3.7V     | VOC -       | VOC                 | VOC +  | ٧  |

| Overcharge detection voltage                        | VOC 1               | VC7=3.7Vÿ4.5V                    | 0.025       | VOC                 | 0.025  | V  |

|                                                     | VOOR                | VC1=VC2=VC3=VC4=VC5=VC6=3.7V     | VOCR -      | VOOD                | VOCR + | ٧  |

| Overcharge release voltage                          | VOCR                | VC7=4.5Vÿ3.7V                    | 0.030       | VOCR                | 0.030  | V  |

|                                                     |                     | VC1=VC2=VC3=VC4=VC5=VC6=3.7V     | VOD-        |                     | VOD+   | ., |

| Over discharge detection voltage                    | VOD                 | VC7=3.7Vÿ2.0V                    | 0.080       | VOD                 | 0.080  | V  |

|                                                     | V-5-                | VC1=VC2=VC3=VC4=VC5=VC6=3.7V     | V.O.D.R     | V = 5 =             | VODR + | v  |

| Over discharge release voltage                      | V.O.D.R.            | VC7=2.0ÿ3.7V                     | 0.100       | V.O.D.R.            | 0.100  | V  |

|                                                     |                     | VC1=VC2=VC3=VC4=VC5=VC6=3.7V     | VBAL-       |                     | VBAL+  | V  |

| Balanced starting voltage                           | VBAL                | VC7=3.7Vÿ4.4V                    | 0.025       | VBAL                | 0.025  |    |

|                                                     |                     | VC1=VC2=VC3=VC4=VC5=VC6=VC7=3.7V | VEC1-       |                     | VEC1+  |    |

| Overcurrent 1 detection voltage                     | VEC1                | CS=0ÿ0.15V                       | 0.005       | VEC1                | 0.005  | V  |

|                                                     |                     | VC1=VC2=VC3=VC4=VC5=VC6=VC7=3.7V | VEC2-       |                     | VEC2+  | V  |

| Overcurrent 2 detection voltage                     | VEC2                | CS=0ÿ0.3V                        | 0.005       | VEC2                | 0.005  |    |

|                                                     |                     | VC1=VC2=VC3=VC4=VC5=VC6=VC7=3.7V | VSHR-       | insulated wire mesh | VSHR + | V  |

| Short circuit detection voltage                     | insulated wine mesh | CS=0ÿ0.6V                        | 0.010       |                     | 0.010  |    |

| Charging over-temperature detection tem             | erature TCOT* 2     | VDD=25.9V,NTC=103AT B=3435       | тсот-з      | TCOT TCO            | Г+3    | °C |

| Charging over-temperature protection release delay  |                     |                                  |             |                     |        |    |

| Hysteresis Temperature                              | TCOTR               |                                  |             | 5                   |        | °C |

| Discharge over-temperature detection tem            | perature TDOT* 2    | VDD=25.9V,NTC=103AT B=3435       | TDOT-3      | TDOT                | TDOT+3 | °C |

| Discharge over-temperature protection release delay |                     |                                  |             |                     |        | _  |

| Hysteresis Temperature                              | TDOTR               |                                  |             | 5                   |        | °C |

| Charging low temperature detection temperature      | TCUT                | VDD=25.9V,NTC=103AT B=3435       | TCUT-3      | TCUT TCU            | T+3    | °C |

| Charging low temperature protection release delay   |                     |                                  |             | _                   |        |    |

| Hysteresis Temperature                              | TCUTR               |                                  |             | 5                   |        | °C |

| Discharge low temperature detection temperature     | TDUT                | VDD=25.9V,NTC=103AT B=3435       | TDUT-3      | TDUT TDU            | T+3    | °C |

| Discharge low temperature protection release delay  |                     |                                  |             |                     | ,      |    |

| Hysteresis Temperature                              | TDUTR               |                                  |             | 5                   |        | °C |

| DCTRL terminal high level input                     |                     |                                  |             |                     | ,      |    |

| Input voltage                                       | VCTRLH              |                                  | 2.5         |                     |        | V  |

| DCTRL terminal low level input                      |                     |                                  |             |                     | >      |    |

| Input voltage                                       | VCTRLL              |                                  |             |                     | 1      | V  |

| Discharge state judgment voltage V                  | DCH                 |                                  | 2           | 3.5                 | 5      | mV |

| Wire break judgment voltage                         | VOW                 |                                  | 20          | 50                  | 100 mV |    |

|                                                     |                     |                                  | L           |                     |        |    |

| describe                                            | project      | Test conditions                               | Min Typ Ma  | x Unit |             |    |  |  |

|-----------------------------------------------------|--------------|-----------------------------------------------|-------------|--------|-------------|----|--|--|

| Load detection voltage                              | VLD          |                                               |             | 2      |             | ٧  |  |  |

| Delay time                                          | Delay time   |                                               |             |        |             |    |  |  |

| Overcharge protection delay                         | TOC          | VC1=VC2=VC3=VC4=VC5=VC6=3.7V<br>VC7=3.7Vÿ4.5V | 0.8*<br>TOC | TOC    | 1.2*<br>TOC | s  |  |  |

| Overcharge protection reset delay TRE               | SET SET      |                                               | 1           | 2.5    | 4           | ms |  |  |

| Overcharge protection release delay                 | TOCR         | VC1=VC2=VC3=VC4=VC5=VC6=3.7V<br>VC7=4.5Vÿ3.7V | 150         | 200    | 250         | ms |  |  |

| Over discharge protection delay                     | TOD          | VC1=VC2=VC3=VC4=VC5=VC6=3.7V<br>VC7=3.7Vÿ2.0V | 0.7*<br>TOD | TOD    | 1.3*<br>TOD | s  |  |  |

| Over discharge protection release delay             | TODR         | VC1=VC2=VC3=VC4=VC5=VC6=3.7V<br>VC7=2.0Vÿ3.7V | 150         | 200    | 360         | ms |  |  |

| Balanced start delay                                | TBAL         | VC1=VC2=VC3=VC4=VC5=VC6=3.7V<br>VC7=3.7Vÿ4.5V |             |        | 64          | ms |  |  |

| Balanced off delay                                  |              |                                               |             |        | 64          | ms |  |  |

| Overcurrent 1 protection delay                      | TEC1         | CIT connects to a 0.1ÿF capacitor             | 0.7         | 1      | 1.3         | s  |  |  |

| Overcurrent 2 protection delay                      | TEC2         | CIT connects to a 0.1ÿF capacitor             | 60          | 100    | 140         | ms |  |  |

| Short circuit protection                            | TSHORT       |                                               | 180         | 240    | 300         | ÿs |  |  |

| delay Overcurrent release delay                     | TECR* 3      |                                               | 90          | 120    | 150         | ms |  |  |

| Load lock state release delay TLLR                  |              | VC1=VC2=VC3=VC4=VC5=VC6=VC7=3.7V<br>VMÿVLD    | 5           | 10     | 16          | ms |  |  |

| Sleep delay                                         | TSLP         |                                               | 25          | 30     | 40          | s  |  |  |

| charging over temperature protection delay          | тсот         |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Charging over-temperature protection release delay  | TCOTR        |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Discharge over-temperature protection delay         | TDOT         |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Discharge over-temperature protection release delay | TDOTR        |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Charging low temperature protection delay           | TCUT         |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Charging low temperature protection release delay   | TCUTR        |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Discharge low temperature protection d              | elay TDUT    |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Discharge low temperature protection release delay  | TDUTR        |                                               | 0.8         | 1.5    | 2           | s  |  |  |

| Disconnection detection delay                       | TOW input ca | pacitance = 0.1ÿF                             |             | 1      |             | s  |  |  |

| Disconnection recovery delay                        | TOWR         |                                               |             | 6      |             | s  |  |  |

| Discharge state detection delay TDCH                |              |                                               | 3           | 5      | 10          | ms |  |  |

| <b>0V</b> charging function                         |              |                                               |             |        |             |    |  |  |

| 0V charging start voltage                           | V0V          |                                               | 1.5         |        |             | ٧  |  |  |

| VM terminal                                         |              |                                               |             |        |             |    |  |  |

| Resistance between VM and VSS RVM                   | vss          |                                               | 30          | 50     | 80          | kÿ |  |  |

| describe                     | project            | Test conditions                  | Min Typ Max | Unit  |   |    |  |  |

|------------------------------|--------------------|----------------------------------|-------------|-------|---|----|--|--|

| Pin output voltage           | Pin output voltage |                                  |             |       |   |    |  |  |

| CO logic low output          | CO*4               |                                  |             | VSS   |   | ٧  |  |  |

| Voltage                      | CO 4               |                                  |             | V33   |   | V  |  |  |

| DO logic high output         |                    | VDD>=11V                         |             | 10.6  | 5 | ٧  |  |  |

| Voltage                      |                    | VDD>=11V                         |             | 10.0  |   | V  |  |  |

| DO logic high output         | DO                 | VDD<11V                          |             | VDD - |   | V  |  |  |

| Voltage                      | DO                 | VDD<11V                          |             | 0.7   |   | V  |  |  |

| DO logic low output          |                    |                                  |             | vss   |   | ٧  |  |  |

| Voltage                      |                    |                                  |             | V33   |   | •  |  |  |

| DO_PWM logic high            |                    | VDD>=11V                         |             | 10.6  |   | V  |  |  |

| Flat output voltage          |                    | 1557-111                         |             |       |   | •  |  |  |

| DO_PWM logic high            | DO_                | VDD<11V                          |             | VDD - |   | V  |  |  |

| Flat output voltage          | PWM                | VBBNIIV                          |             | 0.7   |   | •  |  |  |

| DO_PWM logic low             |                    |                                  | Ĭ           | VSS   |   | V  |  |  |

| Flat output voltage          |                    |                                  |             | 100   |   | •  |  |  |

| Drive current* 5             |                    |                                  |             |       |   |    |  |  |

|                              | CO                 | CO terminal logic high level     |             | -     |   | ÿA |  |  |

| CO terminal output current   |                    | CO terminal logic low level      |             | 10    |   | ÿA |  |  |

|                              | DO                 | DO terminal logic high level     |             | 70    |   | ÿA |  |  |

| DO terminal output current   | DO                 | DO terminal logic low level      |             | -680  |   | ÿA |  |  |

| DO_PWM terminal              | DO_PWM terminal    |                                  |             |       |   |    |  |  |

| DO_PWM Pull-up resistor DO_  |                    | DO_PWM terminal logic high level |             | 3.7   |   | kÿ |  |  |

| DO_PWM pull-down resistor *1 | PWM                | DO_PWM terminal logic low level  |             | 700   |   | Oh |  |  |

For detailed protection threshold selection, please refer to the selection guide table

<sup>12</sup> The charging over-temperature protection temperature protection temperature defeated to the charging over-temperature protection temperature protection tempe

If the over-temperature protection temperature is 50y, the over-temperature protection temperature for discharge is 70y; the low-temperature protection temperature setting for charge and discharge is consistent with the high-temperature setting for charge and discharge;

<sup>\*3</sup> All over-current protection (including over-current 1, over-current 2 and short-circuit protection) release delay time is 120ms

<sup>\*4</sup> The output high level of the CO terminal is high impedance state.

<sup>\*5</sup> The external voltage source for the CO and DO terminal output current test is 0.5V

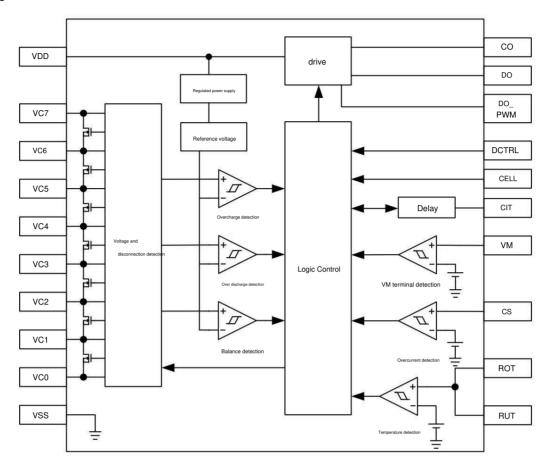

# Block Diagram

11

#### Functional Description

#### Normal state

All battery voltages are between the overcharge detection voltage (VOC) and the overdischarge detection voltage (VOD), the battery temperature is within the operating range, and CS

When the terminal voltage is lower than the overcurrent detection voltage (VEC1), CW1073 is in normal working state. Overcharge state

Under normal conditions, if the voltage of any battery cell is higher than the overcharge detection voltage (VOC) and exceeds the overcharge protection delay time (TOC), CO

The terminal outputs a high impedance state to turn off the charging MOSFET and stop charging.

During the overcharge protection delay time (TOC), if the detected battery voltage is lower than the overcharge detection voltage (VOC) for a period longer than the overcharge reset delay time

(TRESET), the accumulated overcharge delay time (TOC) is reset. Otherwise, the drop in battery voltage is considered as irrelevant interference and is shielded.

Overcharge protection release condition:

All battery voltages are lower than the overcharge release voltage (VOCR) and exceed the overcharge release delay time (TOCR).

#### Over discharge state

Under normal conditions, if the voltage of any battery is lower than the over-discharge protection voltage (VOD) and exceeds the over-discharge protection delay time (TOD), the DO terminal

The DO PWM terminal outputs a low level to turn off the discharge MOSFET and stop discharging. Over-discharge protection

release conditions: VM terminal voltage is

lower than 2V (load release), all battery voltages are higher than the over-discharge release voltage (VODR) and maintain for more than the over-discharge release delay time.

Time (TODR).

#### Overcurrent status

CW1073 has three levels of built-in overcurrent detection, overcurrent 1, overcurrent 2 and short circuit protection.

Protection mechanism: The voltage of the current sampling resistor on the main circuit is detected through the CS terminal to determine whether CW1073 enters the corresponding overcurrent protection state.

Taking

overcurrent 1 protection as an example, the discharge current changes with the external load. If the CS terminal detects that the voltage on the current sampling resistor is higher than the overcurrent 1 protection threshold (VEC1) and maintains more than the overcurrent 1 protection delay time (TEC1), the DO terminal and DO\_PWM terminal output low level to turn off the discharge MOSFET and stop discharging. Overcurrent protection release condition: The VM terminal

voltage is lower than 2V (load release) and

exceeds the overcurrent release delay time (TECR), and the overcurrent protection is released.

Temperature protection function

CW1073 uses an NTC resistor to achieve charge and discharge over-temperature protection and charge and discharge low-temperature protection functions. The ROT and RUT terminals detect the NTC resistor voltage. If the detection voltage reaches the internal comparison threshold and maintains the charge and discharge temperature protection delay time, the temperature protection function is triggered.

After the charging temperature protection, the charging MOSFET is turned off and charging stops; After

the discharging temperature protection, the discharging MOSFET is turned off and discharging stops;

Charging temperature protection release

condition: The temperature returns to within the charging release temperature, and the time exceeds the charging temperature release delay, the charging temperature

protection is released. Discharging temperature

protection release condition: 1. The chip has a temperature protection recovery load lock function: The VM terminal voltage is lower than 2V (load release), the temperature returns to within the discharge release

temperature, and the time exceeds the discharge temperature release delay, the discharge temperature protection is

released. 2. The chip does not have a temperature protection recovery load lock function: The temperature returns to within the discharge release temperature, and the time exceeds the discharge temperature release delay

When the discharge temperature protection is

released. Over-temperature threshold

setting steps 1. Select the NTC resistor. The recommended NTC resistor model for CW1073 is: 103AT, B=3435;  $\frac{1}{2} \left( \frac{1}{2} \right) \left( \frac{1}{2}$

2. Determine the charge over-temperature protection threshold, such as

50°C; 3. According to the temperature curve of the NTC resistor, find the resistance value corresponding to 50°C, such as 3.5kÿ; 4. Use a

normal resistor with 10 times the resistance to connect to the ROT terminal, that is, 35kÿ; 5. After determining the

charge over-temperature protection threshold, the discharge over-temperature protection threshold defaults to  $50^{\circ}\text{C} + 20^{\circ}\text{C} = 70^{\circ}\text{C}$ ; 6. The charge low-

temperature protection setting uses the same method, but the resistor needs to be connected to the RUT terminal; 7. Please refer

to the application circuit for detailed circuits, and set the appropriate protection temperature by selecting resistors;

CW1073 has an optional discharge low temperature protection function. The default discharge low temperature protection temperature setting is the charge low temperature protection temperature of -20%

#### Low power state

CW1073 enters the over-discharge protection state and exceeds the sleep delay time (TSLP), then CW1073 enters the low power state. DO terminal

Keep low level to keep the discharge MOSFET off; keep CO terminal low level to keep the charge MOSFET on. Sleep state release condition: the battery voltage is higher than the

over-discharge release voltage

(VODR) and lasts longer than the over-discharge release delay time (TODR).

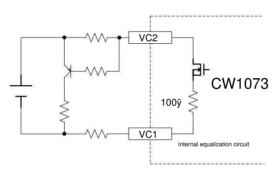

#### Equalization function

CW1073 has built-in balancing function, internal balancing resistor is 100ỹ, and balancing current is adjusted by external voltage sampling resistor.

The sample resistance is 200ỹ~1kỹ. If large current balancing is required, an external balancing circuit can be added to expand the current. The balancing current is determined by the external balancing resistor.

Equalization function diagram

Under normal conditions, if the voltage of any cell is higher than the balancing detection voltage (VBAL) and the voltage of the other cells is lower than the balancing detection voltage (VBAL), and the balancing start delay time (TBAL) is exceeded, CW1073 starts balancing. Balancing stop conditions: 1.

All cell voltages are lower

than the balancing detection voltage (VBAL). 2. All cell voltages are higher than the

balancing detection voltage (VBAL).

3. CW1073 enters the disconnection protection state, discharge temperature protection state, and low power consumption state.

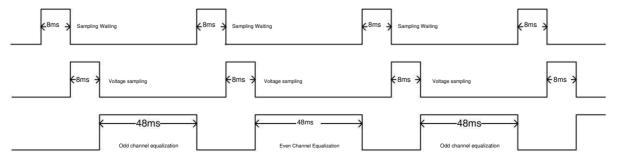

CW1073 uses odd-even channel time-sharing balancing. The balancing function does not affect the normal battery voltage sampling. When multiple balancing channels are turned on at the same time, the odd channels will enter the balancing state first, and the even channels will enter the balancing state in the next cycle. The specific battery voltage sampling and balancing start timing diagram is as follows:

Voltage sampling and balancing start timing diagram

Line break protection function

CW1073 includes disconnection detection and protection functions.

Under normal conditions, when the detection line of any battery in the battery pack is disconnected and maintained for more than the disconnection detection delay (TOW), the DO terminal and DO\_PWM terminal output low level to turn off the discharge MOSFET; CO output high impedance to turn off the charging MOSFET; CW1073 enters the disconnection protection state. Conditions for releasing the

disconnection protection state: VM terminal

voltage is lower than 2V (load release), the detection line is reconnected, and maintained for more than the disconnection release delay (TOWR), the disconnection protection state is released.

#### **0V** charging (allowed)

CW1073 supports the battery 0V charging function, that is, when the battery voltage is lower than the normal operating voltage of the chip, the battery pack can be charged normally.

The VDD voltage of CW1073 is higher than the 0V charging start voltage (VOV), a charger is connected and the charger output voltage is higher than the charging MOSFET

The battery pack starts charging after the threshold

is turned on. Delay time setting

The delay time refers to the time from when CW1073 detects that the voltage reaches the set protection threshold to when CW1073 drives the CO or DO terminal to output high or low.

The overcurrent 1 and overcurrent 2 protections of CW1073 can be set with external capacitors to set the delay time.

String number selection

catch;

The SEL terminal is the battery series number selection terminal, which can be used to select the number of batteries connected in series.

If the SEL terminal is connected to the ground with a resistor in series, the number of battery strings protected by CW1073 is 6. When 6 battery strings are used, the VC7 terminal and the VC6 terminal are shorted.

If the SEL terminal is left unconnected, the number of battery strings protected by CW1073 is 7;

Discharge status detection function

In the application of charging and discharging at the same port, the battery pack is in the overcharge and charging temperature protection state. If the CS terminal detection voltage is higher than 3.5mV and the discharge state detection delay (TDCH) continues, the battery pack is considered to be in the discharge state, and the CO terminal outputs a low level to turn on the charging MOSFET.

## PWM control drive

CW1073 has built-in MOS drive function, supports external PWM signal to control DO\_PWM terminal output through DCTRL terminal, DCTRL terminal input voltage is higher than 2.5V,

DO\_PWM terminal outputs low level; DCTRL terminal input voltage is lower than 1V, DO\_PWM terminal outputs high level. When external signal is not needed to control DO\_PWM terminal, DCTRL terminal series resistor is grounded;

When the internal protection state of the CW1073 chip occurs, such as over-discharge, over-current, discharge over-temperature and disconnection protection, the chip protection action will be executed first.

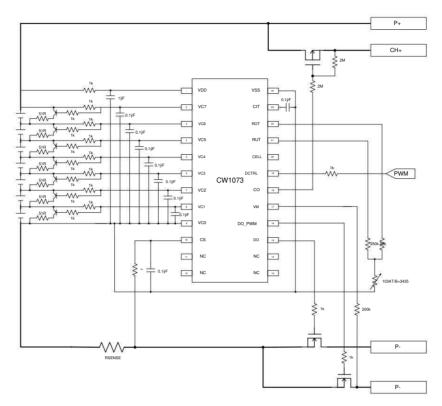

## Reference Application Circuit

7- string application circuit with equalization function

7- string application circuit with equalization function

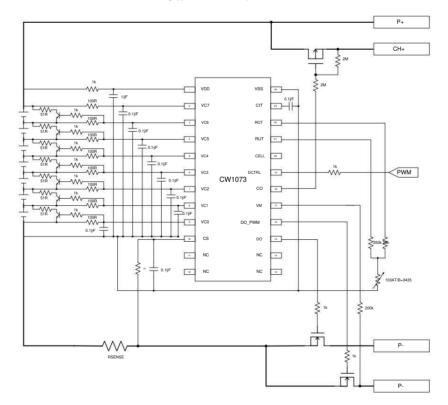

## Reference Application Circuit

7 -string application circuit without equalization function

6 -string application circuit without equalization function

Package Drawing and Package Dimensions

| OVERDO | MILLIMETER |          |      |  |  |

|--------|------------|----------|------|--|--|

| SYMBOL | MIN.       | NAME.    | MAX. |  |  |

| А      |            |          | 1.75 |  |  |

| A1     | 0.10       | 0.15     | 0.25 |  |  |

| A2     | 1.30       | 1.40     | 1.50 |  |  |

| A3     | 0.60       | 0.65     | 0.70 |  |  |

| b      | 0.23       |          | 0.31 |  |  |

| b1     | 0.22       | 0.25     | 0.28 |  |  |

| С      | 0.20       | ****     | 0.24 |  |  |

| c1     | 0.19       | 0.20     | 0.21 |  |  |

| D      | 8.55       | 8.65     | 8.75 |  |  |

| AND    | 5.80       | 6.00     | 6.20 |  |  |

| E1     | 3.80       | 3.90     | 4.00 |  |  |

| and    |            | 0.635BSC |      |  |  |

| h      | 0.30       |          | 0.50 |  |  |

| L      | 0.50       |          | 0.80 |  |  |

| L1     | 1.05REF    |          |      |  |  |

| ÿ      | 0          | 80.000   | 8°   |  |  |

## Version History

| Date Version |             | Modify Project                                                                                                                                                                                     | Modify             | approve    |

|--------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------|

| 2017-08-25   | 1.0 New ver | sion of the manual released                                                                                                                                                                        | Zeng               | Zhou Jun   |

| 2018-01-25   | 1.1 Added C | W1073AACS model 1.2 Added CW1073AADS                                                                                                                                                               | Kang               | Zhou Jun   |

| 2018-06-29   | model       |                                                                                                                                                                                                    | Zeng Kang Zeng Kan | g Zhou Jun |

| 2018-08-14   | 1.3         | Added CW1073AAES model     Modify CW1073AADS parameters     Modify the discharge over-temperature recovery condition and the description of the balancing function     Added ESD level description | Zeng Kang          | Zhou Jun   |

| 2018-11-26   | 1.4         | Modify the reference application circuit     Increase the upper and lower limits of parameters     Add PWM control instructions                                                                    | Zeng Kang          | Zhou Jun   |

| 2019-01-14   | 1.5 Added C | W1073AAFS, CW1073AAGS models 1.6 1. Added CW1073AAJS, AAKS,                                                                                                                                        | Zeng Kang          | Zhou Jun   |

| 2019-06-18   | AAIS produ  | at models  2. Adjust the over-discharge delay accuracy                                                                                                                                             | Zeng Kang          | Zhou Jun   |

## statement

To improve the reliability, function or design of the product, Saiwei Microelectronics reserves the right to make changes without prior notice.

Saiwei Microelectronics Co., Ltd. does not assume any responsibility for any problems arising from the application of any product or circuit described in this document; it does not transfer any No license or other rights are conveyed.

Without the formal written authorization of the President of Siwei Microelectronics, its products may not be used as critical components in life support devices or systems.

The details are as follows:

1. Life support devices or systems are devices or systems that

System: (a) intended for surgical implantation in the human body, or (b)

sustain or maintain life, and even if used according to the instructions

Follow the instructions to perform the correct operation, but if the operation fails,

Will cause serious harm to the user.

2. Critical components refer to those components in life support equipment or systems.

Failure of this device can lead to the failure of the entire life support device

or system failure, or affect its safety and use

Effect.

© 2017-2019 Cellwise Microelectronics