# CW2217BAAD

## Fuel Gauge IC with Current Sensing

### Features

- System-Side or Pack-Side Fuel Gauging

- High C-Rate Charging Compliance

- High precision ADCs for Voltage, Current and Temperature Measurement

- High Side or Low Side Current Sensing

- Support Low to 1mOhm Sense Resistor

- External Thermistor or Host Reported Temperature

- Battery Voltage, Current, Temperature, SOC, and Cycle Count Report

- No Offset Accumulation during Life Time

- No Full-To-Empty Calibration Cycles Required

- Interrupt for SOC, Temperature and 1% SOC Change

- Ultra-low Power Consumption

- Active Mode 12 $\mu$ A

- Shutdown Mode 0.5 $\mu$ A

- General I<sup>2</sup>C Control Interface

- Lead-Free, DFN-12 Package

### Applications

- Power Banks

- Tablets and Laptops

- Power Tools

- Li+ Battery Pack

### General Description

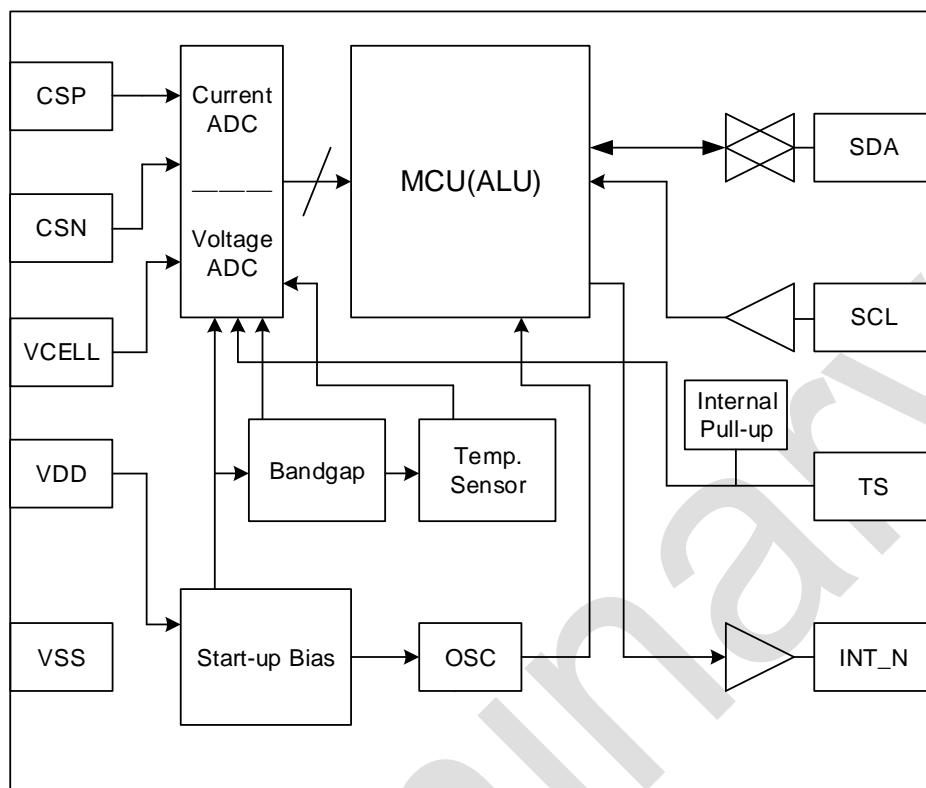

The CW2217 is an ultra-compact, system-side or pack-side fuel gauging IC for Lithium-ion based batteries used in wearable and portable devices. The CW2217 tracks battery operating conditions and performs state-of-the-art algorithm to calculate the State-of-Charge (SOC) of various battery chemistry systems, including LiCoO<sub>x</sub>, polymer Li-ion and LiMnO<sub>x</sub> etc.

The CW2217 includes two high precision ADCs, voltage reference circuits and build-in NTC thermistor bias circuits. It continually monitors the battery voltage and temperature and measures the current flow through the sense resistor. All the measurements and the battery characterization data are utilized by the IC embedded FastCali algorithm and accurate battery SOC is reported and refreshed in a wide variety of operating conditions.

The CW2217 also provides alarm functions. When SOC or temperature reaches the pre-programmed threshold, the relevant interrupt will be generated to alert the host MCU.

The CW2217 use a 2-wire I<sup>2</sup>C compatible serial interface that operates in standard mode or fast mode. The CW2217BAAD is available in Lead-free 2.5mmx4mm, 12-lead DFN package.

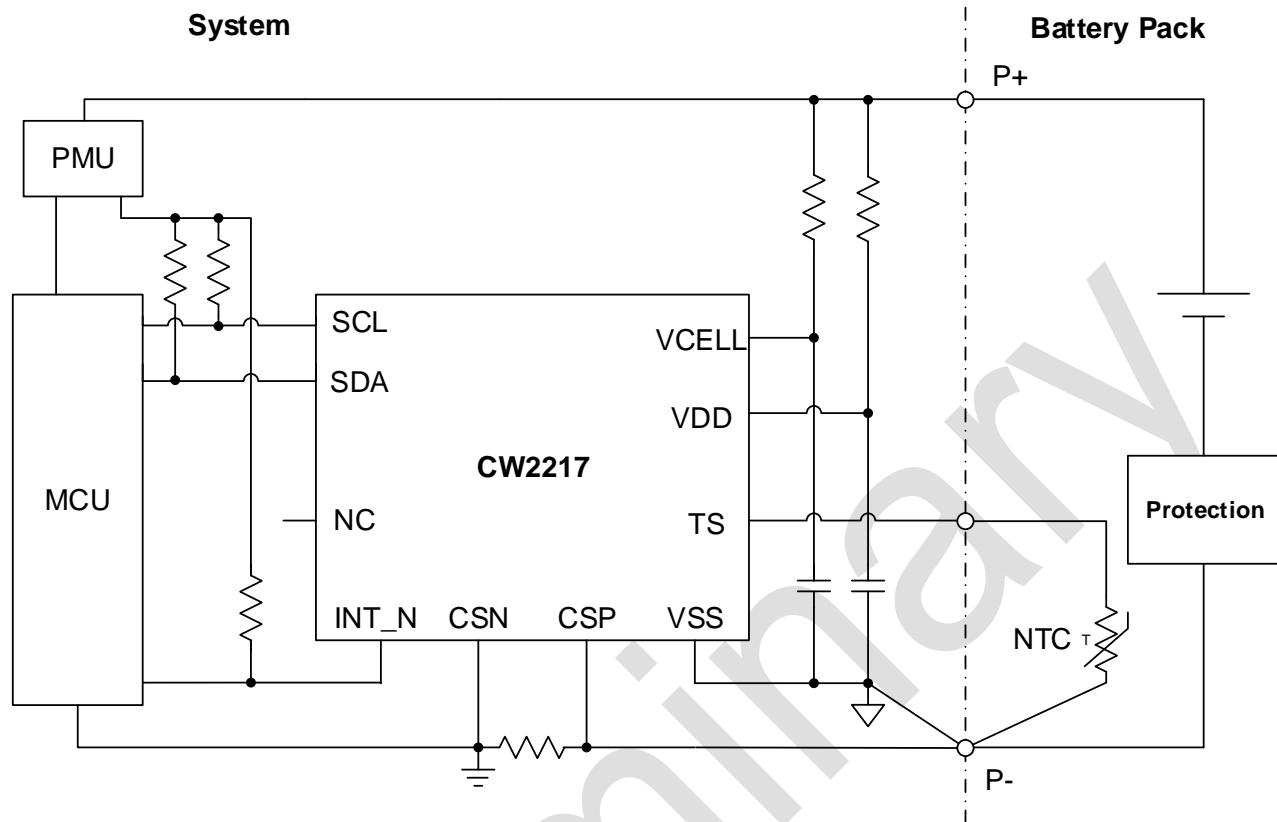

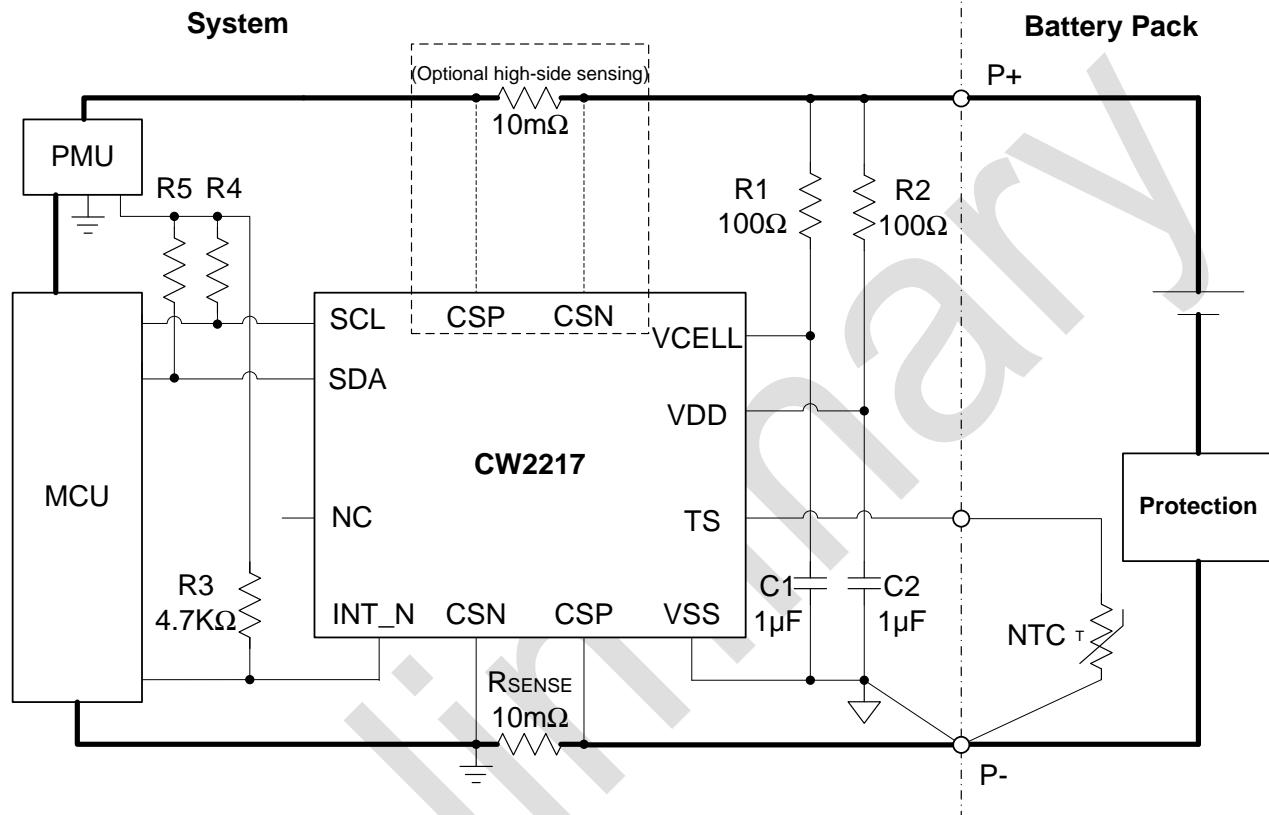

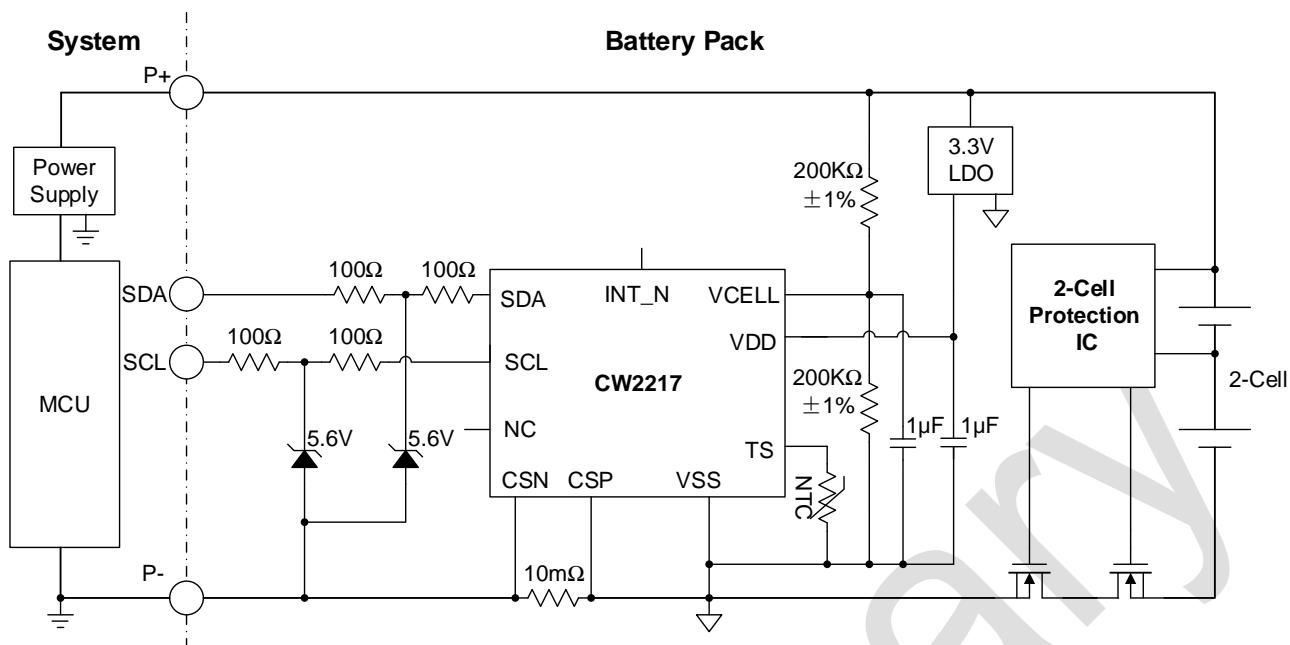

## Typical Application

Figure 1. Typical Application for Single Cell

## Ordering Information

| PART       | I <sup>2</sup> C ADDRESS | OPERATING TEMPERATURE | PACKAGE | SIZE        | TOP MARK         |

|------------|--------------------------|-----------------------|---------|-------------|------------------|

| CW2217BAAD | 0x64                     | -40°C to 85°C         | DFN-12  | 2.5mmx4.0mm | 2217BA<br>ADXXXX |

Note: XXXX stands for manufacture info. Contact manufacturer for details.

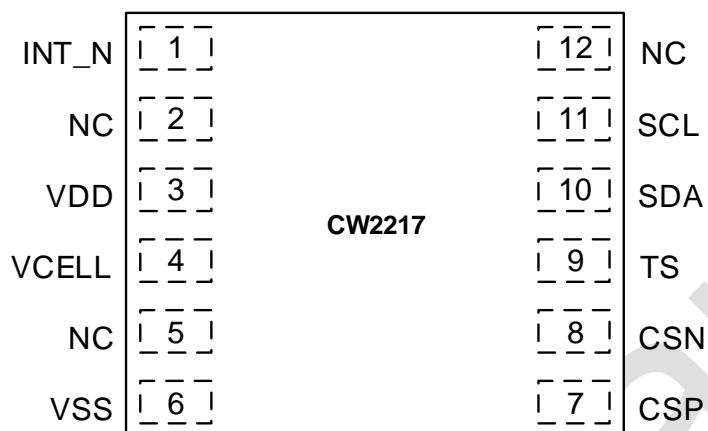

## Pin Configuration

Package DFN-12

Top view

## Pin Descriptions

| PIN      | NAME  | DESCRIPTION                                                  |

|----------|-------|--------------------------------------------------------------|

| 3        | VDD   | IC power supply                                              |

| 4        | VCELL | Battery voltage monitor I/O                                  |

| 6        | VSS   | General purpose ground connection                            |

| 7        | CSP   | Current sensing positive input                               |

| 8        | CSN   | Current sensing negative input                               |

| 9        | TS    | NTC measuring I/O                                            |

| 2, 5, 12 | NC    | NC pin, no connection with any internal circuits             |

| 10       | SDA   | Serial data input/output                                     |

| 11       | SCL   | Serial clock input                                           |

| 1        | INT_N | Alarm signal for MCU interrupt controller; open drain output |

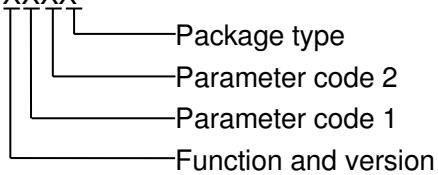

## Type Number

CW2217XXXX

D: DFN package

A: Standard firmware

A: Standard Li+ battery profile

B: Product version

## Absolute Maximum Ratings

|                            |                                           | VALUE   |       | UNITS |

|----------------------------|-------------------------------------------|---------|-------|-------|

|                            |                                           | MIN     | MAX   |       |

| Voltage respect to GND     | VCELL, VDD, CSP, CSN, INT_N, TS, SCL, SDA | -0.3    | 6     | V     |

| Output Current             | INT_N, SDA                                |         | 10    | mA    |

| Operation Temperature      | T <sub>A</sub>                            | -40     | 85    | °C    |

| Junction Temperature       | T <sub>J</sub>                            | -40     | 150   | °C    |

| Storage Temperature        | T <sub>STG</sub>                          | -60     | 150   | °C    |

| ESD                        | All pins. HBM model.                      |         | ±2000 | V     |

|                            | All pins. CDM model.                      |         | ±1000 | V     |

| Moisture Sensitivity Level | MSL                                       | Level 3 |       |       |

### Caution:

Stresses beyond "Absolute Maximum Ratings" condition may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## Recommended DC Operating Conditions

| PARAMETER                        | DESCRIPTION              | MIN  | MAX                    | UNITS |

|----------------------------------|--------------------------|------|------------------------|-------|

| Input Voltage Range              | VDD, INT_N, TS, SCL, SDA | -0.3 | 5.5                    | V     |

| Input Voltage Range              | VCELL                    | -0.3 | 5.0                    | V     |

| Input Voltage Range              | CSP, CSN                 | -0.3 | V <sub>CELL</sub> +0.3 | V     |

| I <sup>2</sup> C Clock Frequency |                          |      | 400                    | kHz   |

| Operation Temperature            |                          | -40  | 85                     | °C    |

## Electrical Characteristics

2.5V≤V<sub>DD</sub>≤5.5V, T<sub>A</sub>= -40 to 85°C, unless otherwise noted

| PARAMETER                                           | SYMBOL                 | CONDITIONS                                   | MIN  | TYP   | MAX | UNIT |

|-----------------------------------------------------|------------------------|----------------------------------------------|------|-------|-----|------|

| <b>POWER SUPPLY CONTROL</b>                         |                        |                                              |      |       |     |      |

| V <sub>DD</sub> power on threshold                  | V <sub>ON_VDD</sub>    | I <sup>2</sup> C communication enable        |      | 2.4   |     | V    |

| V <sub>DD</sub> power off threshold                 | V <sub>OFF_VDD</sub>   | I <sup>2</sup> C communication stop          |      | 2.2   |     | V    |

| <b>QUIESCENT CURRENT</b>                            |                        |                                              |      |       |     |      |

| Shutdown mode current                               | I <sub>SD</sub>        |                                              |      | 0.5   |     | μA   |

| Active normal mode current                          | I <sub>NOR</sub>       |                                              |      | 12    |     | μA   |

| <b>CELL VOLTAGE MEASUREMENT ADC CHARACTERISTICS</b> |                        |                                              |      |       |     |      |

| Cell pin measurement range                          | V <sub>CELL</sub>      |                                              | 2.5  |       | 5.0 | V    |

| Conversion time                                     | t <sub>ADC_CONV</sub>  |                                              |      | 5     |     | ms   |

| Effective bits                                      |                        |                                              |      | 14    |     | bits |

| Measurement resolution                              | V <sub>LSB_CELL</sub>  |                                              |      | 312.5 |     | μV   |

| Measurement error                                   | V <sub>ERR_CELL</sub>  | T <sub>A</sub> = 25°C and cell voltage is 4V | -7.5 |       | 7.5 | mV   |

|                                                     |                        | T <sub>A</sub> =-20 to 70°C                  | -12  |       | 12  | mV   |

|                                                     |                        | T <sub>A</sub> =-40 to 85°C                  | -20  |       | 20  | mV   |

| <b>TS PIN TEMPERATURE ADC CHARACTERISTICS</b>       |                        |                                              |      |       |     |      |

| Measurement range                                   | V <sub>TS</sub>        |                                              | 0    |       | 2.1 | V    |

| Conversion time                                     | t <sub>ADC_CONV</sub>  |                                              |      | 5     |     | ms   |

| Effective bits                                      |                        |                                              |      | 14    |     | bits |

| Measurement resolution                              | V <sub>LSB_TS</sub>    |                                              |      | 312.5 |     | μV   |

| Measurement error                                   | V <sub>ERR_TS</sub>    | T <sub>A</sub> = 25°C                        | -7.5 |       | 7.5 | mV   |

|                                                     |                        | T <sub>A</sub> =-20 to 70°C                  | -12  |       | 12  | mV   |

|                                                     |                        | T <sub>A</sub> =-40 to 85°C                  | -20  |       | 20  | mV   |

| <b>CURRENT MEASUREMENT ADC CHARACTERISTICS</b>      |                        |                                              |      |       |     |      |

| CSP-CSN full scale magnitude                        | V <sub>CSP-CSN</sub>   |                                              |      | ±52.4 |     | mV   |

| Conversion time                                     | t <sub>CADC_CONV</sub> |                                              |      | 10    |     | ms   |

| Effective bits                                      |                        |                                              |      | 16    |     | bits |

| Measurement offset                                  | V <sub>ZERO_OFF</sub>  |                                              |      | ±1    |     | LSB  |

| Measurement error                                   | I <sub>ERR</sub>       | Current=1A, Rsense=10mohm                    | -1   |       | 1   | %    |

| <b>DIGITAL IO CHARACTERISTICS</b>                   |                        |                                              |      |       |     |      |

| Input voltage, high                                 | V <sub>IH(OD)</sub>    | SDA, SCL and INT_N                           | 1.4  |       |     | V    |

| Input voltage, low                                  | V <sub>IL(OD)</sub>    | SDA, SCL and INT_N                           |      |       | 0.5 | V    |

| Output voltage, low                                 | V <sub>OL</sub>        | SDA and INT_N with 4mA current sink          |      |       | 0.3 | V    |

## Electrical Characteristics: I<sup>2</sup>C Interface

2.5V ≤ V<sub>DD</sub> ≤ 5.5V, T<sub>A</sub> = -40 to 85°C, unless otherwise noted

| PARAMETER                                        | SYMBOL              | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|--------------------------------------------------|---------------------|-----------------|------|-----|-----|------|

| Clock operating frequency                        | f <sub>SCL</sub>    |                 | 10   |     | 400 | kHz  |

| Bus free time between a STOP and START condition | t <sub>BUF</sub>    |                 | 1300 |     |     | ns   |

| Low period of SCL clock                          | t <sub>LOW</sub>    |                 | 1300 |     |     | ns   |

| High period of SCL clock                         | t <sub>HIGH</sub>   |                 | 600  |     |     | ns   |

| SDA data setup time                              | t <sub>SU:DAT</sub> |                 | 100  |     |     | ns   |

| SDA data hold time                               | t <sub>HD:DAT</sub> |                 | 0    |     | 900 | ns   |

| Hold time after START condition                  | t <sub>HD:STA</sub> |                 | 600  |     |     | ns   |

| Setup time for a repeated START condition        | t <sub>SU:STA</sub> |                 | 600  |     |     | ns   |

| Fall time for SDA, SCL                           | t <sub>F</sub>      |                 | 20   |     | 300 | ns   |

| Rise time for SDA, SCL                           | t <sub>R</sub>      |                 | 20   |     | 300 | ns   |

| Spike pulse widths suppressed by input filter    | t <sub>SP</sub>     |                 | 0    |     | 50  | ns   |

| Setup time for STOP condition                    | t <sub>SU:STO</sub> |                 | 600  |     |     | ns   |

| Capacitive load for each bus line                | C <sub>B</sub>      |                 |      |     | 400 | pF   |

| SDA, SCL input capacitance                       | C <sub>BIN</sub>    |                 |      |     | 60  | pF   |

## I<sup>2</sup>C Timing Diagram

Figure 2. I<sup>2</sup>C Timing Diagram

## Function Block Diagram

Figure 3. Function Block Diagram

## Detailed Description

### Power States

After power up, the CW2217 stays in shutdown mode by default to minimize power consumption. The IC needs two steps to enter active mode, in which normal gauging is in operation: step one, clear sleep register by writing 0x30 to REG 0x08; step two, clear restart register by writing 0x00 to REG 0x08.

### FastCali Algorithm

The FastCali algorithm embedded in the CW2217 could calculate the SOC based on the battery characterization data and the measurement of battery voltage, temperature and charging or discharging current. It can achieve high accuracy SOC calculation across wide operating conditions and over the battery lifetime. It does not accumulate error with time and current, which is a big advantage compared to the coulomb counter (CC). The CC suffers from SOC drift caused by the accumulation error of current sense offset and battery self-discharge.

### First SOC Estimation after Power Up

After power up, the CW2217 will take the first voltage and current measurement and calculate the OCV, and then get the first SOC. The first SOC error could be healed during the following normal usage since more battery data can be used for calibration.

## Temperature Measurement

The TS pin of the CW2217 is the external battery temperature sensing pin and its driving circuits (internal pull-up) are integrated. The measured temperature is utilized by the gauge algorithm directly and could be read by the host MCU too. 10kohm, 47kohm and 100kohm NTC thermistors are supported and the thermistor type selection is in the battery profile, 10kohm NTC is selected by default.

| Part   | NTC Thermistor Supported                       |

|--------|------------------------------------------------|

| CW2217 | R25C=10kΩ±1%, $\beta(25/85)$ value = 3435K±1%  |

|        | R25C=10kΩ±1%, $\beta(25/50)$ value = 3380K±1%  |

|        | R25C=47kΩ±1%, $\beta(25/50)$ value = 4050K±1%  |

|        | R25C=100kΩ±1%, $\beta(25/50)$ value = 4250K±1% |

Table 1. NTC Thermistor Selection Guide

The CW2217 also supports host reported temperature. For accurate SOC calculation, the host MCU need to timely transfer the battery temperature to the gauge IC when TS pin sensing is not used. The selection of the temperature measurement source is in the battery profile.

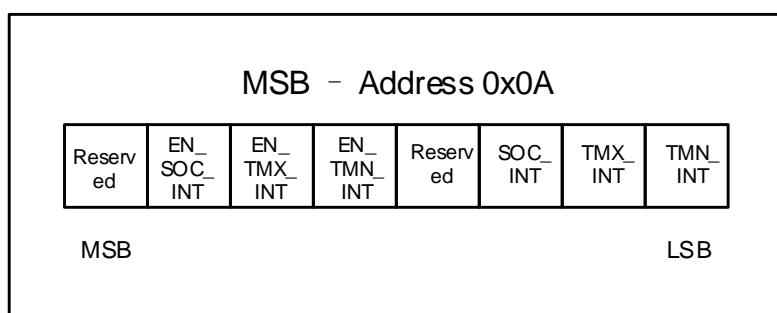

## Interrupt

The CW2217 have 3 interrupt sources: SOC change, Max. temperature and Min. temperature. The INT source enable bit should be set before used. If any INT event occur, the relevant register status bit in INT\_CONF [3:0] of register 0x0A will be set and the INT\_N pin will generate a low pulse with about 1ms duration to inform the host MCU. The host needs to clear the INT status bit to prevent from missing any new coming INT event.

Note that the 1ms low pulse will keep on popping up in the interval of 1 second or longer until the current INT event is gone. For example, when the measured temperature is over Max. temperature threshold continually, low pulse will keep on popping up on the INT\_N pin.

## Battery Profile

The battery profile of the CW2217 is programmable to match battery parameters, such as various maximum charging voltages, like 4.20V, 4.35V, 4.40V or other values. User's battery needs to have battery characterization to get its exclusive profile for more accurate SOC calculation. Contact Cellwise to have the battery characterization.

Besides battery characteristic relevant info, some configurations are included in the battery profile too. For example, the current sensing calibration value is stored in the profile since it is user's design related parameter.

## Register Map

Below table shows the I<sup>2</sup>C register map of the CW2217.

| REGISTER NAME | ADDRESS | DESCRIPTION                                   | READ/ WRITE | DEFAULT VALUE |

|---------------|---------|-----------------------------------------------|-------------|---------------|

| VERSION       | 0x00    | IC version                                    | R           | 0xA0          |

| VCELL_H       | 0x02    | VCELL voltage conversion result, VCELL[13:8]  | R           | 0x00          |

| VCELL_L       | 0x03    | VCELL voltage conversion result, VCELL[7:0]   | R           | 0x00          |

| SOC_H         | 0x04    | SOC result, SOC[15:8]                         | R           | 0x00          |

| SOC_L         | 0x05    | SOC result, SOC[7:0]                          | R           | 0x00          |

| TEMP          | 0x06    | Battery NTC thermistor temperature, TEMP[7:0] | R/W         | 0x82          |

| CONFIG        | 0x08    | IC configuration                              | R/W         | 0xF0          |

| INT_CONF      | 0x0A    | Interrupt configuration                       | R/W         | 0x40          |

| SOC_ALERT     | 0x0B    | SOC interrupt threshold                       | R/W         | 0x14          |

| TEMP_MAX      | 0x0C    | Maximum temperature threshold                 | R/W         | 0xAA          |

| TEMP_MIN      | 0x0D    | Minimum temperature threshold                 | R/W         | 0x50          |

| CURRENT_H     | 0x0E    | Current conversion result [15:8]              | R           | 0x00          |

| CURRENT_L     | 0x0F    | Current conversion result [7:0]               | R           | 0x00          |

| T_HOST_H      | 0xA0    | Host reported temperature, T_HOST[15:8]       | R/W         | 0x00          |

| T_HOST_L      | 0xA1    | Host reported temperature, T_HOST[7:0]        | R/W         | 0x00          |

| USER_CONF     | 0xA2    | Configurable register for developer           | R/W         | 0x00          |

| CYCLECNT_H    | 0xA4    | Battery charging cycles, CYCLECNT[15:8]       | R           | 0x00          |

| CYCLECNT_L    | 0xA5    | Battery charging cycles, CYCLECNT[7:0]        | R           | 0x00          |

| SOH           | 0xA6    | Battery state of health, SOH[7:0]             | R           | 0x00          |

| STB_CUR_H     | 0xA8    | Standby current conversion result [15:8]      | R           | 0x00          |

| STB_CUR_L     | 0xA9    | Standby current conversion result [7:0]       | R           | 0x00          |

| FW_VERSION    | 0xAB    | Firmware version                              | R           | 0x00          |

Table 2. Register Map

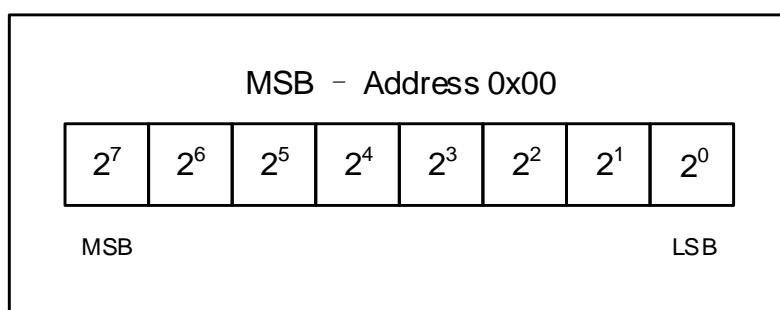

## VERSION Register (0x00)

The VERSION register is an **UNSIGNED** 8bit read-only register. Its value is fixed to 0xA0 in shutdown mode and active mode, which is the CW2217 IC version.

Figure 4. VERSION Register Format

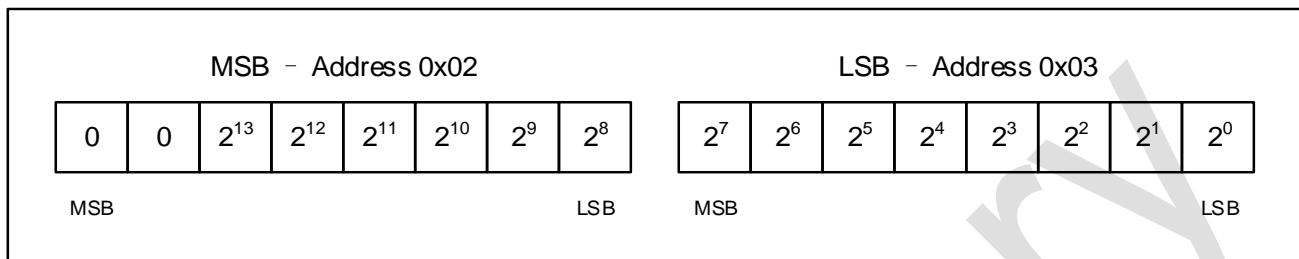

## VCELL Register (0x02~0x03)

The VCELL register is an **UNSIGNED** 14bit read-only register that updates the battery voltage continuously. Battery voltage is measured between the VCELL pin and VSS pin, which is the ground reference. A 14bit sigma-delta A/D converter is used and the voltage resolution is 312.5µV.

$$V(uV) = \text{Value}_{(0x02 \text{ } 0x03 \text{ DEC})} * 312.5$$

Figure 5. VCELL Register Format

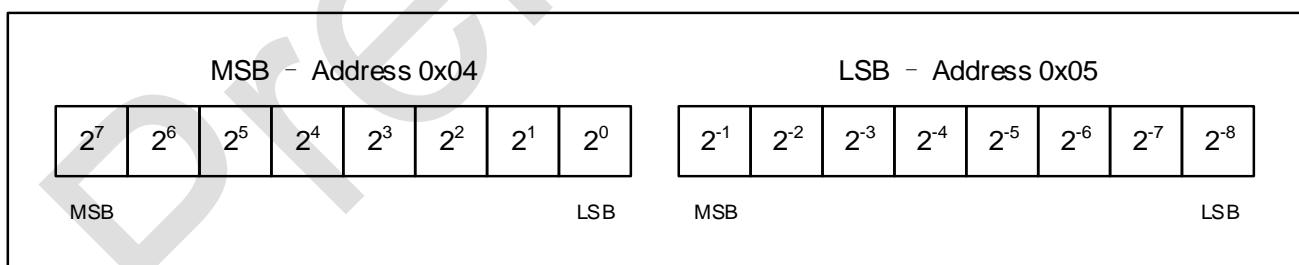

## SOC Register (0x04~0x05)

The SOC register is an **UNSIGNED** 16bit read-only register that indicates the SOC of the battery. The SOC shows in % format, which means how much percent of the battery's total available capacity is remaining in the battery now. The SOC can intrinsically adjust itself to cater to the change of battery status, including load, temperature and aging etc.

The high byte(0x04) contains the SOC in 1% unit which can be directly used if this resolution is good enough for the application. The low byte(0x05) provides more accurate fractional part of the SOC and its LSB is (1/256) %.

$$SOC(%) = \text{Value}_{(0x04 \text{ DEC})} + \frac{\text{Value}_{(0x05 \text{ DEC})}}{256}$$

Figure 6. SOC Register Format

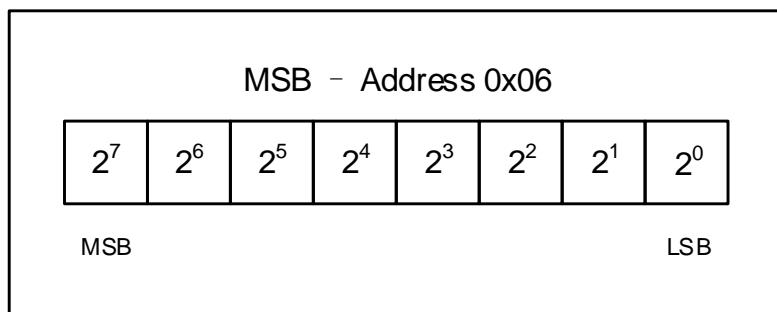

## TEMP Register (0x06)

The TEMP register is an **UNSIGNED** 8bit read only register. It reports the real-time battery temperature measured at TS pin. The scope is from -40 to 87.5 degrees Celsius, LSB is 0.5 degree Celsius.

$$TEMP(^{\circ}\text{C}) = -40 + \frac{\text{Value}_{(0x06 \text{ DEC})}}{2}$$

Figure 7. TEMP Register Format

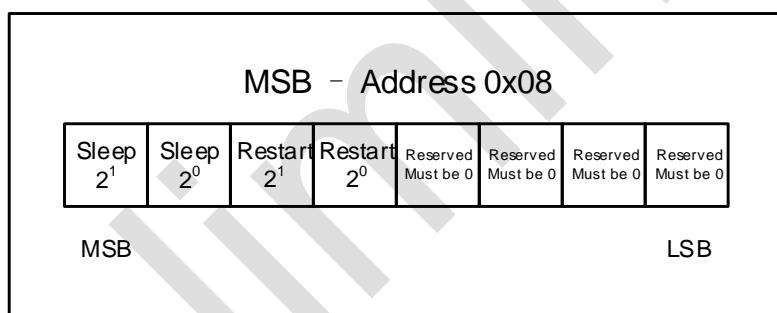

### CONFIG Register (0x08)

The CONFIG register is used for the host MCU to configure the fuel gauge IC. The default value is 0xF0, SLEEP and RESTART bits are set. To power up the IC, the host MCU needs to write 0x30 to exit shutdown mode, and then write 0x00 to restart the gauge to enter active mode. To reset the IC, the host MCU needs to write 0xF0, 0x30 and 0x00 in sequence to this register to complete the restart procedure. The CW2217 will reload relevant parameters and settings and restart SOC calculation. Note that the SOC may be a different value after reset operation since it is a brand-new calculation based on the latest battery status. CONFIG [3:0] is reserved. Don't do any operation with it.

Figure 8. CONFIG Register Format

### INT\_CONF Register (0x0A)

INT\_CONF [6:4] are used to enable interrupt source, and INT\_CONF [2:0] indicate relative INT event. There are three interrupt sources. SOC\_INT indicates SOC change. TMX\_INT is the maximum temperature flag. It will be set when temperature is higher than TEMP\_MAX(0x0C). TMN\_INT is the minimum temperature flag. It will be set when temperature is lower than TEMP\_MIN(0x0D).

Figure 9. INT\_CONF Register Format

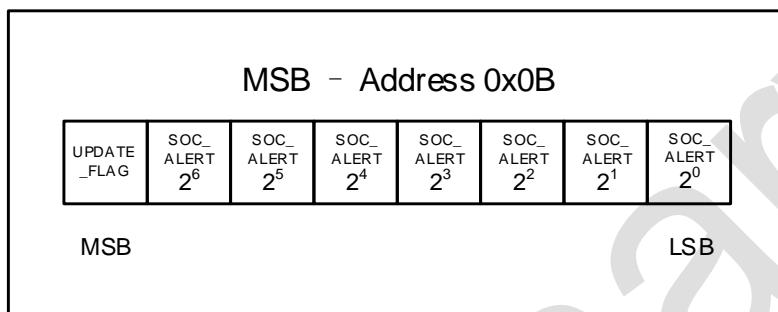

## SOC\_ALERT Register (0x0B)

UPDATE\_FLAG [7] can be set to “1” by the host MCU after the battery profile is successfully loaded. Since it will be clear after POR, it can be used to check whether the IC has been reset. Its default value is “0”. SOC\_ALERT [6:0] configures the specified SOC alarm threshold to remind the host MCU. For instance, set it to 0x14 means that SOC\_INT will be set when the SOC updates downward from 0x15 to 0x14 or upward from 0x13 to 0x14. If set SOC\_ALERT [6:0] to any value from 0x65 to 0x7F, the SOC\_INT will generate as long as the integer part of the SOC Register (0x04) has been changed.

Figure 10. SOC\_ALERT Register Format

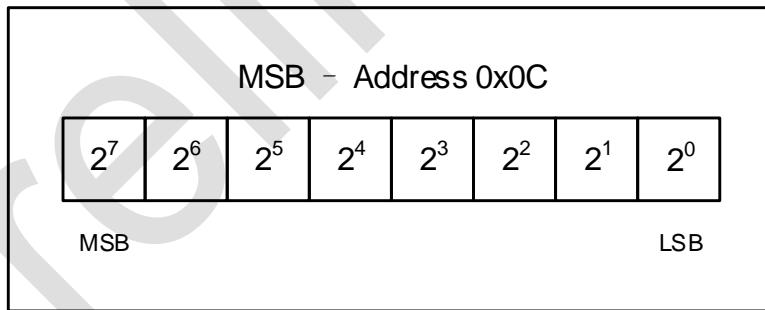

## TEMP\_MAX Register (0x0C)

TEMP\_MAX is the maximum temperature alert threshold. When temperature reach this value, TMX\_INT (0x0A) bit is set, and a low pulse is sent on INT\_N pin. LSB is 0.5 degree Celsius.

$$\text{TEMP}_{\text{MAX}}^{\circ\text{C}} = -40 + \frac{\text{Value}_{(0x0C\text{ DEC})}}{2}$$

Figure 11. TEMP\_MAX Register Format

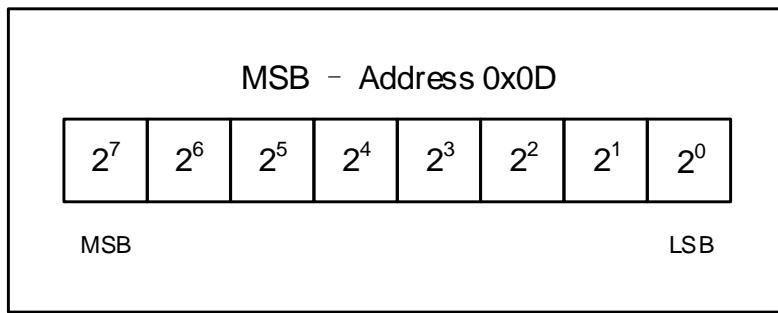

## TEMP\_MIN Register (0x0D)

TEMP\_MIN is the minimum temperature alert threshold. When temperature reach this value, TMN\_INT (0x0A) bit is set, and a low pulse is sent on INT\_N pin. LSB is 0.5 degree Celsius.

$$\text{TEMP}_{\text{MIN}}^{\circ\text{C}} = -40 + \frac{\text{Value}_{(0x0D\text{ DEC})}}{2}$$

Figure 12. TEMP\_MIN Register Format

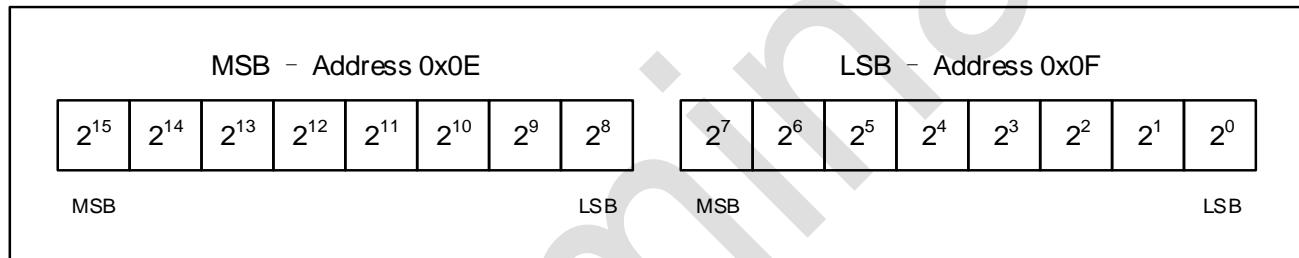

### CURRENT Register (0x0E~0x0F)

CURRENT is a **SIGNED** 16bit register that reports current A/D converter result of the voltage across the current sense resistor, 10mohm typical. The result is stored as a two's complement value to show positive and negative current. Voltages outside the minimum and maximum register values are reported as the minimum or maximum value.

Figure 13. CURRENT Register Format

The register value should be divided by the sense resistance to convert to amperes. The value of the sense resistor determines the resolution and the full-scale range of the current readings. The LSB of 0x0F is (52.4/32768) mV. Table 3 shows range and resolution values for typical sense resistances. The default value is 0x0000, stands for 0mA. 0x7FFF stands for the maximum charging current and 0x8001 stands for the maximum discharging current.

$$I(A) = \frac{52.4 * \text{Value}_{(0x0E \text{ } 0x0F \text{ } DEC)}}{32768 * R_{sense}(m\Omega)}$$

| Sense Resistor (mΩ) | Current Register Resolution (μA) | Current Register Range (A) |

|---------------------|----------------------------------|----------------------------|

| 1                   | 1600                             | ±52.4                      |

| 2                   | 800                              | ±26.2                      |

| 5                   | 320                              | ±10.5                      |

| 10                  | 160                              | ±5.2                       |

| 50                  | 32                               | ±1.05                      |

Table 3. Current Measurement Range and Resolution vs. Sense Resistor Value

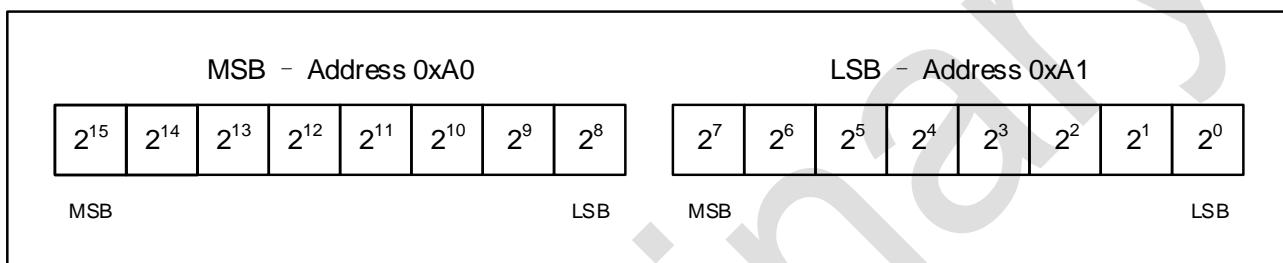

### T\_HOST Register (0xA0~0xA1)

T\_Host is an **UNSIGNED** 16bit register where the host MCU could write its reported temperature via I<sup>2</sup>C

interface. The high byte 0xA0 contains the host reported temperature in 0.5 degree Celsius unit and the low byte 0xA1 provides more accurate part of the host reported temperature in 1/512 degree Celsius unit. The algorithm checks this register value about every second when host reported temperature is configured. The low byte 0xA1 must be a different value compare with the previous temperature, otherwise, both 0xA0 and 0xA1 value are neglected by the algorithm.

To secure the host timely refresh its reported temperature to the fuel gauge IC, an alarm feature can be used to remind the host. When the algorithm has not gotten a new valid temperature over 16 seconds, the high temperature INT will generate and the TMX\_INT bit of Register 0x0A will be set when the EN\_TMX\_INT bit of Register 0x0A is enabled. When high temperature alarm happens, the host can write "0" to clear the TMX\_INT bit.

$$T_{HOST} ({}^\circ C) = -40 + \frac{Value_{(0xA0\ DEC)}}{2} + \frac{Value_{(0xA1\ DEC)}}{512}$$

Figure 14. T\_HOST Register Format

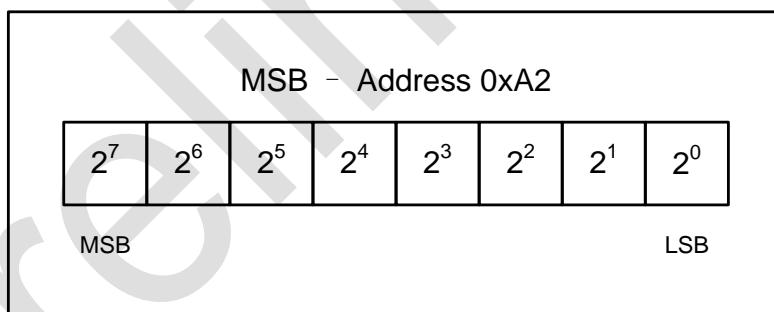

### USER\_CONF Register (0xA2)

USER\_CONF is a free configurable 8bit register which can be read or write by developers directly.

Figure 15. USER\_CONF Register Format

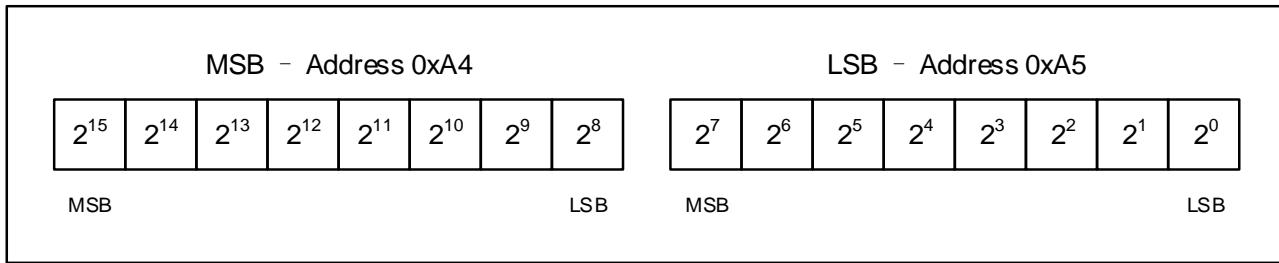

### CYCLECNT Register (0xA4~0xA5)

CYCLECNT is an **UNSIGNED** 16bit register that counts cycle life of the battery. The LSB of 0xA5 stands for 1/16 cycle. This register will be clear after enters shutdown mode.

$$\text{Cycle Count} = \frac{Value_{(0xA4\ 0xA5\ DEC)}}{16}$$

Figure 16. CYCLECNT Register Format

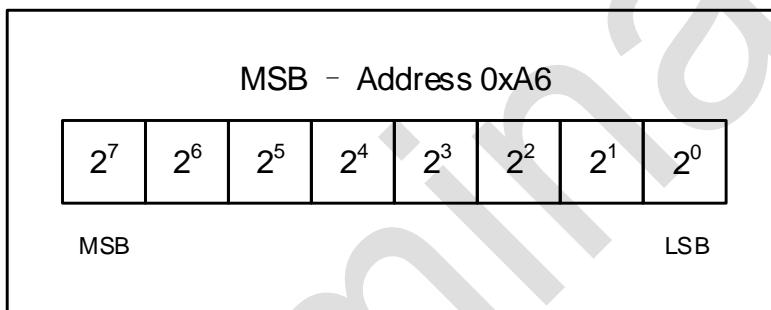

### SOH Register (0xA6)

SOH (State of Health) is an **UNSIGNED** 8bit register that represents the level of battery aging by tracking battery internal impedance increment. When the device enters active mode, this register refresh to 0x64 by default. Its range is 0x00 to 0x64, indicating 0 to 100%. This register will be clear after enters shutdown mode.

Figure 17. SOH Register Format

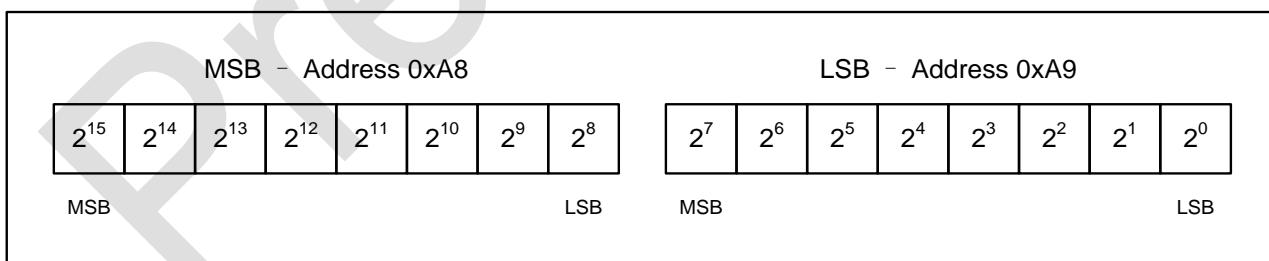

### STB\_CUR Register (0xA8-0xA9)

STB\_CUR is a **SIGNED** 16bit register that reports the equipment standby current. It automatically reports the average standby current of the past 64 seconds when the equipment is in low power standby state. The result is stored as a two's complement value to show positive and negative current.

Figure 18. STB\_CUR Register Format

The register value should be divided by the sense resistance to convert to amperes. Note that the full range of STB\_CUR register is only 1/16 of that of CURRENT register. Thus, the LSB of 0xA9 is (52.4/32768)/16 mV. For a 10mohm sense resistor, the standby current full range is -327.5mA to +327.5mA. The register default value is 0x0000, stands for 0mA.

$$I(A) = \frac{52.4 * Value_{(0xA8\ 0xA9\ DEC)}}{16 * 32768 * Rsense(m\Omega)}$$

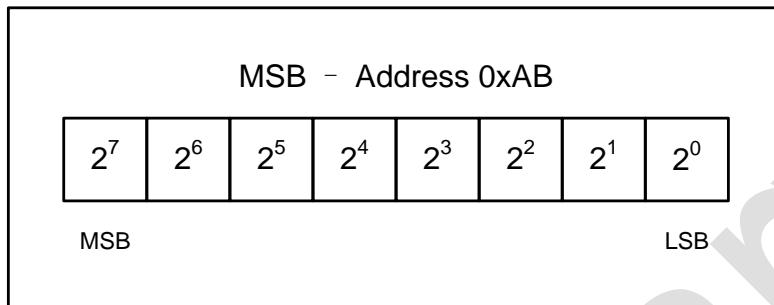

## FW\_VERSION Register (0xAB)

FW\_VERSION register reports the firmware (FW) running in the chip. It is fixed to 0x00 when the chip is in shutdown mode. When in active mode, Bit [7:6] are fixed to '01', which stand for the CW2217 and Bit [5:0] stand for the FW version running in the chip. Note that the FW version is subject to update and contact sales office for confirmation when necessary.

Figure 19. FW\_VERSION Register Format

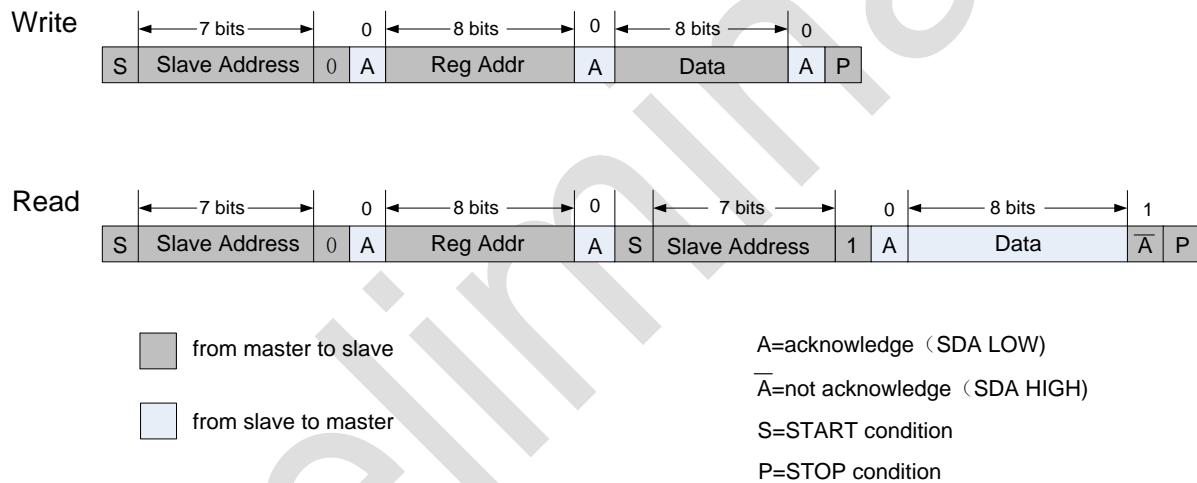

## I<sup>2</sup>C Characteristics

The CW2217 includes an I<sup>2</sup>C bus which provides access to internal registers to program parameters and report device status. To adjust these parameters, data transmission from the host to the CW2217 and vice versa must take place through the two wires. The two wires of the bus consist of the SDA line, over which all data is sent and the SCL line which is a clock signal used to synchronize sending/receiving of the data. Data on the I<sup>2</sup>C bus can be transferred up to 100kbps in the standard mode or up to 400kbps in the fast mode. When the bus is free, both lines are HIGH. The device operates as a slave device. The I<sup>2</sup>C interface of the CW2217 works after the supply voltage rises above POR threshold.

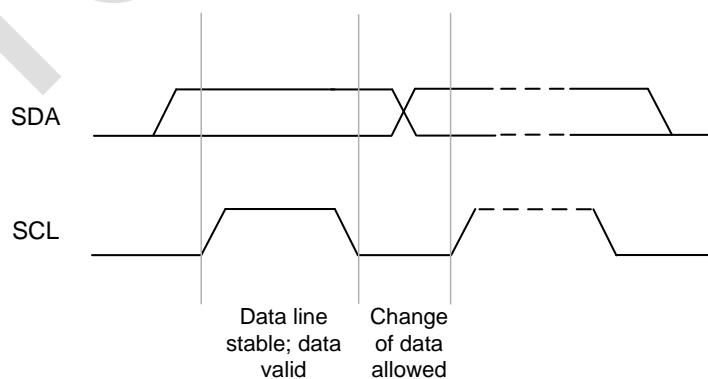

### Data Validity

The data on the SDA line must be stable during the HIGH period of the SCL, unless generating a START or STOP condition. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

Figure 20. Bit Transfer on the I<sup>2</sup>C Bus

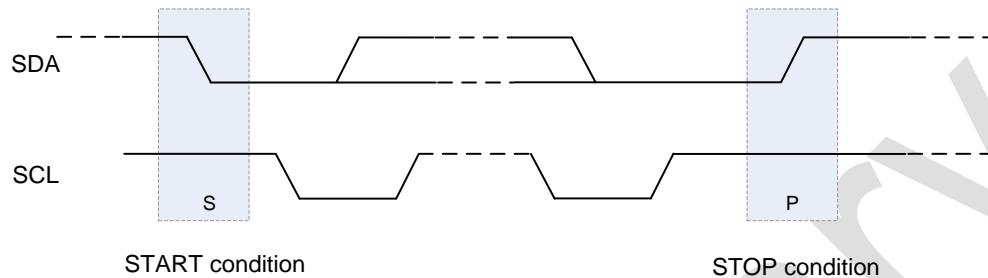

## START and STOP Conditions

All transactions begin with a START (S) and are terminated by a STOP (P). A HIGH to LOW transition on the SDA line while SCL is HIGH defines a START condition. A LOW to HIGH transition on the SDA line while SCL is HIGH defines a STOP condition. START and STOP conditions are always generated by the master. The bus is considered to be busy after the START condition and free after the STOP condition.

Figure 21. START and STOP Conditions

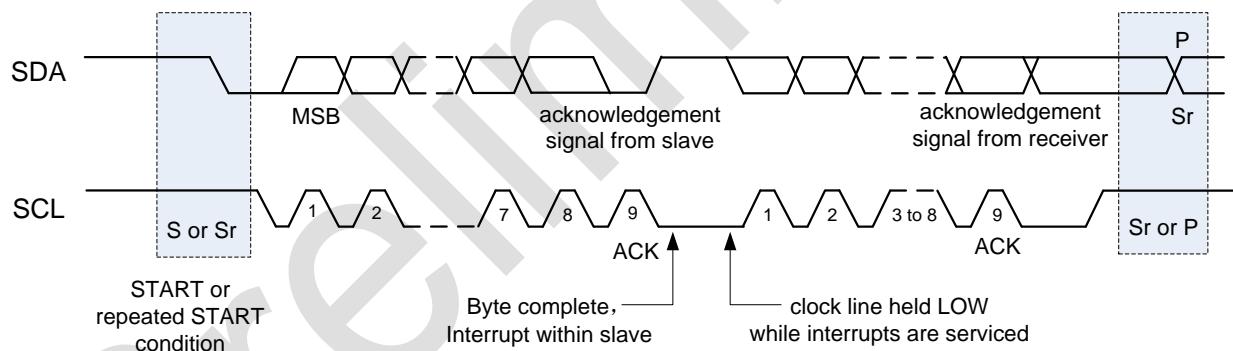

## Byte Format

Every byte put on the SDA line must be eight bits long, the number of bytes that can be transmitted per transfer is unrestricted. Each byte must be followed by an Acknowledge bit. Data is transferred with the MOST Significant Bit (MSB) first.

Figure 22. Data Transfer on the I2C Bus

## Acknowledge (ACK) and Not Acknowledge (NACK)

The acknowledge takes place after each byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. The master generates all clock pulses, including the ACK ninth clock pulse. The ACK signal is defined as follows: The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains stable LOW during the HIGH period of this clock pulse. When SDA remains HIGH during this ninth clock pulse, this is defined as the NACK signal. The master can then generate either a STOP condition to abort the transfer, or a repeated a START condition to start a new transfer.

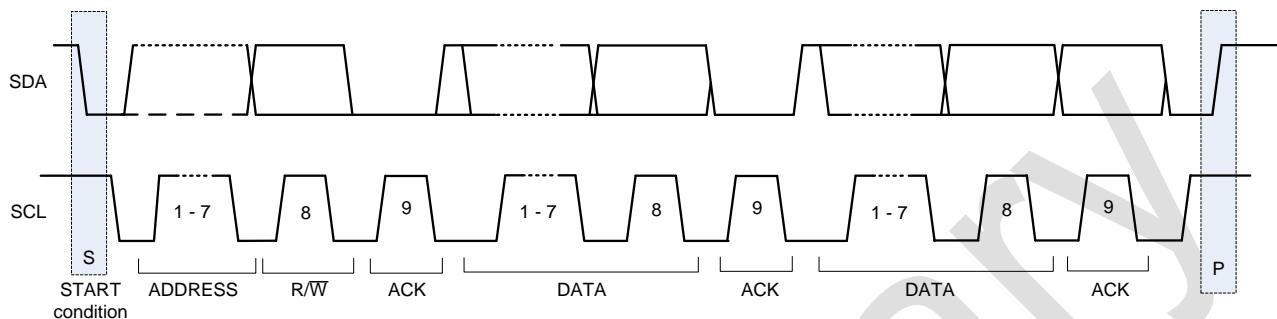

## The Slave Address and R/W Bit

After the START condition (S), a slave address is sent. This address is seven bits long followed by an eighth bit which is data direction bit (R/W), a 'zero' indicates a transmission (WRITE), a 'one' indicates a request for data (READ). A data transfer is always terminated by a STOP condition (P) generated by the master.

Figure 23. Complete Data Transfer

Figure 24. Write and Read Transaction

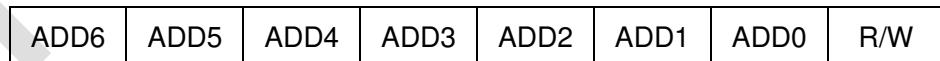

## Device Address

I<sup>2</sup>C device address is consisted of 7bits slave address and 1 read/write control bit.

Figure 25. I<sup>2</sup>C Address Format

7bits address of CW2217BAAD is 0b1100100 or 0x64. Combine with the R/W bit:

Read command is 0xC9;

Write command is 0xC8.

## Application and Implementation

The CW2217 provides fuel gauging for single-cell Li-Ion batteries. Battery fuel gauging with the fuel gauge requires connections only to P+ and P- for a removable battery pack or embedded battery circuits. It supports low-side current sensing or high-side current sensing. Battery temperature can be measured via the TS pin on the NTC thermistor in the pack. To allow for optimal performance, special considerations must be taken to ensure robustness of the application circuits and minimization of measurement error.

Figure 26. Typical Application for Single Cell

### Power Supply Decoupling

The battery pack connection to the VCELL pin is used for voltage measurement of the cell and the connection to the VDD is to power the fuel gauge IC. Bypass capacitors whose effective value after considering the derating of capacitor should be at least 1 $\mu$ F should be added on VCELL and VDD pins. One 100ohm resistor is good to put in front of the VCELL and VDD pin respectively and the RC can filter the noise on the power supply net.

### Sense Resistor

Any variation encountered in the resistance present between the CSP and CSN pins will affect the resulting differential voltage and the derived current it senses. Thus, it is recommended to select a sense resistor with minimal tolerance and temperature coefficient of resistance (TCR) characteristics. The recommendation is using  $\pm 1\%$  tolerance, 50 ppm drift sense resistor. And the power rating of the sense resistor should be considered according to the application.

## PCB Layout Guide

To ensure the measurement accuracy of the CW2217, the recommended layout guideline is as below:

- 1) Place the VCELL and VDD bypass capacitors as close to the IC as possible to avoid the noise effect.

- 2) The VCELL and VSS path should be Kelvin sense routing connected to the P+ and P- to minimize the IR drop effect on voltage measurement accuracy.

- 3) The CSP and CSN pins must be Kelvin sense routing connected to the sense resistor terminals.

- 4) The NTC thermistor should be as close as possible to the battery and far away from the thermal area.

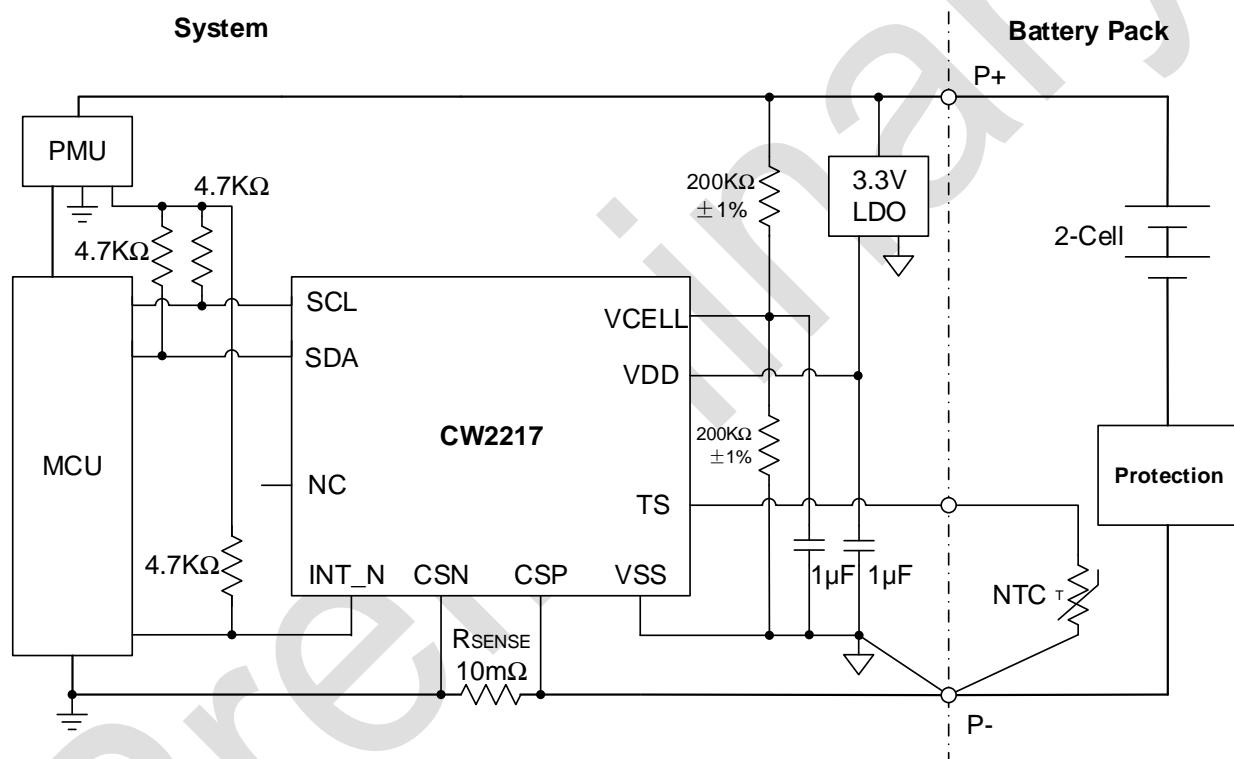

## Typical Applications (continued.) (Note1, 2, 3)

Figure 27. Typical Application for 2-Cell System Side

Figure 28. Typical Application for 2-Cell Pack Side

Note:

- 1) Add TVS diode at I<sup>2</sup>C interface when using in a removable battery pack.

- 2) For applications using multiple cells in serials, a voltage divider can be used to adapt the CW2217 usage, but it does not provide any individual cell information. Therefore, cell balance circuits are recommended to maintain the pack safety.

- 3) It is up to the pack maker and the original equipment manufacturer to make sure that the multiple cells in series are not out of balance and that the safety of the pack is maintained.

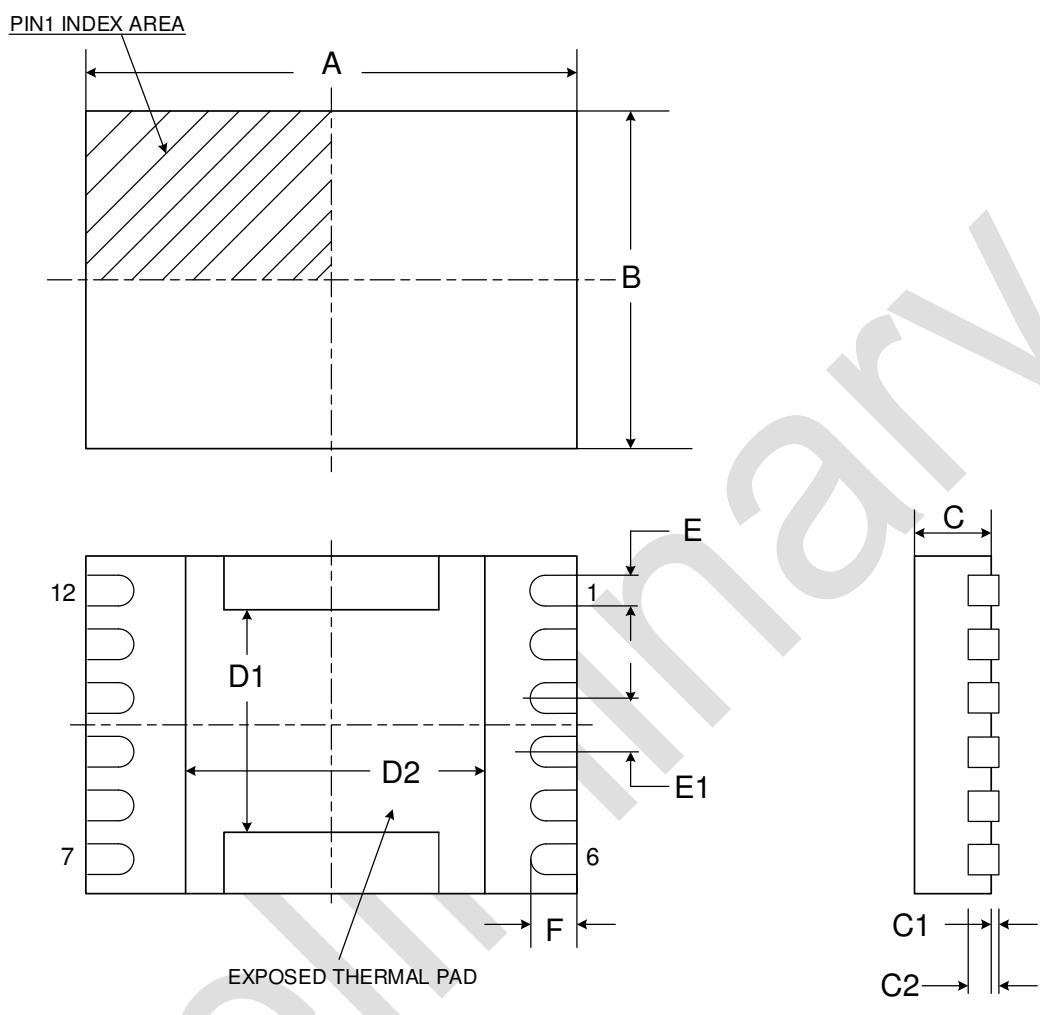

## Package Information

DFN-12 Package

| SYMBOL | UNiT (mm) |      |      |

|--------|-----------|------|------|

|        | MIN       | Typ  | MAX  |

| A      | 3.90      | 4.00 | 4.10 |

| B      | 2.40      | 2.50 | 2.60 |

| C      | 0.60      | --   | 0.80 |

| C1     | 0         | --   | 0.05 |

| C2     | 0.20 BSC  |      |      |

| D1     | 2.00 BSC  |      |      |

| D2     | 2.50 BSC  |      |      |

| E      | 0.15      | 0.20 | 0.25 |

| E1     | 0.40 BSC  |      |      |

| F      | 0.30      | 0.40 | 0.50 |

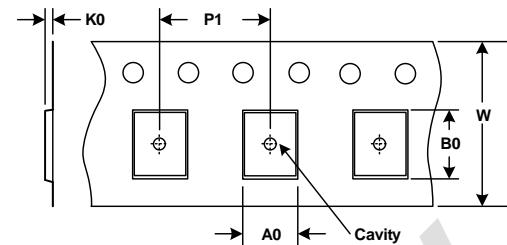

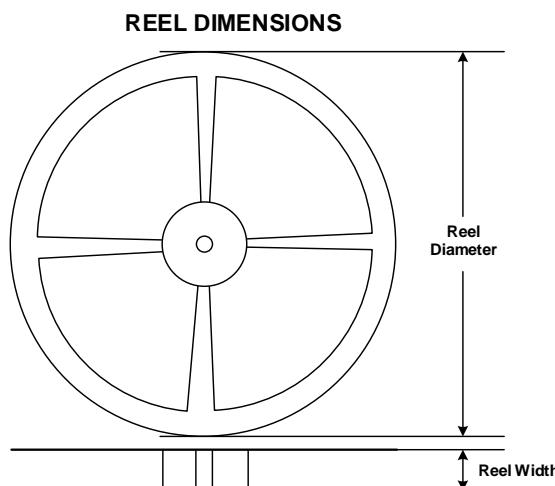

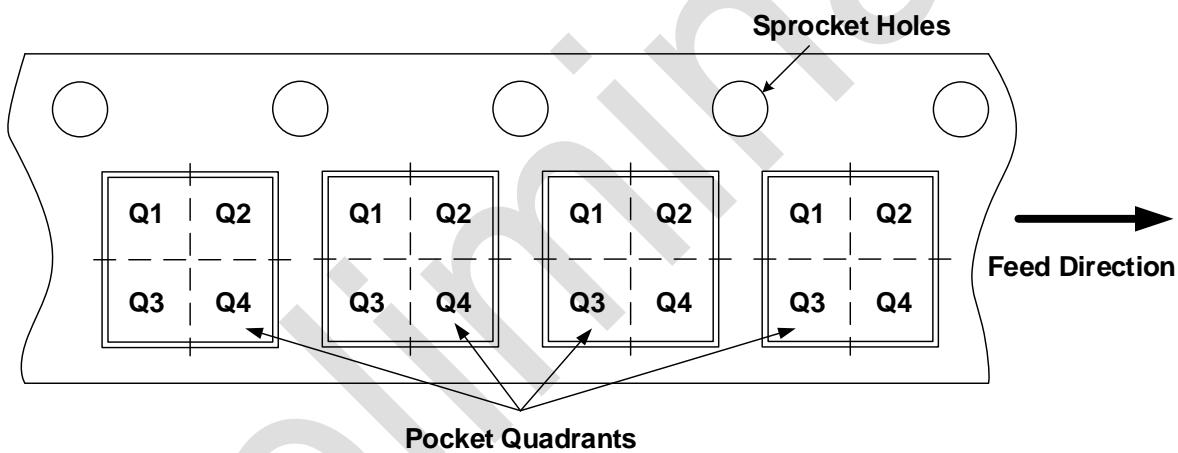

## Tape and Reel Information

|           |                                                           |

|-----------|-----------------------------------------------------------|

| <b>A0</b> | Dimension designed to accommodate the component width     |

| <b>B0</b> | Dimension designed to accommodate the component length    |

| <b>K0</b> | Dimension designed to accommodate the component thickness |

| <b>W</b>  | Overall width of the carrier tape                         |

| <b>P1</b> | Pitch between successive cavity centers                   |

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| Device     | Package Type | Reel Diameter (mm) | Reel Width (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1 (mm) | W (mm) | Pin 1 Quadrant |

|------------|--------------|--------------------|-----------------|---------|---------|---------|---------|--------|----------------|

| CW2217BAAD | DFN-12       | 330                | 12.4            | 2.8     | 4.3     | 1.2     | 4.0     | 12.0   | Q2             |

Note: All dimensions are nominal.

## Revision History

| Release No. | Date       | Revision Description   |

|-------------|------------|------------------------|

| 0.1         | 2021.12.15 | Preliminary DS Release |

## DISCLAIMER

*CELLWISE reserves the right to make changes without further notices to any products herein to improve reliability, function or design. CELLWISE does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights, nor the rights of others.*

*CELLWISE's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of CELLWISE corporation.*

*As used herein:*

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.*

- 2. A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.*