## CX28224/5/9 Inverse Multiplexing for ATM (IMA) Family

**Data Sheet**

#### **Ordering Information**

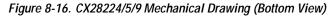

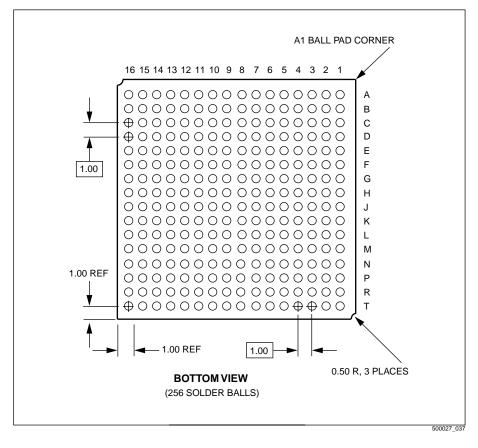

| Model Number | Manufacturing Part<br>Number | Product<br>Revision | Package            | Operating Temperature |

|--------------|------------------------------|---------------------|--------------------|-----------------------|

| CX28224      | 28224-14                     | D                   | 256-pin, 17 mm BGA | –40 °C to 85 °C       |

| CX28225      | 28225-14                     | D                   | 256-pin, 17 mm BGA | –40 °C to 85 °C       |

| CX28229      | 28229-14                     | D                   | 256-pin, 17 mm BGA | –40 °C to 85 °C       |

#### **Revision History**

| Revision | Level       | Date           | Description                                                                                                                                                                                                      |

|----------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A        | Preliminary | July 2001      | Preliminary A version. Note that this document was also released as a preliminary version under the document numbers 101265P1 and 101265P2.                                                                      |

| В        | Preliminary | September 2001 | Preliminary B version.                                                                                                                                                                                           |

| С        | Preliminary | September 2001 | Removed all references to PLCP and updated some of the bit descriptions.                                                                                                                                         |

| D        | Preliminary | April 2002     | Restructured and enhanced document to include more IMA related information.                                                                                                                                      |

| E        | Preliminary | May 2002       | Updated Ordering Information and a few register descriptions to reflect the CX28229-13 part.                                                                                                                     |

| F        | Preliminary | September 2002 | Updated to reflect the -14 part. Section 8, Electrical<br>and Mechanical Specifications, improved and noted<br>with change bars.                                                                                 |

| A        | Released    | January 2003   | Revised document number to reflect new numbering<br>system: new document number is 28229-DSH-001-B.<br>Removed Prelimary document designations. Replaced<br>hysteresis references with TTL levels in Table 8-16. |

© 2001, 2002, Mindspeed Technologies™, a Conexant business All Rights Reserved.

Information in this document is provided in connection with Mindspeed Technologies ("Mindspeed") products. These materials are provided by Mindspeed as a service to its customers and may be used for informational purposes only. Mindspeed assumes no responsibility for errors or omissions in these materials. Mindspeed may make changes to specifications and product descriptions at any time, without notice. Mindspeed makes no commitment to update the information and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to its specifications and product descriptions.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Mindspeed's Terms and Conditions of Sale for such products, Mindspeed assumes no liability whatsoever.

THESE MATERIALS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED, RELATING TO SALE AND/OR USE OF MINDSPEED PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, CONSEQUENTIAL OR INCIDENTAL DAMAGES, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. MINDSPEED FURTHER DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. MINDSPEED SHALL NOT BE LIABLE FOR ANY SPECIAL, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS, WHICH MAY RESULT FROM THE USE OF THESE MATERIALS.

Mindspeed products are not intended for use in medical, lifesaving or life sustaining applications. Mindspeed customers using or selling Mindspeed products for use in such applications do so at their own risk and agree to fully indemnify Mindspeed for any damages resulting from such improper use or sale.

The following are trademarks of Conexant Systems, Inc.: Mindspeed Technologies<sup>™</sup>, the Mindspeed<sup>™</sup> logo, and "Build It First"<sup>™</sup>. Product names or services listed in this publication are for identification purposes only, and may be trademarks of third parties. Third-party brands and names are the property of their respective owners.

For additional disclaimer information, please consult Mindspeed Technologies Legal Information posted at www.mindspeed.com which is incorporated by reference.

# MNDSPEED

## CX28224/5/9

### Inverse Multiplexing for ATM (IMA) Family

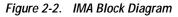

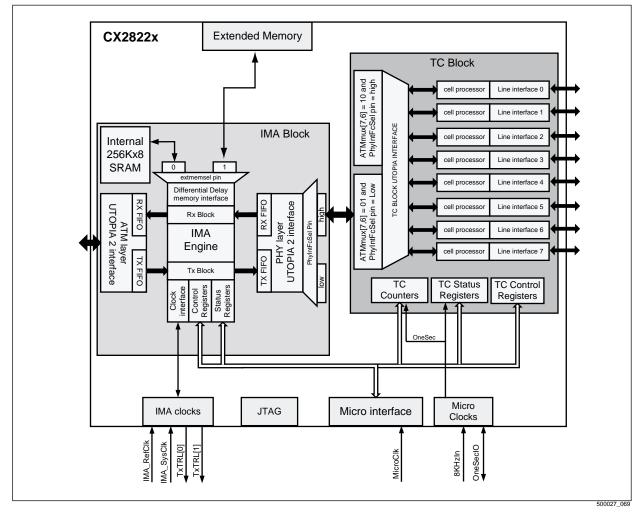

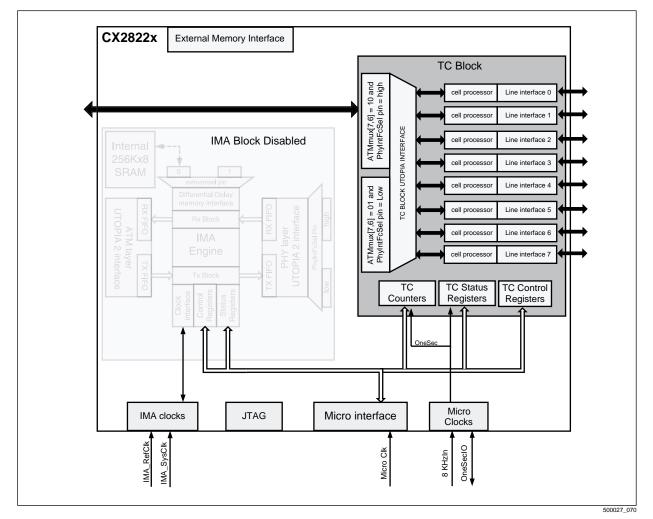

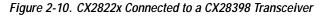

The CX2822x family of devices provides system designers with a complete integrated IMA solution for up to 32 ports. All devices include a Transmission Convergence block to perform cell delineation, on-board RAM to meet ATM forum requirements for differential delay compensation and a dual mode (UTOPIA or Serial) PHY layer interface.

Source code for all required software functions is available from Mindspeed. Since all processing intensive functions are performed in hardware, they require only minimal overhead from the system processor.

The TC block is capable of bit level cell delineation, which allows for direct connection DSL serial data streams without a frame sync pulse. Individual ports can be operated in a 'pass thru' mode without the IMA overhead.

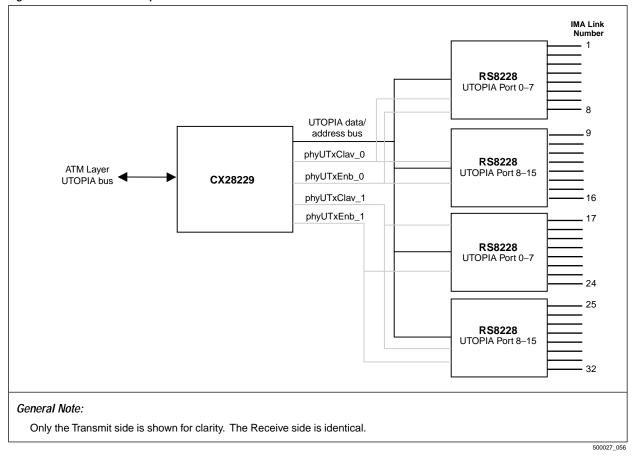

The CX28229 provides direct connection to 8 serial links or can be expanded to a 32 port IMA using the PHY side UTOPIA bus and external TC devices such as the RS8228. In addition, an external memory bus allows the differential delay memory to access up to 2 Mbytes of external RAM.

#### **Distinguishing Features**

- Complete IMA solution in a single package

- 2 port, CX28224, 17mm BGA

- 4 port, CX28225, 17mm BGA

- 8/32 port, CX28229, 17mm BGA

- Field tested software available

- Supports up to 32 ports using external TC PHYs

- Up to 16 IMA groups

- Supports the IMA standard requirements for 25 ms differential delay with 256K Internal memory

- Memory expandable to 2 M bytes via external bus (CX28229 only)

- UTOPIA level 2 interfaces

- Glueless interface to Mindspeed Framers

- Octet or Bit level cell delineation

- Variable link data rates (64K–3.072 Mb/s)

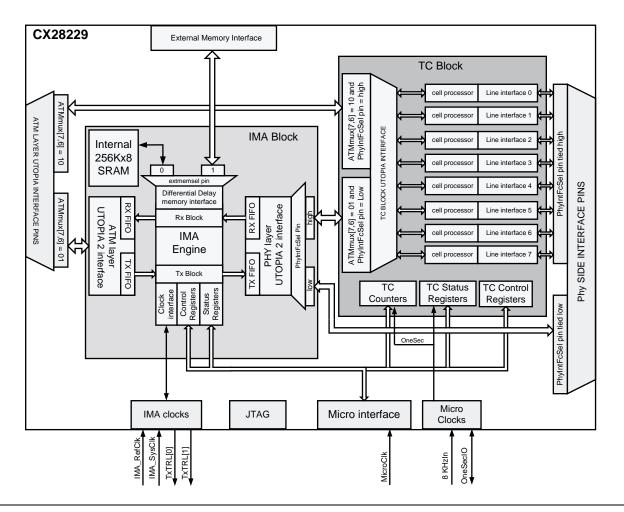

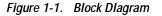

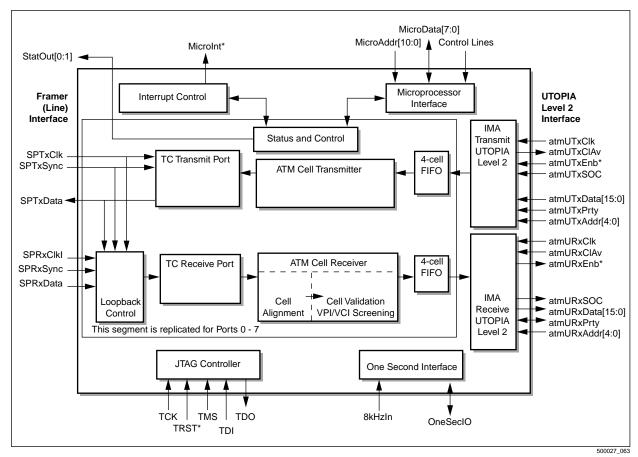

#### Functional Block Diagram

#### **IMA Features**

- Field proven design

- All software available

- Supports variable link data rates (64K– 3.072 Mb/s)

- Internal memory

- Connects directly to the Mindspeed SARs for inexpensive CPE solutions

- CX28224 2 ports

- CX28225 4 ports

- CX28229 32 ports

- Memory expandable to 2 M bytes via external bus

- Up to 16 independent groups (using external PHYs): Each group can have up to 8 links.

- Supports IMA versions 1.0 and 1.1

- Fractional T1/E1

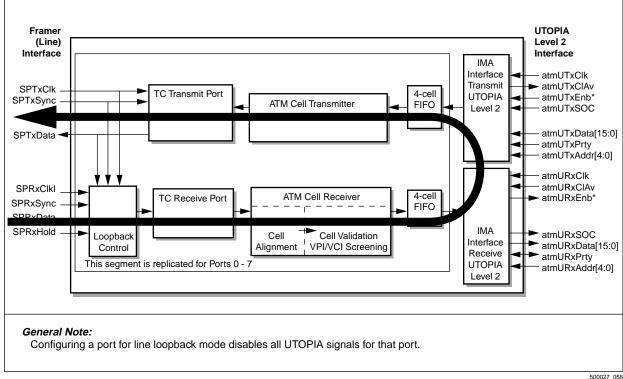

#### Cell Delineation Section

- Supports ATM cell interface for:

- Circuit-based physical layer

- Cell-based physical layer

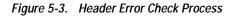

- Performs single-bit HEC correction and single- or multiple-bit detection

- Inserts headers and generates HEC

- Direct connection to external

- Mindspeed components for:

- T1/E1

- xDSL

- General purpose mode

- Byte-level or bit-level cell delineation

#### **Control and Status**

#### Microprocessor Interface

- Asynchronous SRAM-like interface mode

- Synchronous, glueless Bt8233/RS8234 SAR interface mode

- 8-bit data bus

- Open-drain interrupt output

- Open-drain ready output

- ♦ 8–33 MHz operation

- All control registers are read/write

#### UTOPIA Interfaces

- UTOPIA Level 2 Interface to ATM Layer:

8/16 bit operation

- 50 MHz

- PHY-side UTOPIA Interface:

- 8-bit UTOPIA Level 2

- Supports 32 ports via dual CLAV and Enable lines

#### **Counters/Status Register Section**

- Summary interrupt indications

- Configuration of interrupt enables

- One-second counter latching

- Counters for:

- LOCD events

- Corrected HEC errors

- Uncorrected HEC errors

- Transmitted cells

- Matching received cells

- Non-matching received cells

## Contents

| Figur | es.                                                                                                                | xi                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table | es                                                                                                                 | xiii                                                                                                                                                                                                                                                                                                                                                                                    |

| 1     | Intro                                                                                                              | duction to IMA.                                                                                                                                                                                                                                                                                                                                                                         |

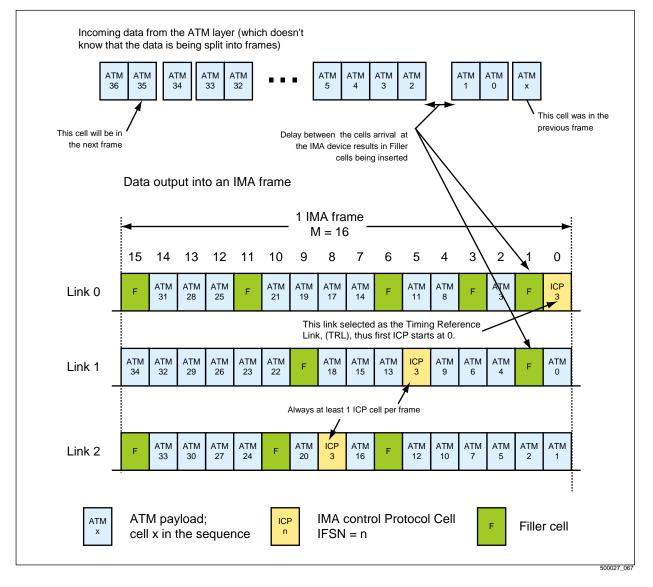

|       | 1.1                                                                                                                | Introduction To Inverse Multiplexing for ATM1-21.1.1IMA Framing.1-41.1.2IMA Control Protocol Cells1-51.1.3Link State Machine1-81.1.4Transmit Clocks1-81.1.5Differential Delay.1-9Software Overview.1-101.2.1Software Subsystems1-121.2.2Configuration (CF)1-121.2.3Diagnostics (DG)1-121.2.4Failure Monitoring (FM)1-131.2.5Performance Monitoring (PM)1-131.2.6Group State Machine1-13 |

| 2     | CX28                                                                                                               | 822x Hardware Description                                                                                                                                                                                                                                                                                                                                                               |

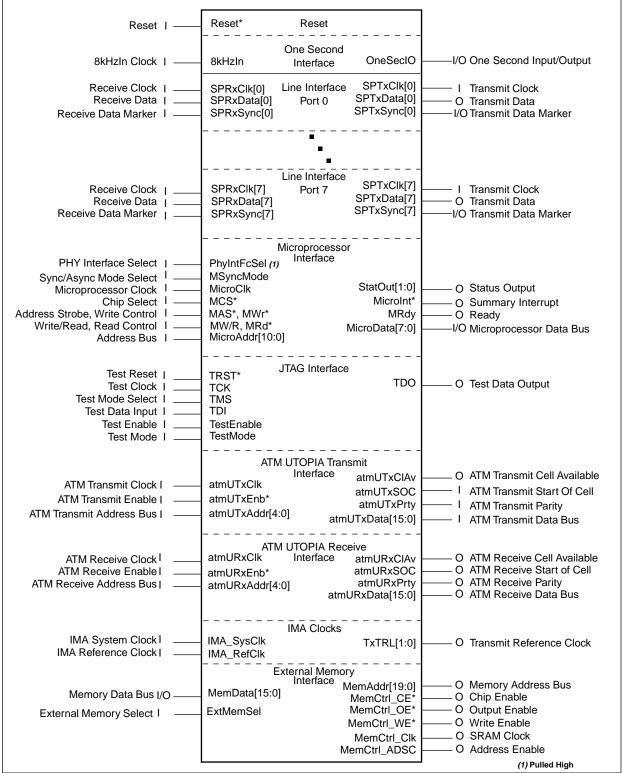

|       | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> <li>2.5</li> <li>2.6</li> <li>2.7</li> <li>2.8</li> </ol> | Logic Diagram2-1Pin Diagram and Definitions (UTOPIA-to-UTOPIA Configuration)2-3Pin Diagram and Definitions (UTOPIA-to-Serial Configuration)2-18Stand Alone Cell Delineation2-34Source Loopback (UTOPIA-to-Serial Configuration Only)2-35Far-End Line Loopback (Serial Configuration Only)2-36Application Overview2-37Reference Designs2-37                                              |

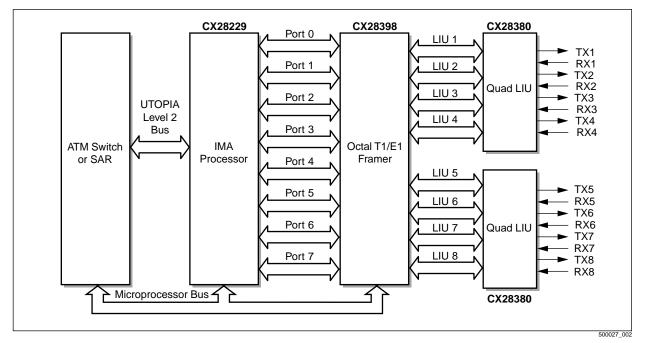

| 3     | IMA                                                                                                                | Clocks                                                                                                                                                                                                                                                                                                                                                                                  |

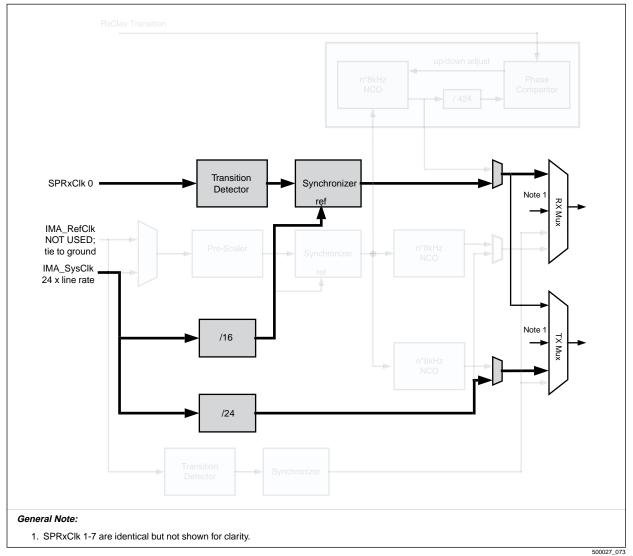

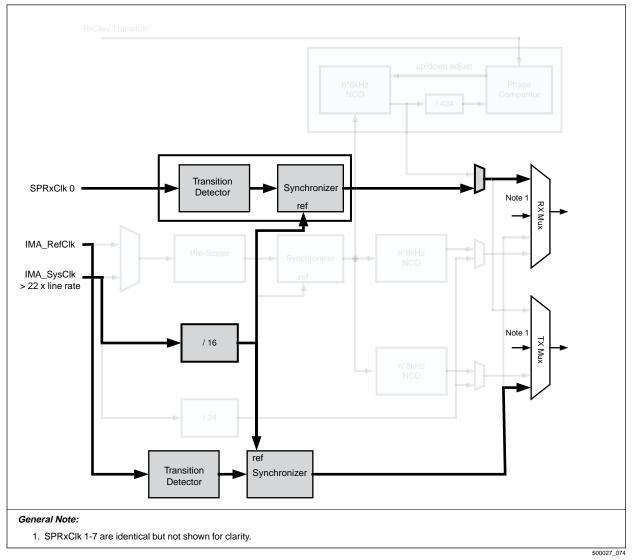

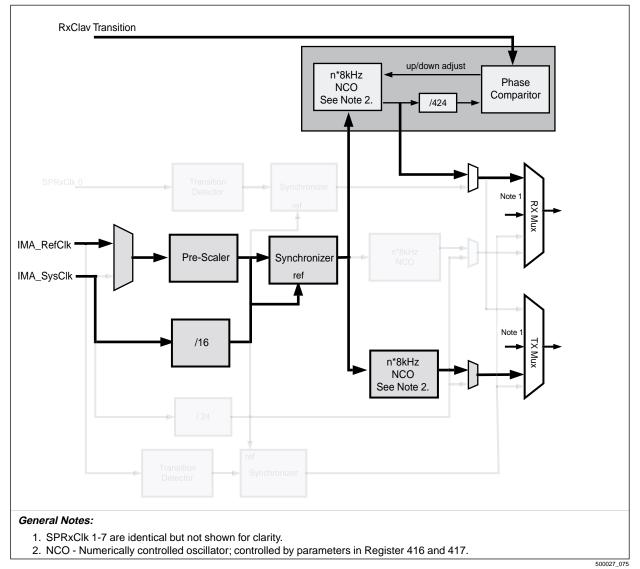

|       | 3.1                                                                                                                | Common Applications3-43.1.1T1/E1 Using Internal Serial Ports3-43.1.1.1Using IMA_SysClk as the Transmit Clock3-43.1.1.2Using IMA_RefClk as the Transmit Clock3-63.1.2DSL/T1/E1 Using UTOPIA-to-UTOPIA Interfaces3-8                                                                                                                                                                      |

| 4 | JTOPIA Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | l                                         |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

|   | I.1General UTOPIA Operation4-2I.2UTOPIA 8-bit and 16-bit Bus Widths4-2I.3IMA UTOPIA4-3I.4TC Block UTOPIA4-3I.5PHY Side UTOPIA4-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2<br>3<br>3<br>5                          |

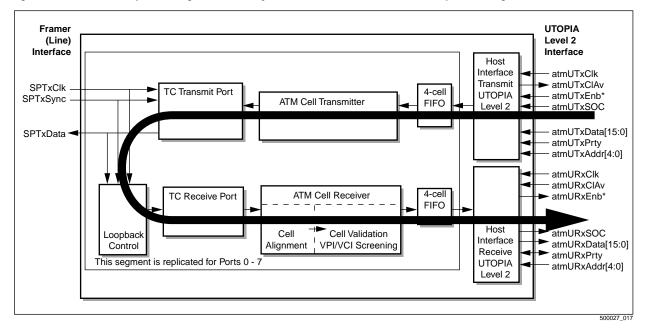

| 5 | Fransmission Convergence Block    5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                         |

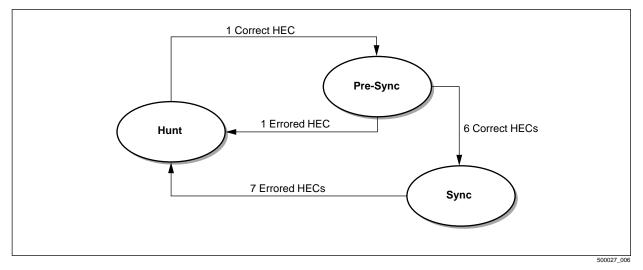

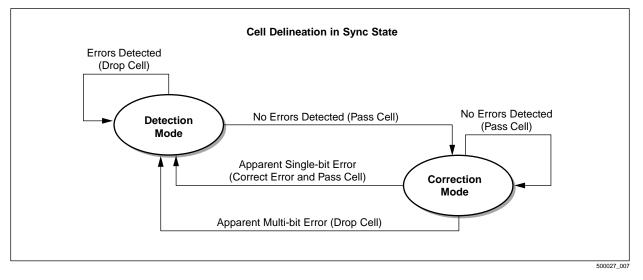

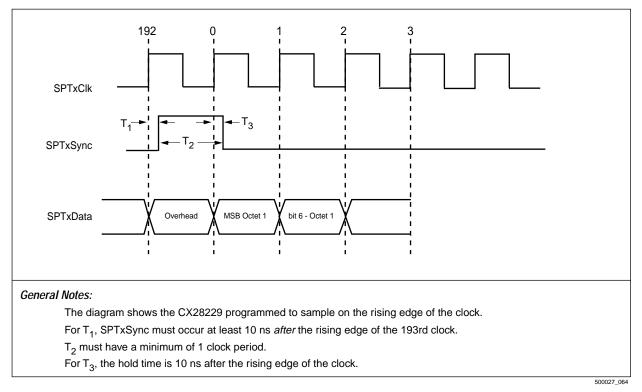

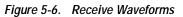

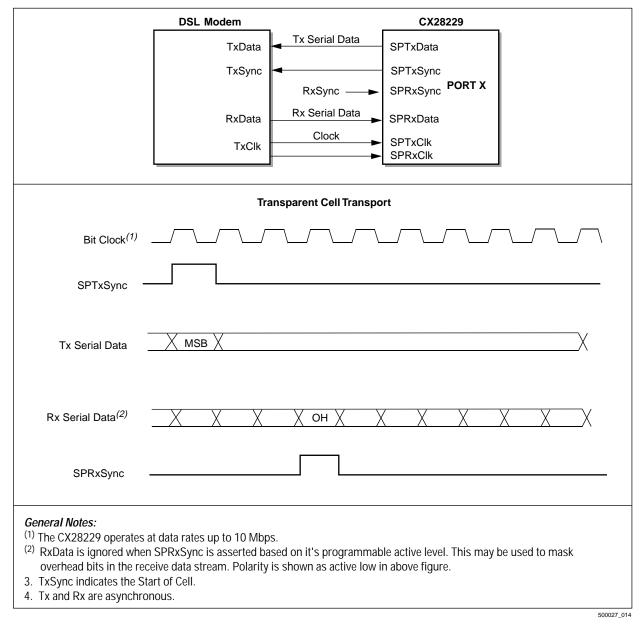

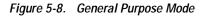

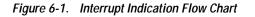

|   | 5.1       ATM Cell Transmitter       5-1         5.1.1       HEC Generation       5-2         5.2       ATM Cell Receiver       5-2         5.2.1       Cell Delineation       5-3         5.2.2       Processing Non-Standard Traffic Using the CX28229       5-4         5.2.3       Cell Screening       5-6         5.2.4       Cell Scrambler       5-7         5.2.4.1       SSS Scrambling       5-7         5.2.5.5       Framing Modes (UTOPIA-to-Serial Configuration)       5-6         5.2.5.2       DSL Mode Interface       5-11         5.2.5.2       DSL Mode Interface       5-11         5.2.5.3       General Purpose Mode Interface       5-12                                                                                         | 2<br>3<br>4<br>6<br>7<br>7<br>8<br>8<br>1 |

| 6 | General Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                           |

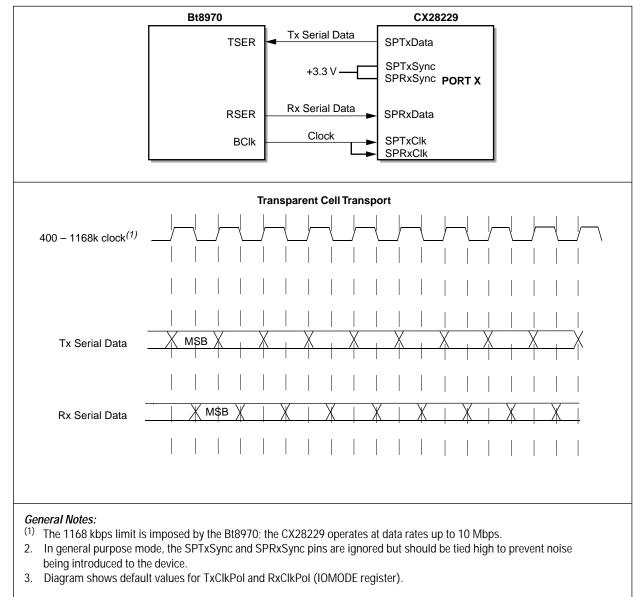

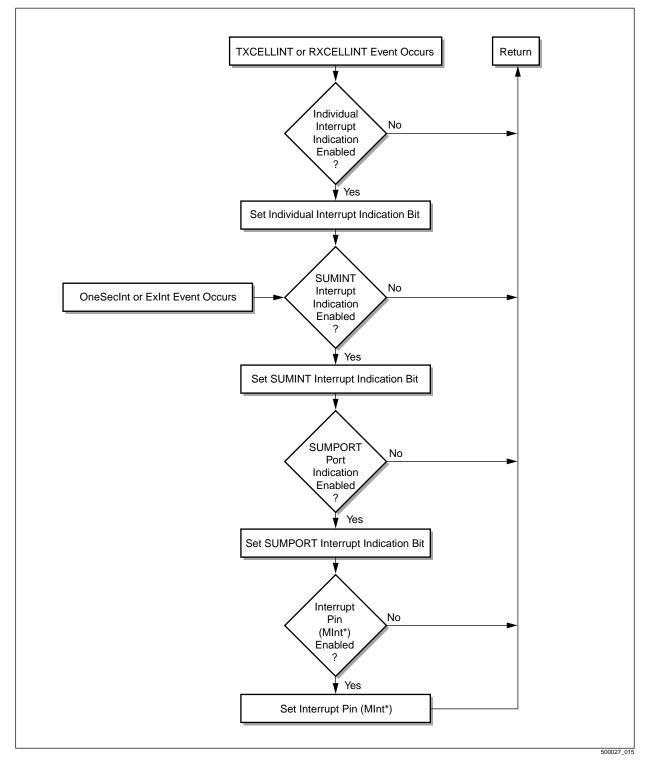

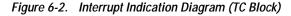

|   | b.1       Micro Interface       6-1         6.1.1       Resets       6-1         6.1.2       Counters (TC Block Only)       6-2         6.1.2.1       One-second Latching       6-2         6.1.2.2       Interrupts       6-3         6.1.2.3       Interrupt Servicing       6-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1<br>1<br>2<br>3                          |

| 7 | Registers.7-10x00—SUMINT (Summary Interrupt Indication Status Register).7-330x01—ENSUMINT (Summary Interrupt Control Register).7-340x04—PMODE (Port Mode Control Register)7-350x05—IOMODE (Input/Output Mode Control Register)7-360x08—CGEN (Cell Generation Control Register)7-370x09—HDRFIELD (Header Field Control Register)7-360x0A—IDLPAY (Transmit Idle Cell Payload Control Register)7-360x0B—ERRPAT (Error Pattern Control Register)7-360x0C—CVAL (Cell Validation Control Register)7-360x0D—UTOP1 (UTOPIA Control Register 1)7-400x0F—UDF2 (UDF2 Control Register)7-410x10—TXHDR1 (Transmit Cell Header Control Register 1)7-410x11—TXHDR2 (Transmit Cell Header Control Register 2)7-420x12—TXHDR3 (Transmit Cell Header Control Register 3)7-42 | 345678899001122                           |

|   | 0x13—TXHDR4 (Transmit Cell Header Control Register 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3                                         |

| 0x14—TXIDL1 (Transmit Idle Cell Header Control Register 1)7-43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x15—TXIDL2 (Transmit Idle Cell Header Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 0x16—TXIDL3 (Transmit Idle Cell Header Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 0x17—TXIDL4 (Transmit Idle Cell Header Control Register 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0x18—RXHDR1 (Receive Cell Header Control Register 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0x19—RXHDR2 (Receive Cell Header Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0x1A—RXHDR3 (Receive Cell Header Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0x1B—RXHDR4 (Receive Cell Header Control Register 4)7-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0x1C—RXMSK1 (Receive Cell Mask Control Register 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 0x1D—RXMSK2 (Receive Cell Mask Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 0x1E—RXMSK3 (Receive Cell Mask Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0x1F—RXMSK4 (Receive Cell Mask Control Register 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| 0x20—RXIDL1 (Receive Idle Cell Header Control Register 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x21—RXIDL2 (Receive Idle Cell Header Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x22—RXIDL3 (Receive Idle Cell Header Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x23—RXIDL4 (Receive Idle Cell Header Control Register 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x24—IDLMSK1 (Receive Idle Cell Mask Control Register 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0x25—IDLMSK2 (Receive Idle Cell Mask Control Register 2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0x26—IDLMSK3 (Receive Idle Cell Mask Control Register 3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0x27—IDLMSK4 (Receive Idle Cell Mask Control Register 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 0x28—ENCELLT (Transmit Cell Interrupt Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 0x29—ENCELLR (Receive Cell Interrupt Control Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 0x2C—TXCELLINT (Transmit Cell Interrupt Indication Status Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 0x2D—RXCELLINT (Receive Cell Interrupt Indication Status Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0x2E—TXCELL (Transmit Cell Status Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 0x2F—RXCELL (Receive Cell Status Register)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 0x2F—RXCELL (Receive Cell Status Register)       7-56         0x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])       7-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [High Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [High Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-600x38—RXCNTL (Received Cell Counter [Low Byte])7-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [High Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x39—RXCNTL (Received Cell Counter [Low Byte])7-61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-600x38—RXCNTL (Received Cell Counter [Low Byte])7-610x39—RXCNTM (Received Cell Counter [Mid Byte])7-610x3A—RXCNTH (Received Cell Counter [Mid Byte])7-610x3A—RXCNTH (Received Cell Counter [Mid Byte])7-61                                                                                                                                                                                                                                                                                                                                  |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x38—RXCNTL (Received Cell Counter [Low Byte])7-610x3A—RXCNTH (Received Cell Counter [Mid Byte])7-610x3A—RXCNTH (Received Cell Counter [Mid Byte])7-610x3A—RXCNTH (Received Cell Counter [High Byte])7-610x3A—RXCNTH (Received Cell Counter [High Byte])7-610x3A—RXCNTH (Received Cell Counter [High Byte])7-620x3B—UNCCNT (Uncorrected HEC Error Counter)7-62                                                                                                                                                                            |  |

| 0x2FRXCELL (Receive Cell Status Register)7-560x30IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33LOCDCNT (LOCD Event Counter)7-580x34TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36TXCNTH (Transmitted Cell Counter [High Byte])7-600x37CORRCNT (Corrected HEC Error Counter)7-610x39RXCNTH (Received Cell Counter [Low Byte])7-610x34RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Low Byte])7-610x33RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Low Byte])7-620x33RXCNTH (Non-matching Cell Counter [Low Byte])7-63                                                                                                                                                                                       |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x38—RXCNTL (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Mid Byte])7-610x33—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-620x3B—UNCCNT (Uncorrected HEC Error Counter)7-620x3B—UNCCNT (Uncorrected HEC Error Counter)7-630x3D—NONCNTH (Non-matching Cell Counter [Low Byte])7-63                                                                         |  |

| 0x2FRXCELL (Receive Cell Status Register)7-560x30IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33LOCDCNT (LOCD Event Counter)7-580x34TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36TXCNTH (Transmitted Cell Counter [High Byte])7-600x37CORRCNT (Corrected HEC Error Counter)7-610x39RXCNTH (Received Cell Counter [Low Byte])7-610x34RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Low Byte])7-610x33RXCNTH (Received Cell Counter [Mid Byte])7-610x33RXCNTH (Received Cell Counter [Low Byte])7-620x33RXCNTH (Non-matching Cell Counter [Low Byte])7-63                                                                                                                                                                                       |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x38—RXCNTL (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Mid Byte])7-610x33—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-620x3B—UNCCNT (Uncorrected HEC Error Counter)7-620x3B—UNCCNT (Uncorrected HEC Error Counter)7-630x3D—NONCNTH (Non-matching Cell Counter [Low Byte])7-63                                                                         |  |

| 0x2F—RXCELL (Receive Cell Status Register)7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [High Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x39—RXCNTL (Received Cell Counter [Mid Byte])7-610x34—RXCNTH (Received Cell Counter [Mid Byte])7-610x38—RXCNTH (Received Cell Counter [Low Byte])7-610x38—RXCNTH (Received Cell Counter [Low Byte])7-610x38—RXCNTH (Received Cell Counter [High Byte])7-620x38—UNCCNT (Uncorrected HEC Error Counter)7-620x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x200—MODE (Device Mode Control Register)7-63                                                                                                                           |  |

| 0x2F—RXCELL (Receive Cell Status Register).7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x38—RXCNTL (Received Cell Counter [Low Byte])7-610x39—RXCNTM (Received Cell Counter [Mid Byte])7-610x34—RXCNTH (Received Cell Counter [Mid Byte])7-610x34—RXCNTH (Received Cell Counter [Low Byte])7-610x39—RXCNTM (Received Cell Counter [Mid Byte])7-620x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x200—MODE (Device Mode Control Register)7-630x201—PHYINTFC (PHY-side Interface Control Register)7-650x202—ATMINTFC (ATM-side Interface Control Register)7-65                                                           |  |

| 0x2F—RXCELL (Receive Cell Status Register).7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-600x38—RXCNTL (Received Cell Counter [Mid Byte])7-610x39—RXCNTM (Received Cell Counter [Mid Byte])7-610x30—RXCNTH (Received Cell Counter [High Byte])7-610x30—RXCNTH (Received Cell Counter [Mid Byte])7-620x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x200—MODE (Device Mode Control Register)7-630x201—PHYINTFC (PHY-side Interface Control Register)7-650x203—OUTSTAT (Output Status Control Register)7-650x203—OUTSTAT (Output Status Control Register)7-65                                                                |  |

| 0x2F—RXCELL (Receive Cell Status Register).7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [High Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-610x39—RXCNTL (Received Cell Counter [Low Byte])7-610x30—RXCNTH (Received Cell Counter [Mid Byte])7-610x30—RXCNTH (Received Cell Counter [Low Byte])7-610x30—RXCNTH (Received Cell Counter [Low Byte])7-630x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x200—MODE (Device Mode Control Register)7-650x202—ATMINTFC (ATM-side Interface Control Register)7-650x203—OUTSTAT (Output Status Control Register)7-650x204—SUMPORT (Summary Port Interrupt Status Register)7-66 |  |

| 0x2F—RXCELL (Receive Cell Status Register).7-560x30—IDLCNTL (Idle Cell Receive Counter [Low Byte])7-570x31—IDLCNTM (Idle Cell Receive Counter [Mid Byte])7-570x32—IDLCNTH (Idle Cell Receive Counter [High Byte])7-580x33—LOCDCNT (LOCD Event Counter)7-580x34—TXCNTL (Transmitted Cell Counter [Low Byte])7-590x35—TXCNTM (Transmitted Cell Counter [Mid Byte])7-590x36—TXCNTH (Transmitted Cell Counter [Mid Byte])7-600x37—CORRCNT (Corrected HEC Error Counter)7-600x38—RXCNTL (Received Cell Counter [Mid Byte])7-610x39—RXCNTM (Received Cell Counter [Mid Byte])7-610x30—RXCNTH (Received Cell Counter [High Byte])7-610x30—RXCNTH (Received Cell Counter [Mid Byte])7-620x30—NONCNTL (Non-matching Cell Counter [Low Byte])7-630x200—MODE (Device Mode Control Register)7-630x201—PHYINTFC (PHY-side Interface Control Register)7-650x203—OUTSTAT (Output Status Control Register)7-650x203—OUTSTAT (Output Status Control Register)7-65                                                                |  |

| 7.1 | IMA Subsystem Registers    7-68                                                                   |

|-----|---------------------------------------------------------------------------------------------------|

|     | 0x400—IMA_VER_1_CONFIG (IMA Type and Version Code I)                                              |

|     | 0x401—IMA_VER_2_CONFIG (IMA Version Codes II and III)                                             |

|     | 0x402—IMA_SUBSYS_CONFIG (IMA Configuration Control)                                               |

|     | 0x403—IMA_MISC_STATUS (IMA Miscellaneous Status)                                                  |

|     | 0x404—IMA_MISC_CONFIG (IMA Miscellaneous Control)                                                 |

|     | 0x405—IMA_MEM_LOW_TEST (IMA Memory Test Address                                                   |

|     | (Bits 0–7)) 7-70                                                                                  |

|     | 0x406—IMA_MEM_HI_TEST (IMA Memory Test Address                                                    |

|     | (Bits 8–15)) 7-70                                                                                 |

|     | 0x407—IMA_MEM_TEST_CTL (IMA Memory Test Control / Address MSBs)                                   |

|     | 0x408—IMA_MEM_TEST_DATA (IMA Memory Test Data)                                                    |

|     | 0x409—IMA_LNK_DIAG_CTL (IMA Link Diagnostic Control Register)                                     |

|     | 0x40A—IMA_LNK_DIFF_DEL (IMA Link Differential Delay Write Counter)                                |

|     | 0x40B—IMA_RCV_LNK_ANOMALIES (IMA Receive Link Anomalies)                                          |

|     | 0x40E—IMA_DIAG_XOR_BIT (IMA Diagnostic Bit)                                                       |

|     | 0x40F—IMA_DIAG (IMA Diagnostic Register)7-74                                                      |

|     | 0x410—IMA_TIM_REF_MUX_CTL_ADDR (IMA Timing Reference Multiplexer Control Address) 7-              |

|     | 75<br>Over 11 - INAA TINA DEE MULY OTH DATA (INAA Timing Deference Multiplayer Control Date) 7.7( |

|     | 0x411—IMA_TIM_REF_MUX_CTL_DATA (IMA Timing Reference Multiplexer Control Data) . 7-76             |

|     | 0x412—IMA_RX_PERSIST_CONFIG (IMA Receive Persistence Configuration)                               |

|     | 0x413—IMA_ATM_UTOPIA_BUS_CTL (IMA ATM Utopia Bus Control)                                         |

|     | 0x414—IMA_DIFF_DELAY_ADDR (IMA Differential Delay Control Address)                                |

|     | 0x415—IMA_DIFF_DELAY_DATA (IMA Differential Delay Control Data)                                   |

|     | 0x416—IMA_DSL_CLOCK_GEN_ADDR (IMA DSL Clock Generator Control)                                    |

|     | 0x417—IMA_DSL_CLOCK_GEN_DATA (IMA_DSL Clock Generator Data)                                       |

|     | 0x418—IMA_RX_TRANS_TABLE (IMA Receive Translation Table Address)                                  |

|     | 0x419—IMA_RX_ATM_TRANS_TABLE (IMA Receive ATM Translation Table Internal Channel) . 7-<br>84      |

|     | 0x41B—IMA_TX_TRANS_TABLE (IMA Transmit Translation Table Address)                                 |

|     | 0x41C—IMA_TX_ATM_TRANS_TABLE (Transmit ATM Translation Table Internal Channel) 7-86               |

|     | 0x458—IMA_RX_SOC_DETECTOR (PHY Utopia RX_SOC Detector)                                            |

| 7.2 | IMA Group                                                                                         |

|     | 0x41F—IMA_GRP_1TO4_SEM (Group Table Control I)                                                    |

|     | 0x51F—IMA_GRP_5T08_SEM (Group Table Control II (CX28229 Only))                                    |

|     | 0x61F—IMA_GRP_9T012_SEM (Group Table Control III (CX28229 Only))                                  |

|     | 0x71F—IMA_GRP_13T016_SEM (Group Table Control IV (CX28229 Only))                                  |

|     | IMA_TX_GRPn_RX_TEST_PATTERN (Transmit Group Rx Test Pattern)                                      |

|     | IMA_TX_GRPn_CTL (Transmit Group Control Register)                                                 |

|     | IMA_TX_GRPn_FIRST_PHY_ADDR (Transmit First PHY Address)                                           |

|     | IMA_TX_GRPn_ID (Transmit Group ID)                                                                |

|     | IMA_TX_GRPn_STAT_CTL (Transmit Group Status and Control)                                          |

|     | IMA_TX_GRPn_TIMING_INFO (Transmit Timing Information)                                             |

|     | IMA_TX_GRPn_TEST_CTL (Transmit Test Control)                                                      |

|     | IMA_TX_GRPn_TX_TEST_PATTERN (Transmit Group Tx Test Pattern)                                      |

|     | IMA_TX_GRPn_CELL_COUNT_LSB (Transmit Cell Count LSBs)                                             |

|     | IMA_TX_GRPn_CELL_COUNT_LSB (Transmit Cell Count MSBs)                                             |

|     |                                                                                                   |