www.DataSheet4U.com

## SONY

# **CXA2101Q**

## Multi-Component Processor (Base Band Video Signal Processor IC)

#### Description

The CXA2101Q is a bipolar IC which integrates the following functions on a single chip: base band signal processing, RGB signal processing, and video switching for 4 systems (including HV sync signal processing) using YCbCr inputs.

It was developed for multiscan TVs, and enables high-end TV systems to be configured.

#### **Features**

- I<sup>2</sup>C bus compatible

- Multiscan supported

- · Normal, PAL-FF, HD-TV supported

- · On-chip video switching for 4 systems

- On-chip automatic sync signal identification circuit (with fixed mode)

- On-chip sync separation circuit (HD supported)

- On-chip CbCr input offset adjustment circuit

- On-chip LTI, CTI circuits

- On-chip AKB system

- YCbCr input for 1 system, external YCbCr input for 1 system

- Analog RGB input for 2 systems

- Analog RGB1 forced OFF mode supported

#### **Applications**

- Multiscan TVs

- LCD projector TVs

#### Structure

Bipolar silicon monolithic IC

#### Supply voltage

9V

#### Power consumption

1.15W

#### **Absolute Maximum Ratings**

- Supply voltage

Operating temperature

Topr -20 to +75 °C

- Storage temperature

Allowable power dissipation

Tstg: -65 to +150 °C

W

(When mounted on single-layer circuit board with dimensions of 76mm × 1.14mm × 1.6thick)

#### **Recommended Operating Conditions**

Supply voltage Vcc 8.5 to 9.5 V

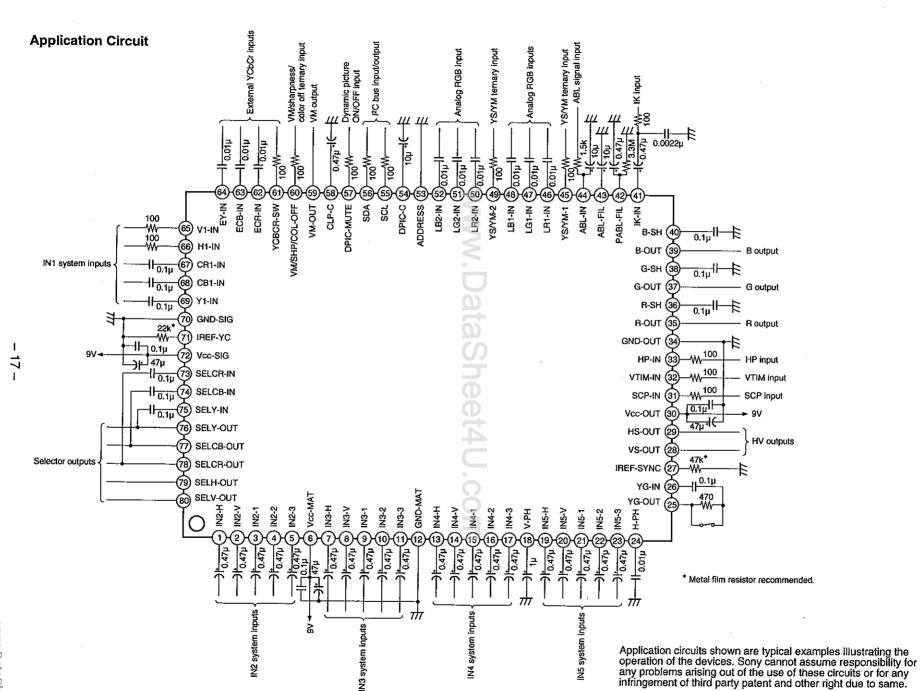

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

www.DataSheet4U.com

DataSheet4 U.com

**Block Diagram**

ECA-IN ECB-IN EY-IN

VM/SHP /COL-OFF

CLP-C

SPA

VM-OUT

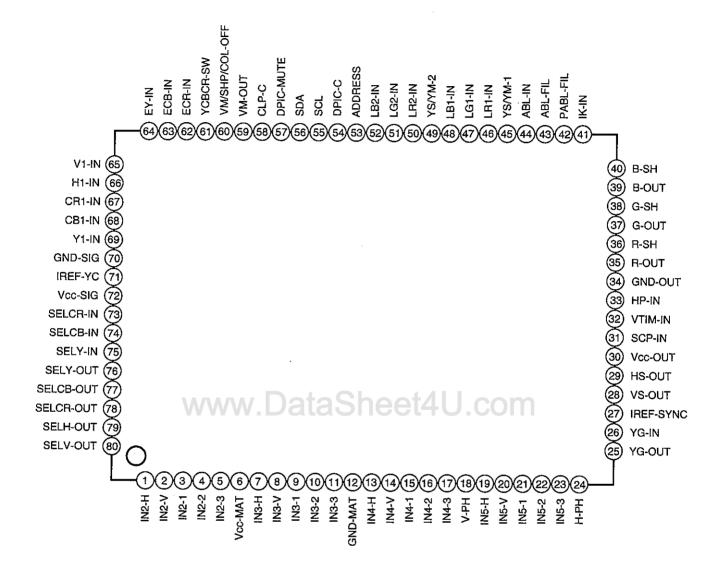

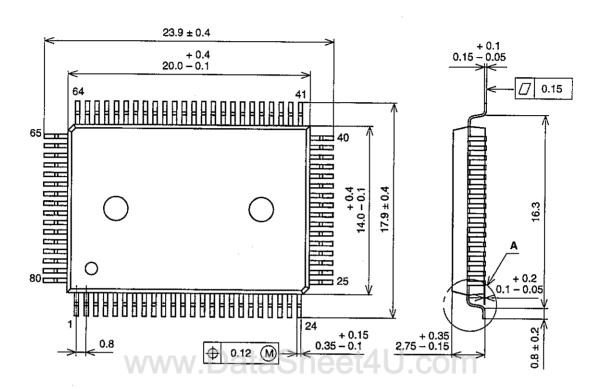

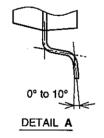

#### Pin Configuration

#### **Pin Description**

| Pin<br>No.    | Symbol                  | Equivalent circuit                                   | Description                                                                                                                                                                                                                                                                                                                                        |

|---------------|-------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | IN2-H                   | Vcc                                                  | IN2-H: Separate H sync or CS input. IN2-V: Separate V sync signal input. Input the signals through a clamping capacitor. The bottom level is clamped to 2.5V.                                                                                                                                                                                      |

| 2             | IN2-V                   | 50µА<br>50µА<br>50µА                                 | Both positive and negative polarities are supported. Input the signals at the level shown below.                                                                                                                                                                                                                                                   |

| 3<br>4<br>5   | IN2-1<br>IN2-2<br>IN2-3 | Vcc ₹100k<br>3<br>4<br>4<br>5<br>143<br>₹200k<br>T3V | IN2 system signal inputs. Input the signals through a capacitor. The pin voltage is biased to 3V. Refer to the input pin correspondence table. Set the Y input level to 0.7Vp-p and color difference input level to 0.7Vp-p using 100% color bar signals. In the case of sync on Y and sync on Green, input the signal at a sync level of 0.3Vp-p. |

| 6             | Vcc-MAT                 |                                                      | Selector system and sync processing system power supply.                                                                                                                                                                                                                                                                                           |

| 7             | IN3-H                   | Vcc                                                  | IN3-H: Separate H sync or CS input. IN3-V: Separate V sync signal input. Input the signals through a capacitor. The bottom level is clamped to 2.5V. Both positive and negative polarities are                                                                                                                                                     |

| 8             | IN3-V                   | GND 50µА                                             | supported. Input the signals at the level shown below. $IN3-H \\ 0.5Vp-p \leq IN3-V \leq 5Vp-p$                                                                                                                                                                                                                                                    |

| 9<br>10<br>11 | IN3-1<br>IN3-2<br>IN3-3 | Vcc ₹100k  9 10 143 200k T 3V                        | IN3 system signal inputs. Input the signals through a capacitor. The pin voltage is biased to 3V. Refer to the input pin correspondence table. Set the Y input level to 0.7Vp-p and color difference input level to 0.7Vp-p using 100% color bar signals. In the case of sync on Y and sync on Green, input the signal at a sync level of 0.3Vp-p. |

### Input Pin Correspondence Table (by input signal)

| mal   | 문   | nary<br>r    |   | IN2 |   |   | IN3 | - |   | IN4 |   |   | IN5 |   |

|-------|-----|--------------|---|-----|---|---|-----|---|---|-----|---|---|-----|---|

| Norma | 工   | Prin<br>colo | 1 | 2   | 3 | 1 | 2   | 3 | 1 | 2   | 3 | 1 | 2   | 3 |

| Υ     | YHD | G            | × | ×   | 0 | × | ×   | 0 | × | ×   | 0 | × | ×   | 0 |

| Cb    | Pb  | В            | × | 0   | × | × | 0   | × | × | 0   | × | × | 0   | × |

| Cr    | Pr  | R            | 0 | ×   | × | 0 | ×   | × | 0 | ×   | × | 0 | ×   | × |

$O = Input enabled; \times = input disabled$

| Pin<br>No.     | Symbol                  | Equivalent circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Description                                                                                                                                                                                                                                                                                                                                        |

|----------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12             | GND-MAT                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | GND for selector block and sync processing block.                                                                                                                                                                                                                                                                                                  |

| 13             | IN4-H                   | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IN4-H: Separate H sync or CS input. IN4-V: Separate V sync signal input. Input the signals through a clamping capacitor. The bottom level is clamped to 2.5V. Both positive and negative polarities are                                                                                                                                            |

| 14             | IN4-V                   | 50µА<br>50µА                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | supported. Input the signals at the level shown below. $!N4-H \\ 0.5Vp-p \leq \frac{1}{1N4-V} \leq 5Vp-p$                                                                                                                                                                                                                                          |

| 15<br>16<br>17 | IN4-1<br>IN4-2<br>IN4-3 | Vcc<br>15<br>16<br>17<br>143<br>★200k<br>13V<br>GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IN4 system signal inputs. Input the signals through a capacitor. The pin voltage is biased to 3V. Refer to the input pin correspondence table. Set the Y input level to 0.7Vp-p and color difference input level to 0.7Vp-p using 100% color bar signals. In the case of sync on Y and sync on Green, input the signal at a sync level of 0.3Vp-p. |

| 18             | V-PH                    | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | et4U.com Capacitor connection for holding V sync peak.                                                                                                                                                                                                                                                                                             |

| 19             | IN5-H                   | Vcc                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IN5-H: Separate H sync or CS input. IN5-V: Separate V sync signal input. Input the signals through a clamping capacitor. The bottom level is clamped to 2.5V. Both positive and negative polarities are                                                                                                                                            |

| 20             | IN5-V                   | GND 50μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | supported. Input the signals at the level shown below. IN5-H 0.5Vp-p ≤ IN5-V ≤ 5Vp-p                                                                                                                                                                                                                                                               |

| 21<br>22<br>23 | IN5-1<br>IN5-2<br>IN5-3 | Vcc ₹100k<br>(21)<br>(22)<br>(23)<br>(23)<br>(33)<br>(34)<br>(34)<br>(34)<br>(34)<br>(35)<br>(44)<br>(44)<br>(54)<br>(64)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74)<br>(74) | IN5 system signal inputs. Input the signals through a capacitor. The pin voltage is biased to 3V. Refer to the input pin correspondence table. Set the Y input level to 0.7Vp-p and color difference input level to 0.7Vp-p using 100% color bar signals. In the case of sync on Y and sync on Green, input the signal at a sync level of 0.3Vp-p. |

| Pin<br>No. | Symbol           | Equivalent circuit                                            | Description                                                                                                                                                                                                                         |

|------------|------------------|---------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24         | H-PH             | Vcc                                                           | Capacitor connection for holding H sync peak.                                                                                                                                                                                       |

| 25         | YG-OUT           | Vcc<br>\$500<br>1k ₹30k<br>30k<br>GND                         | Composite video signal output for sync separation. The signal selected by I <sup>2</sup> C bus "HYSW" is amplified to 5dB and output.                                                                                               |

| 26         | YG-IN            | Vcc<br>26<br>W<br>1.2k<br>1.2k<br>1.2k<br>3μA<br>1.2k<br>25μA | Composite video signal input for sync separation.  Normally, the signal output at Pin 25 is input through a clamping capacitor.  The sync tip is clamped to 2.5V.  Input the signal at a sync level of 0.5 to 0.6Vp-p.              |

| 27         | IREF-SYNC        | Vcc 4k  (27)  (37)  (4.7V)                                    | For setting the reference current inside the IC (mainly, sync signal processing system). Connect to GND via the 47kΩ resistor (such as a metal film resistor) with an error of less than 1%. The pin voltage is approximately 4.6V. |

| 28<br>29   | VS-OUT<br>HS-OUT | 1.2k \$ 50k                                                   | Either IN1 system HV or IN2 to IN5 system selector output HV signals are selected by I <sup>2</sup> C bus "YCBCR/MAT" and output with a positive polarity.  VoH ≥ 3.5V  VoL ≤ 0.6V                                                  |

| 30         | Vcc-OUT          |                                                               | RGB system power supply.                                                                                                                                                                                                            |

| Pin<br>No.     | Symbol                  | Equivalent circuit                                        | Description                                                                                                                                                                                                                                                           |

|----------------|-------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

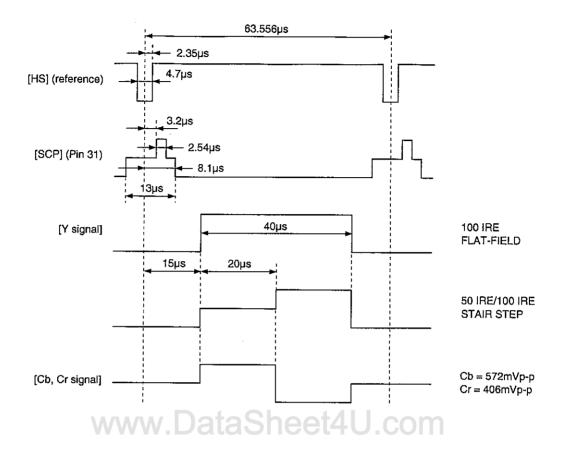

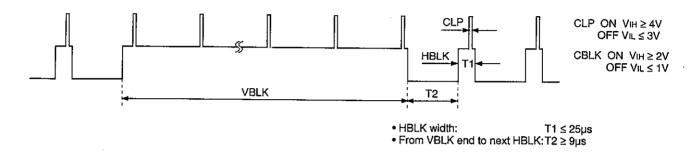

| 31             | SCP-IN                  | Vcc 50μA 50μA 60μA 60μA 60μA                              | Sand castle pulse input. Used for AKB reference pulse generation and RGBOUT blanking. The input SCP definition is given on page 30. CLAMP ON VIH ≥ 4V OFF VIL ≤ 3V Composite BLK ON VIH ≥ 2V OFF VIL ≤ 1V                                                             |

| 32             | VTIM-IN                 | Vcc 100μA 32 143 8k                                       | V timing pulse input. Used to generate AKB reference pulses in the V compression mode (I²C bus "AKB-T=1"). Ground the pin when it is not going to be used. VIH ≥ 3.5V VIL ≤ 1.5V                                                                                      |

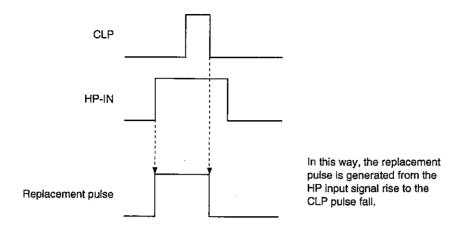

| 33             | HP-IN                   | Vcc 100µA 143 8k                                          | H pulse input. Used to generate AKB reference pulses in the V compression mode (I²C bus "AKB-T=1"). Also used to generate replacement pulses for the color difference input clamping circuit. Ground the pin when it is not going to be used.  VIH ≥ 3.5V  VIL ≤ 1.5V |

| 34             | GND-OUT                 |                                                           | RGB system ground.                                                                                                                                                                                                                                                    |

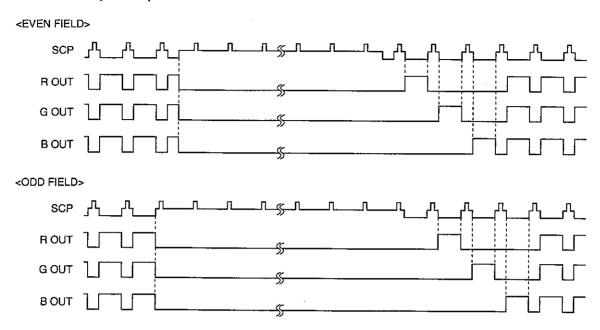

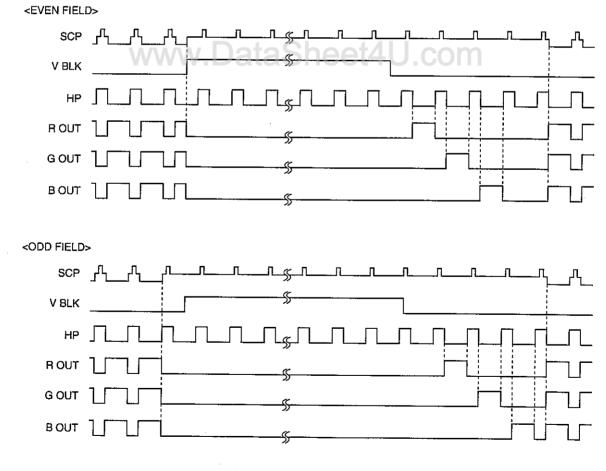

| 35<br>37<br>39 | R-OUT<br>G-OUT<br>B-OUT | Vcc \$100<br>35<br>37<br>39<br>100<br>100<br>3.5mA<br>GND | RGB signal outputs. Signals are output at 2.6Vp-p when 100 IRE white signals are input (only when the i <sup>2</sup> C bus has been set to the data on page 16).                                                                                                      |

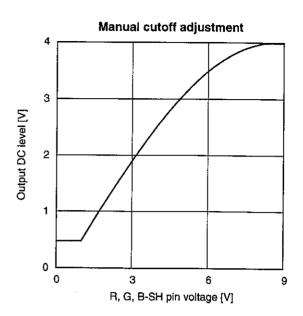

| 36<br>38<br>40 | R-SH<br>G-SH<br>B-SH    | Vcc 1.2k 40 1.2k GND                                      | Sample and hold for AKB of RGB. These connect the capacitors to GND. When AKB is not used, the RGB DC level can be set by applying DC to each pin.                                                                                                                    |

| Pin<br>No. | Symbol   | Equivalent circuit                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------|----------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 41         | IK-IN    | Vcc (41) (1.2k) ≤16k                           | The reference pulse is returned to this pin. Cathode current Ik of the CRT is converted into a voltage and input to the pin through a capacitor. It is clamped to 3.4V at the V retrace timing of the V blanking portion.                                                                                                                                                                                                                                                                                                |

| 42         | PABL-FIL | 42 W 143 S S S S S S S S S S S S S S S S S S S | Peak hold for peak ABL. This pin connects a capacitor and resistor to GND to configure a low-pass filter.                                                                                                                                                                                                                                                                                                                                                                                                                |

| 43         | ABL-FIL  | Vcc                                            | This pin connects a capacitor to configure a low-pass filter for the ABL control signals.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 44         | ABL-IN   | 44) 143 GND                                    | ABL control signal input. It operates as an average value type. The ABLIN threshold voltage can be varied by I <sup>2</sup> C bus "ABL-TH".                                                                                                                                                                                                                                                                                                                                                                              |

| 45         | YS/YM-1  | Vcc  45  143  13k  7k                          | YM1/YS1 control signal input.  Ternary inputs are supported.  The pin also serves to set VM off when YM or YS has reached the respective value.  The mode in which VM is not set off by YM is established when I²C bus "YM-VM = 1" has been set. <ys1sw>  YS1: ON VIH ≥ 3V This selects LRGB1.  YS1: OFF VIL ≤ 1.5V This selects the internal RGB signals.  <ym1sw>  YM1: ON VIH ≥ 1.1V This sets the internal RGB signals to -9.5dB.  YM1: OFF VIL ≤ 0.3V The internal RGB signals pass through at 0dB.</ym1sw></ys1sw> |

| Pin<br>No.     | Symbol                     | Equivalent circuit                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|----------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 46<br>47<br>48 | LR1-IN<br>LG1-IN<br>LB1-IN | Vcc<br>46<br>47<br>48<br>100μA               | Analog RGB1 signal inputs. The 0.7Vp-p 100 IRE (no sync) signal is input through a capacitor. The pedestal is clamped to 4.9V.                                                                                                                                                                                                                                                                                                                                                                                           |

| 49             | YS/YM-2                    | Vcc  49  143  13k  ₹7k                       | YM2/YS2 control signal input.  Ternary inputs are supported.  The pin also serves to set VM off when YM or YS has reached the respective value.  The mode in which VM is not set off by YM is established when I²C bus "YM-VM = 1" has been set. <ys2sw>  YS2: ON VIH ≥ 3V This selects LRGB2.  YS2: OFF VIL ≤ 1.5V This selects the internal RGB signals.  <ym2sw>  YM2: ON VIH ≥ 1.1V This sets the internal RGB signals to -9.5dB.  YM2: OFF VIL ≤ 0.3V The internal RGB signals pass through at 0dB.</ym2sw></ys2sw> |

| 50<br>51<br>52 | LR2-IN<br>LG2-IN<br>LB2-IN | Vcc<br>(50)<br>(51)<br>(52)<br>1.2k<br>200μA | Analog RGB2 signal inputs. The 0.7Vp-p 100 IRE (no sync) signal is input through a capacitor. The pedestal is clamped to 4.6V (I <sup>2</sup> C bus "LRGB2-LEVEL = F").                                                                                                                                                                                                                                                                                                                                                  |

| 53             | ADDRESS                    | Vcc                                          | I <sup>2</sup> C bus slave address setting.<br>86h: V <sub>IH</sub> ≥ 3.5V<br>84h: V <sub>IL</sub> ≤ 1.5V                                                                                                                                                                                                                                                                                                                                                                                                                |

| 54             | DPIC-C                     | Vcc<br>\$20k \$16k<br>W 2k<br>50µA<br>GND    | This connects a capacitor to GND for detecting black in the dynamic picture (black expansion).                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Pin<br>No. | Symbol    | Equivalent circuit                      | Description                                                                                                                                                       |

|------------|-----------|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 55         | SCL       | Vcc ——————————————————————————————————— | Input for SCL (Serial Clock) complying with I <sup>2</sup> C bus standard. VIH ≥ 3V VIL ≤ 1.5V                                                                    |

| 56         | SDA       | Vcc                                     | Input for SDA (Serial Data) complying with I <sup>2</sup> C bus standard.  VIH ≥ 3V  VIL ≤ 1.5V  VOL ≤ 0.6V                                                       |

| 57         | DPIC-MUTE | 57 W Shed                               | Muting of the dynamic picture (black expansion) can be controlled by this pin. MUTE: ON VIH ≥ 1V MUTE: OFF VIL ≤ 0.4V                                             |

| 58         | CLP-C     | GND SR                                  | Y system clamping capacitor connecting pin. Also used as a pin to connect the capacitor which sets the DC transmission rate.                                      |

| 59         | VM-OUT    | Vcc \$500<br>1k \$30k<br>59<br>800µA    | VM output. The differential waveforms of the Y signal are output with a positive polarity. Their amplitude and phase can be adjusted by the I <sup>2</sup> C bus. |

| Pin<br>No.     | Symbol                    | Equivalent circuit                      | Description                                                                                                                                                                                                                                    |

|----------------|---------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60             | VM/SHP/<br>COL-OFF        | Vcc 60 W 50k Sok GND                    | For turning off the VM, sharpness and color. Ternary inputs are supported. COL: OFF VIH ≥ 4.3V ON VIL ≤ 3V VM/SHP: OFF VIH ≥ 2.8V ON VIL ≤ 1.4V                                                                                                |

| 61             | YCBCR-SW                  | 61 W 20k 4.7V T                         | This pin switches the signal which has been input to the INT/EXT switch. The external input is selected when it is high. EXT: ON VIH ≥ 2V EXT: OFF VIL ≤ 1V                                                                                    |

| 62<br>63<br>64 | ECR-IN<br>ECB-IN<br>EY-IN | Vcc<br>62<br>63<br>1.2k<br>70k<br>100μA | External YCbCr inputs.  0.7Vp-p 100 IRE signals (but only with 100% color bars for CbCr) are supplied for YCbCr together through a capacitor. In the case of sync on Y, reduce the sync level to 0.3Vp-p. The pedestal is clamped to 4.9V.     |

| 65<br>66       | V1-IN<br>H1-IN            | GND                                     | HV inputs for IN1 system.<br>Input the signals with a negative polarity.<br>VIH ≥ 3V<br>VIL ≤ 1V                                                                                                                                               |

| 67<br>68<br>69 | CR1-IN<br>CB1-IN<br>Y1-IN | 67 W 1.2k 100k 70k 2.5V 70k             | YCbCr inputs of IN1 system. 0.7Vp-p 100 IRE signals (but only with 100% color bars for CbCr) are supplied for YCbCr together through a capacitor. In the case of sync on Y, reduce the sync level to 0.3Vp-p. The pedestal is clamped to 4.9V. |

| 70             | GND-SIG                   |                                         | GND for Y color difference signal processing system.                                                                                                                                                                                           |

| Pin<br>No.     | Symbol                             | Equivalent circuit                      | Description                                                                                                                                                                                                                                                                                                                                                    |

|----------------|------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71             | IREF-YC                            | Vcc \$50k<br>143 4V T                   | For setting the reference current inside the IC (mainly, Y color difference signal processing system).  Connect to GND via the 22kΩ resistor (such as a metal film resistor) with an error of less than 1%.  The pin voltage is approximately 2.6V.                                                                                                            |

| 72             | Vcc-SIG                            |                                         | Power supply for Y color difference signal processing system.                                                                                                                                                                                                                                                                                                  |

| 73<br>74<br>75 | SELCR-IN<br>SELCB-IN<br>SELY-IN    | 73<br>74<br>1.2k<br>100k<br>70k<br>2.5V | Input the selector output YCbCr (Pins 76, 77, 78) signals through a clamping capacitor. Signals are input at a 0.7Vp-p 100 IRE level (but only with 100% color bars for CbCr). The pedestal is clamped to 4.9V.                                                                                                                                                |

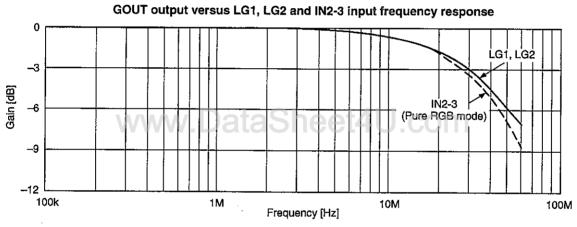

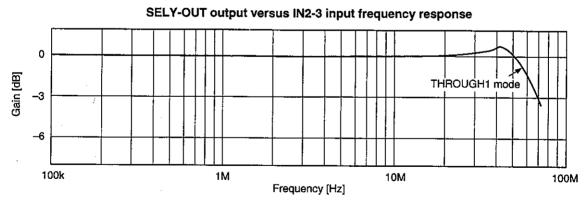

| 76<br>77<br>78 | SELY-OUT<br>SELCB-OUT<br>SELCR-OUT | Vcc 1.2k ₹ 76                           | IN2 to IN5 selector outputs. YCbCr-converted signals are output. These pins can be connected to an external processor, etc. Signals are output at a level equivalent to 0dB compared with the IN2 to IN5 input level. The conversion types are shown on the pages with the description of operation. Select these signals with I <sup>2</sup> C bus "MAT-OUT." |

| 79<br>80       | SELH-OUT<br>SELV-OUT               | Vcc 1k € 15k € 1k                       | IN2 to IN5 selector HV outputs.<br>Voн ≥ 2.8V<br>VoL ≤ 0.4V                                                                                                                                                                                                                                                                                                    |

#### **Electrical Characteristics**

- Ta = 25°C, Vcc-MAT = Vcc-OUT = Vcc-SIG = 9V, GND-MAT = GND-MAT = GND-OUT = GND-SIG = 0V

- Measures the following after setting the I<sup>2</sup>C bus register as shown in "I<sup>2</sup>C BUS Register Initial Settings."

| No. | item                                          | Symbol  | Measurement conditions                                                   | Measurement pins | Measurement contents                                                                         | Min. | Тур. | Max. | Unit |

|-----|-----------------------------------------------|---------|--------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------|------|------|------|------|

| 1   | Video switch system current consumption       | Icc-MAT |                                                                          | 6                |                                                                                              | 18   | 28   | 34   | mA   |

| 2   | RGB system current consumption                | Icc-OUT |                                                                          | 30               | Measure the pin inflow current.                                                              |      | 50   | 61   | mA   |

| 3   | Y color difference system current consumption | lcc-SIG |                                                                          | 72               |                                                                                              | 29   | 45   | 55   | mΑ   |

| 4   | RGB output                                    | VRGB    | 100 IRE signal input to Y1-IN (Pin 69)                                   | 35, 37, 39       | Measure the output level.                                                                    | 2    | 2.6  | 3.1  | Vp-p |

| 5   | RGB linearity                                 | VLIN    | 50 IRE 100 IRE  100 IRE  Staircase wave input to Y1-IN (Pin 69)          | 35, 37, 39       | $VLIN = \frac{V1}{V2 \times 2} \times 100$                                                   | 95   | 102  | 109  | %    |

| 6   | EY-IN gain                                    | GEY     | 100 IRE signal input to EY-IN (Pin 64)<br>YCBCR-SW (Pin 61) = 5V         | 37               |                                                                                              | -1.5 | -0.5 | 0.2  | dВ   |

| 7   | LRGB1 gain                                    | GLI     | 100 IRE signal input to LG1-IN (Pin 47)<br>YS/YM-1 (Pin 45) = 5V         | 37               | Ratio of output level to VRGB                                                                | -1.7 | -0.1 | 1.5  | dΒ   |

| 8   | LRGB2 gain                                    | GL2     | 100 IRE signal input to LG2-IN (Pin 51)<br>YS/YM-2 (Pin 49) = 5V         | 37               |                                                                                              | -2.5 | -1   | 1    | dB   |

| 9   | IN2-3 gain                                    | GSEL    | 100 IRE signal input to IN2-3 (Pin 5)                                    | 76               | Ratio of output level to input level                                                         | -0.3 | -0.1 | 0    | dB   |

| 10  | VM output                                     | VvM     | 50 IRE/4.43MHz  V// Sine wave input to Y1-IN (Pin 64)                    | 59               | Measure the VMOUT level.                                                                     | 1.6  | 2    | 2.4  | Vp-p |

| 11  | HUE center                                    | θв      | Y1IN (69pin)  CB1-IN (68pin) CR1-IN (67pin)  Cb = 572mVp-p Cr = 406mVp-p | 39               | $\theta B = \tan^{-1} \frac{VB \text{ level with Cr input}}{VB \text{ level with Cb input}}$ | -4   | 2    | 8    | deg. |

| 12  | BRIGHT center R channel                       | VBRT-R  |                                                                          | 35               |                                                                                              | -380 | -260 | -150 | mV   |

| 13  | BRIGHT center G channel                       | VBRT-G  |                                                                          | 37               | VBRT = VPED - VREFP                                                                          | -320 | -240 | -160 | mV   |

| 14  | BRIGHT center B channel                       | VBRT-B  |                                                                          | 39               | 777 VREFP 777 VPED                                                                           | -380 | -260 | -150 | mV   |

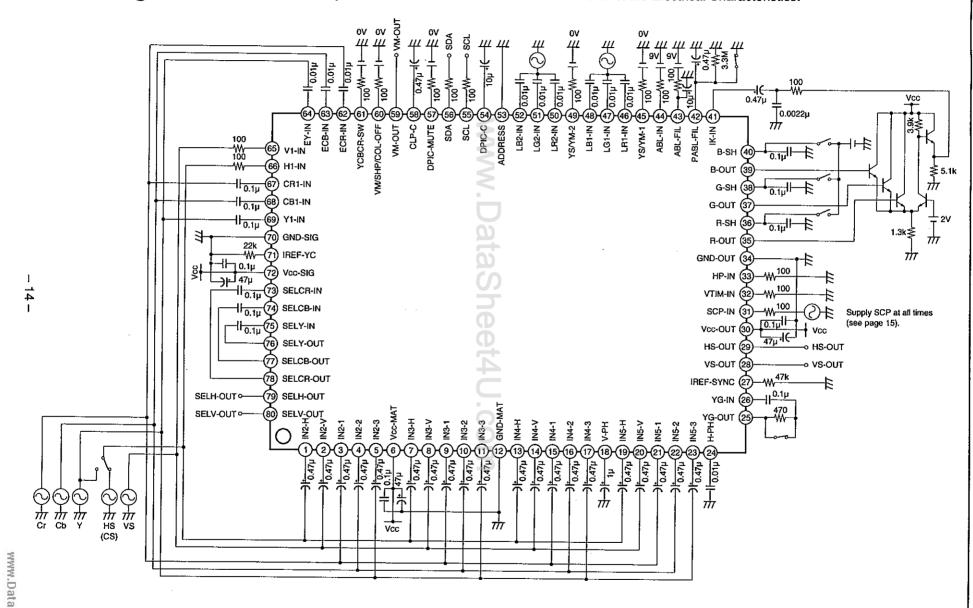

#### **Electrical Characteristics Measurement Circuit**

Signal sources of are all GND unless otherwise specified in the Measurement conditions column of the Electrical Characteristics.

CXA2101Q

#### **Electrical Characteristics Measurement Input Signals**

### SONY

#### Electrical Characteristics Measurement Conditions "I2C BUS Register Initial Settings"

| Register name | No. of<br>bits | Setting<br>value | Description                | Register name | No. of<br>bits | Setting<br>value | Description                           |

|---------------|----------------|------------------|----------------------------|---------------|----------------|------------------|---------------------------------------|

| PICON         | 1              | 1                | Picture mute off           | B-CUTOFF      | 6              | 1Fh              | Center                                |

| RON           | 1              | 1                | R output on                | SUB-BRIGHT    | 6              | 1Fh              | Center                                |

| GON           | 1              | 1                | G output on                | HSEP-SEL      | 1              | 0                | Forced slice                          |

| BON           | 1              | 1                | B output on                | FIX-SYNC      | 2              | 0                | Automatic identification              |

| CBLKOFF       | 1              | 0                | CBLK and AKB both on       | V-TC          | 2              | 3                | Maximum                               |

| AKB-T         | 1              | 0                | Normal                     | H-WIDTH       | 2              | 0                | THROUGH mode                          |

| BLKSW         | 1              | 0                | Regular mode               | HD-TC         | 1              | 1                | Time constant other than HD-TV system |

| INPUT-SEL     | 2              | 0                | IN2 system selected        | HS-MASK       | 1              | 1                | Added                                 |

| MAT-OUT       | 2              | 0                | THROUGH1 mode selected     | CR-OFFSET 1   | 4              | 7h               | Center                                |

| YCbCr/MAT     | 1              | 0                | IN1 system selected        | CB-OFFSET 1   | 4              | 7h               | Center                                |

| HYSW          | 1              | 0                | 3 selected from IN2 to IN5 | CR-OFFSET 2   | 4              | 7h               | Center                                |

| PICTURE       | 6              | 3Fh              | Maximum value              | CB-OFFSET 2   | 4              | 7h               | Center                                |

| LIMIT-LEVEL   | 2              | 0                | Off                        | SUB-CON       | 4              | 7h               | Center                                |

| HUE           | 6              | 1Fh              | Center                     | SUB-COL       | 4              | 7h               | Center                                |

| SYSTEM        | 2              | 0                | Normal                     | SUB-HUE       | 4              | 7h               | Center                                |

| COLOR         | 6              | 1Fh              | Center                     | CTI-LEVEL     | 2              | 0                | Off                                   |

| AGING1        | 1              | 0                | Off/W.Datao                | R-Y/R         | 4-             | 6h               | NTSC-JPN                              |

| AGING2        | 1              | 0                | Off                        | R-Y/B         | 4              | Ch               | NTSC-JPN                              |

| BRIGHT        | 6              | 1Fh              | Center                     | G-Y/R         | 4              | Ah               | NTSC-JPN                              |

| YMYS1SW       | 1              | 0                | Valid                      | G-Y/B         | 4              | 5h               | NTSC-JPN                              |

| YM-VM         | 1              | 0                | No muting of VM by YM      | LRCB2-LEVEL   | 4              | Fh               | Maximum                               |

| SHARPNESS     | 6              | 1Fh              | Center                     | GAMMA         | 4              | 0h               | Off                                   |

| R-DRIVE       | 6              | 26h              | Center                     | PABL-LEVEL    | 4              | Fh               | Maximum                               |

| D-COL         | 1              | 0                | Off                        | BLK-BOTTOM    | 4              | 0h               | Minimum                               |

| G-DRIVE       | 6              | 26h              | Center                     | SUB-SHP       | 2              | 0                | Minimum                               |

| CLP-SW        | 1              | 1                | SCP CLP only used          | SHP-F0        | 2              | 0                | Minimum                               |

| B-DRIVE       | 6              | 26h              | Center                     | PRE/OVER      | 2              | 0                | 1:1                                   |

| CLP-MSK       | 2              | 0                | Normal                     | LTI-LEVEL     | 2              | 0                | Off                                   |

| R-CUTOFF      | 6              | 1Fh              | Center                     | VM-LEV        | 2              | 3                | Maximum                               |

| ABL-MODE      | 2              | 0                | Picture-only mode          | VM-DEL        | 2              | 3                | Maximum                               |

| G-CUTOFF      | 6              | 1Fh              | Center                     | DC-TRAN       | 2              | 0                | 100%                                  |

| ABL-TH        | 2              | 0                | Minimum                    | D-PIC         | 2              | 0                | Off                                   |

.DataSheet4U.com

### SONY

#### Definition of I<sup>2</sup>C BUS Registers

#### **Slave Addresses**

Slave Receiver Slave Transmitte 84h: ADDRESS (Pin 53) = Low, 86h: ADDRESS (Pin 53) = High 85h: ADDRESS (Pin 53) = Low, 87h: ADDRESS (Pin 53) = High

#### **Register Table**

\*\*": Undefined

#### **Control Register**

| Sub Add   | ress | Bit7                     | Bit6  | Bit5        | Bit4               | Bit3      | Bit2     | Bit1    | Bit0   |

|-----------|------|--------------------------|-------|-------------|--------------------|-----------|----------|---------|--------|

| xxx00000  | Oh   | PICON                    | RON   | GON         | BON                | CBLKOFF   | AKB-T    | BLKSW   | 0      |

| xxx00001  | 1h   | INPUT-SEL                |       | MAT-OUT     |                    | YCbCr/MAT | HYSW     | *       | *      |

| xxx00010  | 2h   | PICTURE                  |       |             | ······             |           | LIMIT-   | LEVEL   |        |

| xxx00011  | 3h   |                          |       | Н           | JE                 | SYSTEM    |          | TEM     |        |

| xxx00100  | 4h   |                          | COLOR |             |                    |           |          | AGING1  | AGING2 |

| xxx00101  | 5h   | BRIGHT                   |       |             |                    | -         | YSYM1SW  | YM-VM   |        |

| xxx00110  | 6h   |                          |       | SHARI       | PNESS              |           |          | *       | *      |

| xxx00111  | 7h   | R-DRIVE                  |       |             |                    |           | D-COL    | *       |        |

| xxx01000  | 8h   | G-DRIVE                  |       |             |                    |           | CLPSW    | *       |        |

| xxx01001  | 9h   | B-DRIVE                  |       |             |                    | CLP-MSK   |          |         |        |

| xxx01010  | Ah   | WWW.Date-cutofeet4.U.com |       |             |                    | ABL-MODE  |          |         |        |

| xxx01011. | Bh   | G-CUTOFF                 |       |             |                    |           | ABL-TH   |         |        |

| xxx01100  | Ch   | B-CUTOFF                 |       |             |                    | <u></u>   | *        | *       |        |

| xxx01101  | Dh   | SUB-BRIGHT               |       |             |                    |           | HSEP-SEL | *       |        |

| xxx01110  | Eh   | FIX-SYNC V-TC            |       |             | H-WI               | DTH       | HD-TC    | HS-MASK |        |

| xxx01111  | Fh   | CR-OFFSET 1              |       | CB-OFFSET 1 |                    |           |          |         |        |

| xxx10000  | 10h  | CR OFFSET 2              |       | CB OFFSET 2 |                    |           |          |         |        |

| xxx10001  | 11h  | SUB-CON                  |       | SUB-COL     |                    |           |          |         |        |

| xxx10010  | 12h  | SUB-HUE                  |       |             | CTI-LE             | VEL       | *        | *       |        |

| xxx10011  | 13h  | R-Y/R                    |       |             | R-Y/B              |           |          |         |        |

| xxx10100  | 14h  | G-Y/R                    |       |             | G-Y/B              |           |          |         |        |

| xxx10101  | 15h  | LRGB2-LEVEL              |       | GAMMA       |                    |           |          |         |        |

| xxx10110  | 16h  | PABL-LEVEL               |       | BLK-BOTTOM  |                    |           |          |         |        |

| xxx10111  | 17h  | SUB-SHP SHP-F0           |       |             | PRE/OVER LTI-LEVEL |           | EVEL     |         |        |

| xxx11000  | 18h  | VM-LEV VM-DEL            |       |             | DC-TI              | RAN       | D-F      | PIC OIC |        |

#### **Status Register**

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| 1    | 1    | 1    | 1    | 1    | EH   | ΕV   | IK   |

**Description of Registers**

SONY

**PICON**

(1): ON/OFF switch for RGB outputs including reference pulse

(Set to OFF mode at power-on)

0 = RGB output OFF (all blanking mode)

1 = RGB output ON

RON

(1): ON/OFF switch for R channel video output excluding reference pulse

(Valid when PICON = 1; set to OFF mode at power-on)

0 = R channel video output OFF (blanking mode, REF-P only output)

1 = R channel video output ON

GON

(1): ON/OFF switch for G channel video output excluding reference pulse

(Valid when PICON = 1; set to OFF mode at power-on)

0 = G channel video output OFF (blanking mode, REF-P only output)

1 = G channel video output ON

BON

(1): ON/OFF switch for B channel video output excluding reference pulse

(Valid when PICON = 1; set to OFF mode at power-on)

0 = B channel video output OFF (blanking mode, REF-P only output)

1 = B channel video output ON

**CBLKOFF**

(1): ON/OFF switch for H, V blanking of RGB output (set to ON mode at power-on)

AKB system is set to the OFF mode at the same time as the blanking is set off.

0 = CBLK ON; AKB ON

1 = CBLK OFF; AKB OFF

The pedestal potential when AKB is OFF can be set by the voltage applied to the

R-SH, G-SH and B-SH pins for R, G, B, respectively.

AKB-T

(1): Selection of timing pulse which generates reference pulse

(Set to NORMAL mode at power-on)

0 = NORMAL mode (reference pulse generated by SCP input only)

1 = V compression mode (reference pulse generated from VTIM-IN, HP-IN)

**BLKSW**

(1): Selection of H, V blanking system for RGB-OUT

(Set to 0 at power-on.)

0 = Normal blanking mode (blanking up to VCE (SAT) level)

1 = Blanking at value set by BLK-BOTTOM

(Refer to the description of the BLK-BOTTOM register.)

INPUT-SEL

(2): Selection of four system inputs: IN2, IN3, IN4 and IN5

0 = IN2 selected

1 = IN3 selected

2 = IN4 selected

3 = IN5 selected

### SONY

MAT-OUT

(2): Selection of type matrix conversion; selected signal is output from Pins 76, 77 and 78. A DC voltage of approximately 4V is output only for 3 of these modes.

0 = THROUGH1 (when YCbCr is input)

1 = Matrix conversion of YPbPr to YCbCr signal

2 = Matrix conversion of GBR to YCbCr signal

3 = THROUGH2 (GBR is input directly to internal RGB system)

YCbCr/MAT

(1): Selection of IN1 system signal or SELIN system signal for signal sent to Y color difference processing system. H and V sync signals are simultaneously selected and output.

0 = IN1 system input selected

1 = SELIN system input selected

**HYSW**

(1): Switch for switching signal output to YG-OUT pin

0 = For a sync on Y, sync on Green input

1 = For a composite sync input

**PICTURE**

(6): Picture gain control; valid for input signals except for LRGB2.

0h = -16dB

3Fh = 0dB

LIMIT-LEVEL

(2): Limiter to cope with excessively high inputs.

0 = OFF

1 = 104 IRE

2 = 113 IRE

3 = 122 IRE

HUE

(6): Hue control

$0h = -33^{\circ}$

Flesh color appears red.

1Fh = CENTER

$3Fh = +33^{\circ}$

Flesh color appears green.

SYSTEM

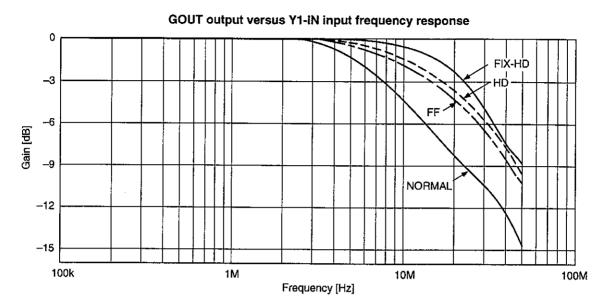

(2): Signal frequency band switching; select the band in accordance with the TV system.

ataSheet4U.com

0 = NORMAL

1 = FF

2 = HD

3 = FIX-HD (setting which gives greater importance to frequency response than 2)

COLOR

(6): Color gain control

0h = Color OFF

1Fh = 0dB

3Fh = +6.2dB

AGING1

(1): White output aging mode ON/OFF switch

74 IRE flat signal is output from Y system

0 = OFF

1 = ON

- 20 -

SONY CXA2101Q

AGING2

(1): All black output aging mode ON/OFF switch

Input signals are cut off inside the Y/color difference signal processing system. As a result, the signals which were input to the RGB system are output.

0 = OFF

1 = ON

BRIGHT

(6): Main brightness control

Output DC bias setting for RGBOUT

0h = -13 IRE

1Fh = CENTER

3Fh = +13 IRE

YSYM1SW

(1): On/off switching for YS/YM-1 input pin (Pin 45)

0 = On

1 = Off

YM-VM

(1): Mute function ON/OFF switch for VM-OUT (Pin 59) in YM ON block

Setting takes effect for both YS/YM-1 (Pin 45) and YS/YM-2 (Pin 49)

0 = OFF: no muting