# **CY15B116QSN, CY15V116QSN**

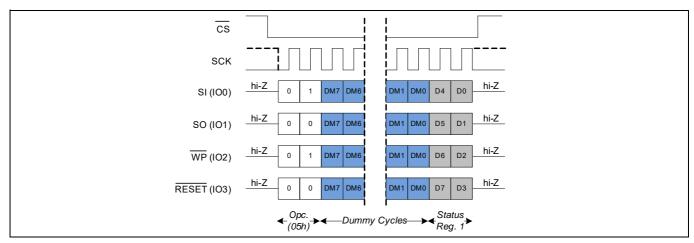

# 16Mb EXCELON™ Ultra Ferroelectric RAM (F-RAM)

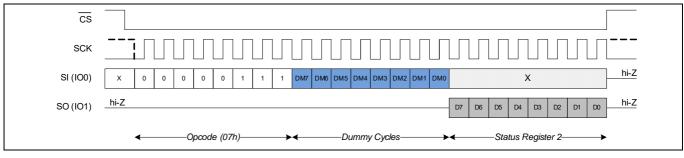

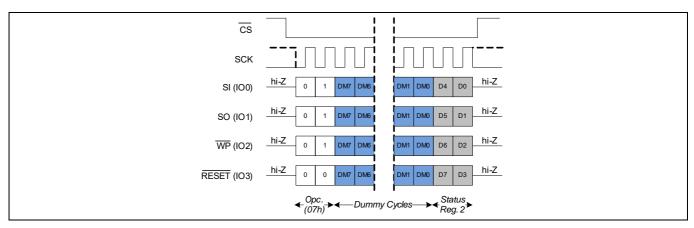

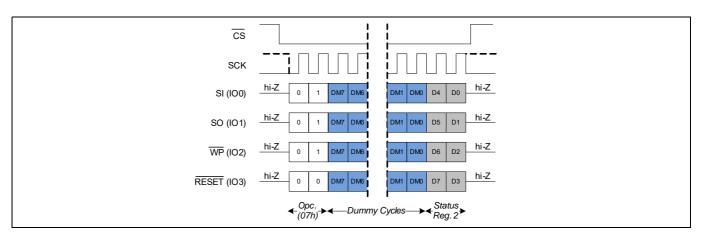

Serial (Quad SPI), 2048K × 8, 108 MHz, extended industrial

# Features

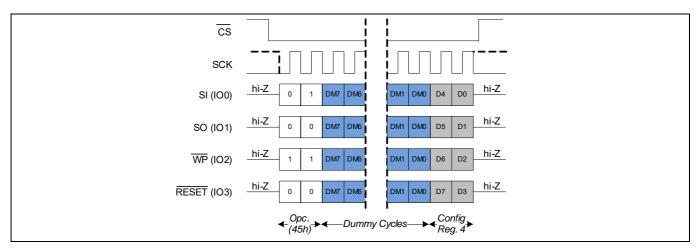

- + 16-Mb ferroelectric random access memory (F-RAM) logically organized as 2048K  $\times$  8

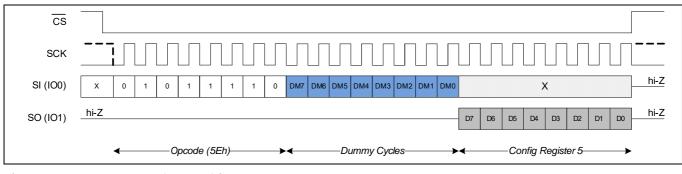

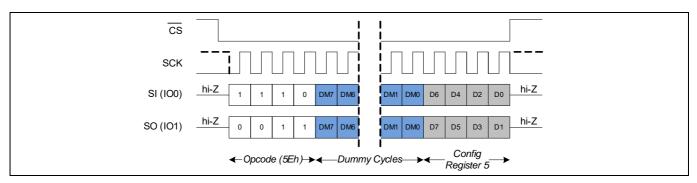

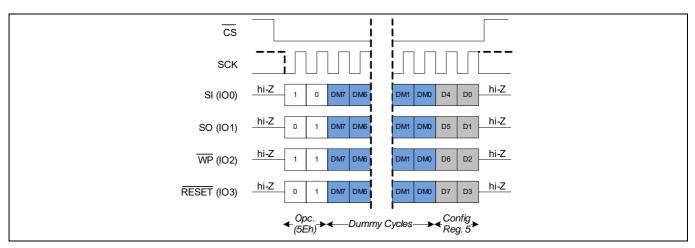

- Virtually unlimited endurance of 100 trillion (10<sup>14</sup>) read/write cycles

- 151-year data retention (see "Data retention and endurance" on page 94)

- Infineon instant non-volatile write technology

- Advanced high-reliability ferroelectric process

- Single and multi I/O serial peripheral interface (SPI)

- Serial bus interface SPI protocols

- Supports SPI Mode 0 (0, 0) and Mode 3f (1, 1) for all SDR mode transfers

- Supports SPI Mode 0 (0, 0) for all DDR mode transfers

- Extended I/O SPI protocols

- Dual SPI (DPI) protocols

- Quad SPI (QPI) protocols

- SPI clock frequency

- Up to 108-MHz frequency SPI single data rate (SDR)

- Up to 46-MHz frequency SPI double data rate (DDR)

- eXecute-In-Place (XIP) for memory read/write

- Write protection, data security, and data integrity

- Hardware protection using the write protect (WP) pin

- Software block protection

- Embedded error correction code (ECC) and cyclic redundancy check (CRC) for enhanced data integrity

- ECC detects and corrects 2-bit error. If a 3-bit error occurs, it does not correct but reports through the ECC Status Register

- CRC detects any accidental change to raw data

- Extended electronic signatures

- Device ID includes manufacturer ID and product ID

- Unique ID

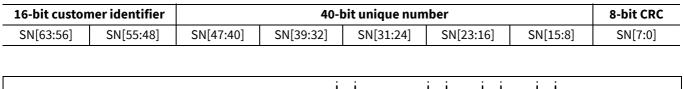

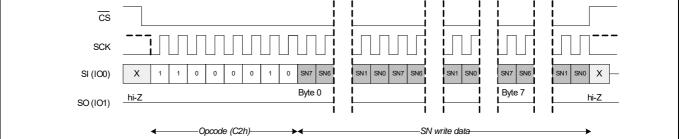

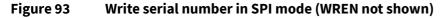

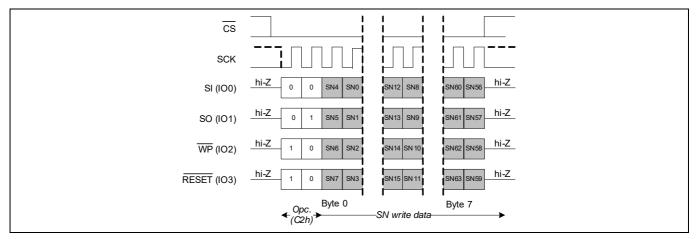

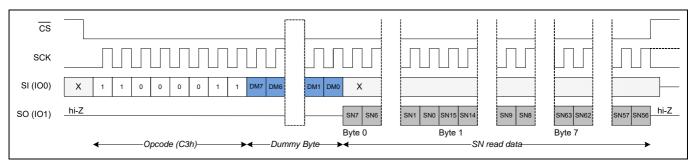

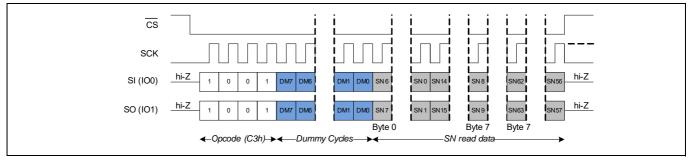

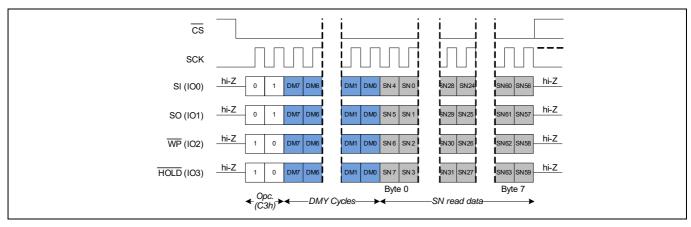

- User programmable serial number

- Dedicated 256-byte special sector F-RAM

- Dedicated special sector write and read

- Content can survive up to three standard reflow cycles

- Low-power consumption at high speed

- 14 mA (typ) active current for 108 MHz SPI SDR

- 22 mA (typ) active current for 108 MHz QSPI SDR

- 16.5 mA (typ) active current for 46-MHz QSPI DDR

- 115 µA (typ) standby current

- 1.4 µA (typ) Deep Power-down mode current

- 0.1 µA (typ) Hibernate mode current

- Low-voltage operation:

- CY15V116QSN: V<sub>DD</sub> = 1.71 V to 1.89 V

- CY15B116QSN:  $V_{DD}$  = 1.8 V to 3.6 V

- Operating temperature:

- Extended industrial: -40°C to +105°C

- Packages

- 24-ball fine pitch ball grid array (FBGA)

- Restriction of hazardous substances (RoHS) compliant

# **Functional description**

The EXCELON<sup>™</sup> Ultra CY15x116QSN is a high-performance, 16-Mb non-volatile memory employing an advanced ferroelectric process. A ferroelectric random access memory or F-RAM is non-volatile and performs reads and writes similar to a RAM. It provides reliable data retention for 151 years while eliminating the complexities, overhead, and system-level reliability problems caused by serial flash and other non-volatile memories.

Unlike serial flash, the CY15x116QSN performs write operations at bus speed. No write delays are incurred. Data is written to the memory array immediately after each byte is successfully transferred to the device. The next bus cycle can commence without the need for data polling. In addition, the product offers substantial write endurance compared to other non-volatile memories. The CY15x116QSN is capable of supporting 10<sup>14</sup> read/write cycles, or 100 million times more write cycles than EEPROM. These capabilities make the CY15x116QSN ideal for non-volatile memory applications, requiring frequent or rapid writes. Examples range from data collection, where the number of write cycles may be critical, to demanding industrial controls where the long write time of serial flash can cause data loss.

The CY15x116QSN combines a 16-Mb F-RAM with the high-speed quad SPI (QPI) SDR and DDR interfaces which enhances the non-volatile write capability of F-RAM technology. The device incorporates a read-only device ID and unique ID features which allow the SPI bus master to determine the manufacturer, product density, product revision and unique ID for each part. The device is also offered with a unique serial number that is read-only and can be used to identify a board or a system.

The device supports on-die ECC logic which can detect and correct 2-bit error in every 8-byte unit data. The device also extends capability to report 3-bit error in 8-byte unit data. The CY15x116QSN also supports the cyclic redundancy check (CRC) feature which can be used to check the data integrity of the stored data in the memory array.

For a complete list of related resources, **click here**.

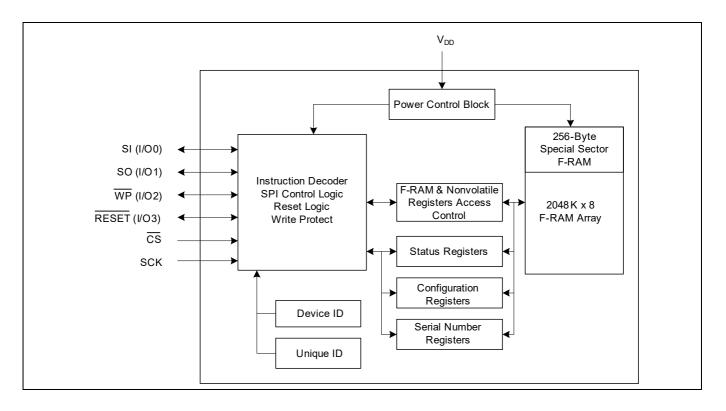

Logic block diagram

# Logic block diagram

Table of contents

# Table of contents

| Features                                                             |     |

|----------------------------------------------------------------------|-----|

| Functional description                                               | 2   |

| Logic block diagram                                                  |     |

| Table of contents                                                    | 4   |

| 1 Pinout                                                             |     |

| 2 Pin definitions                                                    |     |

| 3 Functional overview                                                |     |

| 3.1 Memory architecture                                              |     |

| 3.2 Serial peripheral interface (SPI) bus                            |     |

| 3.3 Terms used in SPI protocol                                       |     |

| 3.4 SPI modes                                                        |     |

| 3.5 Power-up to first access                                         |     |

| 4 CY15x116QSN registers                                              |     |

| 4.1 Status registers                                                 |     |

| 4.2 Configuration registers                                          |     |

| 5 Functional description                                             |     |

| 5.1 Command structure                                                |     |

| 6 Maximum ratings                                                    |     |

| 7 Operating range                                                    |     |

| 8 DC electrical characteristics                                      |     |

| 9 Data retention and endurance                                       |     |

| 9.1 Example of EXCELON™ F-RAM life time in an industrial application |     |

| 10 Capacitance                                                       |     |

| 11 Thermal resistance                                                |     |

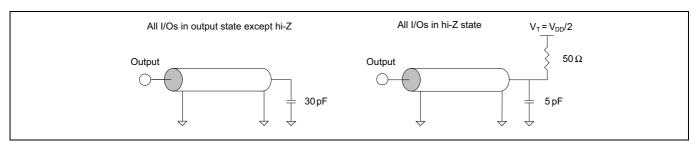

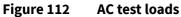

| 12 AC test conditions                                                |     |

| 13 SDR AC switching characteristics                                  |     |

| 14 DDR AC switching characteristics                                  |     |

| 15 Write protect (WP) timing parameters                              |     |

| 16 Reset (RESET) timing parameters                                   |     |

| 17 Power cycle timing                                                |     |

| 18 Ordering information                                              |     |

| 18.1 Ordering code definitions                                       |     |

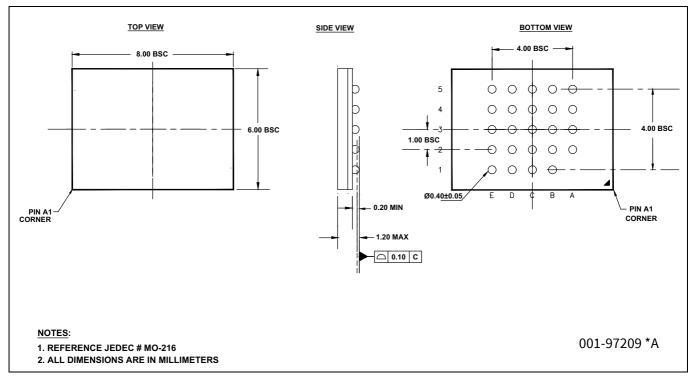

| 19 Package diagram                                                   |     |

| 20 Acronyms                                                          |     |

| 21 Document conventions                                              |     |

| 21.1 Units of measure                                                |     |

| Revision history                                                     | 111 |

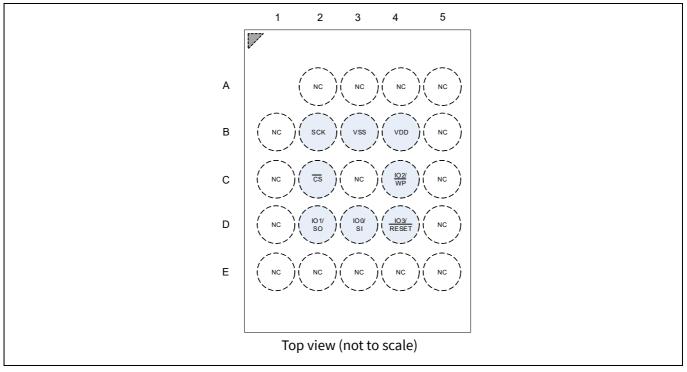

Pinout

# 1 Pinout

Pin definitions

# 2 Pin definitions

| Pin name        | I/O type      | Description                                                                                                                                                                                                                                                                                                                                                                |

|-----------------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <del>CS</del>   | loput         | <b>Chip Select.</b> This active LOW input activates the device. When HIGH, the device enters low-power standby mode, ignores other inputs, and the output is tristated. When LOW, the device internally activates the SCK signal. A falling edge on CS must occur before a new opcode is issued.                                                                           |

| SCK             | Input         | <b>Serial Clock.</b> All I/O activity is synchronized to the serial clock. Inputs are latched on the rising edge and outputs occur on the falling edge. Because the device is synchronous, the clock frequency can vary between 0 and 108 MHz and may be interrupted at any time.                                                                                          |

|                 | Input         | <b>Serial Input.</b> All data is input to the device on this pin. The pin is sampled on the rising edge of SCK and is ignored at other times.                                                                                                                                                                                                                              |

| SI / (I/O0)     | Input/Output  | <b>I/O0:</b> When the part is either in dual mode or quad mode, the SI pin becomes input/output (I/O0) pin and acts as input during command and address cycles and output during the data output cycle.                                                                                                                                                                    |

|                 | Output        | <b>Serial Output.</b> This is the data output pin. It is driven during a read and remains tristated at all other times including when RESET is LOW. Data transitions are driven on the falling edge of the serial clock.                                                                                                                                                   |

| SO / (I/O1)     | Input/Output  | <b>I/O1:</b> When the part is either in dual mode or quad mode, the SO pin becomes input/output (I/O1) pin and acts as input during command and address cycles and output during the data output cycle.                                                                                                                                                                    |

| WP / (I/O2)     | Input         | Write Protect. This active LOW pin prevents write operation to the Status and Configuration registers when SRWD bit (SR1[7]) is set to '1'. A complete explanation of write protection is provided in "Status Register 1 (SR1)" on page 14. This pin must be tied to V <sub>DD</sub> if not used.                                                                          |

|                 | Input/Output  | <b>I/O2:</b> When the part is in quad mode, the WP pin becomes input/output (I/O2) pin and acts as input during command and address cycles and output during the data output cycle.                                                                                                                                                                                        |

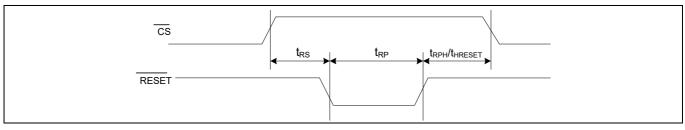

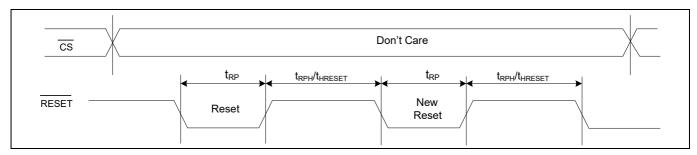

| RESET / (I/O3)  | Input         | <b>Hardware Reset Pin.</b> This active LOW pin resets the device. When RESET is LOW, the device will self-initialize and will return to either standby state or active state depending on CS HIGH or LOW status after the RESET input is released to HIGH. This pin must be tied to V <sub>DD</sub> if not used. RESET / (I/O3) behavior is described in <b>Table 21</b> . |

|                 | Input/Output  | <b>I/O3:</b> When the part is in quad mode, the RESET pin becomes input/output (I/O3) pin and acts as input during command and address cycles and output during the data output cycle.                                                                                                                                                                                     |

| V <sub>SS</sub> | Power Supply  | Ground for the device. Must be connected to the system ground.                                                                                                                                                                                                                                                                                                             |

| VDD             | i ower Supply | Power supply input to the device.                                                                                                                                                                                                                                                                                                                                          |

# 3 Functional overview

The CY15x116QSN is a serial F-RAM memory. The memory array is logically organized as 2,097,152 × 8 bits and is accessed using an industry-standard serial peripheral interface (SPI) bus. The functional operation of the F-RAM is similar to single SPI EEPROM or single/dual/quad SPI flash. The key differences between the CY15x116QSN and a serial flash, with the same pinout, is the F-RAM's superior write performance, high endurance, and lower power consumption.

#### 3.1 Memory architecture

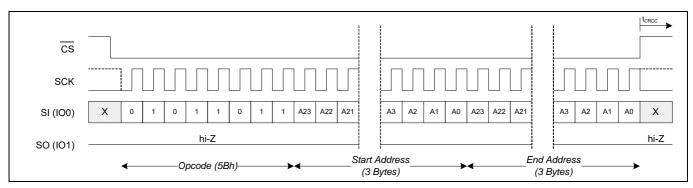

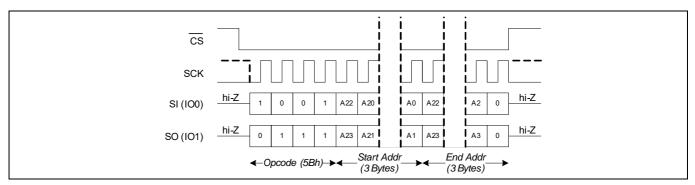

When accessing the CY15x116QSN, the user addresses 2048K locations of eight data bits each. These eight data bits are shifted in or out serially either on single, dual, or quad I/Os. The addresses are accessed using the SPI protocol, which includes a chip select (to permit multiple devices on the bus), an opcode, and a three-byte (24-bit) address. However, since CY15x116QSN requires only 21 bits to address its entire 2048K byte locations, the upper 3 bits of the most significant address byte are 'don't care' values. The 21-bit address uniquely identifies each data byte location in the 2048K memory array.

The access time for the memory operation is essentially zero, beyond the time needed for the serial protocol. That is, the memory is read or written at the speed of the SPI bus. Unlike a serial flash or EEPROM, it is not necessary to poll the device for a ready condition before initiating a new command. This is explained in more detail in **"Functional description"** on page 28.

# 3.2 Serial peripheral interface (SPI) bus

The SPI is a synchronous serial interface, which uses clock and data pins for memory access and supports multiple devices on the data bus. A device on the SPI bus is activated using the  $\overline{CS}$  pin. The relationship between chip select, clock, and data is dictated by the SPI mode. This device supports SPI modes 0 and 3. In both of these modes, data is clocked into the F-RAM on the rising edge of SCK starting from the first rising edge after  $\overline{CS}$  goes active. The SPI protocol is controlled by opcodes. The  $\overline{CS}$  must go inactive after an operation is complete and before a new opcode can be issued.

The CY15x116QSN is an SPI slave device and operates at speeds up to 108 MHz in single data rate (SDR) mode and at speeds up to 46 MHz in DDR mode. This high-speed serial bus provides high-performance serial communication to an SPI master. The CY15x116QSN supports four different SPI interface/protocol options: Single channel SPI, Extended SPI, Dual SPI, Quad SPI.

Refer to **Table 2** for I/O signaling details during opcode, address, and data phase in various SPI modes discussed above.

|           | 51 Thoucs u        | na signataet           | ans                                   |                        |                                       |                        |                                       |  |

|-----------|--------------------|------------------------|---------------------------------------|------------------------|---------------------------------------|------------------------|---------------------------------------|--|

| Interfece | Single             |                        | Extende                               | Multi-channel SPI      |                                       |                        |                                       |  |

| Interface | channel SPI        | Dual data              | Quad data                             | Dual I/O               | Quad I/O                              | DPI                    | QPI                                   |  |

| Signals   | CS, SCK, SI,<br>SO | CS, SCK,<br>I/00, I/01 | CS, SCK, I/O0,<br>I/O1, I/O2,<br>I/O3 | CS, SCK, I/O0,<br>I/O1 | CS, SCK, I/O0,<br>I/O1, I/O2,<br>I/O3 | CS, SCK, I/O0,<br>I/O1 | CS, SCK, I/00,<br>I/01, I/02,<br>I/03 |  |

| Opcode    | SI                 | I/O0                   | I/O0                                  | I/O0                   | I/O0                                  | I/00, I/01             | I/00, I/01,<br>I/02, I/03             |  |

| Address   | SI                 | I/O0                   | I/O0                                  | I/00, I/01             | I/00, I/01,<br>I/02, I/03             | I/00, I/01             | I/00, I/01,<br>I/02, I/03             |  |

| Data      | SI/SO              | I/00, I/01             | I/00, I/01,<br>I/02, I/03             | I/00, I/01             | I/00, I/01,<br>I/02, I/03             | I/00, I/01             | I/00, I/01,<br>I/02, I/03             |  |

#### Table 2SPI modes and signal details

#### Note

<sup>1.</sup> There is no user setting for the extended SPI modes. Device always starts with SPI mode and then changes to the respective extended SPI mode based on the opcode received.

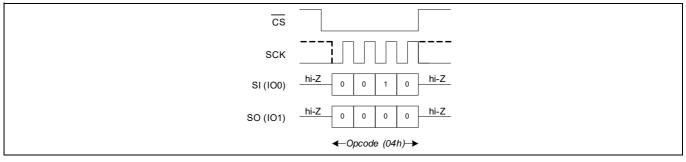

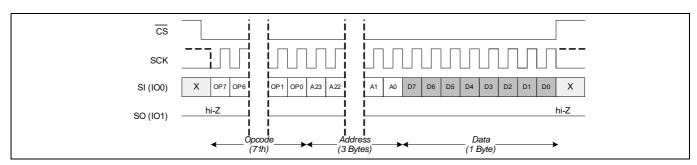

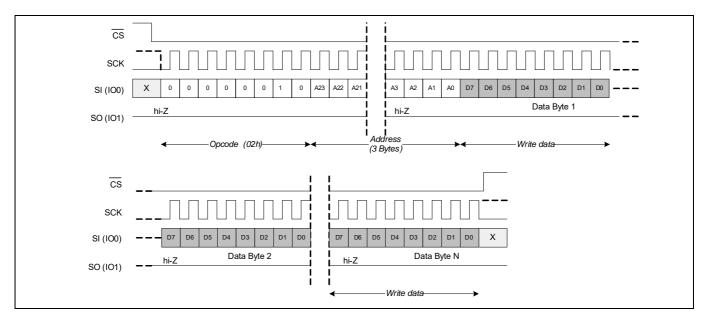

# 3.2.1 Single channel SPI

The single channel SPI is a four-pin interface with Chip Select ( $\overline{CS}$ ), Serial Input (SI), Serial Output (SO), and Serial Clock (SCK) pins. After  $\overline{CS}$  is activated, the first byte transferred from the bus master is the opcode. Following the opcode, any addresses and data are then transferred. The  $\overline{CS}$  must go HIGH (inactive) after an operation is complete and before a new opcode can be issued. This mode uses SI and SO pins for input and output respectively. Opcode and address is transferred by the master on the SI line, while data is read by the master on SO.

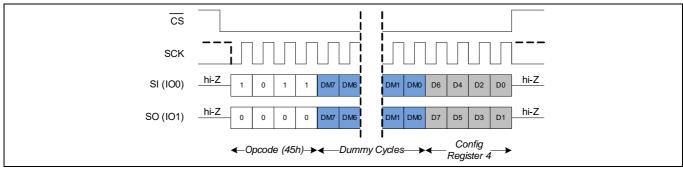

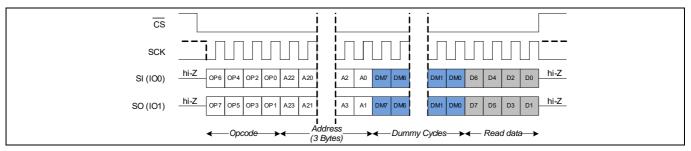

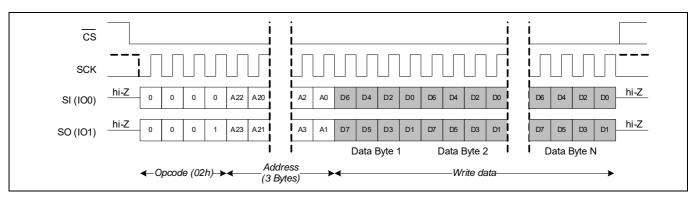

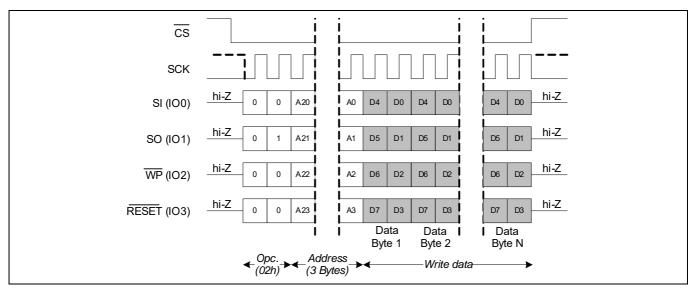

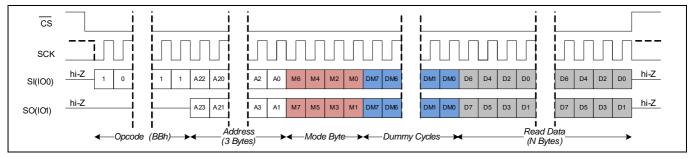

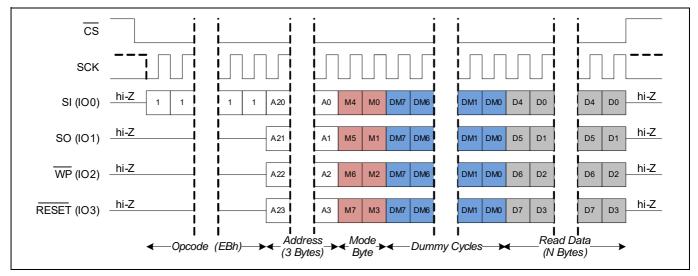

## 3.2.2 Extended SPI

The CY15x116QSN has the capability to reconfigure the standard SPI pins to work in dual or quad I/O modes called extended SPI modes. The extended SPI mode provides: Dual data, dual input/output (I/O), quad data, and quad input/output (I/O) modes. The CS going HIGH after extended SPI command or device reset (either POR or hardware/software reset) brings the device back to the single channel SPI mode. Extended SPI mode has the following I/O configurations:

- When the part is in dual output or dual I/O mode, the SI pin and SO pin become I/O0 pin and I/O1 pin respectively.

- When the part is in quad output or quad I/O mode, the SI pin, SO pin, WP pin, and RESET pin become I/O0 pin, I/O1 pin, I/O2 pin, I/O3 pin respectively.

- Dual or quad data commands and addresses are sent to the memory only on the SI signal. Data will be returned to the host as a sequence of bit pairs on I/O0 and I/O1 or four bit (nibble) groups on I/O0, I/O1, I/O2, and I/O3.

- Dual or quad input/output (I/O) commands are sent to the memory only on SI signal while an address is sent from the host as bit pairs on I/O0 and I/O1 or, four bit (nibble) groups on I/O0, I/O1, I/O2, and I/O3 respectively. Data is returned to the host similarly as bit pairs on I/O0 and I/O1 or, four bit (nibble) groups on I/O0, I/O1, I/O2, and I/O3, and I/O3.

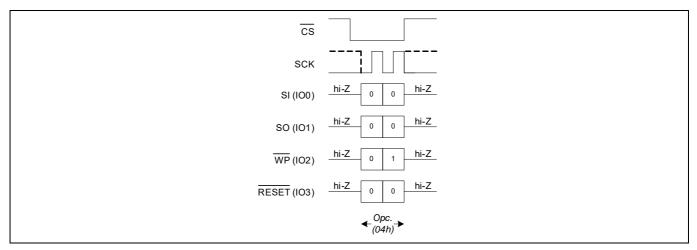

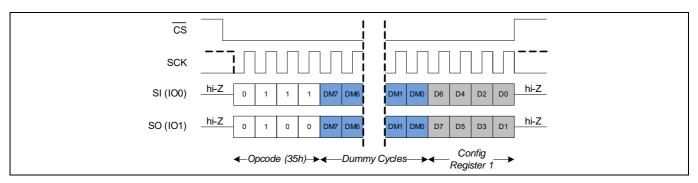

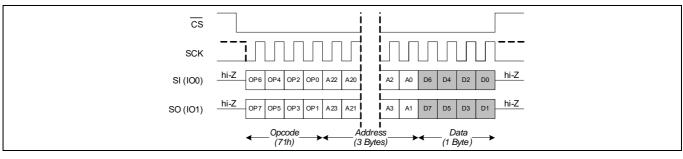

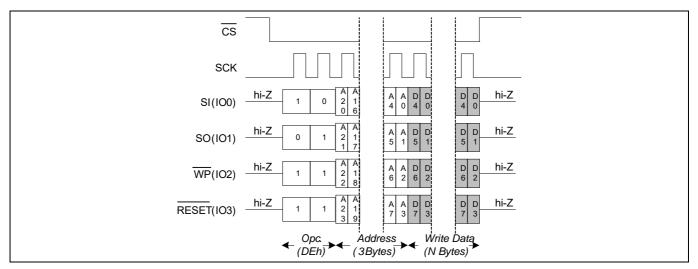

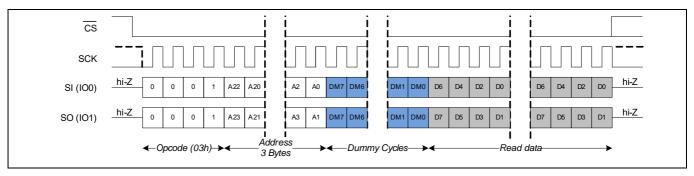

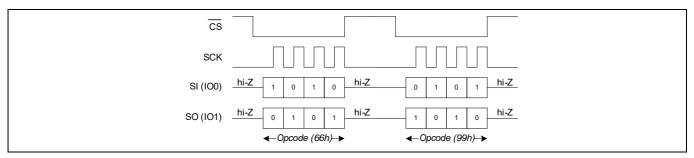

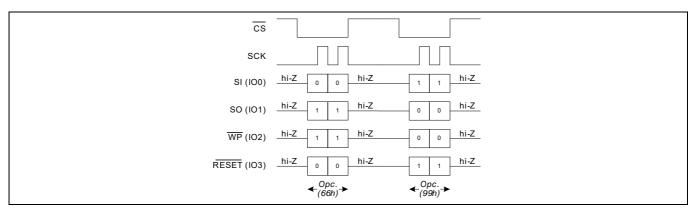

## 3.2.3 Dual SPI (DPI)

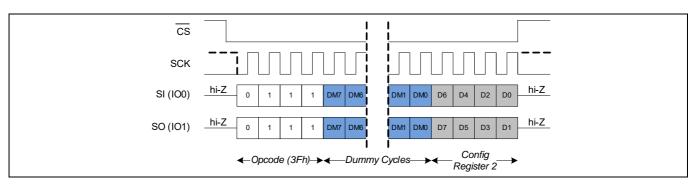

The CY15x116QSN DPI mode is enabled by writing '1' at bit 4 of "Configuration Register 2 (CR2)" on page 23, CR2[4] = 1. Since "Configuration Register 2 (CR2)" on page 23 has both volatile and non-volatile space, user setting in the non-volatile register will survive power and hardware reset cycles. Therefore, once the dual SPI (DPI) mode is set in the non-volatile CR2, it always returns to the DPI mode until the host clears the DPI bit by writing '0' in the non-volatile CR2[4]. The host can change the device interface to DPI mode by writing '1' to the volatile register CR2[4]; but this volatile setting will not survive the power and hardware reset cycles, and the volatile CR2[4] setting will be overwritten with default settings stored at associated non-volatile location at power up or after the hardware reset cycle.

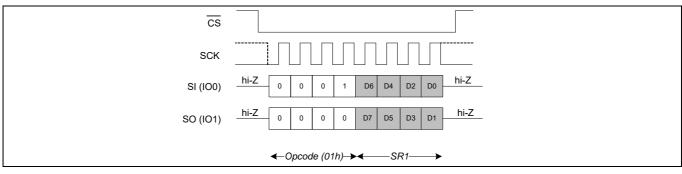

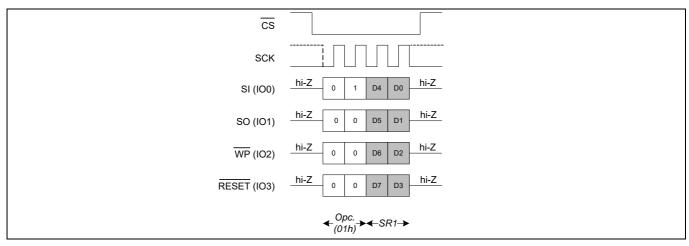

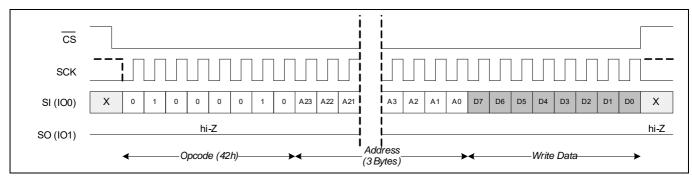

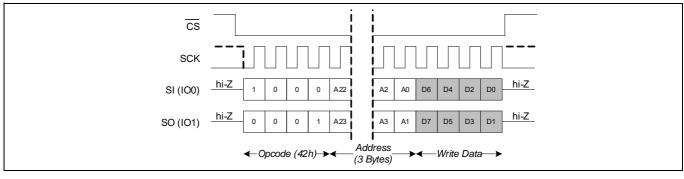

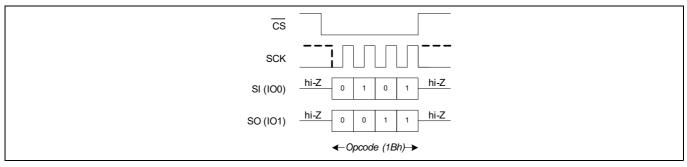

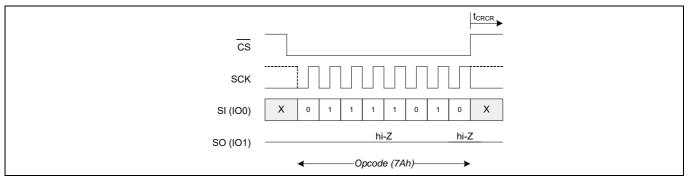

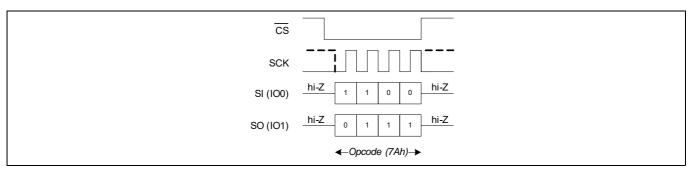

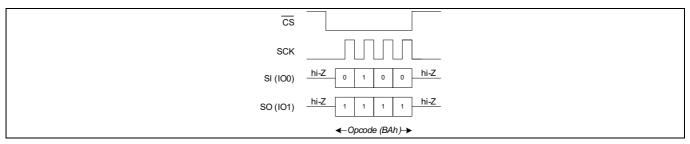

When the part is in Dual SPI mode, the SI pin and SO pin become I/O0 pin and I/O1 pin respectively. Command, address, and data bits are sent to the memory from the host as bit pairs on I/O0 and I/O1. Data bits are returned to the host similarly as bit pairs on I/O0 and I/O1.

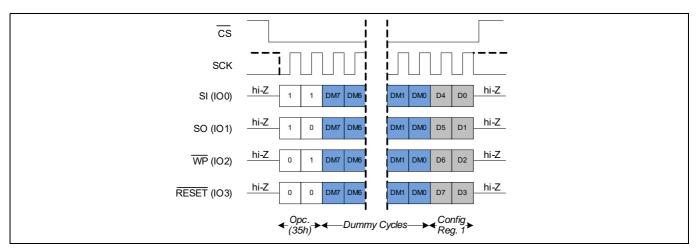

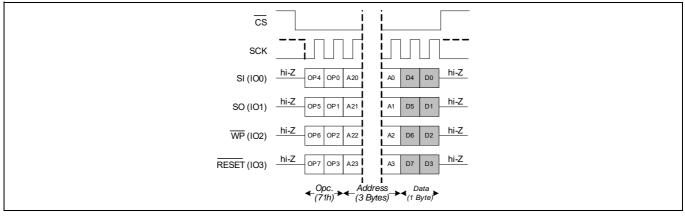

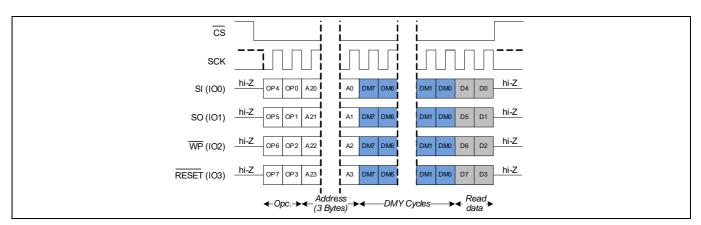

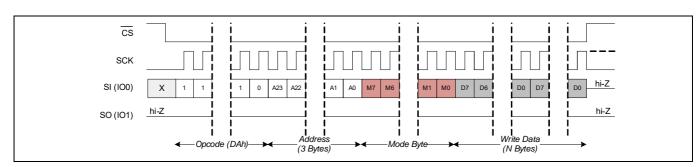

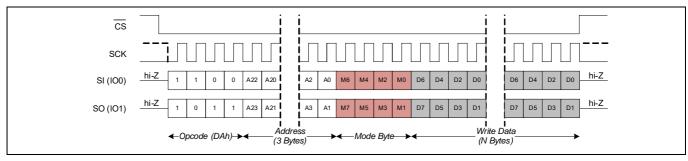

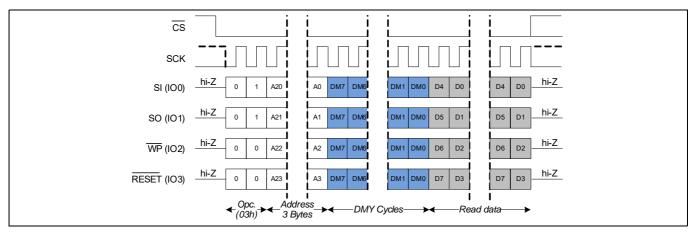

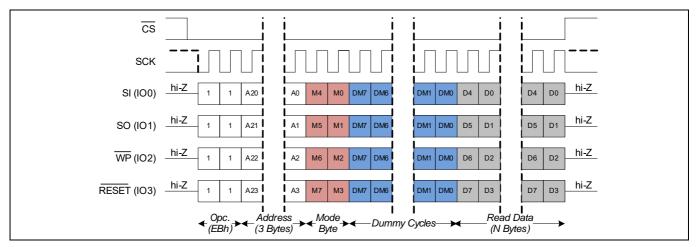

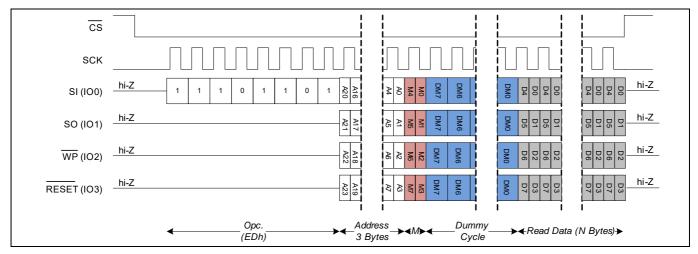

# 3.2.4 Quad SPI (QPI)

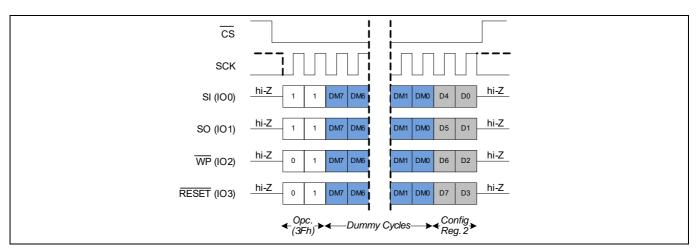

The CY15x116QSN multichannel QPI mode is enabled by writing '1' at bit 6 of "Configuration Register 2 (CR2)" on page 23, CR2[6] = 1. Since "Configuration Register 2 (CR2)" on page 23 has both volatile and non-volatile space, user setting in the non-volatile register will survive power and hardware reset cycles. Therefore, once the Quad SPI (QPI) mode is set in the non-volatile CR2, it always returns to the QPI mode until the host clears the QPI bit by writing '0' in the non-volatile CR2[6]. The host can change the device interface to QPI mode by writing '1' to the volatile register CR2[6]; but this volatile setting will not survive the power and hardware reset cycles, and the volatile CR2[6] setting will be overwritten with default settings stored at associated non-volatile location at power up or after the hardware reset cycle.

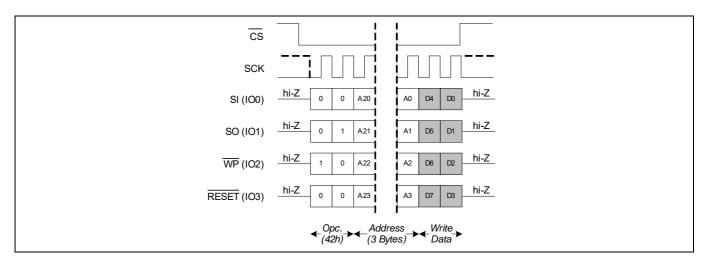

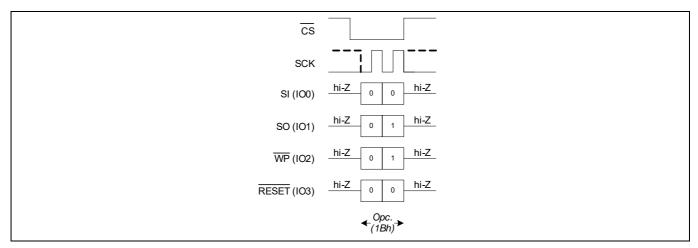

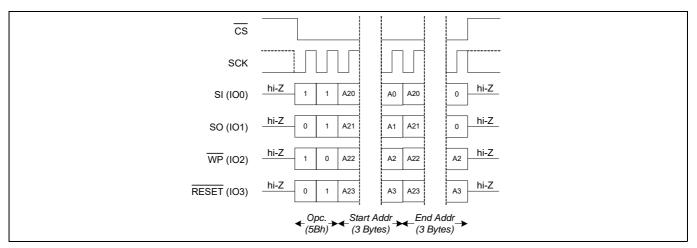

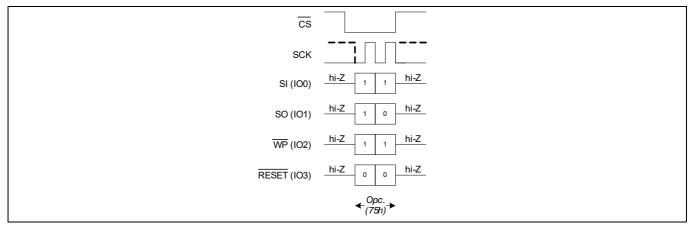

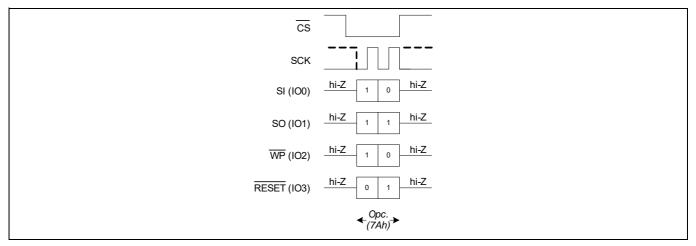

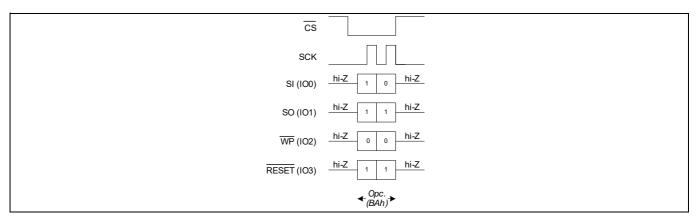

When the part is in Quad SPI mode, the SI pin, SO pin, WP pin, and RESET pins become I/O0 pin, I/O1 pin, I/O2 pin, I/O3 pin respectively. Command, address, and data bits are sent to the memory from the host as four bit (nibble) groups on I/O0, I/O1, I/O2, and I/O3. Data bits are returned to the host similarly as four bit (nibble) groups on I/O0, I/O1, I/O2, and I/O3.

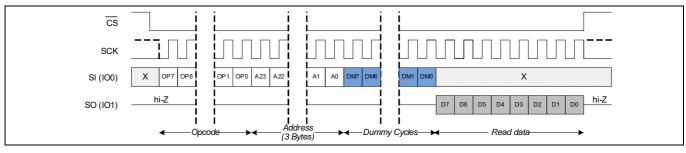

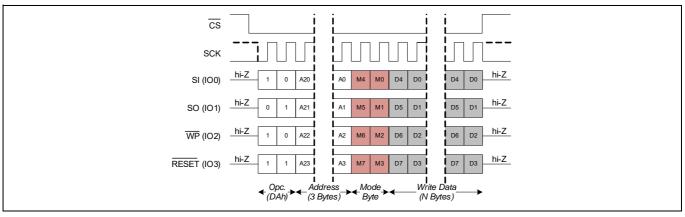

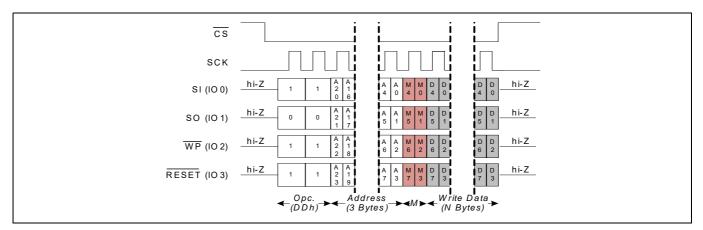

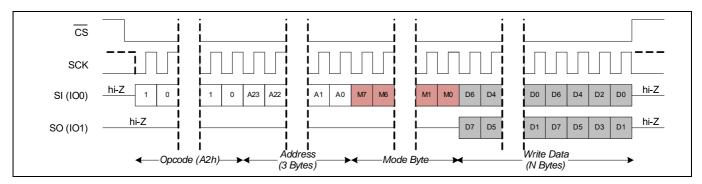

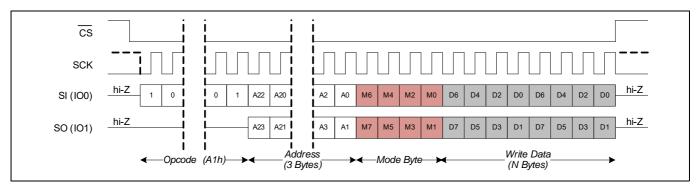

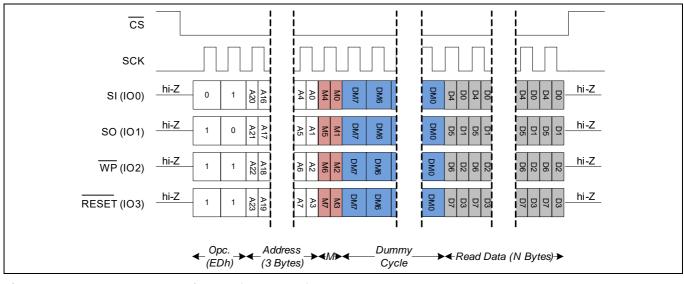

The QPI mode also supports DDR through special opcodes where byte transfer occurs on both edges of the clock for address, mode, and data bytes. There is no DDR mode during the Opcode phase; that is, opcodes are always transmitted in SDR mode. The device enters DDR mode after a specific command is transmitted in SDR mode, which then determines the address, mode, and data cycles in DDR. There is no setting for enabling the DDR mode. The quad SPI DDR mode is only supported for memory write and read operations with special opcodes.

#### 3.3 Terms used in SPI protocol

The commonly used terms in the SPI protocol are as follows:

#### 3.3.1 SPI master

The SPI master device controls the operations on the SPI bus. An SPI bus may have only one master with one or more slave devices. All the slaves share the same SPI bus lines and the master may select any of the slave devices using the CS pin. All of the operations must be initiated by the master activating a slave device by pulling the CS pin of the slave LOW. The master also generates the SCK and all the data transmission on SI and SO lines are synchronized with this clock.

#### 3.3.2 SPI slave

The SPI slave device is activated by the master through the Chip Select line. A slave device gets the SCK as an input from the SPI master and all the communication is synchronized with this clock. An SPI slave never initiates a communication on the SPI bus and acts only on the instruction from the master.

The CY15x116QSN operates as an SPI slave and may share the SPI bus with other SPI slave devices.

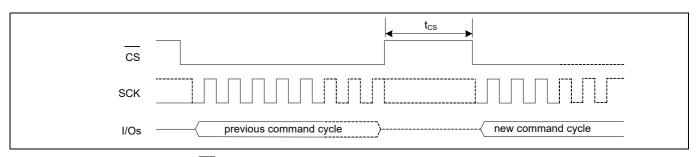

# 3.3.3 Chip Select ( $\overline{CS}$ )

To select any slave device, the master needs to pull down the corresponding  $\overline{CS}$  pin. Any instruction can be issued to a slave device only while the  $\overline{CS}$  pin is LOW. When the device is not selected, data through the SI pin is ignored and the serial output pin (SO) remains in a high-impedance state.

**Note** A new instruction must begin with the falling edge of  $\overline{CS}$ . Therefore, only one opcode can be issued for each active  $\overline{CS}$  HIGH to LOW transition.

# 3.3.4 Serial Clock (SCK)

The serial clock is generated by the SPI master and the communication is synchronized with this clock after  $\overline{CS}$  goes LOW.

The CY15x116QSN enables SPI modes 0 and 3 for data communication. In both of these modes, the inputs are latched by the slave device on the rising edge of SCK and outputs are issued on the falling edge. Therefore, the first rising edge of SCK signifies the arrival of the first most significant bit (MSb) of an SPI instruction on the SI pin. Further, all data inputs and outputs are synchronized with SCK.

# 3.3.5 Data transmission (SI/SO)

The SPI data bus consists of two lines, SI and SO, for serial data communication. SI is also referred to as master-out-slave-in (MOSI) and SO is referred to as master-in-slave-out (MISO). The master issues instructions to the slave through the SI pin, while the slave responds through the SO pin. Multiple slave devices may share the SI and SO lines as described earlier.

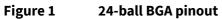

The CY15x116QSN has two separate pins for SI and SO, which can be connected with the master as shown in **Figure 2**. When in dual or quad I/O modes, these pins are configured as I/O pins. **Figure 3** shows such a system interface with a QSPI port.

Figure 2 System configuration with SPI port

Figure 3 System configuration with QSPI port

# 3.3.6 Most significant bit (MSb)

The SPI protocol requires that the first bit to be transmitted is the most significant bit (MSb). This is valid for both address and data transmission.

The 16-Mb serial F-RAM requires a 3-byte address for any read or write operation. Because the address is only 19 bits, the five bits, which are fed in are ignored by the device. Although these five bits are 'don't care', Infineon recommends that these bits be set to 0s to enable seamless transition to higher memory densities.

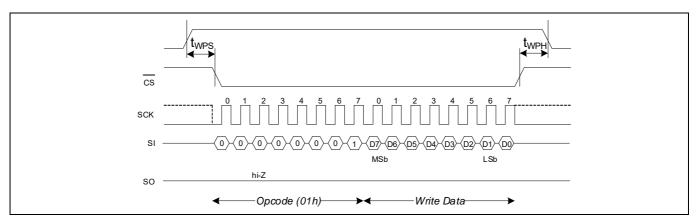

#### 3.3.7 Serial opcode

After the slave device is selected with  $\overline{\text{CS}}$  going LOW, the first byte received is treated as the opcode for the intended operation. CY15x116QSN uses the standard opcodes (refer to **Table 32**) for memory accesses.

#### 3.3.8 Invalid opcode

If a reserved opcode is received, the opcode may internally trigger unintended operation and start driving the I/O pin(s) with a non-deterministic data output. Hence, all <u>op</u>codes under the reserved category should be avoided to transmit over SI pin when CY15x116QSN chip select CS is LOW.

#### 3.3.9 Instruction

Instruction is the combination of the opcode, address, mode and/or dummy bytes/cycles used to access the memory and registers.

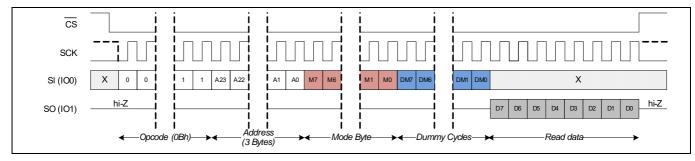

#### 3.3.10 Mode byte

The mode byte is applicable for all write and read commands that support eXecute-In-Place (XIP). The XIP is a method of executing the program (code) directly from an external memory rather than copying or shadowing the code into RAM. When the XIP is set for a write or read command, the device stays in XIP mode after the command cycle is terminated (CS toggles HIGH) so that the subsequent command cycle with CS LOW directly starts with the Address phase (Opcode phase is skipped). When in XIP, the device executes the same operation as in previous cycle. To initiate a new operation while in XIP, for example to switch from memory write to memory read or vice versa, the device should first exit the XIP for the current command cycle and initiate the next command cycle with Opcode phase. Opcodes with the Mode phase only support the XIP. See **Table 32** for the list of opcodes that require Mode phase.

Following the opcode and 3-byte address cycles, the mode byte 0xAX (X don't care bits) or 0xA5 (depending on the opcode) transmitted during the mode phase keeps the device in XIP for the next command cycle. The XIP must be set during every command cycle to remain in XIP for the next command cycle. Any other value than 0xAX or 0xA5 (!0xAX or !0xA5) transmitted during the mode phase will exit the XIP for the current operation. In this case, the next command cycle must always start with the Opcode phase to start the same operation or a new operation. Depending upon the SPI mode and the interface type, the number of clocks to transmit the mode byte will vary from one clock (Quad, DDR) to eight clocks (SPI, SDR).

## 3.3.11 Wait states or dummy cycles

The wait states, also called dummy cycles, are appended after the address bits and mode bits (if applicable). The number of wait state cycles are programmable through "Configuration Register 1 (CR1)" on page 19 and "Configuration Register 2 (CR2)" on page 23 for both memory and registers reads respectively. A valid data is driven on the output bus only after specific number of dummy cycles are elapsed following memory and register read commands that support wait state. A dummy cycle is a full clock cycle irrespective of the SPI modes and data rates (SDR or DDR). The status of I/Os are don't care during Dummy cycle.

#### 3.4 SPI modes

CY15X116QSN may be driven by a microcontroller with its SPI peripheral running in either of the following two modes:

- SPI Mode 0 (CPOL = 0, CPHA = 0)

- SPI Mode 3 (CPOL = 1, CPHA = 1)

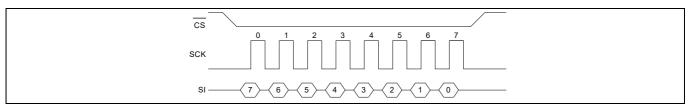

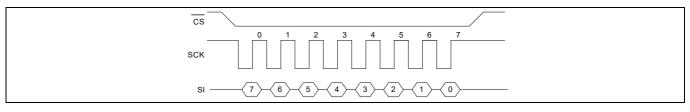

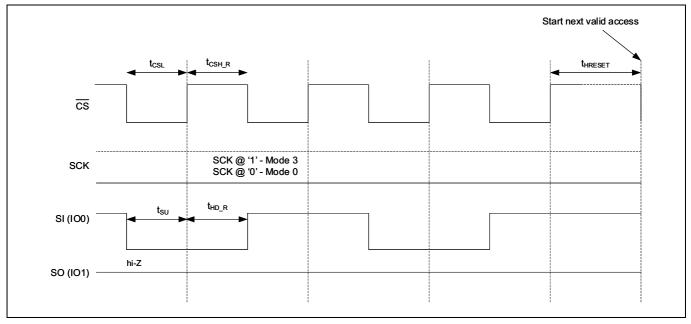

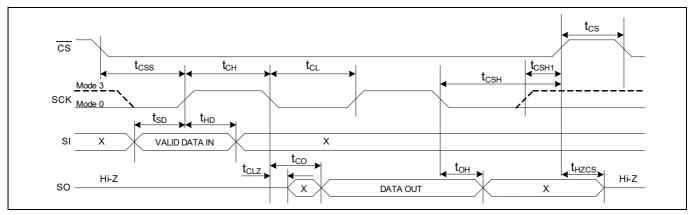

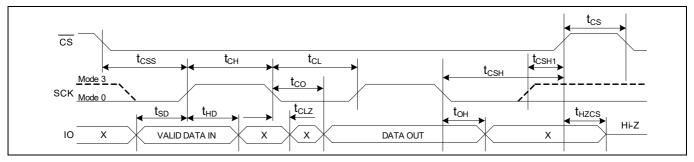

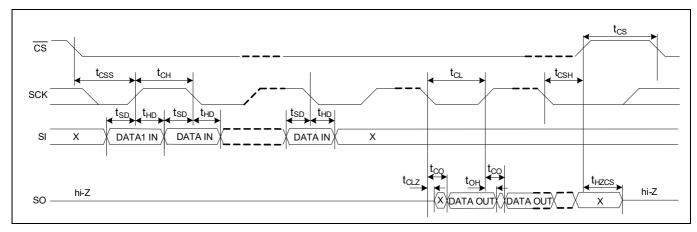

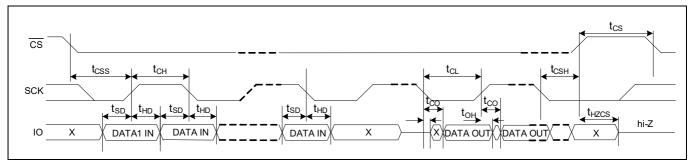

The device detects the SPI mode from the status of the SCK pin when the device is selected by bringing the  $\overline{CS}$  pin LOW. If the SCK pin is LOW when the device is selected, SPI Mode 0 is assumed and if the SCK pin is HIGH, it works in SPI Mode 3. The two SPI modes are shown in **Figure 4** and **Figure 5**. The status of the clock SCK when the bus master is not transferring data is:

- SCK remains at 0 for Mode 0

- SCK remains at 1 for Mode 3

SPI Mode 0 and SPI Mode 3 are supported for all SDR mode commands. While, all DDR mode commands support only SPI Mode 0.

Figure 4 SPI Mode 0

Figure 5 SPI Mode 3

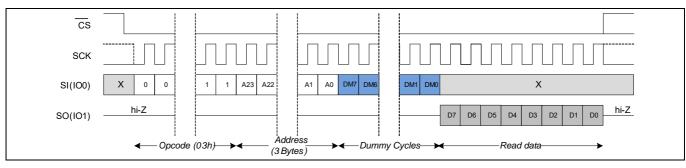

#### 3.4.1 SDR

The input data bits (includes instruction, address, and data) are always latched in on the rising edge of SCK starting from the first rising edge after  $\overline{CS}$  goes active. If the clock starts from a HIGH state (in Mode 3), the first rising edge after the clock toggles is considered. The output data is available on the falling edge of SCK.

#### 3.4.2 DDR

The instruction bits are always latched on the rising edge of SCK starting from the first rising edge after CS goes active. If the clock starts from a HIGH state (in Mode 3), the first rising edge after the clock toggles is considered. However, the address and input data that follow the instruction are latched on both the rising and falling edges of SCK. The first address bit is latched on the first rising edge of SCK following the falling edge at the end of the last instruction bit. The first bit of output data is driven on the falling edge of SCK at the end of the last access latency (dummy) cycle.

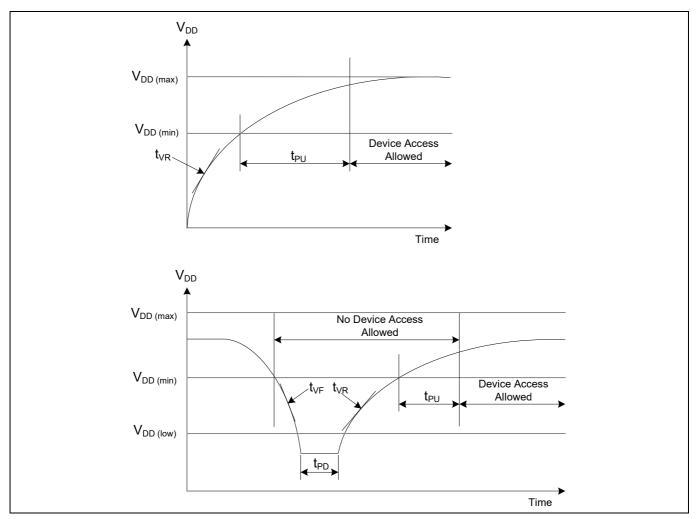

#### 3.5 Power-up to first access

When the CY15x116QSN power supply ( $V_{DD}$ ) falls below  $V_{DD}$ (low), the power-up cycle starts. CY15x116QSN waits for the  $V_{DD}$  power supply to rise above the minimum  $V_{DD}$ (min), after which the device stars its internal boot-up sequence. The boot-up sequence for CY15x116QSN includes internal power-on-reset (POR) followed by loading the internal device configuration and trim registers as well as setting the user accessible registers. All user accessible registers (Status and Configuration, Mode, ID, ECC, and CRC) are set to their default values after a successful boot-up cycle. **Table 3** shows the status of each register of CY15x116QSN after a successful power-up (or POR) sequence.

CY15x116QSN ignores all instructions until a time delay of  $t_{PU}$  has elapsed after the moment  $V_{DD}$  rises above  $V_{DD}$ (min). No instruction should be sent to the device until the end of  $t_{PU}$ . After the  $t_{PU}$ , if  $\overline{CS}$  is HIGH, the device enters Standby mode and draws standby current ( $I_{SB}$ ). The device enters Deep Power-down mode after  $t_{PU}$  if the Deep Power-down mode upon POR (DPDPOR) in **"Configuration Register 4 (CR4)"** on page 25 is set to '1' (CR4 [2] = 1).

The WIP bit of Status Register 1 (SR1[0]) cannot be used to poll the device readiness after the POR event because device is still not accessible for executing any command including RDSR1 until the  $t_{PU}$  time is over. However, if the WIP status remains HIGH even after  $t_{PU}$  time or device remains inaccessible, indicates device didn't boot up correctly (boot error). Once the boot error occurs, the device enters the following default states:

- The interface mode is set to single SPI (SDR)

- IO3R bit of CR2 (CR2[5]) is internally set '1' to enable the hardware reset (RESET) on IO3

- Register latency is set to three-clock cycle (max value)

- Output impedance is set to 45  $\Omega$

- Only RDSR1 and RDAR commands are allowed (in SPI SDR mode only) to read the SR1. All other commands will remain disabled and will return undefined data if executed.

- Reading the SR1 returns 0x61 as boot error signature

CY15x116QSN will require power cycle or hardware reset to restart the boot-up again. The above default settings will be replaced with actual user configurations after a successful boot-up.

| Function                            | Register type                  | CY15x116QSN registers status after POR                                        |

|-------------------------------------|--------------------------------|-------------------------------------------------------------------------------|

| Douise status                       | Status Register 1 (SR1)        | Default to corresponding non-volatile bits                                    |

| Device status                       | Status Register 2 (SR2)        | 0x00                                                                          |

|                                     | Configuration Register 1 (CR1) | Default to corresponding non-volatile bits                                    |

| Device configuration <sup>[2]</sup> | Configuration Register 2 (CR2) | Default to corresponding non-volatile bits                                    |

| Device configuration.               | Configuration Register 4 (CR4) | Default to corresponding non-volatile bits                                    |

|                                     | Configuration Register 5 (CR5) | Default to corresponding non-volatile bits                                    |

|                                     | Identification Register        | Default to corresponding non-volatile bits (factory set)                      |

| Identification                      | Unique Identification Register | Default to corresponding non-volatile bits (factory set)                      |

|                                     | Serial Number Register         | Default to corresponding non-volatile bits (factory set to 0x000000000000000) |

|                                     | ECC Status Register            | 0x00                                                                          |

| Error correction                    | ECC Count Register             | 0x0000                                                                        |

|                                     | ECC Address Trap Register      | 0x0000000                                                                     |

| Cyclic redundancy check             | CRC Register                   | 0x0000000                                                                     |

#### Note

<sup>2.</sup> Configuration Register 3 (CR3) is reserved for future use.

# 4 CY15x116QSN registers

CY15x116QSN supports various Status and Configuration registers for device status update and configuration settings. CY15x116QSN registers and their access details are discussed in follow on sections.

#### 4.1 Status registers

The CY15x116QSN supports two status registers - Status Register 1 (SR1) and Status Register 2 (SR2) to provide the write protect settings as well ready/CRC status of the device. The SR1 register has a volatile and an associated non-volatile register space in the F-RAM. The non-volatile register retains the device configuration during power down which is then copied to the respective volatile register during power up or after the hardware reset (JEDEC reset or RESET pin). The CY15x116QSN state machine uses only the volatile register settings to change the device configuration during normal access. Since the CY15x116QSN provides independent space for both volatile and non-volatile configuration registers, the host can program the volatile register only to make the configuration effective for the current power cycle. The non-volatile write changes the content of both volatile and non-volatile registers. Therefore, the new configurations become effective immediately for the current power cycle as well as subsequent power cycles or hardware reset cycles. The SR2 is a read only register.

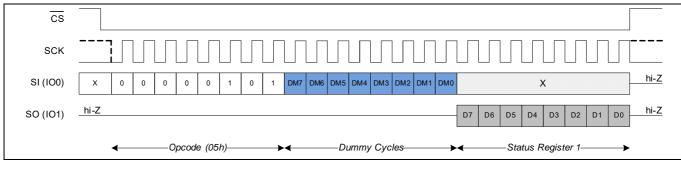

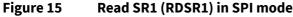

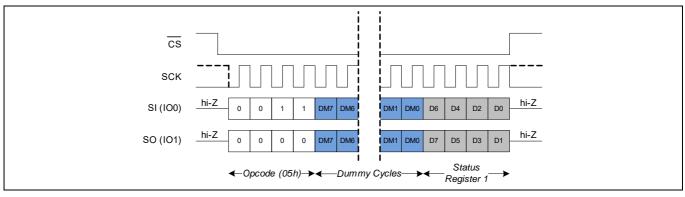

Read from Status Registers either uses dedicated Status Register Read Opcodes (RDSR1, RDSR2) or RDAR followed Status Register address. The Status Register read always returns the volatile register content. Individual Status Register details are provided in follow on sections.

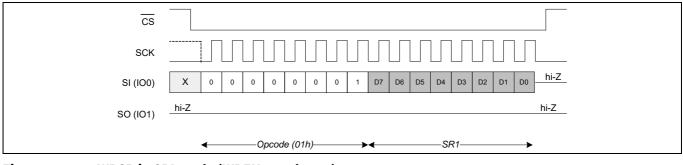

## 4.1.1 Status Register 1 (SR1)

The Status Register 1 (SR1), as shown in **Table 4**, contains both status and write protect control bits. The SR1 is accessible by WRSR and WRAR command for write and the RDSR1 or the RDAR command for read operations. The SR1 access details are provided in **"Register Access commands"** on page 33.

WRAR non-volatile write address - 0x000000

WRAR volatile write address - 0x070000

RDAR read address - 0x000000 or 0x070000

The default state shown after each bit in **Table 4** is the factory programmed value.

#### Table 4Status Register 1 (SR1)

| SR1[7]   | SR1[6]  | SR1[5]     | SR1[4]  | SR1[3]  | SR1[2]  | SR1[1]  | SR1[0]  |

|----------|---------|------------|---------|---------|---------|---------|---------|

| SRWD (0) | RFU (0) | TBPROT (0) | BP2 (0) | BP1 (0) | BP0 (0) | WEL (0) | WIP (0) |

| Table 5 | Status Register I (SRI) - Non-volatile |                                  |         |            |                                                                                                                                                                             |  |  |

|---------|----------------------------------------|----------------------------------|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Bit     | Bit name                               | Bit function                     | Туре    | Read/write | Description                                                                                                                                                                 |  |  |

| SR1[7]  | SRWD                                   | Status register write<br>disable | NV      | R/W        | <ul> <li>1 = Locks state of status &amp; configuration registers<br/>when WP is LOW</li> <li>0 = No register protection irrespective of the status<br/>of WP pin</li> </ul> |  |  |

| SR1[6]  | RFU                                    | Reser                            | ved (0) |            | Reserved for future use                                                                                                                                                     |  |  |

| SR1[5]  | TBPROT                                 | Top/bottom relative protection   | NV      | R/W        | <ul><li>1 = Protection starts at memory array bottom</li><li>0 = Protection starts at memory array top</li></ul>                                                            |  |  |

| SR1[4]  | BP2                                    |                                  | NV      |            |                                                                                                                                                                             |  |  |

| SR1[3]  | BP1                                    | Block protect bit                | NV      | R/W        | Protects the selected address range of memory array                                                                                                                         |  |  |

| SR1[2]  | BP0                                    |                                  | NV      |            |                                                                                                                                                                             |  |  |

| SR1[1]  | WEL                                    | Write enable latch               | V       | R          | WEL indicates if the device is write enabled. This bit<br>defaults to '0' (disabled) on power-up.<br>WEL = 1> write enabled<br>WEL = 0> write disabled                      |  |  |

| SR1[0]  | WIP                                    | Work in progress                 | V       | R          | 1 = Device busy<br>0 = Device ready                                                                                                                                         |  |  |

Table 5Status Register 1 (SR1) - Non-volatile

NV - Non-volatile; V - Volatile

#### Table 6Status Register 1 (SR1) - Volatile

|        | Jun      |                                  |         | •          |                                                                                                                                                                             |

|--------|----------|----------------------------------|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit    | Bit name | Bit function                     | Туре    | Read/write | Description                                                                                                                                                                 |

| SR1[7] | SRWD     | Status register write<br>disable | V       | R/W        | <ul> <li>1 = Locks state of status &amp; configuration registers<br/>when WP is LOW</li> <li>0 = No register protection irrespective of the status<br/>of WP pin</li> </ul> |

| SR1[6] | RFU      | Reser                            | ved (0) |            | Reserved for future use                                                                                                                                                     |

| SR1[5] | TBPROT   | Top/bottom relative protection   | V       | R/W        | 1 = Protection starts at memory array bottom<br>0 = Protection starts at memory array top                                                                                   |

| SR1[4] | BP2      |                                  | V       |            |                                                                                                                                                                             |

| SR1[3] | BP1      | Block protect bit                | V       | R/W        | Protects the selected address range of memory array                                                                                                                         |

| SR1[2] | BP0      |                                  | V       |            |                                                                                                                                                                             |

| SR1[1] | WEL      | Write enable latch               | V       | R          | WEL indicates if the device is write enabled. This bit<br>defaults to '0' (disabled) on power-up.<br>WEL = 1> write enabled<br>WEL = 0> write disabled                      |

| SR1[0] | WIP      | Work in progress                 | V       | R          | 1 = Device busy<br>0 = Device ready                                                                                                                                         |

V - Volatile

# 4.1.1.1 Status Register Protect (SRWD) SR1 [7]

This bit enables write protect for the Status and Configuration registers when set to '1' and the write protect (WP) pin is driven LOW. In this mode, any instruction that changes the Status registers or Configuration registers content is ignored, effectively locking the state of the device. If the SRWD is set to '0', irrespective of the WP status (LOW or HIGH), Status and Configuration registers write protection remains disabled. Refer to **Table 9** for the memory and Status Register Protection options.

# 4.1.1.2 Top or Bottom Protection (TBPROT) SR1 [5]

This bit defines the operation of the Block Protection bits BP2, BP1, and BP0. This bit controls the starting point of the memory array (from top or bottom) memory that gets protected by the Block Protection bits.

| able I                  | Start of Protection noin top (TBPROT = 0) |                      |                                          |                               |  |  |  |

|-------------------------|-------------------------------------------|----------------------|------------------------------------------|-------------------------------|--|--|--|

| Status Register content |                                           | tus Register content |                                          | Ducks studie dalueses were se |  |  |  |

| BP2                     | BP1                                       | BP0                  | Protected fraction of memory array       | Protected address range       |  |  |  |

| 0                       | 0                                         | 0                    | None                                     | None                          |  |  |  |

| 0                       | 0                                         | 1                    | Upper 1/64 <sup>th</sup> of memory array | 0x1F8000-0x1FFFFF             |  |  |  |

| 0                       | 1                                         | 0                    | Upper 1/32 <sup>nd</sup> of memory array | 0x1F0000-0x1FFFFF             |  |  |  |

| 0                       | 1                                         | 1                    | Upper 1/16 <sup>th</sup> of memory array | 0x1E0000-0x1FFFFF             |  |  |  |

| 1                       | 0                                         | 0                    | Upper 1/8 <sup>th</sup> of memory array  | 0x1C0000-0x1FFFFF             |  |  |  |

| 1                       | 0                                         | 1                    | Upper 1/4 <sup>th</sup> of memory array  | 0x180000-0x1FFFFF             |  |  |  |

| 1                       | 1                                         | 0                    | Upper half of memory array               | 0x100000-0x1FFFFF             |  |  |  |

| 1                       | 1                                         | 1                    | Full memory                              | 0x000000-0x1FFFFF             |  |  |  |

#### Table 7Start of Protection from Top (TBPROT = 0)

Table 8Start of Protection from bottom (TBPROT = 1)

| Statu | Status Register content |     | Distantial fraction of momenty array     | Drotostad addross range |

|-------|-------------------------|-----|------------------------------------------|-------------------------|

| BP2   | BP1                     | BP0 | Protected fraction of memory array       | Protected address range |

| 0     | 0                       | 0   | None                                     | None                    |

| 0     | 0                       | 1   | Lower 1/64 <sup>th</sup> of memory array | 0x000000-0x007FFF       |

| 0     | 1                       | 0   | Lower 1/32 <sup>nd</sup> of memory array | 0x000000-0x00FFFF       |

| 0     | 1                       | 1   | Lower 1/16 <sup>th</sup> of memory array | 0x000000-0x01FFFF       |

| 1     | 0                       | 0   | Lower 1/8 <sup>th</sup> of memory array  | 0x000000-0x03FFFF       |

| 1     | 0                       | 1   | Lower 1/4 <sup>th</sup> of memory array  | 0x000000-0x07FFFF       |

| 1     | 1                       | 0   | Lower half of memory array               | 0x000000-0x0FFFFF       |

| 1     | 1                       | 1   | Full memory                              | 0x000000-0x1FFFFF       |

# 4.1.1.3 Block Protection (BP2, BP1 and BP0) SR1 [4:2]

These bits define the memory array to be write-protected against memory write commands. When one or more of the BP bits is set to '1', the respective memory address is protected from write. The block protect bits (BP2, BP1, and BP0) in combination with the TBPROT bit can be used to protect an address range of the memory array. The size of the range is determined by the value of the BP bits and the upper or lower starting point of the range which is selected by the TBPROT. **Table 7** and **Table 8** show CY15x116QSN protected address range for BP[2:0] bits setting.

# 4.1.1.4 Write Enable Latch (WEL) SR1 [1]

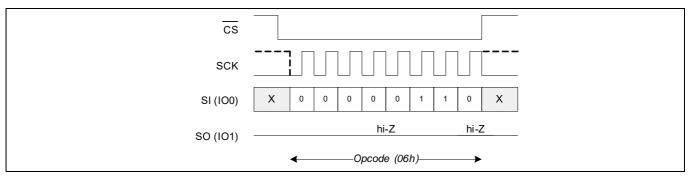

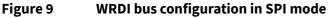

The WEL bit must be set to 1 to enable write operations to memory array or registers, as shown in **Table 9**. This bit is set to '1' only by executing the write enable (WREN) command. The WEL bit (SR1[1]) automatically clears to '0' on the rising edge of CS following opcodes including: WRDI (04h), WRSR (01h), SSWR (42h), WRAR (71h), and WRSN (C2h). The WEL bit (SR1[1]) doesn't clear to '0' on the rising edge of CS following memory write opcodes. The WEL bit is volatile and returns to its default '0' state after POR and all reset events.

|      |    | P   |                  |                    |                                                   |

|------|----|-----|------------------|--------------------|---------------------------------------------------|

| SRWD | WP | WEL | Protected blocks | Unprotected blocks | Status and Configuration registers <sup>[3]</sup> |

| Х    | Х  | 0   | Protected        | Protected          | Protected                                         |

| 0    | Х  | 1   | Protected        | Writable           | Writable                                          |

| 1    | 0  | 1   | Protected        | Writable           | Protected                                         |

| 1    | 1  | 1   | Protected        | Writable           | Writable                                          |

#### Table 9 Write protection

#### 4.1.1.5 Work-In-Progress (WIP) SR1 [0]

This is a read-only bit and indicates device ready or busy status during normal operation. The CY15x116QSN sets this bit to '1' while executing the CRC calculation. No other command (s) and event (s) set the WIP to '1' in CY15x116QSN. When WIP is '1', the CY15x116QSN can execute only read status registers using RDSR1/RDSR2 or Read Any Register (RDAR followed by status register address), CRC suspend (EPCS), and software reset (RSTEN followed by RST) commands. Other commands will be ignored while WIP is '1'. The WIP bit can't be used to poll the device ready status during power up or reset cycles. This bit is volatile and returns to its default state after POR and all reset events.

# 4.1.2 Status Register 2 (SR2)

The Status Register 2 (SR2), as shown in **Table 10**, provides the device status on CRC operations. The SR2 is a read-only volatile register and is accessible by RDSR2 or the RDAR command for read operations. The SR1 access details are provided in **"Register Access commands"** on page 33.

RDAR read address - 0x000001 or 0x070001

The default state shown after each bit in **Table 10** is the factory programmed value.

| Table 10 | Status Register 2 (SR2) |

|----------|-------------------------|

|----------|-------------------------|

| SR2[7]  | SR2[6]  | SR2[5]  | SR2[4]   | SR2[3]   | SR2[2]  | SR2[1]  | SR2[0]  |

|---------|---------|---------|----------|----------|---------|---------|---------|

| RFU (0) | RFU (0) | RFU (0) | CRCS (0) | CRCA (0) | RFU (0) | RFU (0) | RFU (0) |

| Bit    | Bit name | <b>Bit function</b> | Туре         | Read/write | Description                                            |

|--------|----------|---------------------|--------------|------------|--------------------------------------------------------|

| SR2[7] | RFU      |                     | Reserved (0) |            |                                                        |

| SR2[6] | RFU      |                     | Reserved (0) |            | Reserved for future use                                |

| SR2[5] | RFU      |                     | Reserved (0) |            |                                                        |

| SR2[4] | CRCS     | CRC suspend         | V            | R          | 1 = In CRC suspend mode<br>0 = Not in CRC suspend mode |

| SR2[3] | CRCA     | CRC abort           | V            | R          | 1 = CRC command aborted<br>0 = CRC command not aborted |

| SR2[2] | RFU      |                     | Reserved (0) |            |                                                        |

| SR2[1] | RFU      |                     | Reserved (0) |            | Reserved for future use                                |

| SR2[0] | RFU      |                     | Reserved (0) |            |                                                        |

#### Table 11Status Register 2 (SR2) - Volatile only

V - Volatile

# 4.1.2.1 CRC Suspend (CRCS) SR2 [4]

The CRC suspend (CRCS) bit is used to determine whether the device is in CRC suspend mode. When the device CRC calculation is in progress, executing the CRC suspend command (EPCS) will set this bit to '1' to indicate the CRC suspend status. The CRC resume (EPCR) command clears the CRCS bit to '0', indicates device exited the CRC suspend mode. This is a read only bit. This bit also gets cleared after resets (POR, hardware, and software).

# 4.1.2.2 CRC Abort (CRCA) SR2 [3]

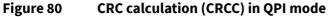

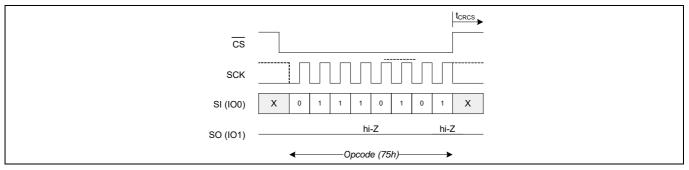

This bit indicates whether the CRC calculation (CRCC) operation is aborted. The CRC calculation is aborted when end address and start address criteria (EA < SA + 3), which is ending address should be at least 32-bit aligned word higher than the starting address, doesn't meet. This bits gets clears when subsequent CRC calculation starts successfully. This bit also gets cleared after reset (POR, hardware, and software).

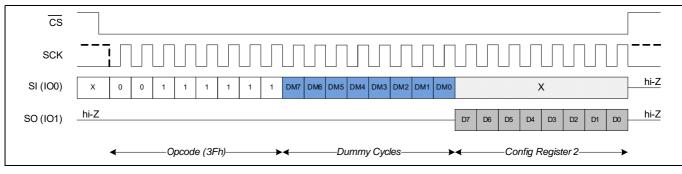

# 4.2 Configuration registers

The CY15x116QSN supports four user configuration registers - CR1, CR2, CR4, and CR5 to program various controls in the device. Each configuration register has a volatile and an associated non-volatile register space in the F-RAM. The non-volatile registers retain the device configuration during power down which <u>are then</u> copied to their respective volatile registers during power up or after the hardware reset (JEDEC reset or RESET pin). The CY15x116QSN state machine uses only the volatile register settings to change the device configuration during normal access. Since the CY15x116QSN provides independent space for both volatile and non-volatile configuration registers, the host can program volatile register only to make the configuration effective for the current power cycle. The non-volatile write changes the content of both volatile and non-volatile registers. Therefore, new configurations become effective immediately for the current power cycle as well as subsequent power cycles or hardware reset cycles.

Read from configuration registers either using dedicated configuration register read opcodes (RDCR1, RDCR2, RDCR3, RDCR4) or RDAR always returns the volatile register content. Individual configuration register details are provided in follow on sections.

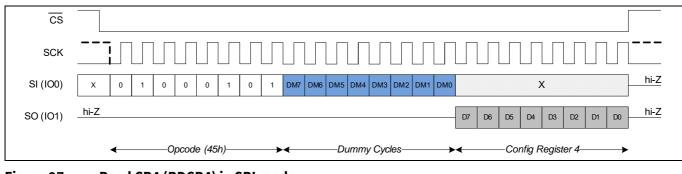

# 4.2.1 Configuration Register 1 (CR1)

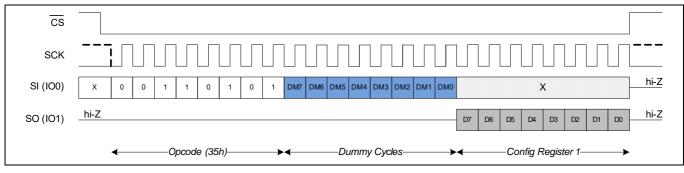

The Configuration Register 1 (CR1), as shown in **Table 12**, configures the latency (dummy) cycles for memory and special sector reads and enables the quad I/O during extended SPI access. The CR1 is accessible by the WRAR command for write and the RDCR1 or the RDAR command for read operations. The CR1 access details are provided in **"Register Access commands"** on page 33.

WRAR non-volatile write address - 0x000002

WRAR volatile write address - 0x070002

RDAR read address - 0x000002 or 0x070002

The default state shown after each bit in **Table 12** is the factory programmed value.

#### Table 12Configuration Register 1 (CR1)

|          | 0        | 0        | · /      |         |         |          |         |

|----------|----------|----------|----------|---------|---------|----------|---------|

| CR1[7]   | CR1[6]   | CR1[5]   | CR1[4]   | CR1[3]  | CR1[2]  | CR1[1]   | CR1[0]  |

| MLC3 (0) | MLC2 (0) | MLC1 (0) | MLC0 (0) | RFU (0) | RFU (0) | QUAD (0) | RFU (0) |

| Bit name | Bit function                                       | Туре                                                | Read/write                                                                                                                                                                   | Description                                                                                                                                                                                                      |

|----------|----------------------------------------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MLC3     |                                                    | NV                                                  |                                                                                                                                                                              | Configures number of latency (dummy) cycles                                                                                                                                                                      |

| MLC2     |                                                    | NV                                                  |                                                                                                                                                                              | for the memory as well as special sector read opcodes.                                                                                                                                                           |

| MLC1     | Memory                                             | NV                                                  | R/W                                                                                                                                                                          | Example-                                                                                                                                                                                                         |

| MLC0     | latency code                                       | NV                                                  |                                                                                                                                                                              | 0000 - 0 cycle<br>0110 - 6 cycles<br>1111 - 15 cycles                                                                                                                                                            |

| RFU      |                                                    | Reserved (0)                                        |                                                                                                                                                                              | Reserved for future use                                                                                                                                                                                          |

| RFU      |                                                    | Reserved (0)                                        |                                                                                                                                                                              |                                                                                                                                                                                                                  |

| QUAD     | Quad                                               | NV                                                  | R/W                                                                                                                                                                          | 1 = Quad<br>0 = Dual or serial                                                                                                                                                                                   |

| RFU      |                                                    | Reserved (0)                                        |                                                                                                                                                                              | Reserved for future use                                                                                                                                                                                          |

|          | MLC3<br>MLC2<br>MLC1<br>MLC0<br>RFU<br>RFU<br>QUAD | MLC3<br>MLC2<br>MLC1<br>MLC0<br>RFU<br>QUAD<br>Quad | MLC3     NV       MLC2     Memory<br>latency code     NV       MLC0     Memory<br>latency code     NV       RFU     Reserved (0)     Reserved (0)       QUAD     Quad     NV | MLC3     NV       MLC2     Memory<br>latency code     NV       MLC1     Memory<br>latency code     NV       MLC0     NV     R/W       RFU     Reserved (0)       RFU     Reserved (0)       QUAD     Quad     NV |

#### Table 13 Configuration Register 1 (CR1) - Non-volatile

NV - Non-volatile

| Table 14 | Configu  | ration Register        | r I (CRI) - VOIA | athe       |                                                        |

|----------|----------|------------------------|------------------|------------|--------------------------------------------------------|

| Bit      | Bit name | Bit function           | Туре             | Read/write | Description                                            |

| CR1[7]   | MLC3     |                        | V                |            | Configures number of latency (dummy) cycles            |

| CR1[6]   | MLC2     |                        | V                |            | for the memory as well as special sector read opcodes. |

| CR1[5]   | MLC1     | Memory<br>latency code | V                | R/W        | Example-                                               |

| CR1[4]   | MLC0     |                        | V                |            | 0000 - 0 cycle<br>0110 - 6 cycles<br>1111 - 15 cycles  |

| CR1[3]   | RFU      |                        | Reserved (0)     |            | Reserved for future use                                |

| CR1[2]   | RFU      |                        | Reserved (0)     |            |                                                        |

| CR1[1]   | QUAD     | Quad                   | V                | R/W        | 1 = Quad<br>0 = Dual or serial                         |

| CR1[0]   | RFU      |                        | Reserved (0)     |            | Reserved for future use                                |

#### Table 14 Configuration Register 1 (CR1) - Volatile

V - Volatile

#### 4.2.1.1 Memory Latency Code (MLC) CR1 [7:4]

These four bits configures the latency (dummy) cycles for all variable latency memory read instructions. It enables the user to adjust the memory read latency during normal operation to optimize the latency for different instructions at different operating frequencies. Dummy cycles are full clock cycles on SCK irrespective of the SPI modes and data rates (SDR and DDR).

Some read opcodes support dummy cycles following address cycles. These dummy cycles provide additional latency that is needed to complete the initial read access of the memory array before data can be returned to the host system. As the SPI clock (SCK) frequency increase, number of dummy cycles need to increase to meet the latency.

**Table 15** to **Table 17** show the max SPI clock frequency versus clock latency for each opcodes that support dummy cycles. The host controller can determine to optimize the timing by setting individual latency cycle for each opcode or can set the worst case latency which meets the latency requirement of all opcodes for a desired operating frequency. The memory read latency set for a higher frequency also applies for all lower frequencies. Hence, when the host lowers the SPI clock (SCK) from higher frequency to a lower frequency, adjusting the clock latency becomes optional.

The format (CMD, ADD, DATA) in **Table 15** header represents the transmission of these bytes over number of I/Os in different SPI modes. For example: (2, 2, 2) represents all command (CMD), address (ADDR), and data (DATA) bytes are transmitted over two I/Os (I/O0 and I/O1) in DPI mode. Similarly, (1, 2, 2) represents CMD byte is transmitted over a single I/O (I/O0), while ADDR and DATA bytes are transmitted over two I/Os (I/O0, I/O1) in dual I/O mode. (1, 1, 4) represents CMD and ADDR bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over a single I/O (I/O0), while DATA bytes are transmitted over four I/Os (I/O0, I/O1, I/O2, I/O3) in quad data mode.

Mode represents number of clock cycles required in various SPI interface modes to transmit the mode byte after address bits. Since mode bits are transmitted after the address cycles, clock cycles required to transmit mode bits are internally added to the latency calculation.

#### **16Mb EXCELON™ Ultra Ferroelectric RAM (F-RAM)** Serial (Quad SPI), 2048K × 8, 108 MHz, extended industrial

CY15x116QSN registers

| Table 15               | Latency (o      | Latency (dummy) cycles for memory read commands - with XIP mode (SDR) |                        |                    |                        |                    |                        |  |  |

|------------------------|-----------------|-----------------------------------------------------------------------|------------------------|--------------------|------------------------|--------------------|------------------------|--|--|

|                        | SPI (SDR)       | DPI (SDR)                                                             | QPI (SDR)              | Dual data<br>(SDR) | Dual I/O<br>(SDR)      | Quad data<br>(SDR) | Quad I/O<br>(SDR)      |  |  |

| Latency<br>(Dummy      | FAST_READ       | FAST_READ                                                             | FAST_READ,<br>QIOR     | DOR                | DIOR                   | QOR                | QIOR                   |  |  |

| cycles) <sup>[4]</sup> | (1, 1, 1, 1, 1) | (2, 2, 2, 2, 2)                                                       | (4, 4, 4, 4, 4)        | (1, 1, 1, 1, 2)    | (1, 2, 2, 2, 2)        | (1, 1, 1, 1, 4)    | (1, 4, 4, 4, 4)        |  |  |

|                        | Mode = 8        | Mode = 4                                                              | Mode = 2               | Mode = 8           | Mode = 4               | Mode = 8           | Mode = 2               |  |  |

| 0                      | 108 MHz         | 45 MHz <sup>[4]</sup>                                                 | 10 MHz <sup>[4]</sup>  | 108 MHz            | 45 MHz <sup>[4]</sup>  | 108 MHz            | 10 MHz <sup>[4]</sup>  |  |  |

| 1                      | 108 MHz         | 55 MHz <sup>[4]</sup>                                                 | 20 MHz <sup>[4]</sup>  | 108 MHz            | 55 MHz <sup>[4]</sup>  | 108 MHz            | 20 MHz <sup>[4]</sup>  |  |  |

| 2                      | 108 MHz         | 70 MHz <sup>[4]</sup>                                                 | 35 MHz <sup>[4]</sup>  | 108 MHz            | 70 MHz <sup>[4]</sup>  | 108 MHz            | 35 MHz <sup>[4]</sup>  |  |  |

| 3                      | 108 MHz         | 80 MHz <sup>[4]</sup>                                                 | 45 MHz <sup>[4]</sup>  | 108 MHz            | 80 MHz <sup>[4]</sup>  | 108 MHz            | 45 MHz <sup>[4]</sup>  |  |  |

| 4                      | 108 MHz         | 90 MHz <sup>[4]</sup>                                                 | 55 MHz <sup>[4]</sup>  | 108 MHz            | 90 MHz <sup>[4]</sup>  | 108 MHz            | 55 MHz <sup>[4]</sup>  |  |  |

| 5                      | 108 MHz         | 105 MHz <sup>[4]</sup>                                                | 70 MHz <sup>[4]</sup>  | 108 MHz            | 105 MHz <sup>[4]</sup> | 108 MHz            | 70 MHz <sup>[4]</sup>  |  |  |

| 6                      | 108 MHz         | 108 MHz                                                               | 80 MHz <sup>[4]</sup>  | 108 MHz            | 108 MHz                | 108 MHz            | 80 MHz <sup>[4]</sup>  |  |  |

| 7                      | 108 MHz         | 108 MHz                                                               | 90 MHz <sup>[4]</sup>  | 108 MHz            | 108 MHz                | 108 MHz            | 90 MHz <sup>[4]</sup>  |  |  |

| 8                      | 108 MHz         | 105 MHz                                                               | 105 MHz <sup>[4]</sup> | 108 MHz            | 108 MHz                | 108 MHz            | 105 MHz <sup>[4]</sup> |  |  |

| 9-15                   | 108 MHz         | 108 MHz                                                               | 108 MHz                | 108 MHz            | 108 MHz                | 108 MHz            | 108 MHz                |  |  |

| Table 16 | Latency (dummy) cycles for memory read commands - with XIP mode (DDR) |

|----------|-----------------------------------------------------------------------|

|----------|-----------------------------------------------------------------------|

|                   |                       | · · ·                 |  |  |

|-------------------|-----------------------|-----------------------|--|--|

|                   | QPI (DDR)             | Quad I/O (DDR)        |  |  |

| Latency           | DDRFR, DDRQIOR        | DDRQIOR               |  |  |

| (Dummy<br>cycles) | (4, 4, 4, 4, 4)       | (1, 4, 4, 4, 4)       |  |  |

|                   | Mode = 1              | Mode = 1              |  |  |

| 0                 | NA                    |                       |  |  |

| 1                 | Ν                     | IA                    |  |  |

| 2                 | 10 MHz <sup>[4]</sup> | 10 MHz <sup>[4]</sup> |  |  |

| 3                 | 15 MHz <sup>[4]</sup> | 15 MHz <sup>[4]</sup> |  |  |

| 4                 | 25 MHz <sup>[4]</sup> | 25 MHz <sup>[4]</sup> |  |  |

| 5                 | 33 MHz <sup>[4]</sup> | 33 MHz <sup>[4]</sup> |  |  |

| 6                 | 40 MHz <sup>[4]</sup> | 40 MHz <sup>[4]</sup> |  |  |

| 7-15              | 46 MHz <sup>[4]</sup> | 46 MHz <sup>[4]</sup> |  |  |

#### Note

4. This parameter is guaranteed by characterization; not tested in production.

| able 17           | Latency (dummy) cycles for memory read commands - without XIP mode |                        |                        |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------|------------------------|------------------------|--|--|--|--|--|

|                   | SPI (SDR)                                                          | DPI (SDR)              | QPI (SDR)              |  |  |  |  |  |

| Latency           |                                                                    | READ, ECCRD, SSRD      |                        |  |  |  |  |  |

| (Dummy<br>cycles) | (1, 1, 1, 1, 1)                                                    | (2, 2, 2, 2, 2)        | (4, 4, 4, 4, 4)        |  |  |  |  |  |

|                   | Mode = NA                                                          | Mode = NA              | Mode = NA              |  |  |  |  |  |

| 0                 | 35 MHz <sup>[5]</sup>                                              | NA                     | NA                     |  |  |  |  |  |

| 1                 | 45 MHz <sup>[5]</sup>                                              | NA                     | NA                     |  |  |  |  |  |

| 2                 | 55 MHz <sup>[5]</sup>                                              | 20 MHz <sup>[5]</sup>  | 10 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 3                 | 70 MHz <sup>[5]</sup>                                              | 35 MHz <sup>[5]</sup>  | 20 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 4                 | 80 MHz <sup>[5]</sup>                                              | 45 MHz <sup>[5]</sup>  | 35 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 5                 | 90 MHz <sup>[5]</sup>                                              | 55 MHz <sup>[5]</sup>  | 45 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 6                 | 105 MHz <sup>[5]</sup>                                             | 70 MHz <sup>[5]</sup>  | 55 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 7                 | 108 MHz                                                            | 80 MHz <sup>[5]</sup>  | 70 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 8                 | 108 MHz                                                            | 90 MHz <sup>[5]</sup>  | 80 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 9                 | 108 MHz                                                            | 105 MHz <sup>[5]</sup> | 90 MHz <sup>[5]</sup>  |  |  |  |  |  |

| 10                | 108 MHz                                                            | 108 MHz                | 105 MHz <sup>[5]</sup> |  |  |  |  |  |

| 11-15             | 108 MHz                                                            | 108 MHz                | 108 MHz                |  |  |  |  |  |

#### 4.2.1.2 Quad Data Width (QUAD) CR1 [1]

When set to '1', this bit switches the data width of the device to 4 I/Os – quad mode, that is WP becomes I/O2 and RESET / (I/O3) becomes I/O3. If the alternate function is enabled on I/O3 by setting IO3R bit in Configuration Register 2 (CR2[5]), RESET / (I/O3) works as I/O3 when CS is low and RESET input when CS is HIGH. The WP input is disabled and is internally set to '1'. The QUAD bit must be set to '1' when executing the extended SPI read commands: quad output read, and quad I/O read, and DDR quad I/O read. The impact of "QUAD" bit setting on various SPI interfaces are shown in Table 21.

# 4.2.2 Configuration Register 2 (CR2)

The Configuration Register 2 (CR2), as shown in **Table 18**, controls the serial interface settings. The CR2 is accessible by the WRAR command for write and the RDCR2 or the RDAR command for read operations. The CR2 access details are provided in **"Register Access commands"** on page 33.

WRAR non-volatile write address - 0x000003

WRAR volatile write address - 0x070003

RDAR read address - 0x000003 or 0x070003

The default state shown after each bit in **Table 18** is the factory programmed value.

#### Table 18Configuration Register 2 (CR2)

| CR2[7]  | CR2[6]  | CR2[5]   | CR2[4]  | CR2[3]  | CR2[2]  | CR2[1]  | CR2[0]  |

|---------|---------|----------|---------|---------|---------|---------|---------|

| RFU (0) | QPI (0) | IO3R (0) | DPI (0) | RFU (0) | RFU (0) | RFU (0) | RFU (0) |

#### Table 19 Configuration Register 2 (CR2) - Non-volatile

|        |          | • •                |              |            |                                                                                                   |

|--------|----------|--------------------|--------------|------------|---------------------------------------------------------------------------------------------------|

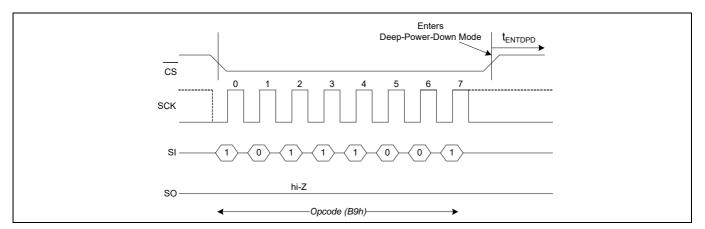

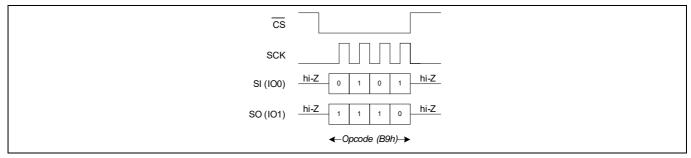

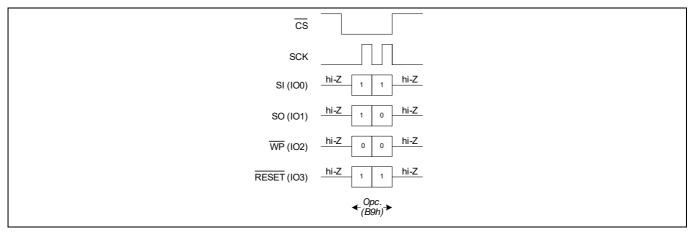

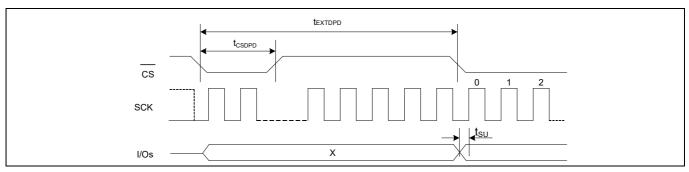

| Bit    | Bit name | Bit function       | Туре         | Read/write | Description                                                                                       |