#### Features

- Integrated Phase-Locked Loop (PLL)

- Low Jitter, High Accuracy Outputs

- VCXO with Analog Adjust

- 3.3 V Operation

- Compatible with MK3727 (-1, -4)

- Application compatibility for a wide variety of Designs

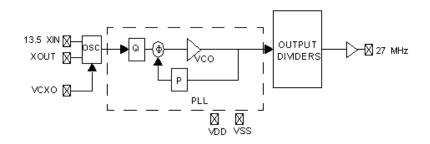

CY241V08A-01, -04 Logic Block Diagram

- Enables Design compatibility

- Lower Drive Strength settings (CY241V08A–04)

#### **Benefits**

- Digital VCXO control

- Second source for existing designs

- Highest performance PLL tailored for multimedia applications

- Meets critical timing requirements in complex system designs

### **Functional Description**

For a complete list of related documentation, click here.

### **Selector Guide**

| Part Number  | Outputs | Input Frequency Range                                                 | Output<br>Frequencies | VCXO Control<br>Curve | Other Features                                                  |

|--------------|---------|-----------------------------------------------------------------------|-----------------------|-----------------------|-----------------------------------------------------------------|

| CY241V08A-01 | 1       | 13.5 MHz pullable crystal input according to Cypress specification    | 1 copy of 27 MHz      | linear                | Compatible with MK3727                                          |

| CY241V08A-04 |         | 13.5 MHz pullable crystal input<br>according to Cypress specification | 1 copy of 27 MHz      |                       | Same as CY241V08A-01<br>except lower drive strength<br>settings |

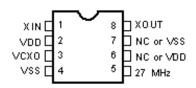

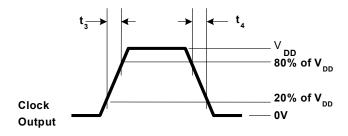

### **Pin Configurations**

Figure 1. 8-pin SOIC pinout

CY241V08A-01, -04

### **Pin Descriptions**

| Name   | Pin Number | Description                   |

|--------|------------|-------------------------------|

| XIN    | 1          | Reference crystal input       |

| VDD    | 2          | Voltage supply                |

| VCXO   | 3          | Input analog control for VCXO |

| VSS    | 4          | Ground                        |

| 27 MHz | 5          | 27 MHz clock output           |

| NC/VDD | 6          | No connect or voltage supply  |

| NC/VSS | 7          | No connect or ground          |

| XOUT   | 8          | Reference crystal output      |

### **Absolute Maximum Conditions**

Exceeding maximum ratings may shorten the useful life of the device. User guidelines are not tested.

| Supply Voltage (V <sub>DD</sub> ) | )–0.5 to +7.0 V                     |

|-----------------------------------|-------------------------------------|

| DC Input Voltage                  | $-0.5$ V to V <sub>DD</sub> + 0.5 V |

| . –55 °C to +125 °C |

|---------------------|

| –40 °C to +125 °C   |

| > 10 years          |

| 350 mW              |

| > 2000 V            |

|                     |

### **Pullable Crystal Specifications**

| Parameter <sup>[1]</sup>       | Description                                              | Comments                                                                                   | Min  | Тур  | Мах  | Unit |

|--------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|------|------|

| F <sub>NOM</sub>               | Nominal crystal frequency                                | Parallel resonance, fundamental mode, AT cut                                               | -    | 13.5 | _    | MHz  |

| C <sub>LNOM</sub>              | Nominal load capacitance                                 |                                                                                            | _    | 14   | -    | pF   |

| R <sub>1</sub>                 | Equivalent series resistance<br>(ESR)                    | Fundamental mode                                                                           | -    | -    | 25   | Ω    |

| R <sub>3</sub> /R <sub>1</sub> | Ratio of third overtone mode ESR to fundamental mode ESR | Ratio used because typical R <sub>1</sub><br>values are much less than the<br>maximum spec | 3    | -    | _    | -    |

| DL                             | Crystal drive level                                      | No external series resistor assumed                                                        | 150  | -    | -    | μW   |

| F <sub>3SEPHI</sub>            | Third overtone separation from 3 × F <sub>NOM</sub>      | High side                                                                                  | 300  | -    | -    | ppm  |

| F <sub>3SEPLO</sub>            | Third overtone separation from 3 × F <sub>NOM</sub>      | Low side                                                                                   | -    | -    | -150 | ppm  |

| C <sub>0</sub>                 | Crystal shunt capacitance                                |                                                                                            | -    | -    | 7    | pF   |

| C <sub>0</sub> /C <sub>1</sub> | Ratio of shunt to motional capacitance                   |                                                                                            | 180  | -    | 250  | -    |

| C <sub>1</sub>                 | Crystal motional capacitance                             |                                                                                            | 14.4 | 18   | 21.6 | fF   |

# **Recommended Operating Conditions**

| Parameter         | Description                                                                                       |      | Тур | Max   | Unit |

|-------------------|---------------------------------------------------------------------------------------------------|------|-----|-------|------|

| V <sub>DD</sub>   | Operating Voltage                                                                                 |      | 3.3 | 3.465 | V    |

| T <sub>A</sub>    | Ambient Temperature                                                                               | 0    | -   | 70    | °C   |

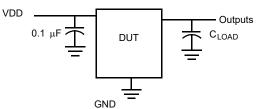

| C <sub>LOAD</sub> | Maximum Load Capacitance                                                                          | -    | -   | 15    | pF   |

| t <sub>PU</sub>   | Power up time for all VDD pins to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | _   | 500   | ms   |

Note

1. Crystals that meet this specification include: Ecliptek ECX-5788-13.500M, Siward XTL001050A-13.5-14-400, Raltron A-13.500-14-CL, PDI HA13500XFSA14XC.

### **DC Electrical Specifications**

| Parameter            | Name                   | Description                                                       | Min | Тур | Max             | Unit |

|----------------------|------------------------|-------------------------------------------------------------------|-----|-----|-----------------|------|

| I <sub>OH</sub>      | Output HIGH Current    | $V_{OH} = V_{DD} - 0.5 \text{ V}, \text{ V}_{DD} = 3.3 \text{ V}$ | 12  | 24  | -               | mA   |

| I <sub>OL</sub>      | Output LOW Current     | V <sub>OL</sub> = 0.5 V, V <sub>DD</sub> = 3.3 V                  | 12  | 24  | -               | mA   |

| C <sub>IN</sub>      | Input Capacitance      | Except XIN, XOUT pins                                             | -   | -   | 7               | pF   |

| V <sub>VCXO</sub>    | VCXO Input Range       |                                                                   | 0   | -   | V <sub>DD</sub> | V    |

| f <sub>ΔXO</sub> [2] | VCXO Pullability Range | Low Side                                                          | -   | -   | -115            | ppm  |

|                      |                        | High Side                                                         | 115 | -   | -               | ppm  |

| I <sub>VDD</sub>     | Supply Current         |                                                                   | -   | 30  | 35              | mA   |

#### **Thermal Resistance**

| Parameter <sup>[3]</sup> | Description                              | Test Conditions                                                                                        | 8-pin SOIC | Unit |

|--------------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------|------------|------|

| $\Theta_{JA}$            | (junction to ambient)                    | Test conditions follow standard test methods and procedures for measuring thermal impedance, according |            | °C/W |

| $\Theta^{JC}$            | Thermal resistance<br>(junction to case) | to EIA/JESD51.                                                                                         | 53         | °C/W |

# **AC Electrical Specifications**

(V<sub>DD</sub> = 3.3 V)

| Parameter <sup>[4]</sup> | Name                  | Description                                                                                                             | Min | Тур | Max | Unit |

|--------------------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

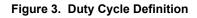

| DC                       | Output Duty Cycle     | Duty Cycle is defined in Figure 3, 50% of $V_{DD}$                                                                      | 45  | 50  | 55  | %    |

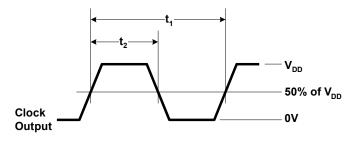

| ER <sub>OR</sub>         | Rising Edge Rate -01  | Output Clock Edge Rate,<br>Measured from 20% to 80% of V <sub>DD</sub> ,<br>C <sub>LOAD</sub> = 15 pF<br>See Figure 4.  | 0.8 | 1.4 | _   | V/ns |

| ER <sub>OF</sub>         | Falling Edge Rate -01 | Output Clock Edge Rate,<br>Measured from 80% to 20% of V <sub>DD</sub> ,<br>C <sub>LOAD</sub> = 15 pF,<br>See Figure 4. | 0.8 | 1.4 | _   | V/ns |

| ER <sub>OR</sub>         | Rising Edge Rate -04  | Output Clock Edge Rate,<br>Measured from 20% to 80% of V <sub>DD</sub> ,<br>C <sub>LOAD</sub> = 15 pF,<br>See Figure 4. | 0.7 | 1.1 | -   | V/ns |

| ER <sub>OF</sub>         | Falling Edge Rate -04 | Output Clock Edge Rate,<br>Measured from 80% to 20% of V <sub>DD</sub> ,<br>C <sub>LOAD</sub> = 15 pF,<br>See Figure 4. | 0.7 | 1.1 | -   | V/ns |

| t <sub>9</sub>           | Clock Jitter          | Peak-to-peak period jitter                                                                                              | -   | -   | 100 | ps   |

| t <sub>10</sub>          | PLL Lock Time         |                                                                                                                         | -   | -   | 3   | ms   |

#### Notes

3. Tested initially and after any design or process change that may affect these parameters.

4. Not 100% tested.

<sup>2. -115/+115</sup> ppm assumes 2.5 pF of additional board level load capacitance. This range will be shifted down with more board capacitance or shifted up with less board capacitance.

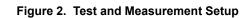

#### **Test and Measurement Setup**

### **Voltage and Timing Definitions**

Figure 4. ER =  $(0.6 \text{ x V}_{DD})/t_3$ , EF =  $(0.6 \text{ x V}_{DD})/t_4$

### **Ordering Information**

| Ordering Code                                                                                                 | Package Type | Operating<br>Range                                                                        | Operating<br>Voltage | Features                  |

|---------------------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------------------------------------------------|----------------------|---------------------------|

| Pure Sn                                                                                                       |              | -                                                                                         |                      |                           |

| CY241V8ASXC-1S                                                                                                | 8-pin SOIC   | Commercial                                                                                | 3.3 V                | Linear VCXO control curve |

| Ordering Code Definitions $\frac{CY}{1} \xrightarrow{241V8A} \xrightarrow{S} \xrightarrow{X} \xrightarrow{C}$ |              | ( = blank or T<br>lank = Tube; T<br>opecific Configur<br>emperature Gra<br>c = Commercial | ration Code: XX      | K = 01 or 1               |

Pb-free

Package Type: S = 8-pin SOIC Base Part Number

Company ID: CY = Cypress

Not Recommended for New Designs

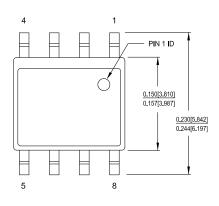

#### **Package Diagrams**

Figure 5. 8-pin SOIC (150 Mils) S0815/SZ815/SW815 Package Outline, 51-85066

- 1. DIMENSIONS IN INCHES[MM] MIN. MAX.

- 2. PIN 1 ID IS OPTIONAL, ROUND ON SINGLE LEADFRAME RECTANGULAR ON MATRIX LEADFRAME

- 3. REFERENCE JEDEC MS-012

- 4. PACKAGE WEIGHT 0.07gms

| PART #  |               |  |

|---------|---------------|--|

| S08.15  | STANDARD PKG  |  |

| SZ08.15 | LEAD FREE PKG |  |

| SW8.15  | LEAD FREE PKG |  |

#### 0.010[0.254] X 45° 0.189[4.800] SEATING PLANE 0.196[4.978] 0.016[0.406] 0.061[1.549] 0.068[1.727] 0.004[0.100] $\frown$ 0.050[1.270] BSC 0.0075[0.190] 0.004[0.100] 0.0098[0.249] 0°~8° 0.016[0.406] 0.0098[0.249] 0.035[0.889] 0.0138[0.350] 0.0192[0.487]

51-85066 \*I

#### Acronyms

| Acronym | Description                           |

|---------|---------------------------------------|

| ESD     | Electrostatic Discharge               |

| ESR     | Equivalent Series Resistance          |

| PLL     | Phase Locked Loop                     |

| SOIC    | Small Outline Integrated Circuit      |

| VCXO    | Voltage Controlled Crystal Oscillator |

### **Document Conventions**

#### **Units of Measure**

| Symbol | Unit of Measure   |  |  |

|--------|-------------------|--|--|

| °C     | degree Celsius    |  |  |

| fF     | femtofarad        |  |  |

| MHz    | megahertz         |  |  |

| μF     | microfarad        |  |  |

| μW     | microwatt         |  |  |

| mA     | milliampere       |  |  |

| ms     | millisecond       |  |  |

| mW     | milliwatt         |  |  |

| ns     | nanosecond        |  |  |

| Ω      | ohm               |  |  |

| %      | percent           |  |  |

| pF     | picofarad         |  |  |

| ppm    | parts per million |  |  |

| ps     | picosecond        |  |  |

| V      | volt              |  |  |

# **Document History Page**

| Rev. | ECN No. | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                            |

|------|---------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **   | 214069  | 03/26/2004         | New data sheet.                                                                                                                                                                                                                                                                  |

| *A   | 220404  | 04/22/2004         | Minor Change:<br>Post to external web.                                                                                                                                                                                                                                           |

| *B   | 393122  | 08/22/2005         | Updated Document Title to read as "CY241V08A-01,04/CY241V8A-01, MPEG Clock<br>Generator with VCXO".<br>Updated Ordering Information:<br>Updated part numbers.                                                                                                                    |

| *C   | 414184  | 12/14/2005         | Minor Change:<br>Updated Benefits:<br>Deleted unnecessary text.                                                                                                                                                                                                                  |

| *D   | 455059  | 04/21/2006         | Updated Ordering Information:<br>Updated part numbers.<br>Updated to new template.<br>Post to internal spec system.                                                                                                                                                              |

| *E   | 2759384 | 09/02/2009         | Updated to new template.<br>Post to external web.                                                                                                                                                                                                                                |

| *F   | 2897423 | 03/22/2010         | Updated Ordering Information:<br>Updated part numbers.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *C to *D.<br>Updated to new template.<br>Completing Sunset Review.                                                                                  |

| *G   | 4009177 | 05/23/2013         | Updated Ordering Information:<br>No change in part numbers.<br>Added Ordering Code Definitions.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *D to *F.<br>Added Acronyms and Units of Measure.<br>Updated to new template.<br>Completing Sunset Review. |

| *H   | 4580603 | 11/26/2014         | Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the end.<br>Updated Ordering Information:<br>Updated part numbers.                                                                                                       |

| *    | 5267358 | 05/11/2016         | Added Thermal Resistance.<br>Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *F to *H.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                               |

| *J   | 6073305 | 02/16/2018         | Updated Package Diagrams:<br>spec 51-85066 – Changed revision from *H to *I.<br>Updated to new template.                                                                                                                                                                         |

| *K   | 6903402 | 06/22/2020         | Added watermark "Not Recommended for New Designs" across the document.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                                                                  |

#### Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### Products

| Arm <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

#### PSoC<sup>®</sup> Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Code Examples | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2004–2020. This document is the property of Cypress Semiconductor Corporation and its subsidiaries ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and other countries worldwide. Cypress rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through reseliers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress shall have no liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. CYPRESS DOES NOT REPRESENT, WARRANT, OR GUARANTEE THAT CYPRESS PRODUCTS, OR SYSTEMS CREATED USING CYPRESS PRODUCTS, WILL BE FREE FROM CORRUPTION, ATTACK, VIRUSES, INTERFERENCE, HACKING, DATA LOSS OR THEFT, OR OTHER SECURITY INTRUSION (collectively, "Security Breach"). Cypress disclaims any liability relating to any Security Breach, and you shall and hereby do release Cypress from any claim, damage, or other liability arising from any Security Breach. In events and described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. "High-Risk Device" means any device or system whose failure could cause personal injury, death, or properly damage. Examples of High-Risk Devices are weapons, nuclear installations, surgical implants, and other medical devices. "Critical Component" means any component of a High-Risk Device whose failure to perform can be reasonably expected to cause, directly or indirectly, the failure of the High-Risk Device, or to affect its safety or effectiveness. Cypress is not liable,

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.