# CY2SSTV16857

### Features

- Differential Clock Inputs up to 280 MHz

- Supports LVTTL switching levels on the RESET pin

- Output drivers have controlled edge rates, so no external resistors are required

- Two KV ESD protection

- Latch-up performance exceeds 100 mA: JESD78, Class II

- Conforms to JEDEC STD (JESD82-3) for buffered DDR DIMMs

- 48-pin TSSOP

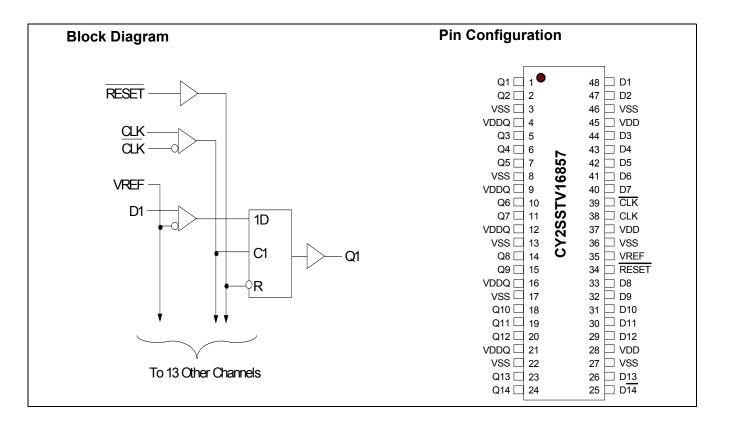

#### Description

This 14-bit registered buffer is designed specifically for 2.3V to 2.7V  $V_{DD}$  operation and is characterized for operation from 0°C to + 85°C.

All inputs are compatible with the JEDEC Standard for SSTL\_2, except the LVCMOS reset (RESET) input. All outputs are SSTL\_2, Class II-compatible.

<u>The</u> SSTV16857 operates from a differential clock (CLK and CLK). Data is measured at the crossing of CLK going HIGH, and CLK going LOW.

# 14-Bit Registered Buffer PC2700-/PC3200-Compliant

When RESET is LOW, the differential input receivers are disabled, and undriven (floating) data, clock, and REF voltage inputs are allowed. In addition, when RESET is LOW, all registers are reset and all outputs force to the LOW state. The LVCMOS RESET input must always be held at a valid logic HIGH or LOW level.

To ensure defined outputs from the register before a stable clock has been supplied, RESET must be held in the LOW state during power-up.

In the DDR registered DIMM application, RESET is specified to be completely asynchronous with respect to CLK and CLK. Therefore, no timing relationship can be guaranteed between the two. When entering reset, the register will be cleared and the outputs will be driven LOW quickly, relative to the time to disable the differential input receivers, thus ensuring no glitches on the output. However, when coming out of reset, the register will become active quickly, relative to the time to enable the differential input receivers. As long as the data inputs are low, and the clock is stable during the time from the LOW-to-HIGH transition of RESET until the input receivers are fully enabled, the design must ensure that the outputs will remain LOW.

**Cypress Semiconductor Corporation** Document #: 38-07443 Rev. \*D

# **Pin Description**

| Pin                                                    | Name     | I/O    | Туре | Description                                                                                |

|--------------------------------------------------------|----------|--------|------|--------------------------------------------------------------------------------------------|

| 34                                                     | RESET    | I      |      |                                                                                            |

| 3,8,13,17,22,27,36,46                                  | VSS      | Ground |      | Ground.                                                                                    |

| 28, 37, 45                                             | VDD      | Power  |      | 2.5V nominal supply voltage.                                                               |

| 1, 2, 5, 6, 7, 10, 11, 14, 15, 18, 19,<br>20, 23, 24   | Q(1:14)  | 0      |      | Data outputs, SSTL_2, Class II output.                                                     |

| 25, 26, 29, 30, 31, 32, 33, 40, 41, 42, 43, 44, 47, 48 | D(1:14)  | I      |      | Data input clocked on the crossing of the rising edge of CLK, and the falling edge of CLK. |

| 39, 38                                                 | CLK, CLK | 1/1    |      | Differential clock input.                                                                  |

| 4, 8, 12, 16, 21                                       | VDDQ     | Power  |      | Power supply voltage quiet, 2.5V nominal.                                                  |

| 35                                                     | VREF     | I      |      | Input reference voltage, 1.25V nominal.                                                    |

### Absolute Maximum Conditions<sup>[1, 2, 3]</sup>

This device contains circuitry designed to protect the inputs against damage due to high static voltages or electric field; however, precautions should be taken to avoid application of any voltage higher than the maximum rated voltages to this circuit. For proper operation,  $V_{in}$  and  $V_{out}$  should be constrained to the range:

$V_{SS} < (V_{in} \text{ or } V_{out}) < V_{DD}.$

Unused inputs must always be tied to an appropriate logic voltage level (either  $V_{SS}$  or  $V_{DD}$ ).

| Parameter                        | Description                                                        | Condition                              | Min. | Max.             | Unit  |

|----------------------------------|--------------------------------------------------------------------|----------------------------------------|------|------------------|-------|

| V <sub>DD</sub>                  | Supply Voltage <sup>[4]</sup>                                      | Non-functional                         | 2.3  | 2.7              | VDC   |

| V <sub>DD</sub>                  | Operating Voltage <sup>[4]</sup>                                   | Functional                             | 2.3  | 2.7              | VDC   |

| V <sub>in</sub>                  | Input Voltage                                                      | Relative to V <sub>SS</sub>            | 0    | V <sub>DD</sub>  | VDC   |

| Voutom                           | Output Voltage                                                     | Relative to V <sub>SS</sub>            |      | V <sub>DDQ</sub> | VDC   |

| I <sub>OUT</sub>                 | DC Output Current                                                  |                                        |      | ±50              | mA    |

| I <sub>IK</sub>                  | Continuous Clamp Current                                           | $V_{I} < 0 \text{ or } V_{I} > V_{SS}$ |      | ±50              | mA    |

| I <sub>OK</sub>                  | Continuous Clamp Current                                           | V <sub>O</sub> < 0                     |      | -50              | mA    |

| I <sub>DD/</sub> I <sub>SS</sub> | Continuous current through each V <sub>DD</sub> or V <sub>SS</sub> |                                        |      | ±100             | mA    |

| LUI                              | Latch Up Immunity                                                  | Exceeds spec of                        | 1(   | 00               | mA    |

| R <sub>PS</sub>                  | Power Supply Ripple                                                | Ripple Frequency < 100 kHz             |      | 150              | mVp-p |

| Τ <sub>s</sub>                   | Temperature, Storage                                               | Non-functional                         | -65  | +150             | °C    |

| T <sub>a</sub>                   | Temperature, Operating Ambient                                     | Functional                             | 0    | +70              | °C    |

| T <sub>j</sub>                   | Temperature, Junction                                              | Functional                             |      | 165              | °C    |

| Ø <sub>Jc</sub>                  | Dissipation, Junction to Case                                      | Mil-Spec 883E Method 1012.1            | 22   | .23              | °C/W  |

| Ø <sub>JA</sub>                  | Dissipation, Junction to Ambient                                   | JEDEC (JESD 51)                        | 74   | .52              | °C/W  |

| UL <sub>FL</sub>                 | Flammability                                                       | By design and verification             | V-   | - 0              | Grade |

| MSL                              | Moisture Sensitivity                                               | By design and verification             | MSI  | _ – 1            | Grade |

| ESD <sub>h</sub>                 | ESD Protection (Human Body Model)                                  |                                        | 2000 |                  | V     |

Table 1. DC Electrical Specifications (V<sub>DD</sub> = Temperature = 0°C to +85 °C)

| Parameter        | Description                                                   |                            | Condition                                                                                                    | Min.                        | Тур.             | Max.                        | Unit |

|------------------|---------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------|------------------|-----------------------------|------|

| V <sub>DD</sub>  | Supply Voltage                                                | PC1600,2100,2700<br>PC3200 |                                                                                                              | 2.5                         | 2.6              | 2.7                         | V    |

| V <sub>DDQ</sub> | Output Supply Voltage                                         | PC1600,2100,2700<br>PC3200 |                                                                                                              | 2.5                         | 2.6              | 2.7                         | V    |

| V <sub>REF</sub> | Reference voltage<br>(V <sub>REF</sub> = V <sub>DDQ</sub> /2) | PC1600,2100,2700<br>PC3200 |                                                                                                              | 1.25                        | 1.3              | 1.35                        | V    |

| V <sub>TT</sub>  | Termination voltage                                           |                            |                                                                                                              | V <sub>REF</sub> –<br>40 mV | V <sub>REF</sub> | V <sub>REF</sub> +4<br>0 mV | V    |

| V <sub>IH</sub>  | Input Voltage, High                                           |                            | RESET                                                                                                        | 1.7                         |                  |                             | V    |

| V <sub>IL</sub>  | Input Voltage, Low                                            |                            | RESET                                                                                                        |                             |                  | 0.7                         | V    |

| V <sub>OL</sub>  | Output Voltage, Low                                           |                            | V <sub>DD</sub> /V <sub>DDQ</sub> = 2.3V to 2.7V, I <sub>OL</sub> =<br>100 μA, V <sub>DD</sub> = 2.3 to 2.7V |                             |                  | 0.2                         | V    |

|                  |                                                               |                            | $V_{DD}/V_{DDQ}$ = 2.3V, $I_{OL}$ = 16 mA,<br>$V_{DD}$ = 2.3V                                                |                             |                  | 0.35                        |      |

Notes:

Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended period may affect reliability.

3. All terminals except  $V_{DD}$ .

4. V<sub>DD</sub>/V<sub>DDQ</sub> terminals.

| Parameter        | Description            | Condition                                                                                                    | Min.                     | Тур. | Max. | Unit |

|------------------|------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------|------|------|------|

| V <sub>OH</sub>  | Output Voltage, High   | V <sub>DD</sub> /V <sub>DDQ</sub> = 2.3V to 2.7V, I <sub>OH</sub> =<br>-100 μA, V <sub>DD</sub> =2.3 to 2.7V | V <sub>DD</sub> -<br>0.2 |      |      | V    |

|                  |                        | $V_{DD}/V_{DDQ}$ = 2.3V, $I_{OH}$ = -16 mA                                                                   | 1.95                     |      |      |      |

| IIL              | Input Current          |                                                                                                              |                          | •    |      |      |

|                  | Data Inputs            | V <sub>I</sub> = 1.7V or 0.8V, V <sub>REF</sub> = 1.15V or<br>1.35V, V <sub>DD</sub> = 2.7V                  |                          |      | ±5   | μΑ   |

|                  |                        | V <sub>I</sub> = 2.7V or 0,V <sub>REF</sub> = 1.15V or<br>1.35V, V <sub>DD</sub> = 2.7V                      |                          |      | ± 5  | μΑ   |

| t4U.com          |                        | V <sub>I</sub> = 1.7V or 0.8V, V <sub>REF</sub> = 1.15V or<br>1.35V, V <sub>DD</sub> = 3.6V                  |                          |      | ± 5  | μΑ   |

|                  |                        | V <sub>I</sub> = 2.7V or 0                                                                                   |                          |      | ± 5  | μA   |

|                  | CLK, CLK               | V <sub>I</sub> = 1.7V or 0.8V, V <sub>REF</sub> = 1.15V or<br>1.35V                                          |                          |      | ±1   | μΑ   |

|                  |                        | V <sub>I</sub> = 2.7V or 0, V <sub>REF</sub> = 1.15V or<br>1.35V, V <sub>dd</sub> = 2.7V                     |                          |      | ± 1  | μΑ   |

|                  | RESET                  | $V_{I} = V_{DD} \text{ or } V_{SS}, V_{DD} = 2.7V$                                                           |                          |      | ± 5  | μA   |

|                  | VREF                   | V <sub>I</sub> = 1.5V or 1.35V, V <sub>DD</sub> = 2.7                                                        |                          |      | ±5   | μA   |

| I <sub>IH</sub>  | Input Current, High    | Data inputs only                                                                                             |                          |      |      | mA.  |

| I <sub>DD</sub>  | Dynamic Supply Current | V <sub>I</sub> = 1.7V or 0.8V, I <sub>O</sub> = 0, V <sub>DD</sub> = 2.7V                                    |                          |      | 90   | mA   |

|                  |                        | $V_1 = 2.7V \text{ or } 0, I_0 = 0, V_{DD} = 2.7V$                                                           |                          |      | 90   | mA   |

| C <sub>in</sub>  | Input pin capacitance  | ·                                                                                                            |                          | •    |      | •    |

|                  | RESET                  | V <sub>I</sub> = 1.7V or 0.8V, I <sub>O</sub> = 0, V <sub>DD</sub> = 2.7V                                    |                          | 3    |      | pF   |

|                  | Clock and Data Inputs  |                                                                                                              | 2.5                      | 2.7  | 3.5  | pF   |

| L <sub>pin</sub> | Pin Inductance         | All                                                                                                          | 2.1                      |      | 4.5  | nH   |

## Table 1. DC Electrical Specifications (V<sub>DD</sub> = Temperature = $0^{\circ}C$ to +85 $^{\circ}C$ ) (continued)

Table 2. AC Input Electrical Specifications (V<sub>DD</sub> = 2.5 VDC  $\pm$  5%, Temperature = 0°C to +85°C)

|                    |                                   |                                                                                           | V <sub>DD</sub> = 2.5 | 5V ± 0.2V |      |

|--------------------|-----------------------------------|-------------------------------------------------------------------------------------------|-----------------------|-----------|------|

| Parameter          | Description                       | Condition                                                                                 | Min.                  | Max.      | Unit |

| F <sub>IN</sub>    | Input Clock Frequency             | CLK, CLK                                                                                  |                       | 200       | MHz  |

| P <sub>W</sub>     | Pulse Duration                    | CLK, CLK HIGH or LOW                                                                      | 3.3                   |           | ns   |

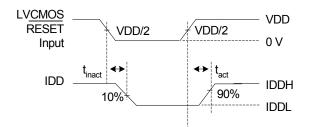

| T <sub>ACT</sub>   | Differential Inputs Active Time   | Data inputs must be LOW after RESET HIGH                                                  | 22                    |           | ns   |

| T <sub>INACT</sub> | Differential Inputs Inactive Time | Data and cloc <u>k inputs</u> must be held at valid levels (not floating) after RESET LOW | 22                    |           | ns   |

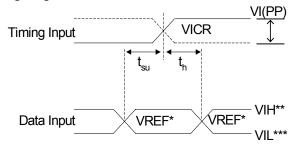

| T <sub>SET</sub>   | Set-up Time                       | Fast slew rate, (see notes 5 and 7), Data before CLK, CLK                                 | 0.75                  |           | ns   |

|                    |                                   | Slow slew rate, (see notes 6 and 7), Data before CLK, CLK                                 | 0.9                   |           | ns   |

| T <sub>HOLD</sub>  | Hold Time                         | Fast slew rate, (see notes 5 and 7), Data after CLK, CLK                                  | 0.75                  |           | ns   |

|                    |                                   | Slow slew rate (see notes 6 and 7), Data after CLK, CLK                                   | 0.9                   |           | ns   |

| I <sub>Vpp</sub>   | Input Voltage, Pk–Pk              |                                                                                           | 360                   |           | mV   |

Notes:

For data signal input slew rate > 1 V/ns.

For data signal input slew rate > 0.5 V/ns and < 1 V/ns.</li>

CLK, CLK signals input slew rates are > 1 V/ns.

# Table 3. AC Output Electrical Specifications (V<sub>DD</sub> = 2.5V VDC $\pm 5\%$ , Temperature = $0^{\circ}C$ to $+85^{\circ}C$ )

|                  |                                     |           | V <sub>DD</sub> = 2.5 | 5V ± 0.2V |      |

|------------------|-------------------------------------|-----------|-----------------------|-----------|------|

| Parameter        | Description                         | Condition | Min.                  | Max.      | Unit |

| F <sub>MAX</sub> |                                     |           |                       | 280       |      |

| T <sub>DEL</sub> | Propagation Delay from CLK/CLK to Q | Q         | 1.1                   | 2.8       | ns   |

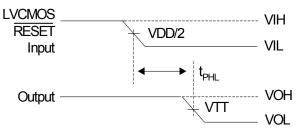

| T <sub>PHL</sub> | RESET                               | Q         |                       | 4.3       | ns   |

| T <sub>R</sub>   | Rise Time                           | Any Q     | 0.85                  | 4         | V/ns |

| Τ <sub>F</sub>   | Fall time                           | Any Q     | 1.0                   | 4         | V/ns |

# **Output Buffer Characteristics**

## Table 4. Output Buffer Voltage vs. Current (V/I) Characteristics

|             | Pull-      | Down       | Pull-Up    |            |  |

|-------------|------------|------------|------------|------------|--|

| Voltage (V) | Min I (mA) | Max I (mA) | Min I (mA) | Max I (mA) |  |

| 0           | 0          | 0          | 0          | 0          |  |

| 0.1         | 6          | 13         | -5         | –15        |  |

| 0.2         | 10         | 25         | -10        | -27        |  |

| 0.3         | 15         | 38         | –15        | -38        |  |

| 0.4         | 19         | 49         | –19        | -49        |  |

| 0.5         | 23         | 60         | -23        | -60        |  |

| 0.6         | 27         | 71         | -28        | -72        |  |

| 0.7         | 30         | 81         | -31        | -83        |  |

| 0.8         | 34         | 91         | -35        | -96        |  |

| 0.9         | 36         | 100        | -38        | -104       |  |

| 1.0         | 38         | 108        | -40        | –112       |  |

| 1.1         | 40         | 115        | -44        | -120       |  |

| 1.2         | 42         | 123        | -46        | -125       |  |

| 1.3         | 43         | 130        | -48        | -130       |  |

| 1.4         | 44         | 137        | -50        | -134       |  |

| 1.5         | 44         | 144        | -51        | -137       |  |

| 1.6         | 45         | 150        | -52        | -140       |  |

| 1.7         | 45         | 158        | -52        | -143       |  |

| 1.8         | 45         | 165        | -52        | -146       |  |

| 1.9         | 45         | 172        | -53        | -149       |  |

| 2.0         | 45         | 179        | -53        | –152       |  |

| 2.1         | 46         | 185        | -53        | -154       |  |

| 2.2         | 46         | 191        | -54        | -156       |  |

| 2.3         | 46         | 196        | -54        | –157       |  |

| 2.4         | 46         | 201        | -54        | -159       |  |

| 2.5         | 46         | 206        | -54        | -160       |  |

| 2.6         | 46         | 211        | -55        | –161       |  |

| 2.7         | 46         | 216        | -55        | -162       |  |

### **Slew Rate**

The following table describes output-buffer slew-rate characteristics that are sufficient to meet the requirements of registered DDR DIMM performance and timings. These characteristics are not necessarily production tested but can be guaranteed by design or characterization. Compliance with these rates is not mandatory if it can be adequately demonstrated that alternate characteristics meet the requirements of the registered DDR DIMM application. This information does not necessarily have to appear in the device data sheet.

Obtain rise and fall time measurements by using the same procedure for obtaining "Ramp" data according to the current WIA IBIS specification. In particular it is very important to note that the following slew rates are specified at the output of the die, without package parasitics in the power, ground or output paths. The measurement points are at 20% and 80%. The slew-rate test load shall be a 50-ohm resistor to GND for Rise and a 50-ohm resistor to V<sub>DDQ</sub> for fall. The dV/dt ratio is reduced to V/ns.

| Table 5. | Output I | Buffer | Slew-Rate | Characteristics |

|----------|----------|--------|-----------|-----------------|

|----------|----------|--------|-----------|-----------------|

| dV/dt | Min.      | Max.   |

|-------|-----------|--------|

| Rise  | 0.85 V/ns | 4 V/ns |

| Fall  | 1.00 V/ns | 4 V/ns |

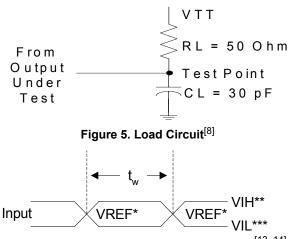

#### Test Configurations<sup>[9, 10]</sup>

$V_{DD} = 2.5V \pm 0.2V$

#### **Timing Diagrams**

# CY2SSTV16857

Figure 2. Voltage Waveforms Enable and Disable Times Low- and High-level Enabling<sup>[11]</sup>

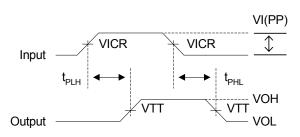

Figure 4. Voltage Waveforms Propagation Delay Times<sup>[11</sup>

Figure 6. Voltage Waveforms Pulse Duration<sup>[13, 14]</sup>

- 8. CL includes probe and jig capacitance.

- IDD tested with clock and data inputs held at VDD or VSS, and IO = 0 mA.

- 10. All input pulses are supplied by generators having the following characteristics: PRR < 10 MHz, ZO = 50 ohm input slew rate = 1 V/ns ±20% (unless otherwise specified).

- 11. the outputs are measured one at a time with one transition per measurement.

- 12.\*VTT = VREF = VDDQ/2.

Notes:

- 13. \*\*VIH = VREF + 350 mV (AC voltage levels).

- 14. \*\*\*VIL = VREF 350 mV (AC voltage levels).

## Ordering Information

| Part Number      | Package Type                 | Product Flow             |

|------------------|------------------------------|--------------------------|

| CY2SSTV16857ZC   | 48-pin TSSOP                 | Commercial, 0° to 70°C   |

| CY2SSTV16857ZCT  | 48-pin TSSOP – Tape and Reel | Commercial, 0° to 70°C   |

| CY2SSTV16857ZI   | 48-pin TSSOP                 | Industrial, –40° to 85°C |

| CY2SSTV16857ZIT  | 48-pin TSSOP – Tape and Reel | Industrial, –40° to 85°C |

| Lead-Free        |                              |                          |

| CY2SSTV16857ZXC  | 48-pin TSSOP                 | Commercial, 0° to 70°C   |

| CY2SSTV16857ZXCT | 48-pin TSSOP – Tape and Reel | Commercial, 0° to 70°C   |

| CY2SSTV16857ZXI  | 48-pin TSSOP                 | Industrial, –40° to 85°C |

| CY2SSTV16857ZXIT | 48-pin TSSOP – Tape and Reel | Industrial, –40° to 85°C |

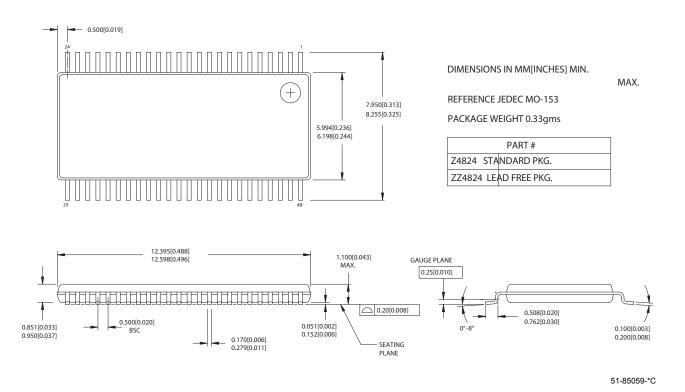

## Package Diagram

#### 48-lead (240-mil) TSSOP II Z4824

All product and company names mentioned in this document may be the trademarks of their respective holders.

© Cypress Semiconductor Corporation, 2005. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not without a charge to the use of medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

# **Document History Page**

| Rev.          | ECN No. | Issue<br>Date | Orig. of<br>Change | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|---------|---------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **            | 116562  | 08/21/02      | HWT                | New Data Sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *A            | 122930  | 12/18/02      | RBI                | Add power-up requirements to maximum ratings information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *B<br>t4U.com | 125621  | 05/20/03      | RGL                | Changed the Supply voltage ( $V_{DD}$ ) and Output supply voltage ( $V_{DDQ}$ ) values from 2.3/2.5/2.7 to 2.5/2.6/2.7Volts in the DC Electrical Specs. table<br>Changed the Reference voltage ( $V_{REF}$ ) values from 1.15/1.25/1.35 to 1.25/1.3/1.35V in the DC Electrical Specs. table<br>Moved the FMAX value from Min to Max in the AC Output Electrical Spec. table<br>Changed the T <sub>R</sub> /T <sub>F</sub> max values from 15.9 to 4V/ns<br>Added Industrial Temp. range in the ordering information<br>Added "PC2700-/PC3200-Compliant" to the title |

| *C            | 130366  | 11/03/03      | IJA                | Removed last Features bullet and second-to-last TVSOP package availability Kept only 48-pin TSSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| *D            | 308314  | See ECN       | RGL                | Added Lead Free Devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |