# CY7C0430BV CY7C0430CV

# 10 Gb/s 3.3V QuadPort™ DSE Family

# Features

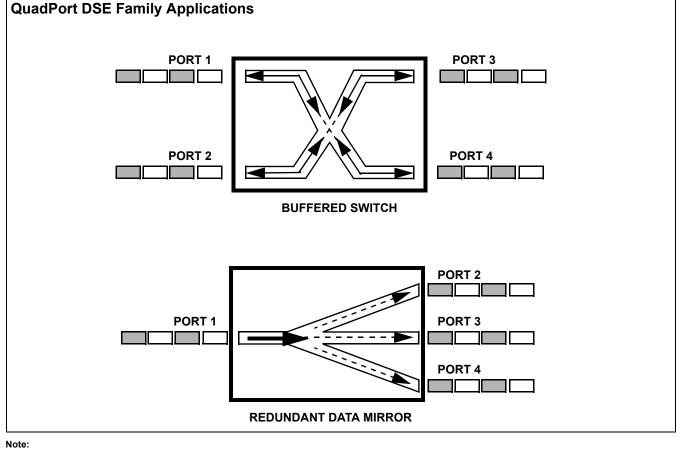

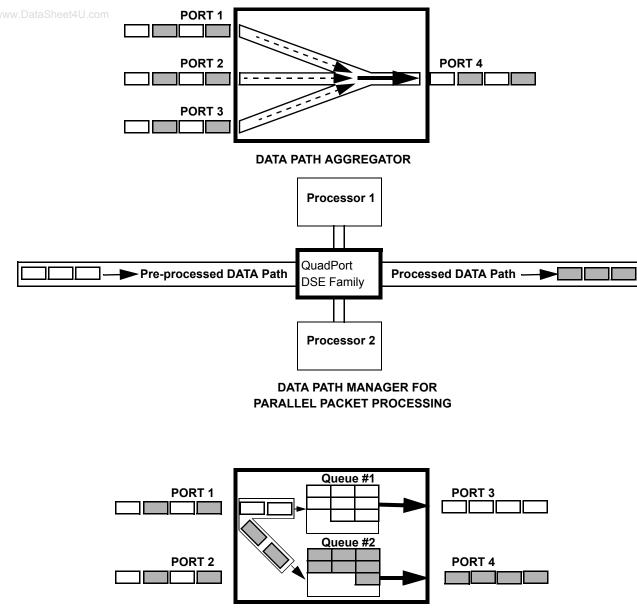

- QuadPort<sup>™</sup> datapath switching element (DSE) family allows four independent ports of access for data path management and switching

- · High-bandwidth data throughput up to 10 Gb/s

- 133-MHz<sup>[1]</sup> port speed x 18-bit-wide interface × 4 ports

- · High-speed clock to data access 4.2 ns (max.)

- Synchronous pipelined device

- 1-Mb (64K × 18) switch array

- 0.25-micron CMOS for optimum speed/power

- IEEE 1149.1 JTAG boundary scan

- · Width and depth expansion capabilities

- BIST (Built-In Self-Test) controller

- Dual Chip Enables on all ports for easy depth expansion

- Separate upper-byte and lower-byte controls on all ports

- Simple array partitioning

- Internal mask register controls counter wrap-around

- Counter-Interrupt flags to indicate wrap-around

- Counter and mask registers readback on address

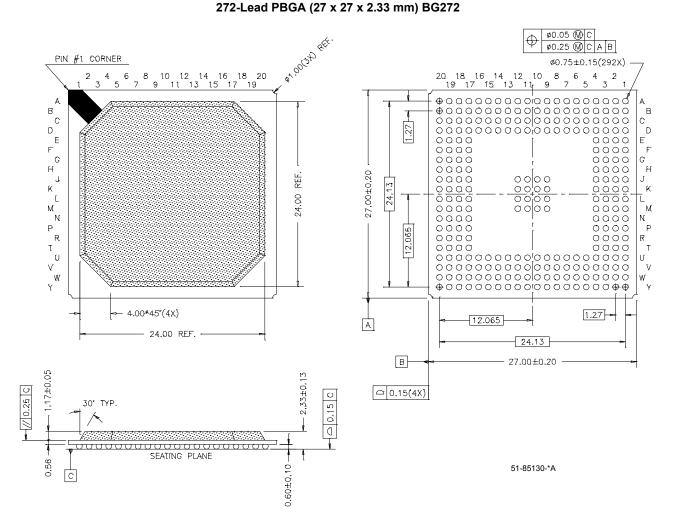

- 272-ball BGA package (27-mm × 27-mm × 1.27-mm ball pitch)

- Commercial and industrial temperature ranges

- 3.3V low operating power

- Active = 750 mA (maximum)

- Standby = 15 mA (maximum

1. f<sub>MAX2</sub> for commercial is 135 MHz and for industrial is 133 MHz.

DATA CLASSIFICATION ENGINE

## **Functional Description**

The Quadport Datapath Switching Element (DSE) family offers four ports that may be clocked at independent frequencies from one another. Each port can read or write up to 133 MHz<sup>[1]</sup>, giving the device up to 10 Gb/s of data throughput. The device is 1-Mb (64K × 18) in density. Simultaneous reads are allowed for accesses to the same address location; however, simultaneous reading and writing to the same address is not allowed. Any port can write to a certain location while other ports are reading that location simultaneously, if the timing spec for port to port delay (t<sub>CCS</sub>) is met. The result of writing to the same location by more than one port at the same time is undefined.

Data is registered for decreased cycle time. Clock to data valid  $t_{CD2}$  = 4.2 ns. Each port contains a burst counter on the input

address register. After externally loading the counter with the initial address the counter will self-increment the address internally (more details to follow). The internal write pulse width is independent of the duration of the R/W input signal. The internal write pulse is self-timed to allow the shortest possible cycle times.

A HIGH on  $\overline{CE}_0$  or LOW on  $CE_1$  for one clock cycle will power down the internal circuitry to reduce the static power consumption. One cycle is required with chip enables asserted to reactivate the outputs.

The CY7C0430BV and CY7C0430CV (64K × 18 device) supports burst contains for simple array partitioning. Counter enable inputs are provided to stall the operation of the address input and utilize the internal address generated by the internal counter for fast interleaved memory applications. A port's burst

counter is loaded with an external address when the port's Counter Load pin (CNTLD) is asserted LOW. When the port's Counter Increment pin (CNTINC) is asserted, the address counter will increment on each subsequent LOW-to- HIGH transition of that port's clock signal. This will read/write one word from/into each successive address location until CNTINC is deasserted. The counter can address the entire switch array and will loop back to the start. Counter Reset (CNTRST) is used to reset the burst counter. A counter-mask register is used to control the counter wrap. The counter and mask register operations are described in more details in the following sections.

The counter or mask register values can be read back on the bidirectional address lines by activating MKRD or CNTRD, respectively.

The new features included for the QuadPort DSE family include: readback of burst-counter internal address value on address lines, counter-mask registers to control the counter wrap-around, readback of mask register value on address lines, interrupt flags for message passing, BIST, JTAG for boundary scan, and asynchronous Master Reset.

Notes:

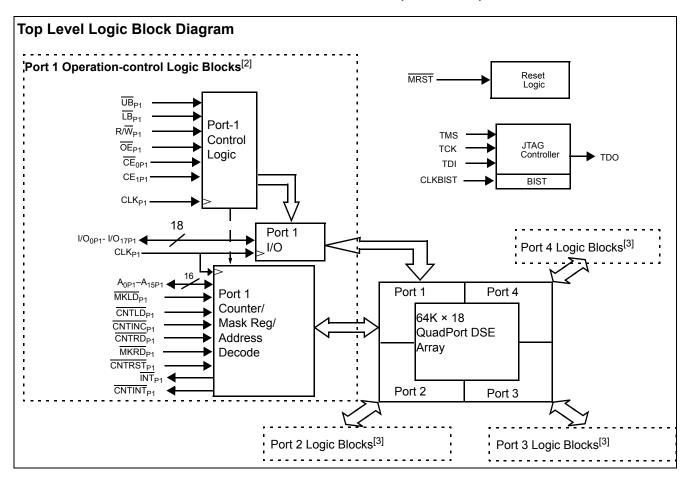

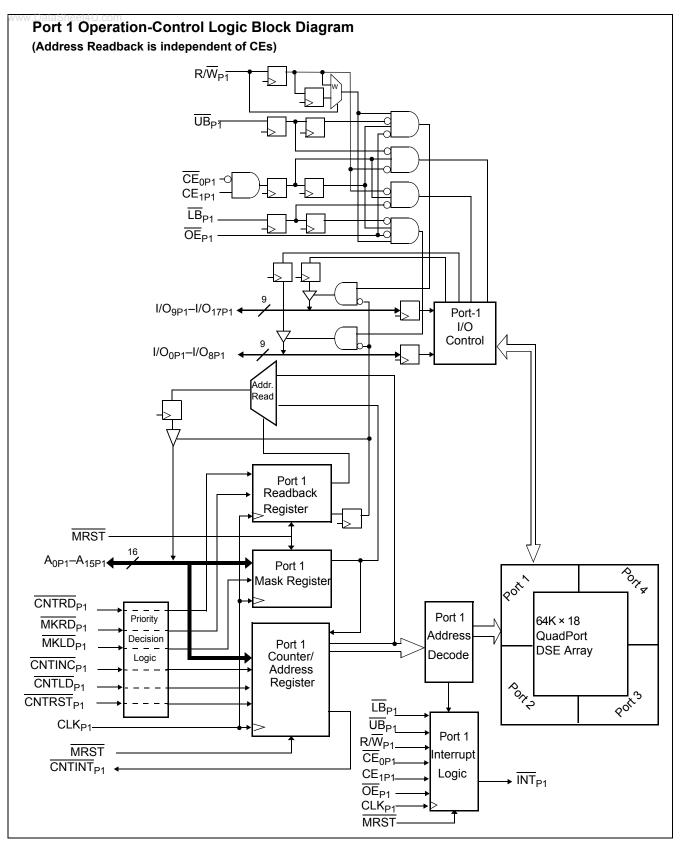

2. Port 1 Control Logic Block is detailed on page 4.

3. Port 2, Port 3, and Port 4 Logic Blocks are similar to Port 1 Logic Blocks.

# CY7C0430BV CY7C0430CV

**Pin Configuration**

272-ball Grid Array (BGA)

Top View

| _ | 1         | 2           | 3            | 4            | 5           | 6           | 7           | 8           | 9                  | 10                 | 11                 | 12                 | 13          | 14          | 15          | 16          | 17           | 18           | 19          | 20        |

|---|-----------|-------------|--------------|--------------|-------------|-------------|-------------|-------------|--------------------|--------------------|--------------------|--------------------|-------------|-------------|-------------|-------------|--------------|--------------|-------------|-----------|

| Α | LB<br>P1  | I/O17<br>P2 | I/O15<br>P2  | I/O13<br>P2  | I/O11<br>P2 | I/O9<br>P2  | I/O16<br>P1 | I/O14<br>P1 | I/O12<br>P1        | I/O10<br>P1        | I/O10<br>P4        | I/O12<br>P4        | I/O14<br>P4 | I/O16<br>P4 | I/O9<br>P3  | I/O11<br>P3 | I/O13<br>P3  | I/O15<br>P3  | I/O17<br>P3 | LB<br>P4  |

| в | VDD1      | UB<br>P1    | I/O16<br>P2  | I/O14<br>P2  | I/O12<br>P2 | I/O10<br>P2 | I/O17<br>P1 | I/O13<br>P1 | I/O11<br>P1        | TMS                | TDI                | I/O11<br>P4        | I/O13<br>P4 | I/O17<br>P4 | I/O10<br>P3 | I/O12<br>P3 | I/O14<br>P3  | I/O16<br>P3  | UB<br>P4    | VDD1      |

| с | A14<br>P1 | A15<br>P1   | CE1<br>P1    | CE0<br>P1    | R/W<br>P1   | I/O15<br>P1 | VSS2        | VSS2        | I/O9<br>P1         | тск                | TDO                | I/O9<br>P4         | VSS2        | VSS2        | I/O15<br>P4 | R/W<br>P4   | CE0<br>P4    | CE1<br>P4    | A15<br>P4   | A14<br>P4 |

| D | VSS1      | A12<br>P1   | A13<br>P1    | OE<br>P1     | VDD2        | VSS2        | VSS2        | VDD2        | VDD                | VSS                | VSS                | VDD                | VDD2        | VSS2        | VSS2        | VDD2        | OE<br>P4     | A13<br>P4    | A12<br>P4   | VSS1      |

| Е | A10<br>P1 | A11<br>P1   | MKRD<br>P1   | CNTRD<br>P1  |             |             |             |             | 1                  |                    |                    |                    |             |             |             |             | CNTRD<br>P4  | MKRD<br>P4   | A11<br>P4   | A10<br>P4 |

| F | A7<br>P1  | A8<br>P1    | A9<br>P1     | CNTINT<br>P1 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINT<br>P4 | A9<br>P4     | A8<br>P4    | A7<br>P4  |

| G | VSS1      | A5<br>P1    | A6<br>P1     | CNTINC<br>P1 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINC<br>P4 | A6<br>P4     | A5<br>P4    | VSS1      |

| н | A3<br>P1  | A4<br>P1    | MKLD<br>P1   | CNTLD<br>P1  |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTLD<br>P4  | MKLD<br>P4   | A4<br>P4    | A3<br>P4  |

| J | VDD1      | A1<br>P1    | A2<br>P1     | VDD          |             |             |             |             | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> |             |             |             |             | VDD          | A2<br>P4     | A1<br>P4    | VDD1      |

| κ | A0<br>P1  | INT<br>P1   | CNTRST<br>P1 | CLK<br>P1    |             |             |             |             | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> |             |             |             |             | CLK<br>P4    | CNTRST<br>P4 | INT<br>P4   | A0<br>P4  |

| L | A0<br>P2  | INT<br>P2   | CNTRST<br>P2 | VSS          |             |             |             |             | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> |             |             |             |             | VSS          | CNTRST<br>P3 | INT<br>P3   | A0<br>P3  |

| м | VDD1      | A1<br>P2    | A2<br>P2     | CLK<br>P2    |             |             |             |             | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> | GND <sup>[4]</sup> |             |             |             |             | CLK<br>P3    | A2<br>P3     | A1<br>P3    | VDD1      |

| N | A3<br>P2  | A4<br>P2    | MKLD<br>P2   | CNTLD<br>P2  |             |             |             |             |                    |                    |                    |                    | I           |             |             |             | CNTLD<br>P3  | MKLD<br>P3   | A4<br>P3    | A3<br>P3  |

| Ρ | VSS1      | A5<br>P2    | A6<br>P2     | CNTINC<br>P2 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINC<br>P3 | A6<br>P3     | A5<br>P3    | VSS1      |

| R | A7<br>P2  | A8<br>P2    | A9<br>P2     | CNTINT<br>P2 |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTINT<br>P3 | A9<br>P3     | A8<br>P3    | A7<br>P3  |

| т | A10<br>P2 | A11<br>P2   | MKRD<br>P2   | CNTRD<br>P2  |             |             |             |             |                    |                    |                    |                    |             |             |             |             | CNTRD<br>P3  | MKRD<br>P3   | A11<br>P3   | A10<br>P3 |

| U | VSS1      | A12<br>P2   | A13<br>P2    | OE<br>P2     | VDD2        | VSS2        | VSS2        | VDD2        | VDD                | VSS                | VSS                | VDD                | VDD2        | VSS2        | VSS2        | VDD2        | OE<br>P3     | A13<br>P3    | A12<br>P3   | VSS1      |

| v | A14<br>P2 | A15<br>P2   | CE1<br>P2    | CE0<br>P2    | R/W<br>P2   | I/O6<br>P2  | VSS2        | VSS2        | I/O0<br>P2         | NC                 | NC                 | I/O0<br>P3         | VSS2        | VSS2        | I/O6<br>P3  | R/W<br>P3   | CE0<br>P3    | CE1<br>P3    | A15<br>P3   | A14<br>P3 |

| w | VDD1      | UB<br>P2    | I/O7<br>P1   | I/O5<br>P1   | I/O3<br>P1  | I/O1<br>P1  | I/O8<br>P2  | I/O4<br>P2  | I/O2<br>P2         | MRST               | CLKBIST            | I/O2<br>P3         | I/O4<br>P3  | I/O8<br>P3  | I/O1<br>P4  | I/O3<br>P4  | I/O5<br>P4   | I/O7<br>P4   | UB<br>P3    | VDD1      |

| Y | LB<br>P2  | I/O8<br>P1  | I/O6<br>P1   | I/O4<br>P1   | I/O2<br>P1  | I/O0<br>P1  | 1/07<br>P2  | I/O5<br>P2  | I/O3<br>P2         | I/O1<br>P2         | I/O1<br>P3         | I/O3<br>P3         | I/O5<br>P3  | I/O7<br>P3  | I/O0<br>P4  | I/O2<br>P4  | I/O4<br>P4   | I/O6<br>P4   | I/O8<br>P4  | LB<br>P3  |

Note:

4. Central Leads are for thermal dissipation only. They are connected to device  $V_{SS}$ .

# Selection Guide

|                                                                 | CY7C0430CV<br>-133 | CY7C0430CV<br>-100 | Unit |

|-----------------------------------------------------------------|--------------------|--------------------|------|

| f <sub>MAX2</sub>                                               | 133 <sup>[1]</sup> | 100                | MHz  |

| Max Access Time (Clock to Data)                                 | 4.2                | 5.0                | ns   |

| Max Operating Current I <sub>CC</sub>                           | 750                | 600                | mA   |

| Max Standby Current for I <sub>SB1</sub> (All ports TTL Level)  | 200                | 150                | mA   |

| Max Standby Current for I <sub>SB3</sub> (All ports CMOS Level) | 15                 | 15                 | mA   |

# **Pin Definitions**

| Port 1                                  | Port 2                                  | Port 3                                  | Port 4                                  | Description                                                                                                                                                                                                                              |

|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0P1</sub> -A <sub>15P1</sub>     | A <sub>0P2</sub> -A <sub>15P2</sub>     | A <sub>0P3</sub> -A <sub>15P3</sub>     | A <sub>0P4</sub> -A <sub>15P4</sub>     | Address Input/Output.                                                                                                                                                                                                                    |

| I/O <sub>0P1</sub> -I/O <sub>17P1</sub> | I/O <sub>0P2</sub> -I/O <sub>17P2</sub> | I/O <sub>0P3</sub> -I/O <sub>17P3</sub> | I/O <sub>0P4</sub> –I/O <sub>17P4</sub> | Data Bus Input/Output.                                                                                                                                                                                                                   |

| CLK <sub>P1</sub>                       | CLK <sub>P2</sub>                       | CLK <sub>P3</sub>                       | CLK <sub>P4</sub>                       | <b>Clock Input</b> . This input can be free running or strobed. Maximum clock input rate is $f_{MAX}$ .                                                                                                                                  |

| LB <sub>P1</sub>                        | LB <sub>P2</sub>                        | LB <sub>P3</sub>                        | LB <sub>P4</sub>                        | <b>Lower Byte Select Input</b> . Asserting this signal LOW enables read and write operations to the lower byte. For read operations both the LB and OE signals must be asserted to drive output data on the lower byte of the data pins. |

| UB <sub>P1</sub>                        | UB <sub>P2</sub>                        | UB <sub>P3</sub>                        | UB <sub>P4</sub>                        | <b>Upper Byte Select Input</b> . Same function as $\overline{LB}$ , but to the upper byte.                                                                                                                                               |

| CE <sub>0P1</sub> ,CE <sub>1P1</sub>    | CE <sub>0P2</sub> ,CE <sub>1P2</sub>    | CE <sub>0P3</sub> ,CE <sub>1P3</sub>    | CE <sub>0P4</sub> ,CE <sub>1P4</sub>    | <b>Chip Enable Input</b> . To select any port, both $\overline{CE}_0$ AND $CE_1$ must be asserted to their active states ( $\overline{CE}_0 \leq V_{IL}$ and $CE_1 \geq V_{IH}$ ).                                                       |

| OE <sub>P1</sub>                        | OE <sub>P2</sub>                        | OE <sub>P3</sub>                        | OE <sub>P4</sub>                        | <b>Output Enable Input</b> . This signal must be asserted <u>LO</u> W to enable the I/O data lines during read operations. OE is asynchronous input.                                                                                     |

| R/W <sub>P1</sub>                       | R/W <sub>P2</sub>                       | R/W <sub>P3</sub>                       | R/W <sub>P4</sub>                       | <b>Read/Write Enable Input</b> . This signal is asserted LOW to write to the dual port memory array. For read operations, assert this pin HIGH.                                                                                          |

| MRST                                    |                                         |                                         |                                         | Master Reset Input. This is one signal for All Ports.<br>MRST is an asynchronous input. Asserting MRST LOW<br>performs all of the reset functions as described in the text.<br>A MRST operation is required at power-up.                 |

| CNTRST <sub>P1</sub>                    | CNTRST <sub>P2</sub>                    | CNTRST <sub>P3</sub>                    | CNTRST <sub>P4</sub>                    | <b>Counter Reset Input</b> . Asserting this signal LOW resets the burst address counter of its respective port to zero. CNTRST is second to MRST in priority with respect to counter and mask register operations.                       |

| MKLD <sub>P1</sub>                      | MKLD <sub>P2</sub>                      | MKLD <sub>P3</sub>                      | MKLD <sub>P4</sub>                      | <b>Mask Register Load Input</b> . Asserting this signal LOW loads the mask register with the <u>external</u> address available on the address lines. MKLD operation has higher priority over CNTLD operation.                            |

| CNTLD <sub>P1</sub>                     | CNTLD <sub>P2</sub>                     | CNTLD <sub>P3</sub>                     | CNTLD <sub>P4</sub>                     | <b>Counter Load Input</b> . Asserting this signal LOW loads the burst counter with the external address present on the address pins.                                                                                                     |

| CNTINC <sub>P1</sub>                    | CNTINC <sub>P2</sub>                    | CNTINC <sub>P3</sub>                    | CNTINC <sub>P4</sub>                    | <b>Counter Increment Input</b> . Asserting this signal LOW increments the burst address counter of its respective port on each rising edge of CLK.                                                                                       |

# Pin Definitions (continued)

| Port 1               | Port 2               | Port 3               | Port 4               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------|----------------------|----------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNTRD <sub>P1</sub>  | CNTRD <sub>P2</sub>  | CNTRD <sub>P3</sub>  | CNTRD <sub>P4</sub>  | <b>Counter Readback Input</b> . When asserted LOW, the internal address value of <u>the counter will be read back on</u> the <u>address lines</u> . During CNTRD operation, both CNTLD and CNTINC must be HIGH. Counter readback operation has higher priority over mask register readback operation. Counter readback operation is independent of port chip enables. If addr <u>ess</u> readback operation occurs with chip enables active ( $\overline{CE}_0 = LOW$ , $CE_1 = HIGH$ ), the data lines (I/Os) will be three-stated. The readback timing will be valid after one no-operation cycle plus t <sub>CD2</sub> from the rising edge of the next cycle. |

| MKRD <sub>P1</sub>   | MKRD <sub>P2</sub>   | MKRD <sub>P3</sub>   | MKRD <sub>P4</sub>   | Mask Register Readback Input. When asserted LOW,<br>the value of the mask register will be readback on address<br>lines. During mask register readback operation, all<br>counter and MKLD inputs must be HIGH (see Counter<br>and Mask Register Operations truth table). Mask register<br>readback operation is independent of port chip enables.<br>If address readback operation occurs with chip enables<br>active ( $\overline{CE}_0$ = LOW, $\overline{CE}_1$ = HIGH), the data lines (I/Os) will<br>be three-stated. The readback will be valid after one<br>no-operation cycle plus t <sub>CD2</sub> from the rising edge of the<br>next cycle.            |

| CNTINT <sub>P1</sub> | CNTINT <sub>P2</sub> | CNTINT <sub>P3</sub> | CNTINT <sub>P4</sub> | <b>Counter Interrupt Flag Output</b> . Flag is asserted LOW for one clock cycle when the counter wraps around to location zero.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| INTP1                | INTP2                | INTP3                | INTP4                | Interrupt Flag Output. Interrupt permits communications<br>between all four ports. The upper four memory locations<br><u>can</u> be used for message passing. Example of operation:<br>$INT_{P4}$ is asserted LOW when another port writes to the<br>mailbox location of Port 4. Flag is cleared when Port 4<br>reads the contents of its mailbox. The same operation is<br>applicable to ports 1, 2, and 3.                                                                                                                                                                                                                                                      |

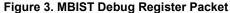

| TMS                  |                      |                      |                      | JTAG Test Mode Select Input. It controls the advance of JTAG TAP state machine. State machine transitions occur on the rising edge of TCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ТСК                  |                      |                      |                      | <b>JTAG Test Clock Input</b> . This can be CLK of any port or an external clock connected to the JTAG TAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TDI                  |                      |                      |                      | <b>JTAG Test Data Input</b> . This is the only data input. TDI inputs will shift data serially in to the selected register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TDO                  |                      |                      |                      | <b>JTAG Test Data Output</b> . This is the only data output.<br>TDO transitions occur on the falling edge of TCK. TDO<br>normally three-stated except when captured data is<br>shifted out of the JTAG TAP.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CLKBIST              |                      |                      |                      | BIST Clock Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND                  |                      |                      |                      | Thermal Ground for Heat Dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>      |                      |                      |                      | Ground Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>DD</sub>      |                      |                      |                      | Power Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| V <sub>SS1</sub>     |                      |                      |                      | Address Lines Ground Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V <sub>DD1</sub>     |                      |                      |                      | Address Lines Power Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V <sub>SS2</sub>     |                      |                      |                      | Data Lines Ground Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>DD2</sub>     |                      |                      |                      | Data Lines Power Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# **Maximum Ratings**

(Above which the useful life may be impaired. For user guide-lines, not tested.)

| Storage Temperature65°C to + 150°C                                   |

|----------------------------------------------------------------------|

| Ambient Temperature with<br>Power Applied55°C to + 125°C             |

| Supply Voltage to Ground Potential –0.5V to + 4.6V                   |

| DC Voltage Applied to Outputs in High-Z State0.5V to $V_{CC}$ + 0.5V |

| DC Input Voltage                                                     |

| Output Current into Outputs (LOW) | 20 mA    |

|-----------------------------------|----------|

| Static Discharge Voltage          | > 2200V  |

| Latch-up Current                  | > 200 mA |

**Operating Range**

| Range      | Ambient Temperature | V <sub>DD</sub>  |

|------------|---------------------|------------------|

| Commercial | 0°C to +70°C        | $3.3V\pm150~mV$  |

| Industrial | –40°C to +85°C      | $3.3V\pm150\ mV$ |

# Electrical Characteristics Over the Operating Range

|                  |                                                                                                                                                                                                                                                                       |      | Q    | uadport l | DSE Fam | SE Family |      |      |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-----------|---------|-----------|------|------|--|--|--|

|                  |                                                                                                                                                                                                                                                                       |      | -133 |           |         | -100      |      |      |  |  |  |

| Parameter        | Description                                                                                                                                                                                                                                                           | Min. | Тур. | Max.      | Min.    | Тур.      | Max. | Unit |  |  |  |

| V <sub>OH</sub>  | Output HIGH Voltage<br>(V <sub>CC</sub> = Min., I <sub>OH</sub> = -4.0 mA)                                                                                                                                                                                            | 2.4  |      |           | 2.4     |           |      | V    |  |  |  |

| V <sub>OL</sub>  | Output LOW Voltage<br>(V <sub>CC</sub> = Min., I <sub>OH</sub> = +4.0 mA)                                                                                                                                                                                             |      |      | 0.4       |         |           | 0.4  | V    |  |  |  |

| V <sub>IH</sub>  | Input HIGH Voltage                                                                                                                                                                                                                                                    | 2.0  |      |           | 2.0     |           |      | V    |  |  |  |

| V <sub>IL</sub>  | Input LOW Voltage                                                                                                                                                                                                                                                     |      |      | 0.8       |         |           | 0.8  | V    |  |  |  |

| I <sub>OZ</sub>  | Output Leakage Current                                                                                                                                                                                                                                                | -10  |      | 10        | -10     |           | 10   | μA   |  |  |  |

| I <sub>CC</sub>  | Operating Current ( $V_{CC}$ = Max., $I_{OUT}$ = 0 mA)<br>Outputs Disabled, CE = $V_{IL}$ , f = f <sub>max</sub>                                                                                                                                                      |      | 350  | 700       |         | 300       | 550  | mA   |  |  |  |

| I <sub>SB1</sub> | $\begin{array}{l} Standby Current (four ports toggling at TTL \\ \underline{Le}vels,0 \mbox{ active}) \\ \overline{CE}_{1-4} \geq V_{IH}, \mbox{ f = f}_{MAX} \end{array}$                                                                                            |      | 80   | 200       |         | 60        | 150  | mA   |  |  |  |

| I <sub>SB2</sub> | $\begin{array}{l} \text{Standby Current} \ \underline{(four \ ports} \ \underline{togg} \\ \text{Levels, 1 active}) \ \overline{CE}_1 \   \ \overline{CE}_2 \   \ \overline{CE}_3 \   \ \overline{CE}_4 \leq V_{\text{IL}}, \\ \text{f} = f_{\text{MAX}} \end{array}$ |      | 150  | 300       |         | 125       | 250  | mA   |  |  |  |

| I <sub>SB3</sub> | Standb <u>v C</u> urrent (four ports CMOS Level, 0 active) $CE_{1-4} \ge V_{IH}$ , f = 0                                                                                                                                                                              |      | 1.5  | 15        |         | 1.5       | 15   | mA   |  |  |  |

| I <sub>SB4</sub> | $\begin{array}{l} Standby \ Current \ (fo\underline{ur} \ \underline{p}ort\underline{s} \ \underline{CMOS} \ Le\underline{vel}, \ 1\\ active \ and \ toggling) \ CE_1 \   \ CE_2 \   \ CE_3 \   \ CE_4 \leq \\ V_{IL}, \ f = f_{MAX} \end{array}$                     |      | 110  | 290       |         | 85        | 240  | mA   |  |  |  |

JTAG TAP Electrical Characteristics Over the Operating Range

| Parameter        | Description           | Test Conditions           | Min. | Max. | Unit |

|------------------|-----------------------|---------------------------|------|------|------|

| V <sub>OH1</sub> | Output HIGH Voltage   | I <sub>OH</sub> = -4.0 mA | 2.4  |      | V    |

| V <sub>OL1</sub> | Output LOW Voltage    | I <sub>OL</sub> = 4.0 mA  |      | 0.4  | V    |

| V <sub>IH</sub>  | Input HIGH Voltage    |                           | 2.0  |      | V    |

| V <sub>IL</sub>  | Input LOW Voltage     |                           |      | 0.8  | V    |

| I <sub>X</sub>   | Input Leakage Current | $GND \le V_I \le V_{DD}$  | -100 | 100  | μA   |

# Capacitance

| Parameter                   | Description        | Test Conditions                   | Max. | Unit |

|-----------------------------|--------------------|-----------------------------------|------|------|

| C <sub>IN</sub> (All Pins)  | Input Capacitance  | T <sub>A</sub> = 25°C, f = 1 MHz, | 10   | pF   |

| C <sub>OUT</sub> (All Pins) | Output Capacitance | $V_{CC} = 3.3V$                   | 10   | pF   |

| C <sub>IN</sub> (CLK Pins)  | Input Capacitance  |                                   | 15   | pF   |

| C <sub>OUT</sub> (CLK Pins) | Output Capacitance |                                   | 15   | pF   |

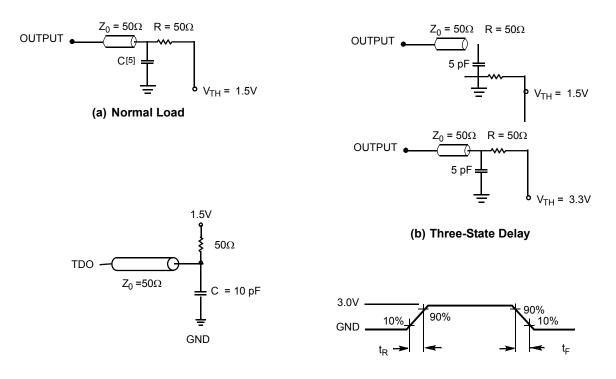

# AC Test Load

(c) TAP Load

All Input Pulses

Note:

5. Test conditions: C = 10 pF.

# Switching Characteristics Over the Industrial Operating Range [6]

|                                  |                                         | CY70 | C0430BV a | nd CY7C04 | 30CV |      |

|----------------------------------|-----------------------------------------|------|-----------|-----------|------|------|

|                                  |                                         | -1   | 33        | -1        | 00   | -    |

| Parameter                        | Description                             | Min. | Max.      | Min.      | Max. | Unit |

| f <sub>MAX2</sub> [7]            | Maximum Frequency                       |      | 133       |           | 100  | MHz  |

| t <sub>CYC2</sub> <sup>[7]</sup> | Clock Cycle Time                        | 7.5  |           | 10        |      | ns   |

| t <sub>CH2</sub>                 | Clock HIGH Time                         | 3    |           | 4         |      | ns   |

| t <sub>CL2</sub>                 | Clock LOW Time                          | 3    |           | 4         |      | ns   |

| t <sub>R</sub>                   | Clock Rise Time                         |      | 2         |           | 3    | ns   |

| t <sub>F</sub>                   | Clock Fall Time                         |      | 2         |           | 3    | ns   |

| t <sub>SA</sub>                  | Address Set-up Time                     | 2.3  |           | 3         |      | ns   |

| t <sub>HA</sub>                  | Address Hold Time                       | 0.7  |           | 0.7       |      | ns   |

| t <sub>SC</sub>                  | Chip Enable Set-up Time                 | 2.3  |           | 3         |      | ns   |

| t <sub>HC</sub>                  | Chip Enable Hold Time                   | 0.7  |           | 0.7       |      | ns   |

| t <sub>SW</sub>                  | R/W Set-up Time                         | 2.3  |           | 3         |      | ns   |

| t <sub>HW</sub>                  | R/W Hold Time                           | 0.7  |           | 0.7       |      | ns   |

| t <sub>SD</sub>                  | Input Data Set-up Time                  | 2.3  |           | 3         |      | ns   |

| t <sub>HD</sub>                  | Input Data Hold Time                    | 0.7  |           | 0.7       |      | ns   |

| t <sub>SB</sub>                  | Byte Set-up Time                        | 2.3  |           | 3         |      | ns   |

| t <sub>HB</sub>                  | Byte Hold Time                          | 0.7  |           | 0.7       |      | ns   |

| t <sub>SCLD</sub>                | CNTLD Set-up Time                       | 2.3  |           | 3         |      | ns   |

| t <sub>HCLD</sub>                | CNTLD Hold Time                         | 0.7  |           | 0.7       |      | ns   |

| t <sub>SCINC</sub>               | CNTINC Set-up Time                      | 2.3  |           | 3         |      | ns   |

| t <sub>HCINC</sub>               | CNTINC Hold Time                        | 0.7  |           | 0.7       |      | ns   |

| t <sub>SCRST</sub>               | CNTRST Set-up Time                      | 2.3  |           | 3         |      | ns   |

| t <sub>HCRST</sub>               | CNTRST Hold Time                        | 0.7  |           | 0.7       |      | ns   |

| t <sub>SCRD</sub>                | CNTRD Set-up Time                       | 2.3  |           | 3         |      | ns   |

| t <sub>HCRD</sub>                | CNTRD Hold Time                         | 0.7  |           | 0.7       |      | ns   |

| t <sub>SMLD</sub>                | MKLD Set-up Time                        | 2.3  |           | 3         |      | ns   |

| t <sub>HMLD</sub>                | MKLD Hold Time                          | 0.7  |           | 0.7       |      | ns   |

| t <sub>SMRD</sub>                | MKRD Set-up Time                        | 2.3  |           | 3         |      | ns   |

| t <sub>HMRD</sub>                | MKRD Hold Time                          | 0.7  |           | 0.7       |      | ns   |

| t <sub>OE</sub>                  | Output Enable to Data Valid             |      | 6.5       |           | 8    | ns   |

| t <sub>OLZ</sub> <sup>[8]</sup>  | OE to Low-Z                             | 1    |           | 1         |      | ns   |

| t <sub>OHZ</sub> <sup>[8]</sup>  | OE to High-Z                            | 1    | 6         | 1         | 7    | ns   |

| t <sub>CD2</sub>                 | Clock to Data Valid                     |      | 4.2       |           | 5    | ns   |

| t <sub>CA2</sub>                 | Clock to Counter Address Readback Valid |      | 4.7       |           | 5    | ns   |

| t <sub>CM2</sub>                 | Clock to Mask Register Readback Valid   |      | 4.7       |           | 5    | ns   |

| t <sub>DC</sub>                  | Data Output Hold After Clock HIGH       | 1    |           | 1         |      | ns   |

| t <sub>СКНZ<sup>[9]</sup></sub>  | Clock HIGH to Output High-Z             | 1    | 4.8       | 1         | 6.8  | ns   |

Notes:

6. If data is simultaneously written and read to the same address location and t<sub>CCS</sub> is violated, the data read from the address, as well as the subsequent data remaining in the address is undefined.

7. f<sub>MAX2</sub> for commercial is 135 MHz. t<sub>CYC2</sub> Min. for commercial is 7.4 ns.

8. This parameter is guaranteed by design, but it is not production tested.

9. Valid for both address and data outputs.

# Switching Characteristics Over the Industrial Operating Range (continued)<sup>[6]</sup>

|                                  |                                                                                                        | CY70 | C0430BV a | nd CY7C04 | 430CV |      |

|----------------------------------|--------------------------------------------------------------------------------------------------------|------|-----------|-----------|-------|------|

|                                  |                                                                                                        | -1   | 133       | -100      |       |      |

| Parameter                        | Description                                                                                            | Min. | Max.      | Min.      | Max.  | Unit |

| t <sub>CKLZ</sub> <sup>[9]</sup> | Clock HIGH to Output Low-Z                                                                             | 1    |           | 1         |       | ns   |

| t <sub>SINT</sub>                | Clock to INT Set Time                                                                                  | 1    | 7.5       | 1         | 10    | ns   |

| t <sub>RINT</sub>                | Clock to INT Reset Time                                                                                | 1    | 7.5       | 1         | 10    | ns   |

| t <sub>SCINT</sub>               | Clock to CNTINT Set Time                                                                               | 1    | 7.5       | 1         | 10    | ns   |

| t <sub>RCINT</sub>               | Clock to CNTINT Reset Time                                                                             | 1    | 7.5       | 1         | 10    | ns   |

| Master Res                       | et Timing                                                                                              |      |           |           |       |      |

| t <sub>RS</sub>                  | Master Reset Pulse Width                                                                               | 7.5  |           | 10        |       | ns   |

| t <sub>RSR</sub>                 | Master Reset Recovery Time                                                                             | 7.5  |           | 10        |       | ns   |

| t <sub>ROF</sub>                 | Master Reset to Output Flags Reset Time                                                                |      | 6.5       |           | 8     | ns   |

| Port to Port                     | Delays                                                                                                 |      |           |           |       |      |

| t <sub>CCS</sub> <sup>[6]</sup>  | Clock to Clock Set-up Time (time required after a write before you can read the same address location) | 6.5  |           | 9         |       | ns   |

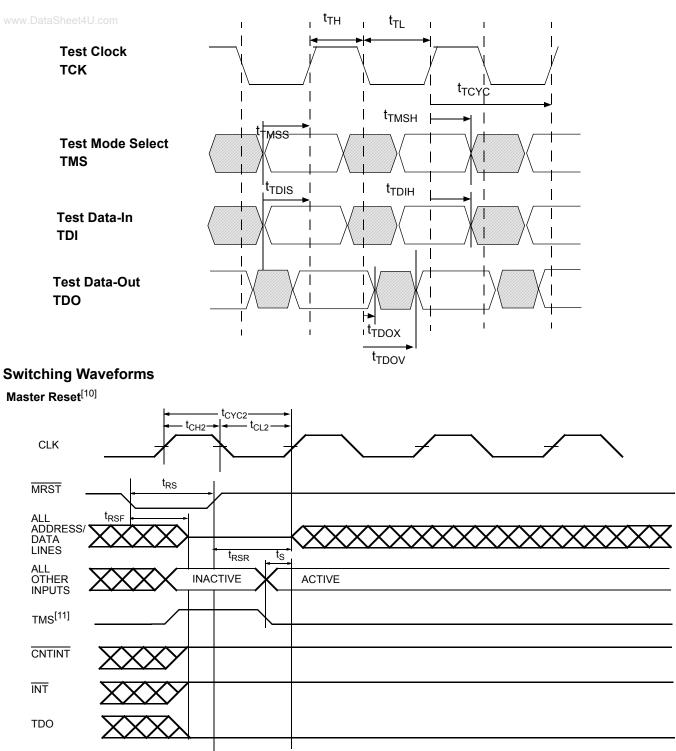

# JTAG Timing and Switching Waveforms

|                   |                                       | Quadport |      |      |

|-------------------|---------------------------------------|----------|------|------|

|                   |                                       | -133     |      |      |

| Parameter         | Description                           | Min.     | Max. | Unit |

| f <sub>JTAG</sub> | Maximum JTAG TAP Controller Frequency |          | 10   | MHz  |

| t <sub>TCYC</sub> | TCK Clock Cycle Time                  | 100      |      | ns   |

| t <sub>TH</sub>   | TCK Clock High Time                   | 40       |      | ns   |

| t <sub>TL</sub>   | TCK Clock Low Time                    | 40       |      | ns   |

| t <sub>TMSS</sub> | TMS Set-up to TCK Clock Rise          | 20       |      | ns   |

| t <sub>TMSH</sub> | TMS Hold After TCK Clock Rise         | 20       |      | ns   |

| t <sub>TDIS</sub> | TDI Set-up to TCK Clock Rise          | 20       |      | ns   |

| t <sub>TDIH</sub> | TDI Hold after TCK Clock Rise         | 20       |      | ns   |

| t <sub>TDOV</sub> | TCK Clock Low to TDO Valid            |          | 20   | ns   |

| t <sub>TDOX</sub> | TCK Clock Low to TDO Invalid          | 0        |      | ns   |

| f <sub>BIST</sub> | Maximum CLKBIST Frequency             |          | 50   | MHz  |

| t <sub>BH</sub>   | CLKBIST High Time                     | 6        |      | ns   |

| t <sub>BL</sub>   | CLKBIST Low Time                      | 6        |      | ns   |

#### Notes:

10. t<sub>S</sub> is the set-up time required for all input control signals.

11. To Reset the test port without resetting the device, TMS must be held low for five clock cycles.

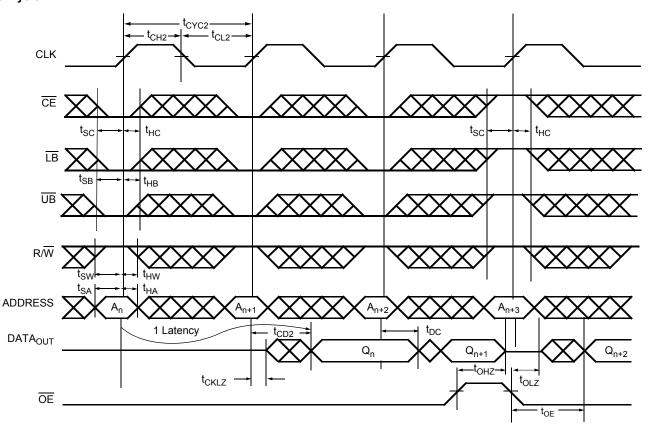

Read Cycle<sup>[12, 13, 14, 15, 16]</sup>

Notes:

12. <u>OE</u> is asynchronously controlled; all other inputs (excluding <u>MRST</u>) are synchronous to the rising clock edge.

13. <u>CNTLD</u> = V<sub>IL</sub>, <u>MKLD</u> = V<sub>IH</sub>, <u>CNTINC</u> = x, and <u>MRST</u> = <u>CNTRST</u> = V<sub>IH</sub>.

14. The output is disabled (high-impedance state) by <u>CE</u> = V<sub>IH</sub> following the next rising edge of the clock.

15. Addresses do not have to be accessed sequentially. Note 13 indicates that address is constantly loaded on the rising edge of the CLK. Numbers are for reference <u>only</u>.

16. <u>CE</u> is internal signal. <u>CE</u> = VIL if <u>CE</u><sub>0</sub> = V<sub>IL</sub> and CE<sub>1</sub> = V<sub>IH</sub>.

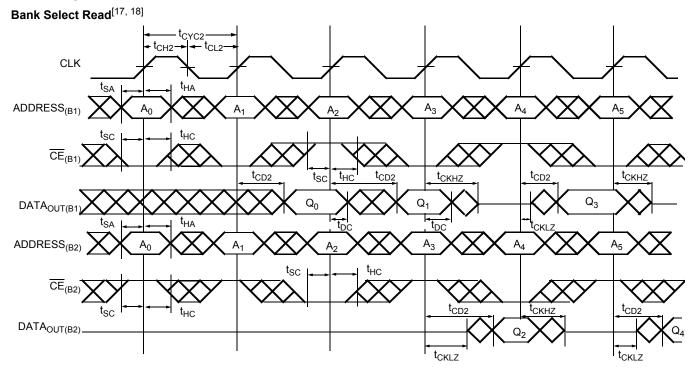

#### Notes:

- Notes: 17. In this depth expansion example, B1 represents Bank #1 and B2 is Bank #2; Each bank consists of one QuadPort DSE device from this data sheet. <u>ADDRESS<sub>(B1)</sub> = ADDRESS<sub>(B2)</sub></u> 18. LB = UB = OE = CNTLD = V<sub>IL</sub>; <u>MRST</u> = CNTRST = MKLD = V<sub>IH</sub>. 19. <u>Output state (HIGH, LOW, or high-impedance) is det</u>ermined by the previous cycle control signals. 20. LB = UB = CNTLD = V<sub>IL</sub>; <u>MRST</u> = CNTRST = MKLD = V<sub>IH</sub>. 21. Addresses do not have to be accessed sequentially since CNTLD = V<sub>IL</sub> constantly loads the address on the rising edge of the CLK; numbers are for reference only. 22. During "No Operation," data in memory at the selected address may be corrupted and should be rewritten to ensure data integrity.

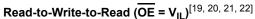

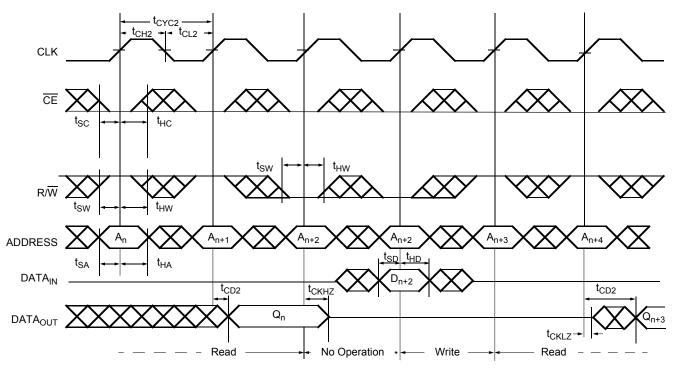

Read-to-Write-to-Read (OE Controlled)<sup>[19, 20, 21, 22]</sup>

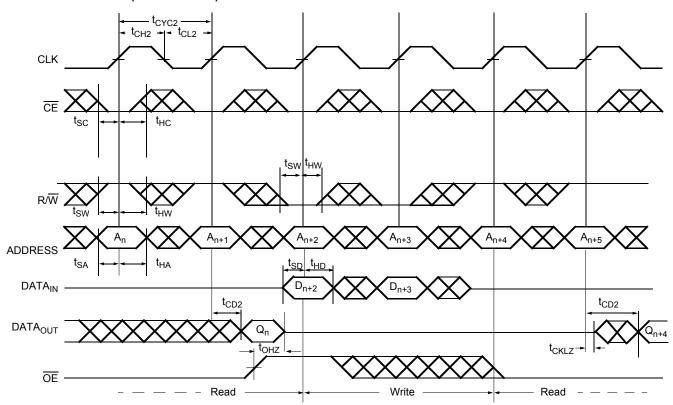

Read with Address Counter Advance<sup>[23, 24]</sup>

Notes: 23.  $\overline{CE}_0 = \overline{OE} = \overline{LB} = \overline{UB} = V_{|L}$ ;  $CE_1 = R/\overline{W} = \overline{CNTRST} = \overline{MRST} = \overline{MKLD} = \overline{MKRD} = \overline{CNTRD} = V_{|H}$ . 24. The "Internal Address" is equal to the "External Address" when  $\overline{CNTLD} = V_{|L}$ .

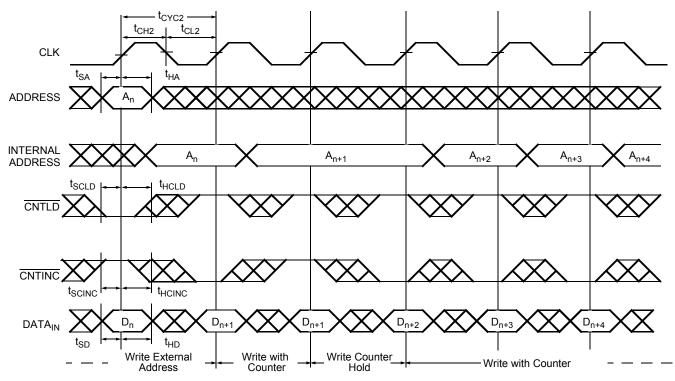

Write with Address Counter Advance <sup>[24, 25]</sup>

Note: 25.  $\overline{CE}_0 = \overline{LB} = \overline{UB} = R/\overline{W} = V_{|L}$ ;  $CE_1 = \overline{CNTRST} = \overline{MRST} = \overline{MKLD} = \overline{MKRD} = \overline{CNTRD} = V_{|H|}$ .

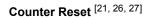

Notes: 26.  $\overline{CE}_0 = \overline{LB} = \overline{UB} = V_{IL}$ ;  $CE_1 = \overline{MRST} = \overline{MKLD} = \overline{MKRD} = \overline{CNTRD} = V_{IH}$ . 27. No dead cycle exists during counter reset. A Read or Write cycle may be coincidental with the counter reset.

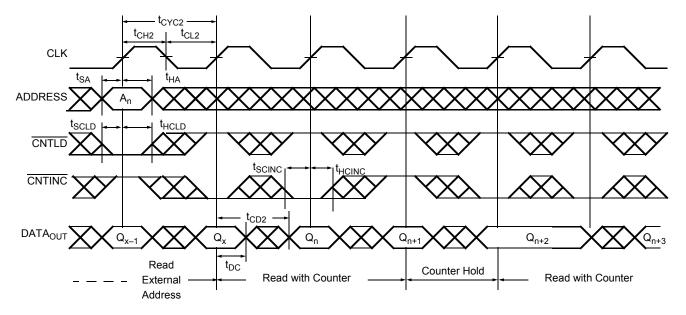

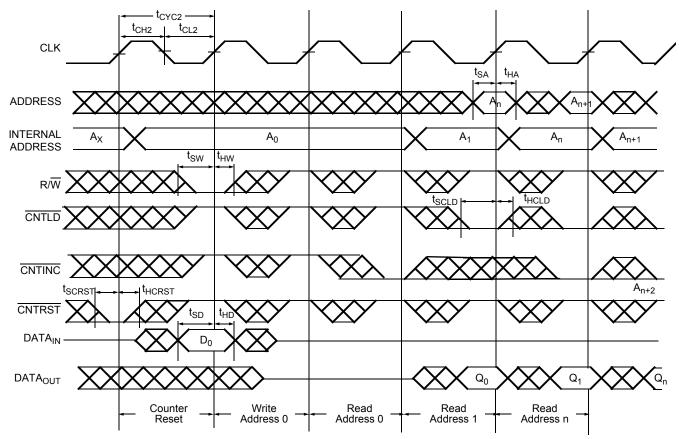

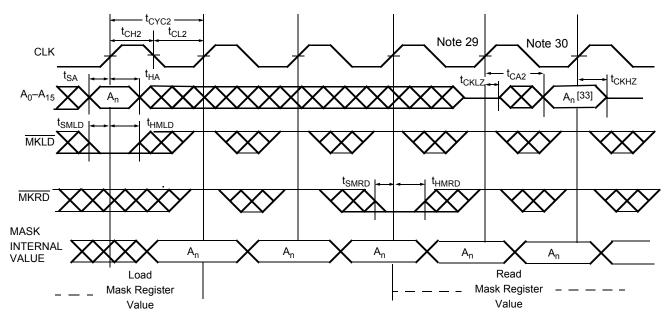

#### Load and Read Address Counter<sup>[28]</sup>

- Notes: 28.  $\overline{CE}_0 = \overline{OE} = \overline{LB} = \overline{UB} = V_{IL}$ ;  $CE_1 = R/W = \overline{CNTRST} = \overline{MRST} = \overline{MKLD} = \overline{MKRD} = V_{IH}$ . 29. Address in output mode. Host must not be driving address bus after time  $t_{CKLZ}$  in next clock cycle.

- 30. Address in input mode. Host can drive address bus after  $t_{CKHZ}$ . 31. This is the value of the address counter being read out on the address lines.

# Load and Read Mask Register [32]

Notes: 32.  $\overline{CE}_0 = \overline{OE} = \overline{LB} = \overline{UB} = V_{|L}$ ;  $CE_1 = R/\overline{W} = \overline{CNTRST} = \overline{MRST} = \overline{CNTLD} = \overline{CNTRD} = \overline{CNTINC} = V_{|H}$ . 33. This is the value of the Mask Register read out on the address lines.

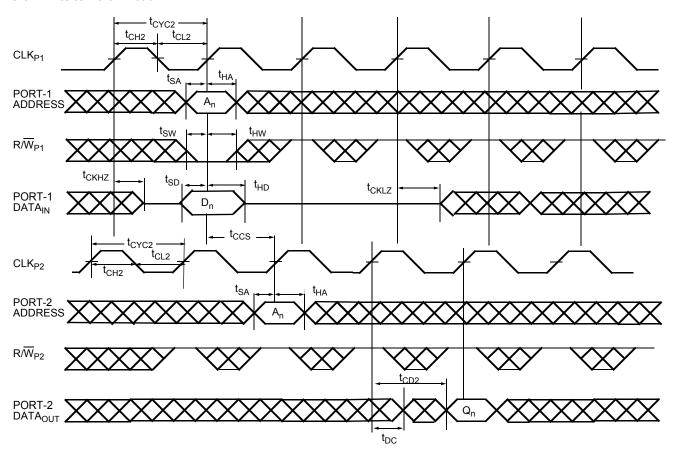

Port 1 Write to Port 2 Read<sup>[34, 35, 36]</sup>

Notes:

34.  $\overline{CE_0} = \overline{OE} = \overline{LB} = \overline{UB} = \overline{CNTLD} = V_{IL}$ ;  $CE_1 = \overline{CNTRST} = \overline{MKST} = \overline{MKRD} = \overline{CNTRD} = \overline{CNTRD} = \overline{CNTINC} = V_{IH}$ . 35. This timing is valid when one port is writing, and one or more of the three other ports is reading the same location at the same time. If  $t_{CCS}$  is violated, indeterminate data will be read out.

36. If t<sub>CCS</sub>< minimum specified value, then Port 2 will read the most recent data (written by Port 1) only (2\*t<sub>CYC2</sub> + t<sub>CD2</sub>) after the rising edge of Port 2's clock. If t<sub>CCS</sub> ≥ minimum specified value, then Port 2 will read the most recent data (written by Port 1) (t<sub>CYC2</sub> + t<sub>CD2</sub>) after the rising edge of Port 2's clock.

Counter Interrupt [37, 38, 39]

Notes:

- $37.\overline{CE_0} = \overline{OE} = \overline{IB} = \overline{IB} = V_{IL}$ ;  $CE_1 = R/\overline{W} = \overline{CNTRST} = \overline{MRST} = \overline{CNTRD} = \overline{MKRD} = V_{IH}$ .  $38.\overline{CNTINT}$  is always driven.

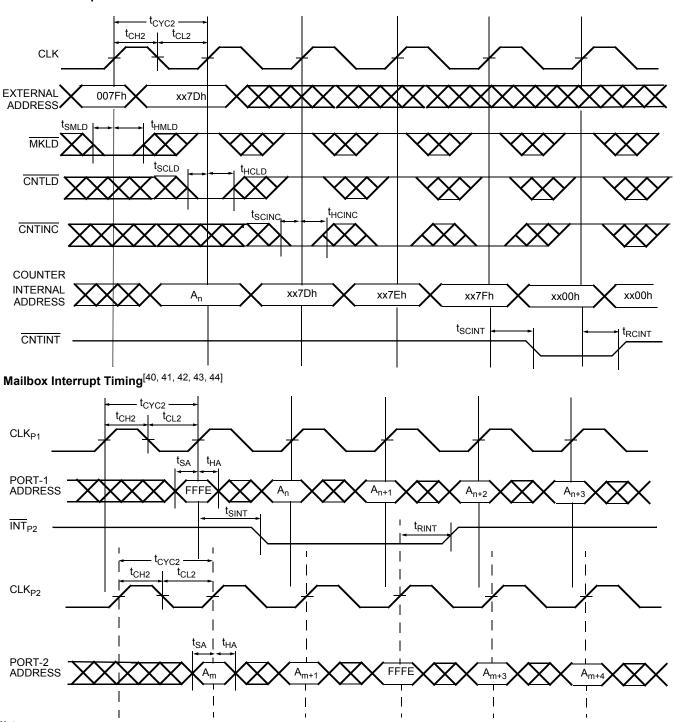

- 39. CNTING goes LOW as the counter address masked portion is incremented from xx7Fh to xx00h. The "x" is "Don't Care." 40.  $CE_0 = OE = LB = UB = CNTLD = V_{|L|}; CE_1 = CNTRST = MRST = CNTRD = CNTINC = MKRD = MKLD = V_{|H|}.$ 41. Address "FFFE" is the mailbox location for Port 2.

- 42. Port 1 is configured for Write operation, and Port 2 is configured for Read operation.

- 43. Port 1 and Port 2 are used for simplicity. All four ports can write to or read from any mailbox.

44. Interrupt flag is set with respect to the rising edge of the write clock, and is reset with respect to the rising edge of the read clock.

# Table 1. Read/Write and Enable Operation (Any Port)<sup>[45, 46, 47]</sup>

|    |     | Inputs |                 |     | Outputs                             |                  |

|----|-----|--------|-----------------|-----|-------------------------------------|------------------|

| OE | CLK | CE0    | CE <sub>1</sub> | R/W | I/O <sub>0</sub> -I/O <sub>17</sub> | Operation        |

| Х  |     | Н      | х               | Х   | High-Z                              | Deselected       |

| Х  | Ļ   | х      | L               | Х   | High-Z                              | Deselected       |

| Х  | 5   | L      | Н               | L   | D <sub>IN</sub>                     | Write            |

| L  | 1   | L      | Н               | Н   | D <sub>OUT</sub>                    | Read             |

| Н  | Х   | L      | Н               | Х   | High-Z                              | Outputs Disabled |

Table 2. Address Counter and Counter-Mask Register Control Operation (Any Port)<sup>[45, 48, 49]</sup>

| CLK | MRST | CNTRST | MKLD | CNTLD | CNTINC | CNTRD | MKRD | Mode             | Operation                                                                                                |

|-----|------|--------|------|-------|--------|-------|------|------------------|----------------------------------------------------------------------------------------------------------|

| x   | L    | х      | х    | Х     | Х      | Х     | Х    | Master-<br>Reset | Counter/Address Register Reset and Mask<br>Register Set (resets entire chip as per reset<br>state table) |

|     | Н    | L      | Х    | Х     | Х      | Х     | Х    | Reset            | Counter/Address Register Reset                                                                           |

|     | Н    | Н      | L    | Х     | Х      | Х     | Х    | Load             | Load of Address Lines into Mask Register                                                                 |

|     | Η    | Н      | Н    | L     | х      | х     | Х    | Load             | Load of Address Lines into Counter/Address<br>Register                                                   |

|     | Н    | Н      | Н    | Н     | L      | Х     | Х    | Increment        | Counter Increment                                                                                        |

|     | Н    | Н      | Н    | Н     | Н      | L     | Х    | Readback         | Readback Counter on Address Lines                                                                        |

|     | Н    | Н      | Н    | Н     | Н      | Н     | L    | Readback         | Readback Mask Register on Address Lines                                                                  |

|     | Н    | Н      | Н    | Н     | Н      | Н     | Н    | Hold             | Counter Hold                                                                                             |

**Notes:** 45. "X" = "Don't Care," "H" = V<sub>IH</sub>, "L" = V<sub>IL</sub>. 46. OE is <u>an</u> asynchronous input signal. 47. <u>When CE</u> changes state, <u>deselection</u> and read happen after one cycle of latency. 48.  $CE_0 = OE = V_{IL}$ ;  $CE_1 = R \overline{W} = V_{IH}$ . 49. Counter operation and mask register operation are independent of Chip Enables.

# Master Reset

The QuadPort DSE device undergoes a complete reset by taking its Master Reset (MRST) input LOW. The Master Reset input can switch asynchronously to the clocks. A Master Reset initializes the internal burst counters to zero, and the counter mask registers to all ones (completely unmasked). A Master Reset also forces the Mailbox Interrupt (INT) flags and the Counter Interrupt (CNTINT) flags HIGH, resets the BIST controller, and takes all registered control signals to a deselected read state.<sup>[50]</sup> A Master Reset must be performed on the QuadPort DSE device after power-up.

### Interrupts

The upper four memory locations may be used for message passing and permit communications between ports. *Table 3* shows the interrupt operation for all ports. For the 1-Mb QuadPort DSE device, the highest memory location FFFF is

the mailbox for Port 1, FFFE is the mailbox for Port 2, FFFD is the mailbox for Port 3, and FFFC is the mailbox for Port 4. *Table 3* shows that in order to set Port 1  $INT_{P1}$  flag, a write by any other port to address FFFF will assert  $INT_{P1}$  LOW. A read of FFFF location by Port 1 will reset  $INT_{P1}$  HIGH. When one port writes to the other port's mailbox, the Interrupt flag (INT) of the port that the mailbox belongs to is asserted LOW. The Interrupt is reset when the owner (port) of the mailbox reads the contents of the mailbox. The interrupt flag is set in a flow-through mode (i.e., it follows the clock edge of the writing port). Also, the flag is reset in a flow-through mode (i.e., it follows the clock edge of the reading port).

Each port can read the other port's mailbox without resetting the interrupt. If an application does not require message passing, INT pins should be treated as no-connect and should be left floating. When two ports or more write to the same mailbox at the same time INT will be asserted but the contents of the mailbox are not guaranteed to be valid.

|                                     | Port 1                       |                          | Port 2                       |                   | Port 3                       |                   | Port 4                       |                   |

|-------------------------------------|------------------------------|--------------------------|------------------------------|-------------------|------------------------------|-------------------|------------------------------|-------------------|

| Function                            | <b>A</b> <sub>0P1-15P1</sub> | <b>INT</b> <sub>P1</sub> | <b>A</b> <sub>0P2-15P2</sub> | INT <sub>P2</sub> | <b>A</b> <sub>0P3–15P3</sub> | INT <sub>P3</sub> | <b>A</b> <sub>0P4-15P4</sub> | INT <sub>P4</sub> |

| Set Port 1 INT <sub>P1</sub> Flag   | х                            | L                        | FFFF                         | Х                 | FFFF                         | Х                 | FFFF                         | Х                 |

| Reset Port 1 INT <sub>P1</sub> Flag | FFFF                         | Н                        | Х                            | Х                 | х                            | Х                 | х                            | Х                 |

| Set Port 2 INT <sub>P2</sub> Flag   | FFFE                         | Х                        | х                            | L                 | FFFE                         | Х                 | FFFE                         | Х                 |

| Reset Port 2 INT <sub>P2</sub> Flag | х                            | Х                        | FFFE                         | Н                 | х                            | Х                 | х                            | Х                 |

| Set Port 3 INT <sub>P3</sub> Flag   | FFFD                         | Х                        | FFFD                         | Х                 | х                            | L                 | FFFD                         | Х                 |

| Reset Port 3 INT <sub>P3</sub> Flag | Х                            | Х                        | Х                            | Х                 | FFFD                         | Н                 | Х                            | Х                 |

| Set Port 4 INT <sub>P4</sub> Flag   | FFFC                         | Х                        | FFFC                         | Х                 | FFFC                         | Х                 | х                            | L                 |

| Reset Port 4 INT <sub>P4</sub> Flag | Х                            | Х                        | Х                            | Х                 | Х                            | Х                 | FFFC                         | Н                 |

#### Table 3. Interrupt Operation Example

Note:

50. <u>During M</u>aster Reset the control signals will be set to a deselected read state:  $\overline{CE}_{0I} = \overline{LBI} = \overline{UBI} = \overline{RWI} = \overline{MKLDI} = \overline{MKRDI} = \overline{CNTRDI} = \overline$

# Address Counter Control Operations

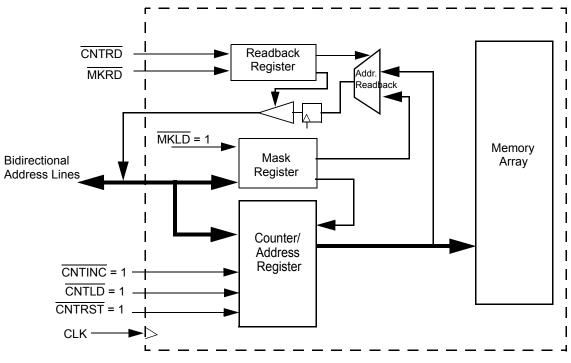

Counter enable inputs are provided to stall the operation of the address input and utilize the internal address generated by the internal counter for the fast interleaved memory applications. A port's burst counter is loaded with the port's Counter Load pin (CNTLD). When the port's Counter Increment (CNTINC) is asserted, the address counter will increment on each LOW to HIGH transition of that port's clock signal. This will read/write one word from/into each successive address location until CNTINC is deasserted. Depending on the mask register state, the counter can address the entire memory array and will loop back to start. Counter Reset (CNTRST) is used to reset the Burst Counter (the Mask Register value is unaffected). When using the counter in readback mode, the internal address value of the counter will be read back on the address lines when Counter Readback Signal (CNTRD) is asserted.

*Figure 1* provides a block diagram of the readback operation. Table 2 lists control signals required for counter operations. The signals are listed based on their priority. For example, Master Reset takes precedence over Counter Reset, and Counter Load has lower priority than Mask Register Load (described below). All counter operations are independent of Chip Enables ( $\overline{CE}_0$  and  $CE_1$ ). When the address readback operation is performed the data I/Os are three-stated (if CEs are active) and one-clock cycle (no-operation cycle) latency is experienced. The address will be read at time  $t_{CA2}$  from the rising edge of the clock following the no-operation cycle. The read back address can be either of the burst counter or the mask register based on the levels of Counter Read signal (CNTRD) and Mask Register Read signal (MKRD). Both signals are synchronized to the port's clock as shown in Table 2. Counter read has a higher priority than mask read.

Figure 1. Counter and Mask Register Read Back on Address Lines

# **Counter-Mask Register**

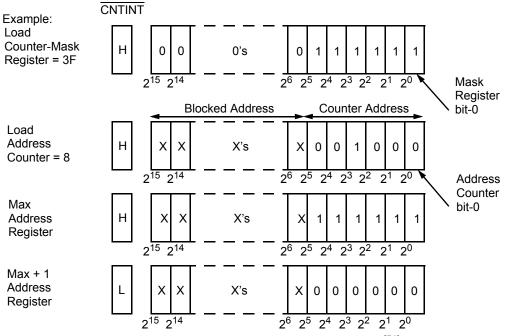

Figure 2. Programmable Counter-Mask Register Operation<sup>[51]</sup>

The burst counter has a mask register that controls when and where the counter wraps. An interrupt flag (CNTINT) is asserted for one clock cycle when the unmasked portion of the counter address wraps around from all ones (CNTINC must be asserted) to all zeros. The example in Figure 2 shows the counter mask register loaded with a mask value of 003F unmasking the first 6 bits with bit "0" as the LSB and bit "15" as the MSB. The maximum value the mask register can be loaded with is FFFF. Setting the mask register to this value allows the counter to access the entire memory space. The address counter is then loaded with an initial value of XXX8. The "blocked" addresses (in this case, the 6th address through the 15th address) are loaded with an address but do not increment once loaded. The counter address will start at address XXX8. With CNTINC asserted LOW, the counter will increment its internal address value till it reaches the mask register value of 3F and wraps around the memory block to location XXX0. Therefore, the counter uses the mask-register to define wrap-around point. The mask register of every port is loaded when MKLD (mask register load) for that port is LOW. When MKRD is LOW, the value of the mask register can be read out on address lines in a manner similar to counter read back operation (see Table 2 for required conditions).

When the burst counter is loaded with an address higher than the mask register value, the higher addresses will form the masked portion of the counter address and are called blocked addresses. The blocked addresses will not be changed or affected by the counter increment operation. The only exception is mask register bit 0. It can be masked to allow the address counter to increment by two. If the mask register bit 0 is loaded with a logic value of "0," then address counter bit 0 is masked and can not be changed during counter increment operation. If the loaded value for address counter bit 0 is "0,"

#### Note:

51. The "X" in this diagram represents the counter upper-bits.

the counter will increment by two and the address values are even. If the loaded value for address counter bit 0 is "1," the counter will increment by two and the address values are odd. This operations allows the user to achieve a 36-bit interface using any two ports, where the counter of one port counts even addresses and the counter of the other port counts odd addresses. This even-odd address scheme stores one half of the 36-bit word in even memory locations, and the other half in odd memory locations. CNTINT will be asserted when the unmasked portion of the counter wraps to all zeros. Loading mask register bit 0 with "1" allows the counter to increment the address value sequentially.

Table 2 groups the operations of the mask register with the operations of the address counter. Address counter and mask register signals are all synchronized to the port's clock CLK. Master reset (MRST) is the only asynchronous signal listed on *Table 2*. Signals are listed based on their priority going from left column to right column with MRST being the highest. A LOW on MRST will reset both counter register to all zeros and mask register to all ones. On the other hand, a LOW on CNTRST will only clear the address counter register to zeros and the mask register will remain intact.

There are four operations for the counter and mask register:

- 1. Load operation: When CNTLD or MKLD is LOW, the address counter or the mask register is loaded with the address value presented at the address lines. This value ranges from 0 to FFFF (64K). The mask register load operation has a higher priority over the address counter load operation.

- 2. Increment: Once the address counter is loaded with an external address, the counter can internally increment the address value by asserting CNTINC LOW. The counter can

- address the entire memory array (depend on the value of the mask register) and loop back to location 0. The increment operation is second in priority to load operation.

- 3. Readback: the internal value of either the burst counter or the mask register can be read out on the address lines when CNTRD or MKRD is LOW. Counter readback has higher priority over mask register readback. A no-operation delay cycle is experienced when readback operation is performed. The address will be valid after  $t_{CA2}$  (for counter readback) or  $t_{CM2}$  (for mask readback) from the following port's clock rising edge. Address readback operation is independent of the port's chip enables ( $\overline{CE}_0$  and  $\overline{CE}_1$ ). If address readback occurs while the port is enabled (chip enables active), the data lines (I/Os) will be three-stated.

- 4. Hold operation: In order to hold the value of the address counter at certain address, all signals in *Table 2* have to be HIGH. This operation has the least priority. This operation is useful in many applications where wait states are needed or when address is available few cycles ahead of data.

The counter and mask register operations are totally independent of port chip enables.

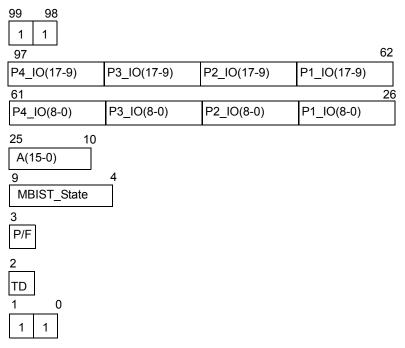

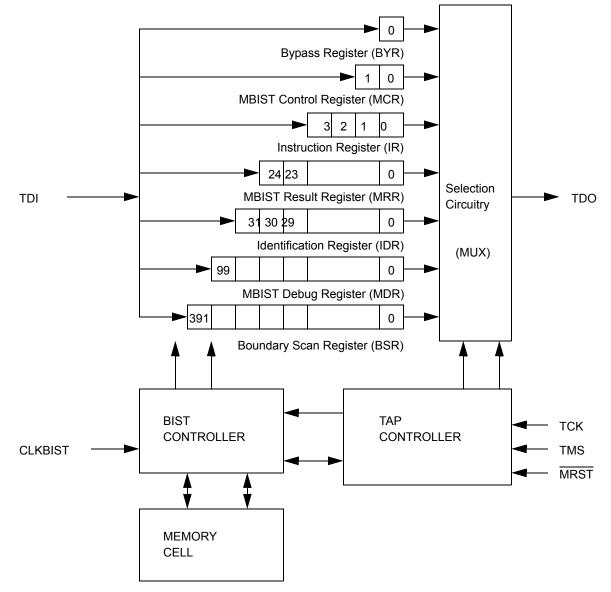

# IEEE 1149.1 Serial Boundary Scan (JTAG) and Memory Built-In-Self-Test (MBIST)

The CY7C0430BV and CY7C0430CV incorporate a serial boundary scan test access port (TAP). This port is fully compatible with IEEE Standard 1149.1-2001<sup>[52]</sup>. The TAP operates using JEDEC standard 3.3V I/O logic levels. It is composed of three input connections and one output connection required by the test logic defined by the standard. Memory BIST circuitry will also be controlled through the TAP interface. All MBIST instructions are compliant to the JTAG standard. An external clock (CLKBIST) is provided to allow the user to run BIST at speeds up to 50 MHz. CLKBIST is multiplexed internally with the ports clocks during BIST operation.

#### **Disabling the JTAG Feature**

It is possible to operate the QuadPort DSE device without using the JTAG feature. To disable the TAP controller, TCK must be tied LOW ( $V_{SS}$ ) to prevent clocking of the device. TDI and TMS are internally pulled up and may be unconnected. They may alternately be connected to  $V_{DD}$  through a pull-up resistor. TDO should be left unconnected. CLKBIST must be tied LOW to disable the MBIST. Upon power-up, the device will come up in a reset state which will not interfere with the operation of the device.

#### Test Access Port (TAP)–Test Clock (TCK)

The test clock is used only with the TAP controller. All inputs are captured on the rising edge of TCK. All outputs are driven from the falling edge of TCK.

#### **Test Mode Select**

The TMS input is used to give commands to the TAP controller and is sampled on the rising edge of TCK. It is allowable to leave this pin unconnected if the TAP is not used. The pin is pulled up internally, resulting in a logic HIGH level.

#### Test Data-In (TDI)

The TDI pin is used to serially input information into the registers and can be connected to the input of any of the registers. The register between TDI and TDO is chosen by the instruction that is loaded into the TAP instruction register. For information on loading the instruction register, see the TAP Controller State Diagram. TDI is internally pulled up and can be unconnected if the TAP is unused in an application. TDI is connected to the most significant bit (MSB) on any register.

#### Test Data Out (TDO)

The TDO output pin is used to serially clock data-out from the registers. The output is active depending upon the current state of the TAP state machine (see TAP Controller State Diagram (FSM)). The output changes on the falling edge of TCK. TDO is connected to the least significant bit (LSB) of any register.

#### Performing a TAP Reset

A Reset is performed by forcing TMS HIGH ( $V_{DD}$ ) for five rising edges of TCK. This RESET does not affect the operation of the QuadPort DSE device and may be performed while the device is operating. At power-up, the TAP is reset internally to ensure that TDO comes up in a High-Z state.

#### **TAP Registers**

Registers are connected between the TDI and TDO pins and allow data to be scanned into and out of the QuadPort DSE device test circuitry. Only one register can be selected at a time through the instruction registers. Data is serially loaded into the TDI pin on the rising edge of TCK. Data is output on the TDO pin on the falling edge of TCK.

#### Instruction Register

Four-bit instructions can be serially loaded into the instruction register. This register is loaded when it is placed between the TDI and TDO pins as shown in the following JTAG/BIST Controller diagram. Upon power-up, the instruction register is loaded with the IDCODE instruction. It is also loaded with the IDCODE instruction if the controller is placed in a reset state as described in the previous section.

When the TAP controller is in the CaptureIR state, the two least significant bits are loaded with a binary "01" pattern to allow for fault isolation of the board level serial test path.

#### **Bypass Register**

To save time when serially shifting data through registers, it is sometimes advantageous to skip certain devices. The bypass register is a single-bit register that can be placed between TDI and TDO pins. This allows data to be shifted through the QuadPort DSE device with minimal delay. The bypass register is set LOW ( $V_{SS}$ ) when the BYPASS instruction is executed.

#### **Boundary Scan Register**

The boundary scan register is connected to all the input and output pins on the QuadPort DSE device. The boundary scan register is loaded with the contents of the QuadPort DSE device Input and Output ring when the TAP controller is in the Capture-DR state and is then placed between the TDI and TDO pins when the controller is moved to the Shift-DR state.

The EXTEST, and SAMPLE/PRELOAD instructions can be used to capture the contents of the Input and Output ring.

#### Identification (ID) Register

The ID register is loaded with a vendor-specific, 32-bit code during the Capture-DR state when the IDCODE command is loaded in the instruction register. The IDCODE is hardwired into the QuadPort DSE device and can be shifted out when the TAP controller is in the Shift-DR state. The ID register has a vendor code and other information described in the Identification Register Definitions table.

#### **TAP Instruction Set**

Sixteen different instructions are possible with the 4-bit instruction register. All combinations are listed in *Table 6*, Instruction Codes. Seven of these instructions (codes) are listed as RESERVED and should not be used. The other nine instructions are described in detail below.

The TAP controller used in this QuadPort DSE device is fully compatible<sup>[52]</sup> with the 1149.1 convention. The TAP controller can be used to load address, data or control signals into the QuadPort DSE device and can preload the Input or output buffers. The QuadPort DSE device implements all of the 1149.1 instructions except INTEST. *Table 6* lists all instructions.

Instructions are loaded into the TAP controller during the Shift-IR state when the instruction register is placed between TDI and TDO. During this state, instructions are shifted through the instruction register through the TDI and TDO pins. To execute the instruction once it is shifted in, the TAP controller needs to be moved into the Update-IR state.

#### EXTEST

EXTEST is a mandatory 1149.1 instruction which is to be executed whenever the instruction register is loaded with all 0s. EXTEST allows circuitry external to the QuadPort DSE device package to be tested. Boundary-scan register cells at output pins are used to apply test stimuli, while those at input pins capture test results.

#### IDCODE

The IDCODE instruction causes a vendor-specific, 32-bit code to be loaded into the identification register. It also places the identification register between the TDI and TDO pins and allows the IDCODE to be shifted out of the device when the TAP controller enters the Shift-DR state. The IDCODE instruction is loaded into the instruction register upon power-up or whenever the TAP controller is given a test logic reset state.

#### High-Z

The High-Z instruction causes the bypass register to be connected between the TDI and TDO pins when the TAP controller is in a Shift-DR state. It also places all QuadPort DSE device outputs into a High-Z state.

#### SAMPLE/PRELOAD

SAMPLE/PRELOAD is a 1149.1 mandatory instruction. When the SAMPLE/PRELOAD instructions loaded into the instruction register and the TAP controller in the Capture-DR state, a snapshot of data on the inputs and output pins is captured in the boundary scan register. The user must be aware that the TAP controller clock can only operate at a frequency up to 10 MHz, while the QuadPort DSE device clock operates more than an order of magnitude faster. Because there is a large difference in the clock frequencies, it is possible that during the Capture-DR state, an input or output will undergo a transition. The TAP may then try to capture a signal while in transition (metastable state). This will not harm the device, but there is no guarantee as to the value that will be captured. Repeatable results may not be possible.