# MoBL-USB™ FX2LP18 USB Microcontroller

### **Features**

- USB 2.0 9 V USB-IF high speed and full speed compliant (TID# 40000188)

- Single-chip integrated USB 2.0 transceiver, smart SIE, and enhanced 8051 microprocessor

- Ideal for mobile applications (cell phone, smart phones, PDAs, MP3 players)

- □ Ultra low power

- □ Suspend current: 20 µA (typical)

- Software: 8051 Code runs from:

- ☐ Internal RAM, which is loaded from EEPROM

- 16 kBytes of on-chip code/data RAM

- Four programmable BULK/INTERRUPT/ISOCHRONOUS endpoints

- □ Buffering options: double, triple, and quad

- Additional Programmable (BULK/INTERRUPT) 64-Byte Endpoint

- 8 or 16-Bit External Data Interface

- Smart Media Standard ECC Generation

- GPIF (General Programmable Interface)

- ☐ Allows direct connection to most parallel interface

- □ Programmable waveform descriptors and configuration registers to define waveforms

- □ Supports multiple Ready and Control outputs

- Integrated, Industry Standard Enhanced 8051

- □ 48 MHz, 24 MHz, or 12 MHz CPU operation

- □ Four clocks per instruction cycle

- □ Three counter/timers

- □ Expanded interrupt system

- □ Two data pointers

- 1.8 V Core Operation

- 1.8 V to 3.3 V I/O Operation

- Vectored USB Interrupts and GPIF/FIFO Interrupts

- Separate Data Buffers for Setup and Data Portions of a CONTROL Transfer

- Integrated I<sup>2</sup>C Controller, runs at 100 or 400 kHz

- Four Integrated FIFOs

- □ Integrated glue logic and FIFOs lower system cost

- □ Automatic conversion to and from 16-bit buses

- □ Master or slave operation

- □ Uses external clock or asynchronous strobes

- ☐ Easy interface to ASIC and DSP ICs

- Available in Industrial Temperature Grade

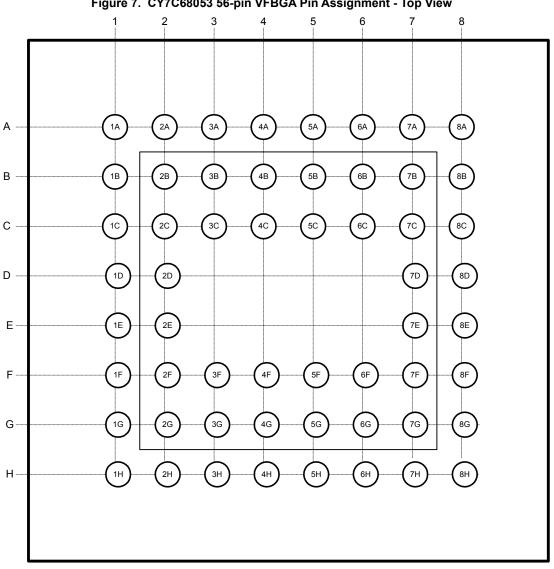

- Available in one Pb-free Package with up to 24 GPIOs□ 56-pin VFBGA (24 GPIOs)

### More Information

Cypress provides a wealth of data at <a href="www.cypress.com">www.cypress.com</a> to help you to select the right device for your design, and to help you to quickly and effectively integrate the device into your design. For a comprehensive list of resources, see the knowledge base article AN65209 - Getting Started with FX2LP.

- Overview: USB Portfolio, USB Roadmap

- USB 3.0 Product Selectors: FX2LP, AT2LP, NX2LP-Flex, SX2

- Application notes: Cypress offers a large number of USB application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with FX3 are:

- □ AN65209 Getting Started with FX2LP

- □ AN15652 Interfacing a Cypress MoBL-USB™ FX2LP18 with an Intel PXA27x Processor

- ¬ AN6076 Differences between EZ-USB<sup>®</sup> FX2LP™ and MoBL-USB™ FX2LP18

- ☐ For complete list of Application notes, click here

- Code Examples:

- □ USB Hi-Speed

- Technical Reference Manual (TRM):

- MoBL-USB™ FX2LP18 Technical Reference Manual

- Reference Designs:

- CY4661 External USB Hard Disk Drives (HDD) with Fingerprint Authentication Security

- □ FX2LP DMB-T/H TV Dongle Reference Design

- Models: IBIS

### MoBL-USB FX2LP18 Development Kit

The CY3687 MoBL-USB™ FX2LP18 Development Kit is a complete development resource for FX2LP18. It provides a platform to develop and test custom projects using FX2LP18. The development kit contains collateral materials for the firmware, hardware, and software aspects of a design using FX2LP18.

### GPIF™ II Designer

FX2LP™ General Programmable Interface (GPIF) provides an independent hardware unit, which creates the data and control signals required by an external interface. FX2LP GPIF Designer allows users to create and modify GPIF waveform descriptors for EZ-USB FX2/ FX2LP family of chips using a graphical user interface. Extensive discussion of general GPIF discussion and programming using GPIF Designer is included in FX2LP18 Technical Reference Manual and GPIF Designer User Guide, distributed with GPIF Designer. AN66806 - Getting Started with EZ-USB® FX2LP™ GPIF can be a good starting point.

### **Contents**

| Functional Description        | . 4 |

|-------------------------------|-----|

| Applications                  | . 4 |

| Functional Overview           | . 4 |

| USB Signaling Speed           |     |

| 8051 Microprocessor           | . 4 |

| I <sup>2</sup> C™ Bus         | . 5 |

| Buses                         |     |

| USB Boot Methods              | . 5 |

| ReNumeration™                 |     |

| Bus-Powered Applications      | . 5 |

| Interrupt System              |     |

| Reset and Wakeup              |     |

| Program/Data RAM              | . 9 |

| Register Addresses            | . 9 |

| Endpoint RAM                  | . 9 |

| External FIFO Interface       | 11  |

| GPIF                          | 11  |

| ECC Generation <sup>[6]</sup> | 12  |

| USB Uploads and Downloads     | 12  |

| Autopointer Access            |     |

| I <sup>2</sup> C Controller   | 12  |

| Pin Assignments               | 13  |

| CY7C68053 Pin Descriptions    | 15  |

| Register Summary              |     |

| Absolute Maximum Ratings      | 26  |

| Operating Conditions          |     |

| DC Characteristics            | 26  |

| AC Electrical Characteristics             | . 27 |

|-------------------------------------------|------|

| USB Transceiver                           | . 27 |

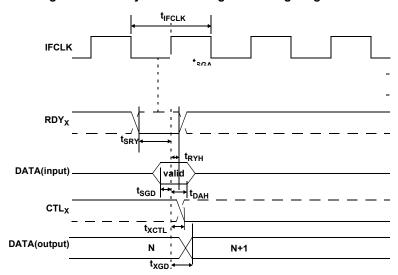

| GPIF Synchronous Signals                  | . 27 |

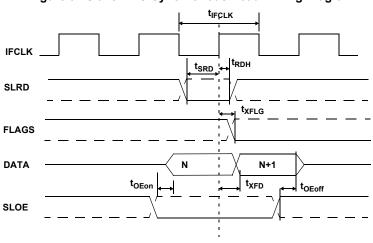

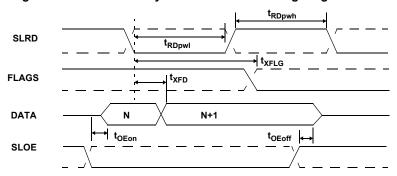

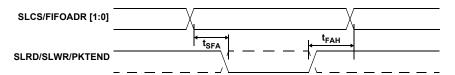

| Slave FIFO Synchronous Read               |      |

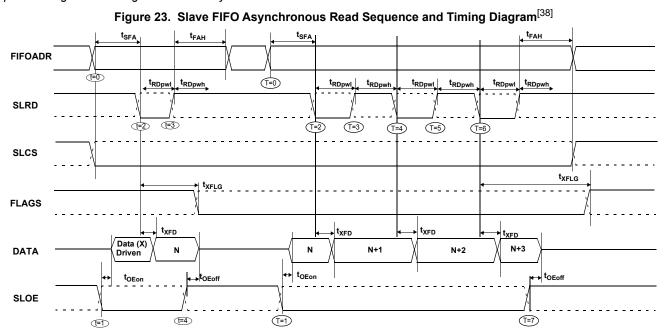

| Slave FIFO Asynchronous Read              |      |

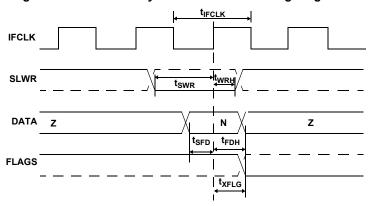

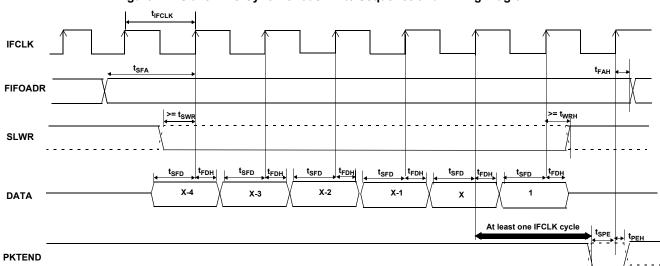

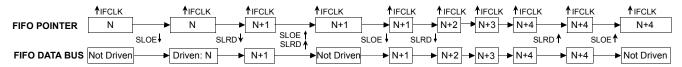

| Slave FIFO Synchronous Write              |      |

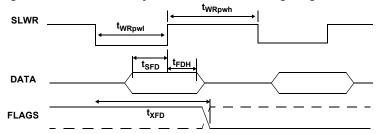

| Slave FIFO Asynchronous Write             |      |

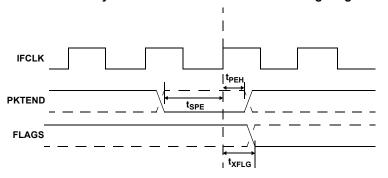

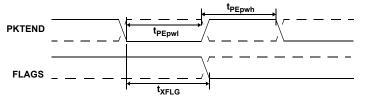

| Slave FIFO Synchronous Packet End Strobe  |      |

| Slave FIFO Asynchronous Packet End Strobe |      |

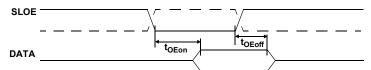

| Slave FIFO Output Enable                  |      |

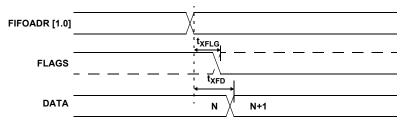

| Slave FIFO Address to Flags/Data          | . 34 |

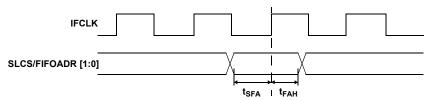

| Slave FIFO Synchronous Address            | . 34 |

| Slave FIFO Asynchronous Address           | . 34 |

| Sequence Diagram                          | . 35 |

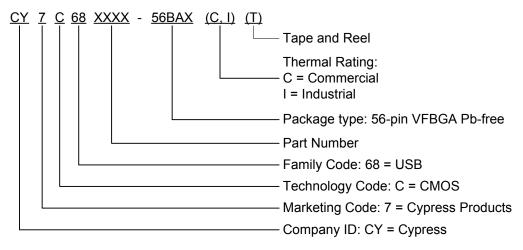

| Ordering Information                      | . 39 |

| Ordering Code Definitions                 | . 39 |

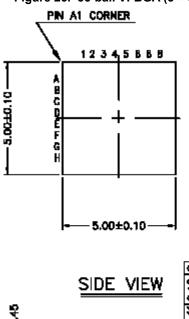

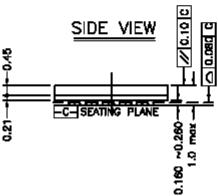

| Package Diagram                           | . 40 |

| PCB Layout Recommendations                | . 41 |

| Acronyms                                  | . 42 |

| Document Conventions                      | . 42 |

| Units of Measure                          | . 42 |

| Document History Page                     | . 43 |

| Sales, Solutions, and Legal Information   | . 44 |

| Worldwide Sales and Design Support        | . 44 |

| Products                                  |      |

| PSoC® Solutions                           |      |

| Cypress Developer Community               | . 44 |

| Technical Support                         | 44   |

### **Functional Description**

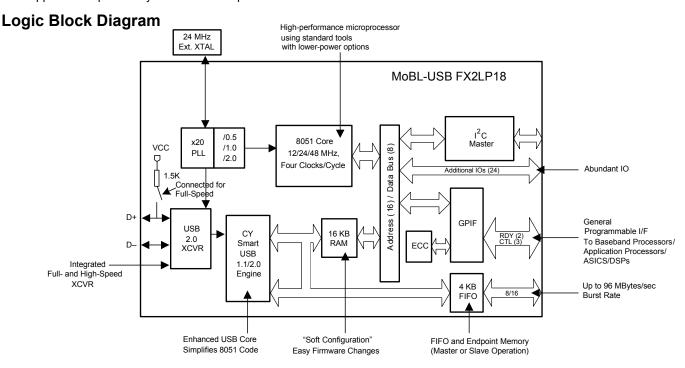

Cypress Semiconductor Corporation's MoBL-USB™ FX2LP18 (CY7C68053) is a low voltage (1.8 V) version of the EZ-USB® FX2LP (CY7C68013A), which is a highly integrated, low power USB 2.0 microcontroller. By integrating the USB 2.0 transceiver, serial interface engine (SIE), enhanced 8051 microcontroller, and a programmable peripheral interface in a single chip, Cypress has created a very cost effective solution that provides superior time-to-market advantages with low power to enable bus powered applications.

The ingenious architecture of MoBL-USB FX2LP18 results in data transfer rates of over 53 Mbytes per second, the maximum allowable USB 2.0 bandwidth, while still using a low cost 8051 microcontroller in a package as small as a 56VFBGA (5 mm x 5 mm). Because it incorporates the USB 2.0 transceiver, the MoBL-USB FX2LP18 is more economical, providing a smaller footprint solution than USB 2.0 SIE or external transceiver implementations. With MoBL-USB FX2LP18, the Cypress Smart SIE handles most of the USB 1.1 and 2.0 protocol in hardware, freeing the embedded microcontroller for application-specific functions and decreasing development time to ensure USB compatibility.

The General Programmable Interface (GPIF) and Master/Slave Endpoint FIFO (8 or 16-bit data bus) provide an easy and glueless interface to popular interfaces such as ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors.

The MoBL-USB FX2LP18 is also referred to as FX2LP18 in this document.

### **Applications**

There are a wide variety of applications for the MoBL-USB FX2LP18. It is used in cell phones, smart phones, PDAs, and MP3 players, to name a few.

The 'Reference Designs' section of the Cypress web site provides additional tools for typical USB 2.0 applications. Each reference design comes complete with firmware source and object code, schematics, and documentation. For more information, visit http://www.cypress.com.

#### Functional Overview

The functionality of this chip is described in the sections below.

### **USB Signaling Speed**

FX2LP18 operates at two of the three rates defined in the USB Specification Revision 2.0, dated April 27, 2000.

- Full speed, with a signaling bit rate of 12 Mbps

- High speed, with a signaling bit rate of 480 Mbps

FX2LP18 does not support the low speed signaling mode of 1.5 Mbps.

### **8051 Microprocessor**

The 8051 microprocessor embedded in the FX2LP18 family has 256 bytes of register RAM, an expanded interrupt system, and three timer/counters.

### 8051 Clock Frequency

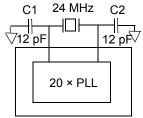

FX2LP18 has an on-chip oscillator circuit that uses an external 24 MHz (±100-ppm) crystal with the following characteristics:

- Parallel resonant

- Fundamental mode

- 500 µW drive level

- 12 pF (5% tolerance) load capacitors

An on-chip PLL multiplies the 24 MHz oscillator up to 480 MHz, as required by the transceiver/PHY; internal counters divide it down for use as the 8051 clock. The default 8051 clock frequency is 12 MHz. The clock frequency of the 8051 can be changed by the 8051 through the CPUCS register, dynamically.

Figure 1. Crystal Configuration

12 pF capacitor values assumes a trace capacitance of 3 pF per side on a four-layer FR4 PCA

The CLKOUT pin, which can be tristated and inverted using internal control bits, outputs the 50% duty cycle 8051 clock, at the selected 8051 clock frequency — 48, 24, or 12 MHz.

### Special Function Registers

Certain 8051 Special Function Register (SFR) addresses are populated to provide fast access to critical FX2LP18 functions. These SFR additions are shown in Table 1 on page 5. Bold type indicates non standard, enhanced 8051 registers. The two SFR rows that end with '0' and '8' contain bit-addressable registers. The four I/O ports A–D use the SFR addresses used in the standard 8051 for ports 0–3, which are not implemented in FX2LP18. Because of the faster and more efficient SFR addressing, the FX2LP18 I/O ports are not addressable in external RAM space (using the MOVX instruction).

**Table 1. Special Function Registers**

| x | 8x    | 9x        | Ax            | Bx             | Сх     | Dx    | Ex  | Fx  |

|---|-------|-----------|---------------|----------------|--------|-------|-----|-----|

| 0 | IOA   | IOB       | IOC           | IOD            | SCON1  | PSW   | ACC | В   |

| 1 | SP    | EXIF      | INT2CLR       | IOE            | SBUF1  |       |     |     |

| 2 | DPL0  | MPAGE     |               | OEA            |        |       |     |     |

| 3 | DPH0  |           |               | OEB            |        |       |     |     |

| 4 | DPL1  |           |               | OEC            |        |       |     |     |

| 5 | DPH1  |           |               | OED            |        |       |     |     |

| 6 | DPS   |           |               | OEE            |        |       |     |     |

| 7 | PCON  |           |               |                |        |       |     |     |

| 8 | TCON  | SCON0     | IE            | IP             | T2CON  | EICON | EIE | EIP |

| 9 | TMOD  | SBUF0     |               |                |        |       |     |     |

| Α | TL0   | AUTOPTRH1 | EP2468STAT    | EP01STAT       | RCAP2L |       |     |     |

| В | TL1   | AUTOPTRL1 | EP24FIFOFLGS  | GPIFTRIG       | RCAP2H |       |     |     |

| С | TH0   | Reserved  | EP68FIFOFLGS  |                | TL2    |       |     |     |

| D | TH1   | AUTOPTRH2 |               | GPIFSGLDATH    | TH2    |       |     |     |

| Е | CKCON | AUTOPTRL2 |               | GPIFSGLDATLX   |        |       |     |     |

| F |       | Reserved  | AUTOPTRSET-UP | GPIFSGLDATLNOX |        |       |     | -   |

### I<sup>2</sup>C™ Bus

FX2LP18 supports the  $I^2C$  bus as a master only at 100 or 400 KHz. SCL and SDA pins have open-drain outputs and hysteresis inputs. These signals must be pulled up to either  $V_{CC}$  or  $V_{CC\_IO}$ , even if no  $I^2C$  device is connected. (Connecting to  $V_{CC\_IO}$  may be more convenient.)

#### **Buses**

This 56-pin package has an 8- or 16-bit 'FIFO' bidirectional data bus, multiplexed on I/O ports B and D.

#### **USB Boot Methods**

During the power up sequence, internal logic checks the I<sup>2</sup>C port for the connection of an EEPROM whose first byte is 0xC2. If found, it boot-loads the EEPROM contents into internal RAM (0xC2 load). If no EEPROM is present, an external processor must emulate an I<sup>2</sup>C slave. The FX2LP18 does not enumerate using internally stored descriptors (for example, Cypress's VID/PID/DID is not used for enumeration).<sup>[1]</sup>

### **ReNumeration™**

Because the FX2LP18's configuration is soft, one chip can take on the identities of multiple distinct USB devices.

When first plugged into USB, the FX2LP18 enumerates automatically and downloads firmware and USB descriptor tables over the USB cable. Next, the FX2LP18 enumerates again, this time as a device defined by the downloaded information. This patented two-step process, called ReNumeration™, happens instantly when the device is plugged in, with no hint that the initial download step has occurred.

Two control bits in the USBCS (USB Control and Status) register control the ReNumeration process: DISCON and RENUM. To simulate a USB disconnect, the firmware sets DISCON to 1. To reconnect, the firmware clears DISCON to 0.

Before reconnecting, the firmware sets or clears the RENUM bit to indicate whether the firmware or the Default USB Device handles device requests over endpoint zero: if RENUM = 0, the Default USB Device handles device requests; if RENUM = 1, the firmware does.

### **Bus-Powered Applications**

The FX2LP18 fully supports bus-powered designs by enumerating with less than 100 mA as required by the USB 2.0 specification.

#### Note

<sup>1.</sup> The I<sup>2</sup>C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

### Interrupt System

The FX2LP18 interrupts are described in this section.

INT2 Interrupt Request and Enable Registers

FX2LP18 implements an autovector feature for INT2. There are 27 INT2 (USB) vectors. See the *MoBL-USB™ Technical Reference Manual (TRM)* for more details.

#### USB Interrupt Autovectors

The main USB interrupt is shared by 27 interrupt sources. To save the code and processing time that is normally required to identify the individual USB interrupt source, the FX2LP18

provides a second level of interrupt vectoring, called 'Autovectoring.' When a USB interrupt is asserted, the FX2LP18 pushes the program counter onto its stack then jumps to address 0x0043, where it expects to find a 'jump' instruction to the USB interrupt service routine.

The FX2LP18 jump instruction is encoded, as shown in Table 2.

If Autovectoring is enabled (AV2EN = 1 in the INTSET-UP register), the FX2LP18 substitutes its INT2VEC byte. Therefore, if the high byte ('page') of a jump-table address is preloaded at location 0x0044, the automatically inserted INT2VEC byte at 0x0045 directs the jump to the correct address out of the 27 addresses within the page.

Table 2. INT2 USB Interrupts

| Priority | INT2VEC Value | Source    | Notes                                      |

|----------|---------------|-----------|--------------------------------------------|

| 1        | 00            | SUDAV     | Setup data available                       |

| 2        | 04            | SOF       | Start of frame (or microframe)             |

| 3        | 08            | SUTOK     | Setup token received                       |

| 4        | 0C            | SUSPEND   | USB suspend request                        |

| 5        | 10            | USB RESET | Bus reset                                  |

| 6        | 14            | HISPEED   | Entered high speed operation               |

| 7        | 18            | EP0ACK    | FX2LP18 ACK'd the control handshake        |

| 8        | 1C            | _         | Reserved                                   |

| 9        | 20            | EP0-IN    | EP0-IN ready to be loaded with data        |

| 10       | 24            | EP0-OUT   | EP0-OUT has USB data                       |

| 11       | 28            | EP1-IN    | EP1-IN ready to be loaded with data        |

| 12       | 2C            | EP1-OUT   | EP1-OUT has USB data                       |

| 13       | 30            | EP2       | IN: buffer available. OUT: buffer has data |

| 14       | 34            | EP4       | IN: buffer available. OUT: buffer has data |

| 15       | 38            | EP6       | IN: buffer available. OUT: buffer has data |

| 16       | 3C            | EP8       | IN: buffer available. OUT: buffer has data |

| 17       | 40            | IBN       | IN-Bulk-NAK (any IN endpoint)              |

| 18       | 44            | _         | Reserved                                   |

| 19       | 48            | EP0PING   | EP0 OUT was pinged and it NAK'd            |

| 20       | 4C            | EP1PING   | EP1 OUT was pinged and it NAK'd            |

| 21       | 50            | EP2PING   | EP2 OUT was pinged and it NAK'd            |

| 22       | 54            | EP4PING   | EP4 OUT was pinged and it NAK'd            |

| 23       | 58            | EP6PING   | EP6 OUT was pinged and it NAK'd            |

| 24       | 5C            | EP8PING   | EP8 OUT was pinged and it NAK'd            |

| 25       | 60            | ERRLIMIT  | Bus errors exceeded the programmed limit   |

| 26       | 64            | _         |                                            |

| 27       | 68            | _         | Reserved                                   |

| 28       | 6C            | _         | Reserved                                   |

| 29       | 70            | EP2ISOERR | ISO EP2 OUT PID sequence error             |

| 30       | 74            | EP4ISOERR | ISO EP4 OUT PID sequence error             |

| 31       | 78            | EP6ISOERR | ISO EP6 OUT PID sequence error             |

| 32       | 7C            | EP8ISOERR | ISO EP8 OUT PID sequence error             |

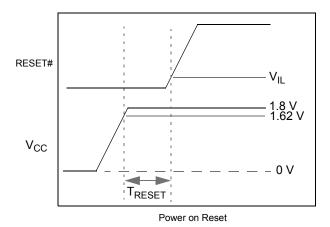

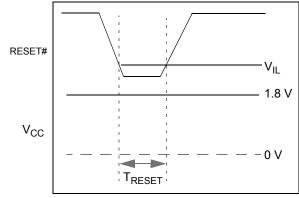

Figure 2. Reset Timing Plots

Powered Reset

#### Reset and Wakeup

The reset and wakeup pins are described in detail in this section.

#### Reset Pin

The input pin, RESET#, resets the FX2LP18 when asserted. This pin has hysteresis and is active LOW. When a crystal is used with the CY7C68053, the reset period must allow for the stabilization of the crystal and the PLL. This reset period must be approximately 5 ms after VCC has reached 3.0 V. If the crystal input pin is driven by a clock signal the internal PLL stabilizes in 200  $\mu s$  after  $V_{CC}$  has reached 3.0  $V^{[2]}$ . Figure 2 shows a power on reset condition and a reset applied during operation. A power on reset is defined as the time reset is asserted while power is being applied to the circuit. A powered reset is defined as a reset in which the FX2LP18 has previously been powered on and operating and the RESET# pin is asserted.

Cypress provides an application note which describes and recommends power on reset implementation, which can be found on the Cypress web site. For more information on reset implementation for the MoBL-USB family of products, visit the Cypress web site at <a href="http://www.cypress.com">http://www.cypress.com</a>.

**Table 3. Reset Timing Values**

| Condition                          | T <sub>RESET</sub>            |

|------------------------------------|-------------------------------|

| Power on reset with crystal        | 5 ms                          |

| Power on reset with external clock | 200 μs + clock stability time |

| Powered reset                      | 200 μs                        |

### Wakeup Pins

The 8051 puts itself and the rest of the chip into a power-down mode by setting PCON.0 = 1. This stops the oscillator and PLL. When WAKEUP is asserted by external logic, the oscillator restarts, after the PLL stabilizes, and then the 8051 receives a wakeup interrupt. This applies whether or not FX2LP18 is connected to the USB.

The FX2LP18 exits the power down (USB suspend) state using one of the following methods:

- USB bus activity (if D+/D- lines are left floating, noise on these lines may indicate activity to the FX2LP18 and initiate a wakeup)

- External logic asserts the WAKEUP pin

- External logic asserts the PA3/WU2 pin

The second wakeup pin, WU2, can also be configured as a general purpose I/O pin. This allows a simple external R-C network to be used as a periodic wakeup source. Note that WAKEUP is active LOW by default.

#### Lowering Suspend Current

Good design practices for CMOS circuits dictate that any unused input pins must not be floating between  $V_{IL}$  and  $V_{IH}$ . Floating input pins will not damage the chip, but can substantially increase suspend current. To achieve the lowest suspend current, configure unused port pins as outputs. Connect unused input pins to ground. Some examples of pins that need attention during suspend are:

- Port pins. For Port A, B, D pins, take extra care in shared bus situations.

- $\square$  Connect completely unused pins to  $V_{CC\_IO}$  or GND.

- □ In a single-master system, the firmware must output enable all the port pins and drive them high or low, before FX2LP18 enters the suspend state.

- □ In a multi-master system (FX2LP18 and another processor sharing a common data bus), when FX2LP18 is suspended, the external master must drive the pins high or low. The external master must not let the pins float.

- CLKOUT. If CLKOUT is not used, it must be tri-stated during normal operation, but driven during suspend.

- IFCLK, RDY0, RDY1. These pins must be pulled to V<sub>CC\_IO</sub> or GND or driven by another chip.

- CTL0-2. If tri-stated via GPIFIDLECTL, these pins must be pulled to V<sub>CC IO</sub> or GND or driven by another chip.

- RESET#, WAKEUP#. These pins must be pulled to V<sub>CC\_IO</sub> or GND or driven by another chip during suspend.

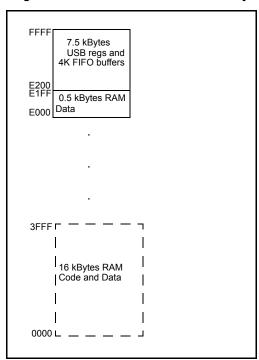

Figure 3. FX2LP18 Internal Code Memory

#### Note

<sup>2.</sup> If the external clock is powered at the same time as the CY7C680xx and has a stabilization wait period, it must be added to the 200 µs.

### Program/Data RAM

This section describes the FX2LP18 RAM.

#### Size

The FX2LP18 has 16 kBytes of internal program/data RAM. No USB control registers appear in this space.

Memory maps are shown in Figure 3 and Figure 4.

### Internal Code Memory

This mode implements the internal 16-kByte block of RAM (starting at 0) as combined code and data memory. Only the **internal** 16 kBytes and **scratch pad** 0.5 kBytes RAM spaces have the following access:

- USB download

- USB upload

- Setup data pointer

- I<sup>2</sup>C interface boot load

### Register Addresses

Figure 4. Register Address Memory

| FFFF         | 4 kBytes EP2-EP8<br>buffers<br>(8 x 512) |

|--------------|------------------------------------------|

| F000<br>EFFF |                                          |

| E800         | 2 kBytes RESERVED                        |

| E7FF<br>E7C0 | 64 Bytes EP1IN                           |

| E7BF<br>E780 | 64 Bytes EP1OUT                          |

| E77F<br>E740 | 64 Bytes EP0 IN/OUT                      |

| E73F<br>E700 | 64 Bytes RESERVED                        |

| E6FF<br>E500 | 8051 Addressable Registers (512)         |

| E4FF<br>E480 | Reserved (128)                           |

| E47F<br>E400 | 128 Bytes GPIF Waveforms                 |

| E3FF<br>E200 | Reserved (512)                           |

| E1FF         |                                          |

|              | 512 Bytes                                |

| E000         | 8051 xdata RAM                           |

### **Endpoint RAM**

This section describes the FX2LP18 Endpoint RAM.

#### Size

- 3 × 64 bytes (Endpoints 0, 1)

- 8 × 512 bytes (Endpoints 2, 4, 6, 8)

#### Organization

- EP0

- Bidirectional endpoint zero, 64-byte buffer

- EP1IN, EP1OUT

- 64-byte buffers: bulk or interrupt

- EP2, 4, 6, 8

- Eight 512-byte buffers: bulk, interrupt, or isochronous. EP4 and EP8 can be double buffered, while EP2 and 6 can be double, triple, or quad buffered. For high speed endpoint configuration options, see Figure 5.

#### Setup Data Buffer

A separate 8-byte buffer at 0xE6B8-0xE6BF holds the setup data from a CONTROL transfer.

### Endpoint Configurations (High Speed Mode)

Endpoints 0 and 1 are the same for every configuration. Endpoint 0 is the only CONTROL endpoint, and endpoint 1 can be either BULK or INTERRUPT. The endpoint buffers can be configured in any one of the 12 configurations shown in the vertical columns of Figure 5. When operating in full speed BULK mode only the first 64 bytes of each buffer are used. For example, in high speed the maximum packet size is 512 bytes, but in full speed it is 64 bytes. Even though a buffer is configured to be a 512 byte buffer, in full speed only the first 64 bytes are used. The unused endpoint buffer space is not available for other operations. An example endpoint configuration is:

EP2-1024 double buffered; EP6-512 quad buffered (column 8).

EP0 IN&OUT 64 64 64 64 64 64 EP1 IN 64 64 64 64 64 EP1 OUT 64 | 64 | 64 64 64

Figure 5. Endpoint Configuration

Default Full Speed Alternate Settings

Table 4. Default Full Speed Alternate Settings<sup>[3, 4]</sup>

| Alternate Setting | 0  | 1                | 2                | 3                |

|-------------------|----|------------------|------------------|------------------|

| ер0               | 64 | 64               | 64               | 64               |

| ep1out            | 0  | 64 bulk          | 64 int           | 64 int           |

| ep1in             | 0  | 64 bulk          | 64 int           | 64 int           |

| ep2               | 0  | 64 bulk out (2×) | 64 int out (2×)  | 64 iso out (2×)  |

| ep4               | 0  | 64 bulk out (2×) | 64 bulk out (2×) | 64 bulk out (2×) |

| ep6               | 0  | 64 bulk in (2×)  | 64 int in (2×)   | 64 iso in (2×)   |

| ep8               | 0  | 64 bulk in (2×)  | 64 bulk in (2×)  | 64 bulk in (2×)  |

Default High Speed Alternate Settings

Table 5. Default High Speed Alternate Settings [3, 4]

| Alternate Setting | 0  | 1                       | 2                 | 3                 |

|-------------------|----|-------------------------|-------------------|-------------------|

| ер0               | 64 | 64                      | 64                | 64                |

| ep1out            | 0  | 512 bulk <sup>[5]</sup> | 64 int            | 64 int            |

| ep1in             | 0  | 512 bulk <sup>[5]</sup> | 64 int            | 64 int            |

| ep2               | 0  | 512 bulk out (2×)       | 512 int out (2×)  | 512 iso out (2×)  |

| ep4               | 0  | 512 bulk out (2×)       | 512 bulk out (2×) | 512 bulk out (2×) |

| ep6               | 0  | 512 bulk in (2×)        | 512 int in (2×)   | 512 iso in (2×)   |

| ep8               | 0  | 512 bulk in (2×)        | 512 bulk in (2×)  | 512 bulk in (2×)  |

#### Notes

- 3. '0' means 'not implemented.'

- '2×' means 'double buffered.'

- 5. Even though these buffers are 64 bytes, they are reported as 512 for USB 2.0 compliance. Nnever transfer packets larger than 64 bytes to EP1.

### **External FIFO Interface**

The architecture, control signals, and clock rates are presented in this section.

#### Architecture

The FX2LP18 slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories and are controlled by FIFO control signals (such as IFCLK, SLCS#, SLRD, SLWR, SLOE, PKTEND, and flags).

In operation, some of the eight RAM blocks fill or empty from the SIE while the others are connected to the I/O transfer logic. The transfer logic takes two forms: the GPIF for internally generated control signals or the slave FIFO interface for externally controlled transfers.

#### Master/Slave Control Signals

The FX2LP18 endpoint FIFOs are implemented as eight physically distinct 256x16 RAM blocks. The 8051/SIE can switch any of the RAM blocks between two domains, the USB (SIE) domain and the 8051-I/O Unit domain. This switching is instantaneous, giving zero transfer time between 'USB FIFOs' and 'Slave FIFOs'. Because they are physically the same memory, no bytes are actually transferred between buffers.

At any given time, some RAM blocks are filling and emptying with USB data under SIE control, while other RAM blocks are available to the 8051, the I/O control unit, or both. The RAM blocks operate as single port in the USB domain, and dual port in the 8051-I/O domain. The blocks can be configured as single, double, triple, or quad buffered as previously shown.

The I/O control unit implements either an internal master (M for master) or external master (S for Slave) interface.

In Master (M) mode, the GPIF internally controls FIFOADR[1:0] to select a FIFO. The two ready (RDY) pins can be used as flag inputs from an external FIFO or other logic. The GPIF can be run from either an internally derived clock or externally supplied clock (IFCLK), at a rate that transfers data up to 96 megabytes/s (48 MHz IFCLK with 16-bit interface).

In Slave (S) mode, the FX2LP18 accepts either an internally derived clock or externally supplied clock (IFCLK, maximum frequency 48 MHz) and SLCS#, SLRD, SLWR, SLOE, PKTEND signals from external logic. When using an external IFCLK, the external clock must be present before switching to the external clock with the IFCLKSRC bit. Each endpoint can individually be selected for byte or word operation by an internal configuration bit, and a Slave FIFO Output Enable signal (SLOE) enables data of the selected width. External logic must insure that the output enable signal is inactive when writing data to a slave FIFO. The slave interface can also operate asynchronously, where the SLRD and SLWR signals act directly as strobes, rather than a clock qualifier as in synchronous mode. The signals SLRD, SLWR, SLOE, and PKTEND are gated by the signal SLCS#.

#### GPIF and FIFO Clock Rates

An 8051 register bit selects one of two frequencies for the internally supplied interface clock: 30 MHz and 48 MHz. Alternatively, an externally supplied clock of 5 MHz–48 MHz feeding the IFCLK pin can be used as the interface clock. IFCLK can be configured to function as an output clock when the GPIF and FIFOs are internally clocked. An output enable bit in the IFCONFIG register turns this clock output off. Another bit within the IFCONFIG register inverts the IFCLK signal whether internally or externally sourced.

#### **GPIF**

The GPIF is a flexible 8- or 16-bit parallel interface driven by a user programmable finite state machine. It allows the CY7C68053 to perform local bus mastering, and can implement a wide variety of protocols such as ATA interface, parallel printer port, and Utopia.

The GPIF has three programmable control outputs (CTL), and two general purpose ready inputs. The data bus width can be 8 or 16 bits. Each GPIF vector defines the state of the control outputs, and determines what state a ready input (or multiple inputs) must be before proceeding. The GPIF vector can be programmed to advance a FIFO to the next data value, advance an address, and so on. A sequence of the GPIF vectors makes up a single waveform that is executed to perform the desired data move between the FX2LP18 and the external device.

#### Three Control OUT Signals

The 56-pin package brings out three of these signals, CTL0–CTL2. The 8051 programs the GPIF unit to define the CTL waveforms. CTLx waveform edges can be programmed to make transitions as fast as once per clock cycle (20.8 ns using a 48 MHz clock).

#### Two Ready IN Signals

The FX2LP18 package brings out all two Ready inputs (RDY0–RDY1). The 8051 programs the GPIF unit to test the RDY pins for GPIF branching.

#### Long Transfer Mode

In master mode, the 8051 appropriately sets GPIF transaction count registers (GPIFTCB3, GPIFTCB2, GPIFTCB1, or GPIFTCB0) for unattended transfers of up to  $2^{32}$  transactions. The GPIF automatically throttles data flow to prevent under or overflow until the full number of requested transactions complete. The GPIF decrements the value in these registers to represent the current status of the transaction.

### ECC Generation<sup>[6]</sup>

The MoBL-USB can calculate Error Correcting Codes (ECCs) on data that passes across its GPIF or Slave FIFO interfaces. There are two ECC configurations: two ECCs, each calculated over 256 bytes (SmartMedia Standard) and one ECC calculated over 512 bytes.

The ECC can correct any 1-bit error or detect any 2-bit error.

#### ECC Implementation

The two ECC configurations are selected by the ECCM bit.

#### ECCM = 0

Two 3-byte ECCs are each calculated over a 256-byte block of data. This configuration conforms to the SmartMedia Standard.

This configuration writes any value to ECCRESET, then passes data across the GPIF or Slave FIFO interface. The ECC for the first 256 bytes of data is calculated and stored in ECC1. The ECC for the next 256 bytes is stored in ECC2. After the second ECC is calculated, the values in the ECCx registers do not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

### ECCM = 1

One 3-byte ECC is calculated over a 512-byte block of data.

This configuration writes any value to ECCRESET then passes data across the GPIF or Slave FIFO interface. The ECC for the first 512 bytes of data is calculated and stored in ECC1; ECC2 is unused. After the ECC is calculated, the value in ECC1 does not change until ECCRESET is written again, even if more data is subsequently passed across the interface.

#### **USB Uploads and Downloads**

The core has the ability to directly edit the data contents of the internal 16-kByte RAM and of the internal 512-byte scratch pad RAM using a vendor-specific command. This capability is normally used when 'soft' downloading user code and is available only to and from internal RAM, only when the 8051 is held in reset. The available RAM spaces are 16 kBytes from 0x0000–0x3FFF (code/data) and 512 bytes from 0xE000–0xE1FF (scratch pad data RAM)<sup>[7]</sup>.

### **Autopointer Access**

FX2LP18 provides two identical autopointers. They are similar to the internal 8051 data pointers, but with an additional feature: they can optionally increment after every memory access. The autopointers are available in external FX2LP18 registers, under control of a mode bit (AUTOPTRSET-UP.0). Using the external FX2LP18 autopointer access (at 0xE67B – 0xE67C) allows the autopointer to access all RAM. Also, the autopointers can point to any FX2LP18 register or endpoint buffer space.

### I<sup>2</sup>C Controller

FX2LP18 has one I<sup>2</sup>C port that is driven by two internal controllers. One controller automatically operates at boot time to load the VID/PID/DID, configuration byte, and firmware. The second controller is used by the 8051, once running, to control external I<sup>2</sup>C devices. The I<sup>2</sup>C port operates in master mode only.

#### I<sup>2</sup>C Port Pins

The  $\rm I^2C$  pins SCL and SDA must have external 2.2K ohm pull up resistors even if no EEPROM is connected to the FX2LP18. The value of the pull up resistors required may vary, depending on the combination of  $\rm V_{CC\_IO}$  and the supply used for the EEPROM. The pull up resistors used must be such that when the EEPROM pulls SDA low, the voltage level meets the  $\rm V_{IL}$  specification of the FX2LP18. For example, if the EEPROM runs off a 3.3 V supply and  $\rm V_{CC\_IO}$  is 1.8 V, the pull up resistors recommended are 10K ohm. This requirement may also vary depending on the devices being run on the  $\rm I^2C$  pins. Refer to the  $\rm I^2C$  specifications for details.

External EEPROM device address pins must be configured properly. See Table 6 for configuring the device address pins.

If no EEPROM is connected to the  $I^2C$  port, EEPROM emulation is required by an external processor. This is because the FX2LP18 comes out of reset with the DISCON bit set, so the device will not enumerate without an EEPROM (C2 load) or EEPROM emulation.

Table 6. Strap Boot EEPROM Address Lines to these Values

| Bytes | Example EEPROM        | A2  | A1  | A0  |

|-------|-----------------------|-----|-----|-----|

| 16    | 24AA00 <sup>[8]</sup> | N/A | N/A | N/A |

| 128   | 24AA01                | 0   | 0   | 0   |

| 256   | 24AA02                | 0   | 0   | 0   |

| 4K    | 24AA32                | 0   | 0   | 1   |

| 8K    | 24AA64                | 0   | 0   | 1   |

| 16K   | 24AA128               | 0   | 0   | 1   |

### I<sup>2</sup>C Interface Boot Load Access

At power on reset the I<sup>2</sup>C interface boot loader loads the VID/PID/DID and configuration bytes and up to 16 kBytes of program/data. The available RAM spaces are 16 kBytes from 0x0000–0x3FFF and 512 bytes from 0xE000–0xE1FF. The 8051 is reset. I<sup>2</sup>C interface boot loads only occur after power on reset.

#### I<sup>2</sup>C Interface General Purpose Access

The 8051 can control peripherals connected to the I<sup>2</sup>C bus using the I2CTL and I2DAT registers. FX2LP18 provides I<sup>2</sup>C master control only, it is never an I<sup>2</sup>C slave.

#### Notes

- 6. To use the ECC logic, the GPIF or Slave FIFO interface must be configured for byte-wide operation.

- After the data is downloaded from the host, a 'loader' can execute from internal RAM in order to transfer downloaded data to external memory.

- 8. This EEPROM does not have address pins.

### **Pin Assignments**

Figure 6 identifies all signals for the package. It is followed by the pin diagram. Three modes are available: Port, GPIF master, and Slave FIFO. These modes define the signals on the right edge of the diagram. The 8051 selects the interface mode using the IFCONFIG[1:0] register bits. Port mode is the power on default configuration.

Figure 6. Signals Port **GPIF Master** Slave FIFO PD7 ⇒ FD[14] ⇔ FC: PD6 PD5 FD[13] PD4 ⇔ FD[11] ⇔ FD[11] PD3 PD2 PD1 PD0 PB7 PB6 PB5 FD[5] ← FD[3] ← FD[4] PB4 **XTALIN** RDY1  $\rightarrow$  FD[3] **XTALOUT** PB3  $\rightarrow$  FD[2] RESET# PB2 CTL0> <sup>→</sup> FD[1] WAKEUP# PB1 CTL1 PB0 FD[0] CTL2 SCL `\_ SLRD ← SLWR SDA INT0#/PA0 INT1#/PA1

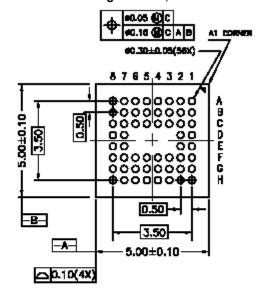

Figure 7. CY7C68053 56-pin VFBGA Pin Assignment - Top View

### CY7C68053 Pin Descriptions

## Table 7. FX2LP18 Pin Descriptions $^{[9]}$

| 56 VFBGA | Name             | Туре   | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------|------------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2D       | AV <sub>CC</sub> | Power  | N/A        | Analog VCC. Connect this pin to 3.3 V power source. This signal provides power to the analog section of the chip. Provide an appropriate bulk/bypass capacitance for this supply rail.                                                                                                                                                                                                                                                                  |

| 1D       | AV <sub>CC</sub> | Power  | N/A        | <b>Analog VCC</b> . Connect this pin to 3.3 V power source. This signal provides power to the analog section of the chip.                                                                                                                                                                                                                                                                                                                               |

| 2F       | AGND             | Ground | N/A        | Analog Ground. Connect this pin to ground with as short a path as possible.                                                                                                                                                                                                                                                                                                                                                                             |

| 1F       | AGND             | Ground | N/A        | Analog Ground. Connect to this pin ground with as short a path as possible.                                                                                                                                                                                                                                                                                                                                                                             |

| 1E       | DMINUS           | I/O/Z  | Z          | USB D- Signal. Connect this pin to the USB D- signal.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2E       | DPLUS            | I/O/Z  | Z          | USB D+ Signal. Connect this pin to the USB D+ signal.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8B       | RESET#           | Input  | N/A        | <b>Active LOW Reset</b> . This pin resets the entire chip. See Reset and Wakeup on page 8 for details.                                                                                                                                                                                                                                                                                                                                                  |

| 1C       | XTALIN           | Input  | N/A        | <b>Crystal Input</b> . Connect this signal to a 24 MHz parallel resonant, fundamental mode crystal and load capacitor to GND. It is also correct to drive XTALIN with an external 24 MHz square wave derived from another clock source.                                                                                                                                                                                                                 |

| 2C       | XTALOUT          | Output | N/A        | Crystal Output. Connect this signal to a 24 MHz parallel resonant, fundamental mode crystal and load capacitor to GND.  If an external clock is used to drive XTALIN, leave this pin open.                                                                                                                                                                                                                                                              |

| 2B       | CLKOUT           | O/Z    | 12 MHz     | <b>CLKOUT.</b> 12, 24, or 48 MHz clock, phase locked to the 24 MHz input clock. The 8051 defaults to 12 MHz operation. The 8051 may tri-state this output by setting CPUCS.1 = 1.                                                                                                                                                                                                                                                                       |

| Port A   | •                | 1      |            |                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8G       | PA0 or<br>INT0#  | I/O/Z  | I<br>(PA0) | Multiplexed pin whose function is selected by PORTACFG.0 <b>PA0</b> is a bidirectional I/O port pin. <b>INT0#</b> is the active LOW 8051 INT0 interrupt input signal, which is either edge triggered (IT0 = 1) or level triggered (IT0 = 0).                                                                                                                                                                                                            |

| 6G       | PA1 or<br>INT1#  | I/O/Z  | I<br>(PA1) | Multiplexed pin whose function is selected by PORTACFG.1 <b>PA1</b> is a bidirectional I/O port pin. <b>INT1#</b> is the active LOW 8051 INT1 interrupt input signal, which is either edge triggered (IT1 = 1) or level triggered (IT1 = 0).                                                                                                                                                                                                            |

| 8F       | PA2 or<br>SLOE   | I/O/Z  | I<br>(PA2) | Multiplexed pin whose function is selected by two bits: IFCONFIG[1:0]. <b>PA2</b> is a bidirectional I/O port pin. <b>SLOE</b> is an input-only output enable with programmable polarity (FIFOPIN-POLAR.4) for the slave FIFO's connected to FD[7:0] or FD[15:0].                                                                                                                                                                                       |

| 7F       | PA3 or<br>WU2    | I/O/Z  | I<br>(PA3) | Multiplexed pin whose function is selected by: WAKEUP.7 and OEA.3  PA3 is a bidirectional I/O port pin.  WU2 is an alternate source for USB Wakeup, enabled by WU2EN bit (WAKEUP.1) and polarity set by WU2POL (WAKEUP.4). If the 8051 is in suspend and WU2EN = 1, a transition on this pin starts up the oscillator and interrupts the 8051 to allow it to exit the suspend mode. Asserting this pin inhibits the chip from suspending, if WU2EN = 1. |

#### Note

Do not leave unused inputs floating. Tie either HIGH or LOW as appropriate. Only pull outputs up or down to ensure signals at power up and in standby. Do not drive

any pins while the device is powered down.

Table 7. FX2LP18 Pin Descriptions<sup>[9]</sup> (continued)

| 56 VFBGA | Name                        | Type  | Default    | Description                                                                                                                                                                                                                                            |

|----------|-----------------------------|-------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6F       | PA4 or<br>FIFOADR0          | I/O/Z | I<br>(PA4) | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PA4</b> is a bidirectional I/O port pin. <b>FIFOADR0</b> is an input-only address select for the slave FIFOs connected to FD[7:0] or FD[15:0].                                         |

| 8C       | PA5 or<br>FIFOADR1          | I/O/Z | I<br>(PA5) | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PA5</b> is a bidirectional I/O port pin. <b>FIFOADR1</b> is an input-only address select for the slave FIFOs connected to FD[7:0] or FD[15:0].                                         |

| 7C       | PA6 or<br>PKTEND            | I/O/Z | I<br>(PA6) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] bits. <b>PA6</b> is a bidirectional I/O port pin. <b>PKTEND</b> is an input that commits the FIFO packet data to the endpoint and whose polarity is programmable using FIFOPINPOLAR.5. |

| 6C       | PA7 or<br>FLAGD or<br>SLCS# | I/O/Z | I<br>(PA7) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and PORTACFG.7 bits.  PA7 is a bidirectional I/O port pin.  FLAGD is a programmable slave FIFO output status flag signal.  SLCS# gates all other slave FIFO enable/strobes             |

| Port B   |                             | •     | •          |                                                                                                                                                                                                                                                        |

| 3H       | PB0 or<br>FD[0]             | I/O/Z | (PB0)      | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PB0</b> is a bidirectional I/O port pin. <b>FD[0]</b> is the bidirectional FIFO/GPIF data bus.                                                                                         |

| 4F       | PB1 or<br>FD[1]             | I/O/Z | I<br>(PB1) | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PB1</b> is a bidirectional I/O port pin. <b>FD[1]</b> is the bidirectional FIFO/GPIF data bus.                                                                                         |

| 4H       | PB2 or<br>FD[2]             | I/O/Z | l<br>(PB2) | Multiplexed pin whose function is selected by IFCONFIG[1:0].  PB2 is a bidirectional I/O port pin.  FD[2] is the bidirectional FIFO/GPIF data bus.                                                                                                     |

| 4G       | PB3 or<br>FD[3]             | I/O/Z | (PB3)      | Multiplexed pin whose function is selected by IFCONFIG[1:0].  PB3 is a bidirectional I/O port pin.  FD[3] is the bidirectional FIFO/GPIF data bus.                                                                                                     |

| 5H       | PB4 or<br>FD[4]             | I/O/Z | I<br>(PB4) | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PB4</b> is a bidirectional I/O port pin. <b>FD[4]</b> is the bidirectional FIFO/GPIF data bus.                                                                                         |

| 5G       | PB5 or<br>FD[5]             | I/O/Z | I<br>(PB5) | Multiplexed pin whose function is selected by IFCONFIG[1:0].  PB5 is a bidirectional I/O port pin.  FD[5] is the bidirectional FIFO/GPIF data bus.                                                                                                     |

| 5F       | PB6 or<br>FD[6]             | I/O/Z | (PB6)      | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>PB6</b> is a bidirectional I/O port pin. <b>FD[6]</b> is the bidirectional FIFO/GPIF data bus.                                                                                         |

| 6H       | PB7 or<br>FD[7]             | I/O/Z | (PB7)      | Multiplexed pin whose function is selected IFCONFIG[1:0].  PB7 is a bidirectional I/O port pin.  FD[7] is the bidirectional FIFO/GPIF data bus.                                                                                                        |

Table 7. FX2LP18 Pin Descriptions<sup>[9]</sup> (continued)

| 56 VFBGA | Name             | Type  | Default    | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|------------------|-------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PORT D   |                  |       |            | ·                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8A       | PD0 or<br>FD[8]  | I/O/Z | l<br>(PD0) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits.  FD[8] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                 |

| 7A       | PD1 or<br>FD[9]  | I/O/Z | I<br>(PD1) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits.  FD[9] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                 |

| 6B       | PD2 or<br>FD[10] | I/O/Z | I<br>(PD2) | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits.  FD[10] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                |

| 6A       | PD3 or<br>FD[11] | I/O/Z | (PD3)      | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits. <b>FD[11]</b> is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                          |

| 3B       | PD4 or<br>FD[12] | I/O/Z | (PD4)      | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits.  FD[12] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                |

| 3A       | PD5 or<br>FD[13] | I/O/Z | (PD5)      | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFI-FOCFG.0 (wordwide) bits.  FD[13] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                               |

| 3C       | PD6 or<br>FD[14] | I/O/Z | (PD6)      | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFI-FOCFG.0 (wordwide) bits.  FD[14] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                               |

| 2A       | PD7 or<br>FD[15] | I/O/Z | (PD7)      | Multiplexed pin whose function is selected by the IFCONFIG[1:0] and EPxFIFOCFG.0 (wordwide) bits.  FD[15] is the bidirectional FIFO/GPIF data bus.                                                                                                                                                                                                                                                                |

| 1A       | RDY0 or<br>SLRD  | Input | N/A        | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>RDY0</b> is a GPIF input signal. <b>SLRD</b> is the input only read strobe with programmable polarity (FIFOPIN-POLAR.3) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                                                     |

| 1B       | RDY1 or<br>SLWR  | Input | N/A        | Multiplexed pin whose function is selected by IFCONFIG[1:0]. <b>RDY1</b> is a GPIF input signal. <b>SLWR</b> is the input only write strobe with programmable polarity (FIFOPIN-POLAR.2) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                                                    |

| 7H       | CTL0 or<br>FLAGA | O/Z   | Н          | Multiplexed pin whose function is selected by IFCONFIG[1:0].  CTL0 is a GPIF control output.  FLAGA is a programmable slave FIFO output status flag signal.  Defaults to programmable for the FIFO selected by the FIFOADR[1:0] pins.                                                                                                                                                                             |

| 7G       | CTL1 or<br>FLAGB | O/Z   | Н          | Multiplexed pin whose function is selected by IFCONFIG[1:0].  CTL1 is a GPIF control output.  FLAGB is a programmable slave FIFO output status flag signal.  Defaults to FULL for the FIFO selected by the FIFOADR[1:0] pins.                                                                                                                                                                                     |

| 8H       | CTL2 or<br>FLAGC | O/Z   | Н          | Multiplexed pin whose function is selected IFCONFIG[1:0].  CTL2 is a GPIF control output.  FLAGC is a programmable slave FIFO output status flag signal.  Defaults to EMPTY for the FIFO selected by the FIFOADR[1:0] pins.                                                                                                                                                                                       |

| 2G       | IFCLK            | I/O/Z | Z          | Interface clock, used to synchronous clock data into or out of the slave FIFOs. IFCLK also serves as a timing reference for all slave FIFO control signals and GPIF. When internal clocking is used (IFCONFIG.7 = 1) the IFCLK pin can be configured to output 30 or 48 MHz by bits IFCONFIG.5 and IFCONFIG.6. IFCLK may be inverted, whether internally or externally sourced, by setting the bit IFCONFIG.4 =1. |

Table 7. FX2LP18 Pin Descriptions<sup>[9]</sup> (continued)

| 56 VFBGA | Name               | Туре   | Default | Description                                                                                                                                                                                                                                                                              |

|----------|--------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7B       | WAKEUP             | Input  | N/A     | <b>USB Wakeup</b> . If the 8051 is in suspend, asserting this pin starts up the oscillator and interrupts the 8051 to allow it to exit the suspend mode. Holding WAKEUP asserted inhibits the MoBL-USB <sup>®</sup> chip from suspending. This pin has programmable polarity (WAKEUP.4). |

| 3F       | SCL                | OD     | Z       | Clock for the I <sup>2</sup> C interface. Connect to V <sub>CC_IO</sub> or V <sub>CC</sub> with a 2.2K–10K pull up resistor. (An I <sup>2</sup> C peripheral is required.)                                                                                                               |

| 3G       | SDA                | OD     | Z       | <b>Data</b> for the I <sup>2</sup> C interface. Connect to V <sub>CC_IO</sub> or V <sub>CC</sub> with a 2.2K–10K pull up resistor. (An I <sup>2</sup> C peripheral is required.)                                                                                                         |

|          | I                  | I      |         | 1400 O 1111                                                                                                                                                                                                                                                                              |

| 5A       | V <sub>CC_IO</sub> | Power  | N/A     | <b>VCC</b> . Connect this pin to 1.8V to 3.3 V power source. Provide the appropriate bulk and bypass capacitance for this supply rail.                                                                                                                                                   |

| 5B       | V <sub>CC_IO</sub> | Power  | N/A     | VCC. Connect this pin to 1.8V to 3.3 V power source.                                                                                                                                                                                                                                     |

| 7E       | V <sub>CC_IO</sub> | Power  | N/A     | VCC. Connect this pin to 1.8 V to 3.3 V power source.                                                                                                                                                                                                                                    |

| 8E       | V <sub>CC_IO</sub> | Power  | N/A     | VCC. Connect this pin to 1.8V to 3.3 V power source.                                                                                                                                                                                                                                     |

| 5C       | V <sub>CC_D</sub>  | Power  | N/A     | VCC. Connect this pin to 1.8V power source. (Supplies power to internal digital 1.8 V circuits.) Provide the appropriate bulk and bypass capacitance for this supply rail.                                                                                                               |

| 1G       | V <sub>CC_A</sub>  | Power  | N/A     | VCC. Connect this pin to 1.8V power source. (Supplies power to internal analog 1.8 V circuits.)                                                                                                                                                                                          |

| 1H       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 2H       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 4A       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 4B       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 4C       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 7D       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

| 8D       | GND                | Ground | N/A     | Ground                                                                                                                                                                                                                                                                                   |

### **Register Summary**

FX2LP18 register bit definitions are described in the MoBL-USB FX2LP18 TRM in greater detail.

Table 8. FX2LP18 Register Summary

|              | ٠.   |                                    | gister Summary                                            |          |          |          |                         |          |           |           |           |                  |          |

|--------------|------|------------------------------------|-----------------------------------------------------------|----------|----------|----------|-------------------------|----------|-----------|-----------|-----------|------------------|----------|

| Hex          | Size | Name                               | Description                                               | b7       | b6       | b5       | b4                      | b3       | b2        | b1        | b0        | Default          | Access   |

|              |      | GPIF Waveform Mem                  | ories                                                     |          |          |          |                         |          |           |           |           |                  |          |

| E400         | 128  | WAVEDATA                           | GPIF Waveform descriptor 0, 1, 2, 3 data                  | D7       | D6       | D5       | D4                      | D3       | D2        | D1        | D0        | xxxxxxx          | RW       |

| E480         | 128  | Reserved                           |                                                           |          |          |          |                         |          |           |           |           |                  |          |

|              |      | GENERAL CONFIGU                    | JRATION                                                   |          |          |          |                         |          |           |           |           |                  |          |

| E50D         |      | GPCR2                              | General Purpose Configura-<br>tion Register 2             | Reserved | Reserved | Reserved | FULL<br>SPEED_ON-<br>LY | Reserved | Reserved  | Reserved  | Reserved  | 00000000         | R        |

| E600         | 1    | CPUCS                              | CPU Control and Status                                    | 0        | 0        | PORTCSTB | CLKSPD1                 | CLKSPD0  | CLKINV    | CLKOE     | 8051RES   | 00000010         | rrbbbbbr |

| E601         | 1    | IFCONFIG                           | Interface Configuration (Ports, GPIF, Slave FIFOs)        | IFCLKSRC | 3048MHZ  | IFCLKOE  | IFCLKPOL                | ASYNC    | GSTATE    | IFCFG1    | IFCFG0    | 10000000         | RW       |

| E602         | 1    | PINFLAGSAB <sup>[10]</sup>         | Slave FIFO FLAGA and FLAGB pin configuration              | FLAGB3   | FLAGB2   | FLAGB1   | FLAGB0                  | FLAGA3   | FLAGA2    | FLAGA1    | FLAGA0    | 00000000         | RW       |

| E603         | 1    | PINFLAGSCD <sup>[10]</sup>         | Slave FIFO FLAGC and FLAGD pin configuration              | FLAGD3   | FLAGD2   | FLAGD1   | FLAGD0                  | FLAGC3   | FLAGC2    | FLAGC1    | FLAGC0    | 00000000         | RW       |

| E604         | 1    | FIFORESET <sup>[10]</sup>          | Restore FIFOs to default state                            | NAKALL   | 0        | 0        | 0                       | EP3      | EP2       | EP1       | EP0       | xxxxxxx          |          |

| E605         | 1    | BREAKPT                            | Breakpoint control                                        | 0        | 0        | 0        | 0                       | BREAK    | BPPULSE   | BPEN      | 0         | 00000000         |          |

| E606         | 1    | BPADDRH                            | Breakpoint address H                                      | A15      | A14      | A13      | A12                     | A11      | A10       | A9        | A8        | XXXXXXX          | RW       |

| E607         | 1    | BPADDRL                            | Breakpoint address L                                      | A7       | A6       | A5       | A4                      | A3       | A2        | A1        | A0        | XXXXXXX          | RW       |

| E608         | 1    | Reserved                           | Reserved                                                  | 0        | 0        | 0        | 0                       | 0        | 0         | 0         | 0         | 00000000         | rrrrrbb  |

| E609         | 1    | FIFOPINPOLAR <sup>[10]</sup>       | Slave FIFO interface pins polarity                        | 0        | 0        | PKTEND   | SLOE                    | SLRD     | SLWR      | EF        | FF        | 00000000         | rrbbbbbb |

| E60A         | 1    | REVID                              | Chip revision                                             | rv7      | rv6      | rv5      | rv4                     | rv3      | rv2       | rv1       | rv0       | RevA<br>00000001 |          |

| E60B         | 1    | REVCTL <sup>[10]</sup>             | Chip revision control                                     | 0        | 0        | 0        | 0                       | 0        | 0         | dyn_out   | enh_pkt   | 00000000         | rrrrrbb  |

| E60C         | 1    | UDMA<br>GPIFHOLDAMOUNT             | MSTB hold time                                            | 0        | 0        | 0        | 0                       | 0        | 0         | HOLDTIME1 | HOLDTIME0 | 00000000         | rrrrrbb  |

|              | 3    | Reserved                           | (for UDMA)                                                |          |          |          |                         |          |           |           |           |                  |          |

|              | 3    | ENDPOINT CONFIG                    | LIDATION                                                  |          |          |          |                         |          |           |           |           |                  |          |

|              |      |                                    | Endpoint 1-OUT                                            |          |          |          |                         |          |           |           |           |                  |          |

| E610         | 1    | EP10UTCFG                          | configuration Endpoint 1-IN                               | VALID    | 0        | TYPE1    | TYPE0                   | 0        | 0         | 0         | 0         | 10100000         |          |

| E611         | 1    | EP1INCFG                           | configuration                                             | VALID    | 0        | TYPE1    | TYPE0                   | 0        | 0         | 0         | 0         | 10100000         |          |

| E612         | 1    | EP2CFG                             | Endpoint 2 configuration                                  | VALID    | DIR      | TYPE1    | TYPE0                   | SIZE     | 0         | BUF1      | BUF0      | 10100010         |          |

| E613         | 1    | EP4CFG                             | Endpoint 4 configuration                                  | VALID    | DIR      | TYPE1    | TYPE0                   | 0        | 0         | 0         | 0         | 10100000         |          |

| E614         | 1    | EP6CFG                             | Endpoint 6 configuration                                  | VALID    | DIR      | TYPE1    | TYPE0                   | SIZE     | 0         | BUF1      | BUF0      | 11100010         |          |

| E615         | 1    | EP8CFG                             | Endpoint 8 configuration                                  | VALID    | DIR      | TYPE1    | TYPE0                   | 0        | 0         | 0         | 0         | 11100000         | bbbbrrrr |

|              | 2    | Reserved                           | F 1 : 10/01 FIFO                                          |          |          |          |                         |          |           |           |           |                  |          |

| E618         | 1    | EP2FIFOCFG <sup>[10]</sup>         | Endpoint 2/Slave FIFO configuration                       | 0        | INFM1    | OEP1     | AUTOOUT                 | AUTOIN   | ZEROLENIN | 0         | WORDWIDE  | 00000101         | rbbbbbrb |

| E619         | 1    | EP4FIFOCFG <sup>[10]</sup>         | Endpoint 4/Slave FIFO configuration Endpoint 6/Slave FIFO | 0        | INFM1    | OEP1     | AUTOOUT                 | AUTOIN   | ZEROLENIN | 0         | WORDWIDE  | 00000101         | rbbbbbrb |

| E61A         | 1    | EP8FIFOCFG <sup>[10]</sup>         | configuration Endpoint 8/Slave FIFO                       | 0        | INFM1    | OEP1     | AUTOOUT                 | AUTOIN   | ZEROLENIN | 0         | WORDWIDE  |                  |          |

| E61B<br>E61C | 1    | Reserved                           | configuration                                             | 0        | INFM1    | OEP1     | AUTOOUT                 | AUTOIN   | ZEROLENIN | 0         | WORDWIDE  | 00000101         | rbbbbbrb |

| E620         | 1    | EP2AUTOINLENH <sup>[10</sup>       | Endpoint 2 AUTOIN packet length H                         | 0        | 0        | 0        | 0                       | 0        | PL10      | PL9       | PL8       | 00000010         | rrrrrbbb |

| E621         | 1    | EP2AUTOINLENL <sup>[10]</sup>      | Endpoint 2 AUTOIN packet length L                         | PL7      | PL6      | PL5      | PL4                     | PL3      | PL2       | PL1       | PL0       | 00000000         | RW       |

| E622         | 1    | EP4AUTOIN-<br>LENH <sup>[10]</sup> | Endpoint 4 AUTOIN packet length H                         | 0        | 0        | 0        | 0                       | 0        | 0         | PL9       | PL8       | 00000010         | rrrrrbb  |

| E623         | 1    | EP4AUTOINLENL <sup>[10]</sup>      | Endpoint 4 AUTOIN packet length L                         | PL7      | PL6      | PL5      | PL4                     | PL3      | PL2       | PL1       | PL0       | 00000000         | RW       |

| E624         | 1    | EP6AUTOIN-<br>LENH <sup>[10]</sup> | Endpoint 6 AUTOIN packet length H                         | 0        | 0        | 0        | 0                       | 0        | PL10      | PL9       | PL8       | 00000010         | rrrrrbbb |