# Intelligent PCI Bus Controller

#### **Features**

- Provides an interface between the PCI Local Bus and the CPU bus

- PCI Bus Rev. 2.0 compliant

- Supports Intel® 486DX, 486DX2, 486SX, 486SL, P24T, AMD AM486 and Cyrix Cx486S2 (M6/M7) CPUs

- Interfaces with Cypress CY82C596 or CY82C297 Core Logic devices to form a complete PC solution supporting PCI, VESA, and ISA buses

- Supports 4 PCI Masters

- Supports burst mode PCI accesses to memory space

- PCI pre-read support with 4-double-word-deep FIFO, each double-word is 32 Data bits wide

- PCI post-write support with 4-double-word-deep FIFO, each double-word is 32 Data bits wide

- Synchronous/Asynchronous PCI bus support

- Standby mode slows down CPU clock

- Power management timers

- SMI generation support for Intel, AMD, Cyrix CPUs

- Provides I/O trap for peripheral device power control

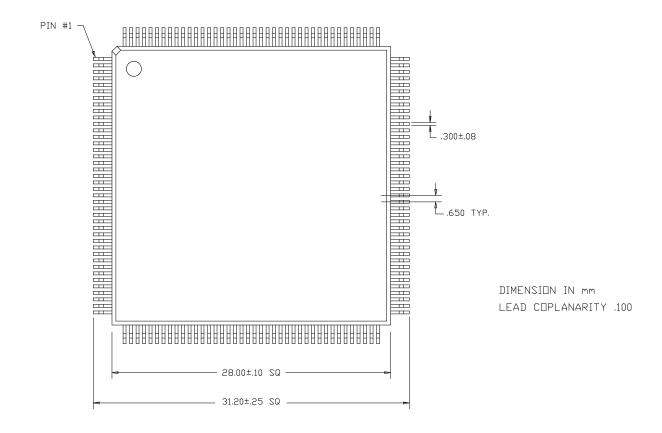

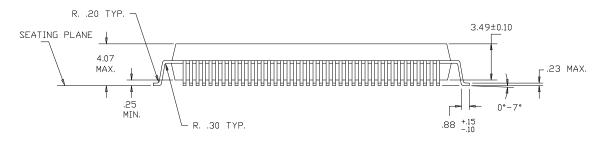

- Packaged in 160-pin PQFP

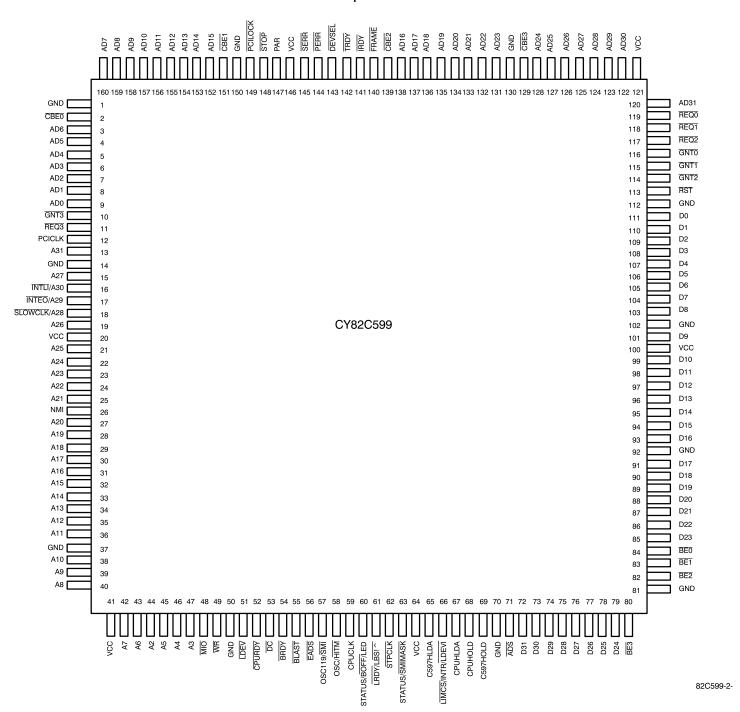

## **Pin Configurations**

#### PQFP Top View

## 1.0 Introduction

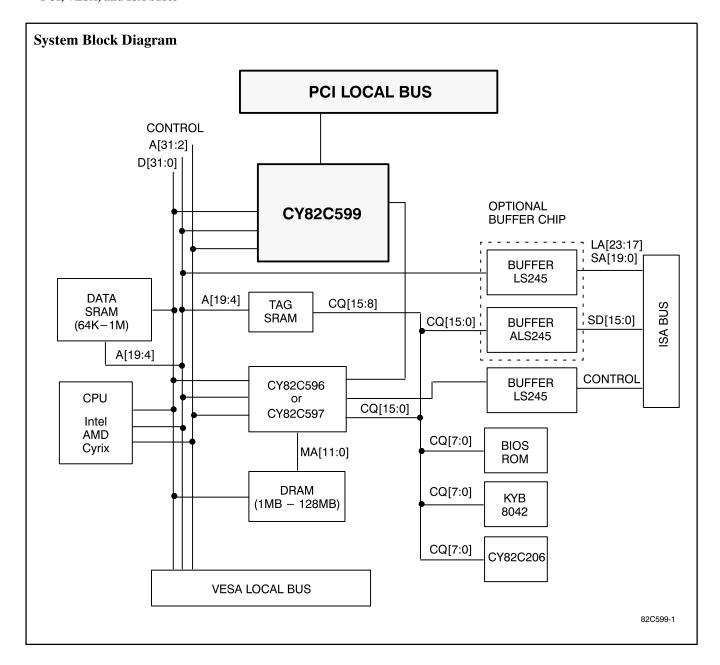

The CY82C599 Intelligent PCI Bus Interface chip is designed to eliminate the ISA Bus I/O bottleneck by providing a glueless path to the high-performance PCI Local Bus. This chip connects the PCI Bus to the VESA Bus and the CPU simultaneously, allowing system designers to take advantage of the PCI Bus's high through-put while maintaining access to the large selection of ISA and VESA local bus expansion cards.

No TTL components are required to connect the CY82C599 to the PCI Bus. However, in applications with heavy loading on the Address/Data lines, buffers may be necessary to distribute the load. The CY82C599 simplifies the interface design by providing buffer control signals.

The CY82C599, along with the CY82C596 PC/AT Core Logic chip or the CY82C597 Green PC/AT Core Logic chip, implements a sophisticated and cost-effective 486-based PCI/VESA/ISA system.

#### 2.0 Functional Overview

The CY82C599 provides the required functions in PCI Specification Revision 2.0 including bus arbitration, bus grant, master support, bus lock support and interrupt support. It supports all the CPU and bus commands except INTA and dual address cycles. INTA cycles are routed to the interrupt controller on the ISA bus. Dual address cycles are reserved for 64-bit addressing and they are ignored by the CY82C599.

The CY82C599 supports bursting in both CPU mode and PCI master mode. It also supports post-write buffering and pre-read buffering with a 4-word-deep bidirectional FIFO. Each word in the FIFO is 64 bits wide (32-bits address, 32-bits data). In addition, fast back-to-back write cycles are supported to enhance system performance.

The central arbiter of the CY82C599 supports two levels of arbitration. The first level arbiter arbitrates bus requests between the VESA and the PCI Buses. The second level arbiter handles bus requests from four PCI master channels. Both levels of arbitration can have either fixed or rotating priority. Optionally, a hold request on the ISA bus (for a refresh, DMA/MASTER, or VESA transactions) can prematurely terminate a PCI transaction.

The CY82C599 has built-in interrupt logic that can convert a level-sensitive interrupt signal to an edge-triggered interrupt signal. This feature enables the usage of popular interrupt controllers such as the 8259 or 83C206.

The preferred PCI Configuration Mechanism #1 is supported in the CY82C599 that allows PCI configuration cycles to be generated by software. To support hierarchical PCI buses, both Type 0 and Type 1 configuration access are implemented. BIOS support is available from AMI & AWARD.

#### 3.0 PCI Bus

The purpose of this section is to give an overview of PCI, the motivation behind it, and its features. Basic transfers and rules are discussed. How the CY82C599 handles inter—bus transfers is discussed in later sections. For a detailed description of the PCI bus, all of the rules and requirements, see the PCI Specification 2.0

The PCI Bus was defined in order to satisfy the growing need for a standardized high-speed local bus that is independent of the processors, operating system, and CPU bus speed. New generations of computers incorporating I/O intensive software will require bandwidth that cannot be satisfied with the

traditional I/O architectures. The PCI specification 2.0 addresses these requirements and provides an upgrade path for future requirements. Some of the PCI features include:

- Processor Independent

- Multiplexed, Burst Mode Operation

- 120 MBytes/sec usable throughput (32-bit data path)

- Three physical address spaces

- Memory

- I/O

- Configuration

- Hidden Arbitration

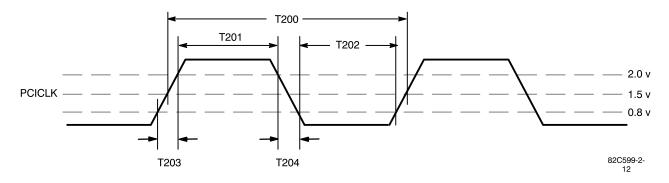

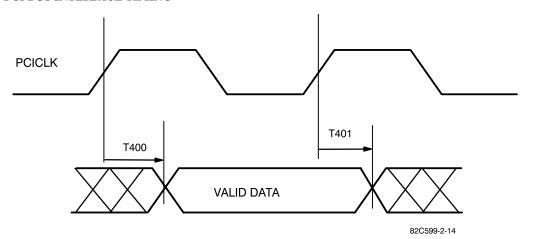

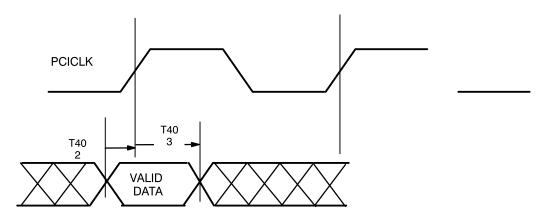

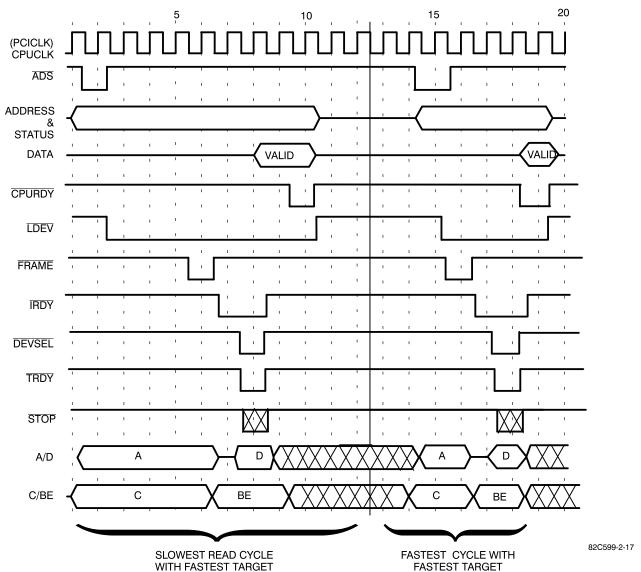

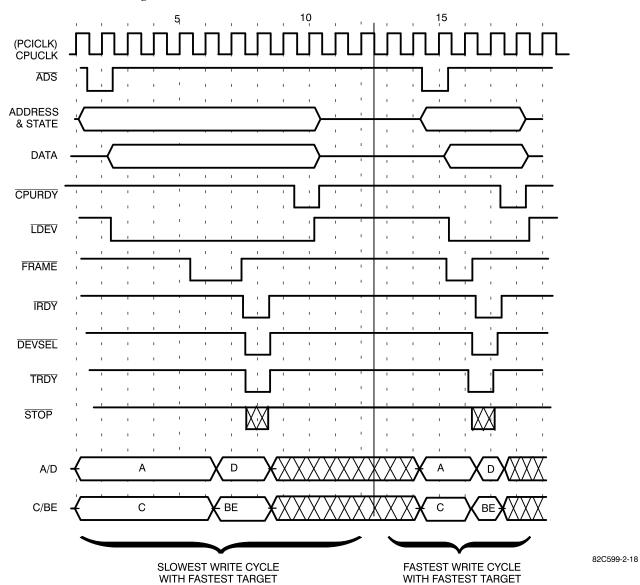

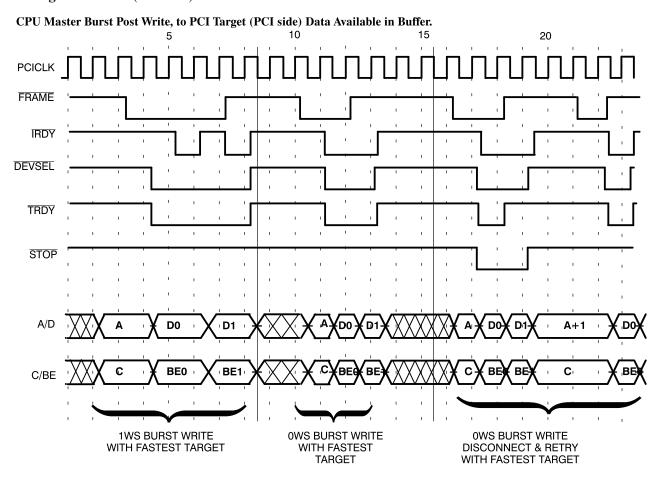

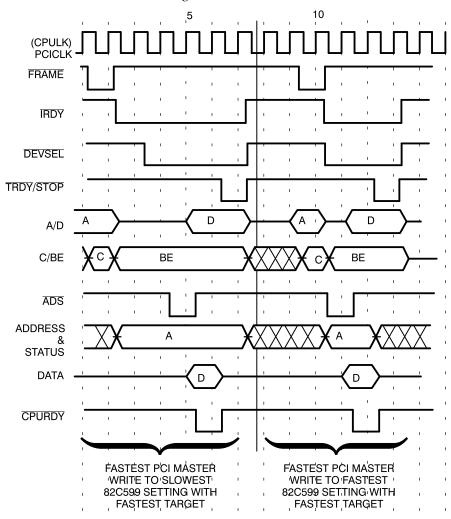

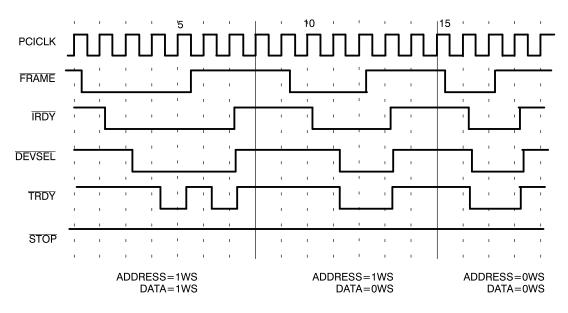

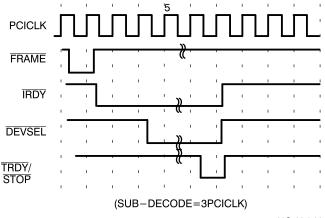

PCI is defined as a synchronous bus that can operate from 0 to 33MHz. All transfers take place on the rising edge of the clock (PCICLK). The basic data transfer in PCI is a burst. A burst transfer consists of an address phase, followed by one or more data phases. The address phase is defined as the first rising edge of the clock where FRAME is asserted (LOW). During the Address phase, the Master (also referred to as the initiator) asserts the appropriate address on the address/data lines (AD[31:0]) while also asserting the appropriate command on the Command/Byte Enable C/BE[3:0] lines. With the information transferred during the address phase, all PCI devices, including the slave (or Target), can determine: 1) Whether the transaction falls within its designated address range, 2) The kind of transfer that will take place (e.g. a read or write to memory, I/O, or configuration space), and 3) How to respond to that particular command.

Once a device recognizes that it is the target for the transaction, it claims the transactions by asserting Device Select (DEVSEL) LOW. DEVSEL must be asserted LOW in order for any information is be transferred.

The address phase is followed by one or more data phases. Whether the initial data phase occurs on the subsequent clock edge is determined by the type of transaction and the ability of either agent to provide/accept the data within the appropriate time period. Since the address and data lines are multiplexed, a normal read operation requires a 'turn-around' cycle to avoid bus contention. During this cycle, control of the Address/Data lines is transferred from the master to the slave, who must now use these lines to drive out the requested information. During a write operation, this 'turn-around' cycle is not required since the master is providing the write data and does not have to relinquish control of the bus. PCI also allows that both the master and slave have the ability to insert wait states should either require additional cycles in order to properly participate in the transfer. This is accomplished with the Initiator Ready signal (IRDY) and the Target Ready signal (TRDY) for the Initiator Target, respectively. Either of these signals being de-asserted (HIGH) during the data phase of the transaction will insert a wait state, thereby preventing data from being transferred during that cycle. The data presented on the AD[31:0] lines is transferred during a data phase on the rising edge of the clock when ALL of the following signals are active (LOW): DEVSEL, TRDY, IRDY, and FRAME (except during the final data phase, when FRAME is HIGH, which is explained The bytes containing meaningful information are controlled by the C/BE[3:0] signals. During the data phase, these signals behave as byte enable lines.

Transactions are normally terminated by the Master by de-asserting FRAME HIGH on the clock prior to the last data

phase. By doing so, all of the agents on the bus, including the Target and the Arbiter, recognize that the current transaction is coming to an end. This advanced notice allows the Arbiter to grant ownership of the bus to the next requesting agent. This is referred to as Hidden Arbitration since no additional clock cycles are consumed. The new Master will not start to drive the bus until the current transaction is actually completed. The Target has the ability to abort the transaction prematurely should the need arise, although this is not the typical method of termination.

Arbitration in PCI is access based instead of time slot based. This is accomplished through a simple request—grant handshaking scheme through a central arbiter. Each agent has dedicated request and grant lines to the arbiter. A bus Master must request and be granted bus ownership each time a transaction is desired.

PCI defines three different physical address spaces; memory, I/O, and configuration space. Each of these address spaces has its own characteristics. Therefore, transactions to each space are handled differently, particularly in regards to AD[0:1]. The memory and I/O address spaces are customary, but the configuration address space has been defined by PCI in order to support hardware configuration.

#### 4.0 Address Space

The purpose of this section is to explain the memory and I/O address space mapping used by the CY82C599.

The CY82C599 recognizes two different physical address spaces; memory and I/O. Transactions to these two address spaces are handled differently, and therefore need to be distinguished from one another. The CY82C599 differentiates these two different type of transactions by monitoring the M/IO signal coming from the CPU bus, or the C/BE signals coming from the PCI bus. In order to recognize the destination of each transaction, each address space needs to be divided (or mapped) into the different target areas (ISA, PCI, VESA, or Local Memory). Each address map, memory and I/O, is discussed below.

## 4.1 I/O Address Space

Although the I/O address space can extend the full 32 bits (a possible 4 GB of I/O address space), x86 CPUs limit I/O transactions to the lower 64KB (0000h-FFFFh). The remaining address locations are not valid I/O address space. In addition, the lower 1KB (0000h-03FFh) of I/O space has been assigned as AT I/O space. Within the lower 1KB (AT space) resides numerous predefined I/O blocks that can be assigned to PCI or ISA/VESA through configuration registers. The remaining I/O address locations (0400h-FFFFh) can be mapped using three 100% user defined I/O blocks. The base address, block size, and bus location (e.g. PCI, VESA, or ISA) of these I/O blocks are determined by the configuration registers during boot-up (see configuration registers). If an I/O address area is excluded from the user defined blocks mentioned above, it is considered to be in an 'unknown' I/O location. 'Unknown' I/O address locations are handled on a priority basis (see the I/O access priority sections for further details). Although the PCI base address can be placed anywhere within the lower 64KB using one of the three 100% user defined I/O blocks, it is recommended that the PCI base address be placed at 8000h or above to avoid contention with VESA devices. VESA and PCI devices should never occupy the same I/O address location. Doing so will cause a bus contention condition. How the CY82C599 responds to each I/O transaction is discussed in the following sections.

#### 4.2 Memory Address Space

The CY82C599 supports up to 256MB of local memory space (128MB when used with the CY82C596/7). The full 4GB memory space can be mapped over the PCI, VESA, or ISA regions (see configuration registers). This mapping allows the CY82C599 to determine the destination of the transaction and respond appropriately. A minimum of 64KB (0000h-FFFFh) of memory address space is reserved for system usage. Up to 256MB can be defined as local memory. The Local memory ending address is user defined through configuration registers 20h and 21h. The CY82C599 also supports 4 user defined memory block. Blocks 0 & 1 can be mapped over the entire address space by defining the base address, block size, and bus location. Blocks 2 & 3 are simply enabled/disabled (through register 46h) and can only be mapped to PCI. With these memory blocks the user can define the memory map of the system. As with I/O address space, some memory areas can be excluded from the memory map, and are therefore defined as 'unknown'. These 'unknown' locations are handled on a priority basis that is discussed in memory priority sections. How the CY82C599 responds to each transaction is discussed in each of the following sections.

#### 4.3 PCI Configuration Space

The CY82C599 supports the preferred PCI Configuration Mechanism #1 that allows PCI configuration cycles to be generated by software. Both Type 0 and Type 1 configurations accesses are also supported. All required fields within the Configuration Header Space are also supported.

#### 5.0 Device Operation

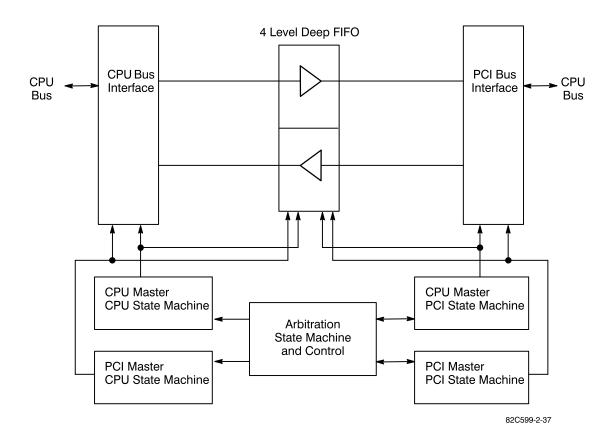

The purpose of this section is to describe the basic operation of the CY82C599 Intelligent PCI Bus Interface. The CY82C599 functional block diagram is shown in the functional block diagram. The core functionality of the CY82C599 is controlled by the Central Arbiter and the surrounding four state machines. These four state machines communicate with one another in order to properly conduct and synchronize all transactions. Supporting functions are conducted through control logic, interface and synchronization logic (PCI and CPU buses), configuration registers, and an internal bidirectional FIFO. The following sections describes the functionality of each of these major blocks within the CY82C599.

#### **5.1 Central Arbiter**

The Central Arbiter is responsible for delegating control of the CY82C599 Intelligent PCI Bus Interface. In addition, the Central Arbiter also performs the general arbitration on the PCI bus. The Central Arbiter monitors incoming requests from both the CPU and PCI buses and grants control of the Interface to either the PP (PCI Master Controlling PCI bus) or CC (CPU Master Controlling CPU bus) state machines. Once a request has been granted, control of the Interface is transferred to that particular state machine. Once the transaction is complete, the arbiter delegates control of the bridge to the next requesting agent. Should there be no pending requests, the default owner of the bridge is the CC (CPU Master Controlling CPU bus) state machine. When servicing a CPU master bus cycle, the Central Arbiter will not grant a PCI agent control of the PCI bus (although CY82C599 to PCI transfers are permitted during CPU to memory bus transactions due to Post-Write Operations). Also, when servicing a PCI agent, a CPU hold is established (HOLD asserted and HLDA acknowledged) prior to the PCI GNT signal

being asserted. The PCI arbitration algorithm is user selectable through register 30h, and can be either fixed or rotating priority.

#### 5.1.1 PCI Arbitration

Arbitration on the PCI bus is controlled by the Central Arbiter within the CY82C599. PCI arbitration is conducted through a request-grant handshake between the requesting master and the arbiter (CY82C599). Request and grant lines are point-to-point signals that are not universally shared on the bus. The CY82C599 will hold off granting the bus to a PCI agent if the CY82C599 is involved with a transaction. The PCI arbitration algorithm can be either a rotating or fixed priority (see control register 30h). When a fixed priority scheme is selected, REQ0/GNT0 has the highest priority and REQ3/GNT3 the lowest priority. A rotating priority scheme starts out with same priority as the fixed algorithm (REQ0/GNT0 highest,...etc.). After each agent gains control of the bus it is delegated to the lowest priority. The highest priority is defaulted to the agent that has had the longest time since having control of the bus.

#### 5.1.2 CPU Arbitration

When used in conjunction with the CY82C596/7, the CY82C599 conducts the first level arbitration on the CPU bus. If the 82C596/7 (or any device controlled by the CY82C596/7 on the ISA or VESA buses) requests control of the CPU bus, it must first assert a hold request (C597HOLD) to the CY82C599. The CY82C599 will asserts a hold request to the CPU (through the CPUHOLD signal). After completing the current transaction, the CPU acknowledges the hold by asserting the CPUHLDA signal back to the 82C599. Upon receiving this acknowledge, the CY82C599 grants the original bus request by asserting a hold acknowledge back to the CY82C596/7 by asserting C597HLDA. The CY82C599 gives the CY82C596/7 the highest priority and will interrupt PCI transactions when a request, such as a request to refresh, is received.

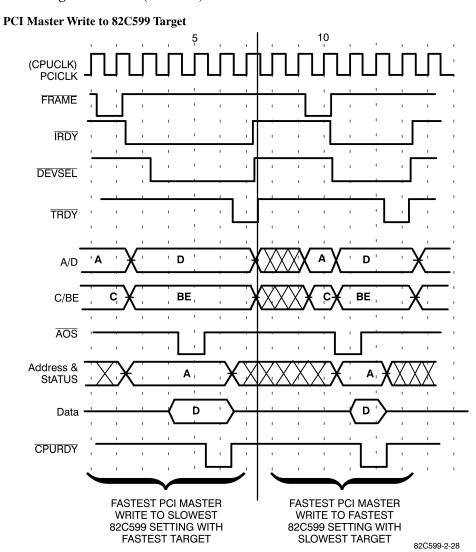

#### 5.2 PCI Master Controlling PCI Bus (PP) State Machine

The PCI Master Controlling PCI Bus (PP) State Machine is responsible for executing all PCI bus transactions based on inputs from the PCI bus. This includes claiming and administering all PCI transactions where the target is on the CPU bus side of the 82C599 Interface. Such transactions are broken into two separate transfers; 1) PCI master device to the CY82C599 as the target, and 2) CY82C599 as the CPU bus master to CPU bus target. The first portion of the transaction is controlled by the PP state machine, while the second transaction is handled with the PC state machine. The PP state machine conducts all PCI related operations, provides control information to the PC state machine, and delivers the address and data to the internal FIFO.

#### 5.3 PCI Master Controlling CPU Bus (PC) State Machine

The PCI Controlling CPU Bus (PC) state machine is responsible for all transactions on the CPU bus initiated by PCI bus inputs. These transactions include conducting a CPU bus cycle in order to deliver data from the internal FIFO to the CPU bus target. Although the PC state machine acts as the master on the CPU bus, it is not considered in control of the CY82C599 during any transaction. Instead, the PC state machine receives control signals from the PP state machine, who is in control of the CY82C599 PCI Interface.

## 5.4 CPU Master Controlling CPU Bus (CC) State Machine

The CPU Master Controlling CPU Bus (CC) State Machine is responsible for handling all CPU bus transactions initiated by CPU bus inputs. This includes claiming all transactions that are within the PCI or 'unknown' address spaces (memory or I/O).

When a CPU bus cycle is claimed by the CY82C599, the CC state machine is in control of the CY82C599 Interface. CPU-to-PCI transfers are broken into two separate transactions; 1) CPU bus master device to the CY82C599 as the CPU bus target, and 2) CY82C599 as the PCI master to PCI bus target. The first portion of the transaction is controlled by the CC state machine, while the second transaction is handled by the CP state machine. The CC state machine conducts all CPU bus related operations, provides control information to the CP state machine, and delivers the address and data to the internal FIFO. When there are no pending bus requests, the CC state machine is the default owner of the CY82C599 Interface.

#### 5.5 CPU Master Controlling PCI Bus (CP) State Machine

The CPU Master Controlling the PCI Bus (PC) State Machine is responsible for all transactions on the PCI bus initiated by CPU bus inputs. These transactions include conducting PCI bus cycle in order to deliver data from the internal FIFO to the PCI bus target. Although the CP state machine acts as the master on the PCI bus, it is not considered in control of the CY82C599 during any transaction. Instead, the CP state machine receives control signal from the CC state machine, who is in control of the CY82C599 Interface.

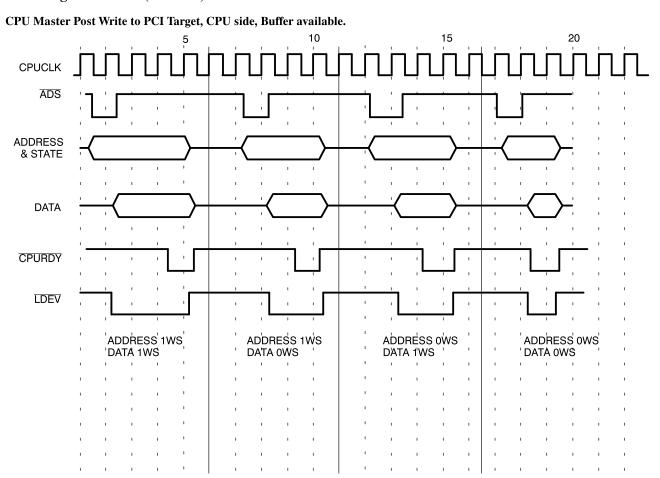

#### 5.6 Post Write Operation

The CY82C599 allows Post-Writing for both CPU-to-PCI bus, and PCI-to-CPU bus transactions. The Post-Write FIFO is a four deep, 64-bit wide circular FIFO designed to allow a CPU or PCI bus agents to Post-Write four full words (32 bits of address and 32 bits of data) to the CY82C599. Once the information arrives in the FIFO, the CY82C599 requests control of the PCI or CPU bus in order to complete the write transaction. Once a line of data has been read from the FIFO, an additional line can be written in order to keep the FIFO full and increase throughput. Should a Post-Write to a PCI agent go unclaimed, the CY82C599 will retry a predetermined number of attempts (see register 33h). Should the transaction still go unclaimed, the data will be lost. By providing this Post-Write feature, the CY82C599 allows the CPU to Post-Write to the CY82C599, and then proceed with other transactions.

#### 5.7 PCI Burst Pre-Read Operation

The CY82C599 supports CPU-to-PCI Burst Pre-Read operations. Pre-Reads are similar to Post-Writes, and are handled with the use of the same on-chip FIFO. The CY82C599 can pre-fetch read data, fill the internal FIFO, and then burst read to the requesting master on the PCI bus. During this pre-fetch, the CY82C599 holds the requesting bus by inserting wait states. The CY82C599 will burst the data to the requesting PCI agent in a linear sequence.

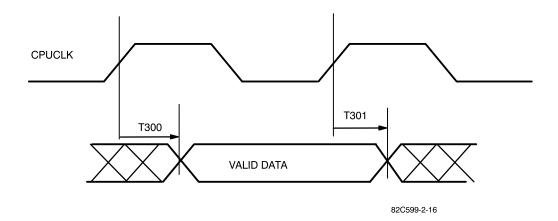

#### 5.8 Synchronous/Asynchronous PCI Operation

The CY82C599 allows for both synchronous and asynchronous PCI bus operation. Synchronous PCI bus operation is defined as when the PCI and CPU buses are operating from the same clock. Asynchronous PCI operation is defined as when the PCI and CPU clocks are either out of phase or running at different frequencies. The CY82C599 is able to accommodate the two asynchronous buses through the use of advanced synchronization circuitry. The asynchronous operation can support a CPU clock up to 50MHz, and a PCI clock from 0 to 40MHz.

#### **6.0 Address Space Priority**

The CY82C599 employs a priority scheme for all memory and I/O transactions. The purpose for this priority system is to achieve predictable results should there be an overlap in the

memory or I/O address space, as well as accesses to 'unknown' address locations. The purpose of the following sections is to explain the priorities of each type of transaction from each side of the CY82C599 Interface.

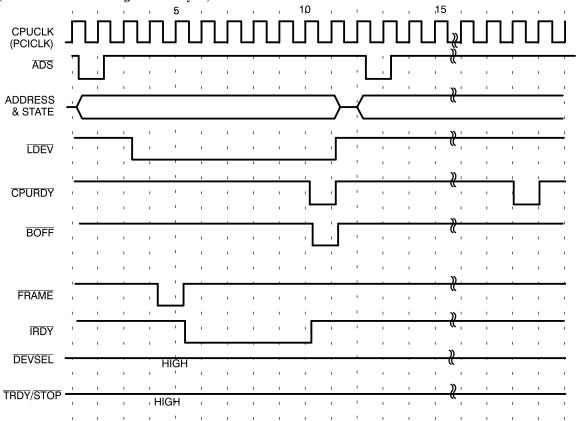

#### **6.1 CPU Bus Master Priority-Memory Accesses**

The highest priority in a CPU bus master memory access is when the target resides in Local memory. During these cycles, the CY82C599 monitors, but does not participate in the transaction.

The second highest priority in a CPU bus master memory access is when the target is in PCI or VESA memory address space. For transactions to PCI memory space, the CY82C599 will claim the transaction by asserting \overline{LDEV}. The transaction is allowed to proceed normally, and is terminated on the CPU bus with \overline{CPURDY} from the CY82C599. If the transaction is claimed by a VESA device, the VESA target will drive \overline{LDEV} and terminates the transaction with \overline{CPURDY}.

The lowest priorities are CPU bus master memory accesses to VESA or ISA address space. The CY82C599 will monitor, but will not participate in the transaction.

The CY82C599 will claim all memory transactions to 'unknown' address space on the CPU bus by asserting LDEV and will immediately initiate a PCI cycle. If the target is a PCI device (in 'unknown' space), the transaction is claimed by the PCI device and proceeds normally, with the CY82C599 terminating the transaction by asserting CPURDY to the CPU. If the PCI transaction goes unclaimed, the CY82C599 de-asserts LDEV. The CY82C599 will automatically de-assert **LDEV** if **CPURDY** goes active (the transaction was claimed and completed by a VESA device). If the target is a VESA device (in 'unknown' space), it asserts LDEV and claims the transaction. Since LDEV CY82C599 and the VESA devices are ANDed together, the CY82C596/7 will only pass the cycle to the ISA bus if neither VESA or PCI claims the transaction. Since VESA and PCI agents share the same priority, two memory devices (one on VESA and the other PCI) should never share the same address space. Doing so will cause a clash condition by having both devices claim the same transaction.

#### 6.2 CPU Bus Master Priority-I/O Accesses

The highest priority CPU bus master I/O transaction is PCI/VESA space. These two types of devices I/O address spaces are considered to have the same priority. The CY82C599 will claim I/O transactions to PCI address space by asserting \overline{LDEV}. The transaction is allowed to proceed normally, and is terminated on the CPU bus with \overline{CPURDY} from the CY82C599. If the transaction is to VESA I/O address space, the VESA target will claim the transaction by asserting \overline{LDEV}.

The second priority CPU bus master access to I/O space is when the target resides in ISA space. The CY82C599 will monitor, but not participated in CPU bus master transactions to ISA space.

If the address is not mapped to PCI/VESA or ISA space, then it is considered as 'unknown'. The CY82C599 will claim all I/O transactions to 'unknown' address space on the CPU bus by asserting \$\overline{LDEV}\$ and will immediately initiate a PCI cycle. If the target is a PCI device (in 'unknown' space), the transaction is claimed by the PCI device and proceeds normally, with the CY82C599 terminating the transaction by asserting \$\overline{CPURDY}\$ to the CPU. If the PCI transaction goes unclaimed, the CY82C599 de-asserts \$\overline{LDEV}\$. The CY82C599 will automatically de-assert \$\overline{LDEV}\$ if \$\overline{CPURDY}\$ goes active (the transaction was claimed and completed by a VESA device). If the target is a VESA device (in 'unknown' space), it asserts \$\overline{LDEV}\$ and claims the transaction. Since \$\overline{LDEV}\$ from the CY82C599 and the VESA devices are

ANDed together, the CY82C596/7 will only pass the cycle to the ISA bus if neither VESA or PCI claims the transaction. Since VESA and PCI agents share the same priority, two I/O devices (one on VESA and the other PCI) should never share the same address space. Doing so will cause a clash condition by having both devices claim the same transaction.

#### **6.3 PCI Master Priority-Memory Accesses**

The highest priority PCI master memory transaction is an access to Local memory. During such transactions the CY82C599 will claim the CPU bus as quickly as possible by asserting a hold request to the CPU. PCI bus ownership is not be granted until a hold acknowledge is received back from the CPU. Once bus ownership has been established, the transaction proceeds normally with the CY82C599 as the CPU bus master.

The second priority PCI master memory transaction is to PCI memory located on another PCI card. During these transactions the CY82C599 monitors, but does not participate in the transaction. In addition, the CY82C599 will hold the CPU bus during the entire transaction.

The third priority PCI master memory transaction is to ISA/VESA address space. During these types of transfers, the CY82C599 will claim the ISA/VESA bus as soon as possible and initiate an ISA/VESA cycle.

If the address is not mapped to PCI/VESA or ISA space, then it is considered as 'unknown'. PCI agents are given the first opportunity to claim PCI master accesses to 'unknown' memory space. The CY82C599 will wait for a PCI agent to claim the transaction by monitoring DEVSEL. If the transaction goes unclaimed on the PCI bus, the CY82C599 will automatically start a CPU bus cycle. If the transaction goes unclaimed on the CPU bus, the 82C596/7 will automatically pass the transaction to the ISA bus.

#### 6.4 PCI Master Priority-I/O Accesses

The highest priority PCI master I/O access is to PCI address space. During these transactions the CY82C599 monitors, but does not participate in the transaction. In addition, the CPU bus is held during the entire transaction.

The second priority PCI master I/O transaction is to the ISA bus. During such transactions, the CY82C599 will claim the transaction by asserting DEVSEL and behave as the PCI target. The CY82C599 will also start a CPU bus as soon as possible and initiate an ISA/VESA cycle.

If the address is not mapped to PCI/VESA or ISA space, then it is considered as 'unknown'. PCI agents are given the first opportunity to claim PCI master accesses to 'unknown' I/O space. The CY82C599 will wait for a PCI agent to claim the transaction by monitoring the DEVSEL. If the transaction goes unclaimed on the PCI bus, the CY82C599 will automatically start a CPU bus cycle. If the transaction goes unclaimed on the CPU bus, the 82C596/7 will automatically pass the transaction to the ISA bus.

#### 7.0 Level 1 Write-Back Cache Support

The CY82C599 also provides for chipsets that support Level 1 write-back cache. The CY82C599 adheres to the HITM protocol required to maintain cache coherency. When HITM is asserted, the CPU has detected a hit to a modified line in the Level 1 cache. In order to allow the CPU to write-back the modified line, the CY82C599 de-asserts the HOLD request to the CPU. The CPU then proceeds to write the modified line to DRAM and L2 cache (if a L2 cache hit is detected). The CY82C599 immediately requests another HOLD to the CPU so the initial transaction can continue.

#### 8.0 Stand-Alone Mode

The CY82C599 can work in conjunction with the 82C596/7 to provide a high performance VESA/ISA/PCI PC/AT system. The CY82C599 also has the built-in flexibility to work with other chipsets to provide a CPU-to-PCI bus bridge. This is referred to as Stand Alone Mode. In Stand-Alone mode, the CY82C599 has enough flexibility to accommodate other chipset's logic and is able to pass transactions to 'unknown' space from one bus to another. In order to operate properly in Stand-Alone mode, the register set of the accompanying chipset must be compatible with the CY82C599 (contact the factory for details).

## 9.0 Power Management Mode

The CY82C599 implements flexible power management logic. When used with the CY82C597 (for a full VESA/ISA/PCI system), most of the power management functions are performed by the CY82C599. The CY82C597 will only perform the SMM memory mapping. All other power management functions in the CY82C597 are disabled. For VESA/ISA-only systems, the CY82C597 provides all of the chipset power management.

There are eleven event detectors and five user-programmable timers in the CY82C599 allowing it to support full hardware power management (for CPUs that do not support SMM, System Management Mode) and software power management (through SMM).

#### **Events that can be Monitored**

The CY82C599 allows the following events to be monitored:

- 1) VESA master request

- 2) Keyboard command

- 3) Serial Port command

- 4) Parallel Port command

- 5) Hard Disk command

- 6) DMA/MASTER request from the ISA bus

- 7) Non-motherboard memory access

- 8) Video memory access

- 9) A specific I/O address

- 10) A specific memory range

- 11) A specific I/O range

When events are detected, the CY82C599 will transition to different power-down states.

#### **Hardware Power Management**

For hardware power management, the CY82C599 supports Full-speed/Stand-by/Suspend/Off states. In Stand-by state, the CY82C599 will assert the SLOWCLK signal that can be used by the system to slow down the CPU's clock frequency. In the Suspend state, the CY82C599 will assert the STOPCLK signal. STOPCLK can be used to stop the CPU's clock or turn off the monitor and other supported peripherals.

In the Full-speed state, the CY82C599 will monitor all stand-by events. Any monitored event will reset the stand-by timer. If no events occur within the period specified by the stand-by timer, the CY82C599 will enter the Stand-by state and assert the SLOWCLK signal. Once Stand-by state has been entered, the CY82C599 will monitor Suspend state events. If no event occurs within the period specified by the suspend timer, the CY82C599 will assert STOPCLK and enter the Suspend state. In the Suspend state, the assertion of STOPCLK can be used to stop the CPU's clock or power-down any supported peripherals. If any monitored event is detected, the CY82C599 will return to the Full-speed state and STOPCLK/SLOWCLK will be deasserted.

Any interrupt will temporarily cause the STOPCLK signal (and optionally the SLOWCLK signal) to be deasserted (allowing the CPU to service the interrupt). If the interrupt timer expires before a monitored event occurs, the CY82C599 will automatically return to the power-down state it was in prior to the interrupt (with the appropriate signal asserted).

#### **Software Power Management**

For software power management, the CY82C599 can fully utilize Intel's, AMD's, and Cyrix's power management modes to reduce system power requirements.

In the Full-speed state, the CY82C599 will monitor all stand-by events. If no events occur within the period specified by the stand-by timer, the CY82C599 will enter the Stand-by state and assert the SMI signal. In Stand-by state, the system clock can be slowed down by the assertion of the SLOWCLK signal. SLOWCLK is controlled through software (See Register 64). Once Stand-by state has been entered, the CY82C599 will monitor Suspend state events. If no event occurs within the period specified by the suspend timer, the CY82C599 will assert SMI and enter the Suspend state. In the Suspend state, software assertion of STOPCLK (See register 64) can be used to stop the CPU's clock, the monitor can be turned off using a software driver, or the hard disk can be spun down. Please note that the assertion/deassertion of STOPCLK and SLOWCLK is fully software controlled and can be implemented in any power-down state (Stand-by and Suspend are customary).

The Suspend timer is fully reprogrammable. In the Suspend state, the Suspend timer can be disabled, the timer value changed, and the timer re-enabled. After the new timer value has expired,  $\overline{SMI}$  will once again be activated to allow for a user-defined power management mode.

The CY82C599 also contains three independent timers that can be used during the power-down control period. Different events and different time periods can be specified for each timer. Each timer will cause  $\overline{SMI}$  to be asserted after the specified time period has expired. The three timers allow for more user-defined, power-down system states.

In order to identify the source of the  $\overline{SMI}$  (System Management Interrupt), the CY82C599 maintains a status register (register 58) that keeps track of which event caused  $\overline{SMI}$  to be asserted. Power-management software should read the status register before determining a course of action. The CPU and peripherals can be individually powered-down based on the source of the System Management Interrupt.

If any specified event is detected during Stand-by, Suspend, or any other power-down state, the CY82C599 will automatically return to the Full-speed state (with the stand-by timer reset). If the system is using software power management, the CY82C599 will assert  $\overline{\text{SMI}}$  and within the  $\overline{\text{SMI}}$  handler, software should bring all of the system clocks to their full-speed, full-power states through the de-assertion of  $\overline{\text{STOPCLK/SLOWCLK}}$ .

## 10.0 Control Registers

This section summarizes the registers in the CY82C599.

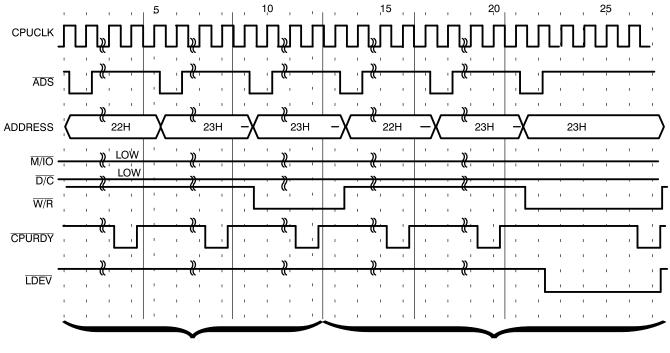

The on-chip registers are accessed via I/O sequence 22H and 23H. Each register is selected by writing a byte containing the register address index to I/O address 22H. A subsequent byte read/write to I/O address 23H will modify/read-out the contents of the selected register.

The CY82C599 provides five groups of registers:

Memory address space configuration registers (except PC/AT high memory)

I/O address space configuration registers

Power down configuration registers

State machine configuration registers

PC/AT high memory address space configuration registers

The Local DRAM Address Configuration Registers are used to establish the boundary of the Local DRAM in the system. Index 20H and 21H are used to specify the ending address of on-board DRAMs. Index 22H to 27H are the configuration registers for

Memory Blocks 0 and 1. They contain the base address of each memory block, the block sizes, and the mapping selection for each block: Local DRAM region, PCI region or ISA region. It is best to specify all Non-Local DRAM memory areas below 16Mbytes as ISA region and remap all other Non-Local DRAM memory areas above 2 Gbytes as the PCI region.

I/O Block Configuration Registers are used to specify the base address, block size, and function select for the user selectable I/O blocks. The pre-defined I/O blocks are simply enabled or disabled.

Power Down Configuration Registers allow various hardware events to be monitored in order to invoke or come out of power down mode.

State Machine configuration registers control features of the PCI and CPU bus State Machines. These features include the number of wait states, and arbitration priority of both State Machines.

PC/AT High Memory Address Space Configuration Registers are used to specify the memory regions from 000A0000H to 000FFFFFH (blocks A, B, C, D, E, and F). These bits are used with CY82C59/67 to provide shadowing in a PC/AT system.

#### Index 20H

| Bit | Function                             | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Reserved                             | 0000                | 0000                                    |

| 3:0 | Local DRAM Ending Address: A27 : A24 | 0000                | User selectable                         |

#### Index 21H

| Bit | Function                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Local DRAM Ending Address: A23: A16 | 00000000            | User selectable                         |

#### Index 22H

| Bit | Function                               | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Memory Block 0 Base Address: A31 : A24 | 00000000            | User selectable                         |

#### Index 23H

| Bit | Function                               |         | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------|---------|-----------------------------------------|

| 7:0 | Memory Block 0 Base Address: A23 : A16 | 0000000 | User selectable                         |

## Index 24H

| Bit | Function                                                                                                                                                                                                                                                 | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:6 | Memory Block 0 Base Address: A15 : A14                                                                                                                                                                                                                   | 00                  | User selectable                         |

| 5:4 | Memory Block 0 Function Select 00: Disable (Default) 01: Local DRAM Region 10: PCI Region 11: ISA /VESA Region                                                                                                                                           | 00                  | User selectable                         |

| 3:0 | Memory Block 0 Size Select: 0000: 16KByte (Default) 0001: 32KByte 0010: 64KByte 0011: 128KByte 0100:: 256KByte 0101: 512KByte 0110: 1MByte 0111: 2MByte 1000: 4MByte 1001: 8MByte 1001: 8MByte 1011: 32MByte 1110: 64MByte 1110: 256MByte 1111: 512MByte | 0000                | User selectable                         |

## Index 25H

| Bit | Function                               | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Memory Block 1 Base Address: A31 : A24 | 00000000            | User selectable                         |

## Index 26H

| Bit | Function                               | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Memory Block 1 Base Address: A23 : A16 | 00000000            | User selectable                         |

## Index 27H

| Bit | Function                                                                                                                                                                                                                                                | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:6 | Memory Block 1 Base Address: A15 : A14                                                                                                                                                                                                                  | 00                  | User selectable                         |

| 5:4 | Memory Block 1 Function Select 00: Disable (Default) 01: Local DRAM Region 10: PCI Region 11: ISA/VESA Region                                                                                                                                           | 00                  | User selectable                         |

| 3:0 | Memory Block 1 Size Select: 0000: 16KByte (Default) 0001: 32KByte 0010: 64KByte 0011: 128KByte 0100: 256KByte 0101: 512KByte 0110: 1MByte 0111: 2MByte 1000: 4MByte 1001: 8MByte 1001: 8MByte 1011: 32MByte 1011: 32MByte 1110: 256MByte 1111: 512MByte | 0000                | User selectable                         |

## Index 28H

| Bit | Function                           | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|------------------------------------|---------------------|-----------------------------------------|

| 7:0 | I/O Block 0 Base Address: A15 : A8 | 00000000            | User selectable                         |

## Index 29H

| Bit | Function                                                                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | I/O Block 0 Base Address: A7 : A4                                                     | 0000                | User selectable                         |

| 3:2 | I/O Block 0 Function Select: 0X: Disable (Default) 10: PCI Region 11: ISA/VESA Region | 00                  | User selectable                         |

| 1:0 | I/O Block 0 Size Select: 00: 16 Byte (Default) 01: 64 Byte 10: 256 Byte 11: 1024Byte  | 00                  | User selectable                         |

## **Index 2AH**

| Bit | Function                           | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|------------------------------------|---------------------|-----------------------------------------|

| 7:0 | I/O Block 1 Base Address: A15 : A8 | 00000000            | User selectable                         |

# Index 2BH

| Bit | Function                                                                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | I/O Block 1 Base Address: A7 : A4                                                     | 0000                | User selectable                         |

| 3:2 | I/O Block 1 Function Select: 0X: Disable (Default) 10: PCI Region 11: ISA/VESA Region | 00                  | User selectable                         |

| 1:0 | I/O Block 1 Size Select: 00: 16 Byte (Default) 01: 64 Byte 10: 256 Byte 11: 1024Byte  | 00                  | User selectable                         |

# Index 2CH

| Bit | Function                                                     | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Keyboard Detection Enable 0: Disable 1: Enable               | 0                   | User selectable                         |

| 6   | Serial Port Detection Enable 0: Disable 1: Enable            | 0                   | User selectable                         |

| 5   | Parallel Port Detection Enable 0: Disable 1: Enable          | 0                   | User selectable                         |

| 4   | Hard Disk Detection Enable 0: Disable 1: Enable              | 0                   | User selectable                         |

| 3   | CY82C599 Hold Detection Enable 0: Disable 1: Enable          | 0                   | User selectable                         |

| 2   | Non Motherboard Memory Detection Enable 0: Disable 1: Enable | 0                   | User selectable                         |

| 1   | Non Motherboard I/O Detection Enable 0: Disable 1: Enable    | 0                   | User selectable                         |

| 0   | Video RAM Detection Enable 0: Disable 1: Enable              | 0                   | User selectable                         |

# **Index 2DH**

| Bit | Function                                                                                                                                                                                                                                                                                                                             | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Reserved                                                                                                                                                                                                                                                                                                                             | 0                   | 0                                       |

| 6   | Green Feature Timer Select (see Register 2DH, Bits 3:0).                                                                                                                                                                                                                                                                             | 0                   | User selectable                         |

| 5   | PCI Master Detection Enable 0: Disable 1: Enable                                                                                                                                                                                                                                                                                     | 0                   | User selectable                         |

| 4   | Floppy Disk Detection Enable 0: Disable 1: Enable                                                                                                                                                                                                                                                                                    | 0                   | User selectable                         |

| 3:1 | Green Feature Timer Delay Select  Bit 6=0  Bit 6=1  000: 30 Second  000: 0.2 Seconds  001: 4 Minute  001: 0.4 Seconds  010: 8 Minute  010: 1.0 Seconds  011: 16 Minute  011: 1.8 Seconds  100: 32 Minute  100: 3.5 Seconds  101: 65 Minute  101: 7.0 Seconds  110: 130 Minute  110: 14.0 Seconds  111: 260 Minute  111: 30.0 Seconds | 000                 | User selectable                         |

| 0   | Green Feature Enable 0: Disable 1: Enable                                                                                                                                                                                                                                                                                            | 0                   | User selectable                         |

# **Index 2EH**

| Bit | Function                      | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------|---------------------|-----------------------------------------|

| 7:0 | I/O Trap Address: IOA7 : IOA0 | 00000000            | User selectable                         |

# Index 2FH

| Bit | Function                                       | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Reserved                                       | 0000                | 0000                                    |

| 3   | I/O Trap Detection Enable 0: Disable 1: Enable | 0                   | User selectable                         |

| 2   | Reserved                                       | 0                   | 0                                       |

| 1:0 | I/O Trap Address: IOA9 : IOA8                  | 00                  | User selectable                         |

## Index 30H

| Bit | Function                                                                       | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | PCI Function Enable 0: Disable 1: Enable                                       | 0                   | 1                                       |

| 6   | Reserved                                                                       | 0                   | 0                                       |

| 5   | LRDY Delay Enable 0: Disable 1: Enable                                         | 0                   | 1                                       |

| 4   | Reserved                                                                       | 0                   | 0                                       |

| 3   | Arbitration Fast Interface Enable 0: Disable 1: Enable                         | 0                   | 0                                       |

| 2   | PCI Hidden Arbitration Mode Enable 0: Disable 1: Enable                        | 0                   | 0                                       |

| 1   | Reserved                                                                       | 0                   | 1                                       |

| 0   | PCI Arbitration Rotate Priority Enable 0: Disable (Fixed) 1: Enable (Rotating) | 0                   | 0                                       |

## Index 31H

| Bit | Function  | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-----------|---------------------|-----------------------------------------|

| 7:0 | Reserved. | 00000000            | 00001000                                |

# Index 32H

| Bit | Function                                                                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Disable BOFF to CPU Control 0: Disable 1: Enable                                      | 0                   | 1                                       |

| 6:5 | Reserved                                                                              | 00                  | 01                                      |

| 4   | CPU Master Post Write Buffer Enable 0: Disable 1: Enable                              | 0                   | 1                                       |

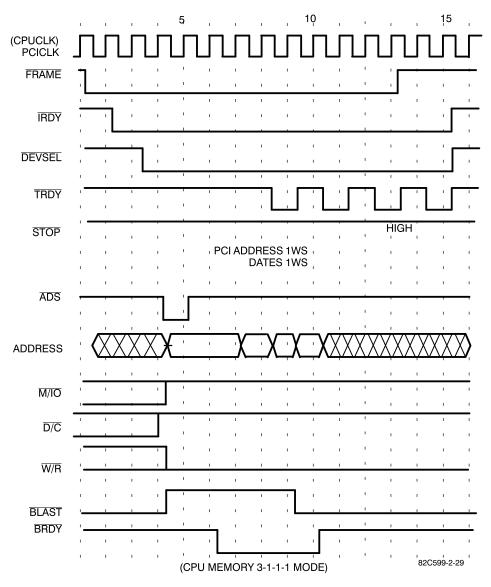

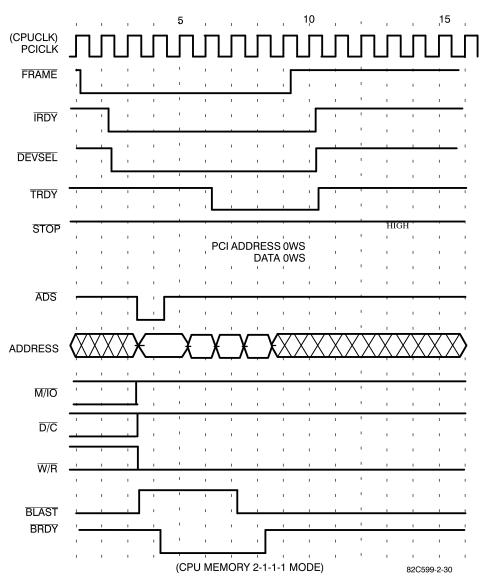

| 3   | CPU Master State Machine Fast Interface Enable 0: Disable 1: Enable                   | 0                   | 0                                       |

| 2   | CPU Master CPU State Machine Address 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS)    | 0                   | 0                                       |

| 1   | CPU Master CPU State Machine Data Write 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS) | 0                   | 0                                       |

| 0   | CPU Master CPU State Machine Data Read 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS)  | 0                   | 0                                       |

# Index 33H

| Bit | Function                                                                      | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | CPU Master CPU State Machine I/O Post Write Cycle Enable 0: Disable 1: Enable | 0                   | 0                                       |

| 6   | Reserved                                                                      | 0                   | 1                                       |

| 5:4 | CPU Master PCI Retry 00: Disable (Default) 01: 1 10: 3 11: Infinite           | 00                  | 11                                      |

| 3   | CPU Master Write Burst Mode Enable 0: Disable 1: Enable                       | 0                   | 0                                       |

| 2   | CPU Master PCI State Machine Fast Back-to-Back Enable 0: Disable 1: Enable    | 0                   | 0                                       |

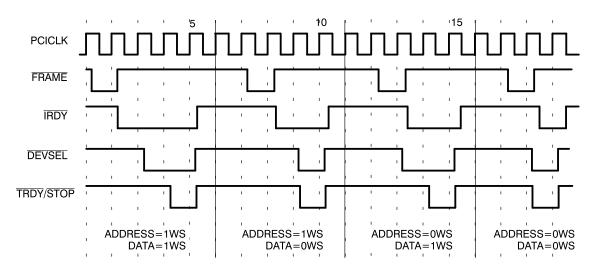

| 1   | CPU Master PCI State Machine Address OWS Enable 0: Disable 1: Enable          | 0                   | 0                                       |

| 0   | CPU Master PCI State Machine Data Write OWS Enable 0: Disable 1: Enable       | 0                   | 0                                       |

# Index 34H

| Bit | Function                                                                                                                                                                                                                                                                                                                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Reserved                                                                                                                                                                                                                                                                                                                              | 0                   | 0                                       |

| 6   | PCI Master Post Write Buffer Enable  0: Disable  1: Enable  Note: Register 34 Bit 6 and Register 35, Bit4 together control the Post write funcitonality. See below for desired register settings.  Reg. 34 Reg.  Bit6 Bit 4 Function  0 X Non Burst, No Post-Write  1 0 Non Burst, Post-Write  1 Burst, Post-Write                    | 0                   | 0                                       |

| 5   | Burst Pre-Read Enable 0: Disable 1: Enable Note: Register 34 Bit 5 and Register 34, Bit4 together control the Burst Pre-Read funcitonality. See below for desired register settings. Reg. 34 Reg. Bit6 Bit 4 Function 0 X Burst Pre-Read Off 1 0 Burst Pre-Read to Local Memory only. 1 Burst Pre-Read to ISA, VESA, and Local memory | 0                   | 0                                       |

| 4   | PCI Master Pre-read Buffer Enable 0: Disable 1: Enable                                                                                                                                                                                                                                                                                | 0                   | 0                                       |

| 3   | PCI Master PCI State Machine VESA+ISA Post Write Enable 0: Disable 1: Enable                                                                                                                                                                                                                                                          | 0                   | 0                                       |

| 2   | PCI Master PCI State Machine Address 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS)                                                                                                                                                                                                                                                    | 0                   | 0                                       |

| 1   | PCI Master CPU State Machine Address 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS)                                                                                                                                                                                                                                                    | 0                   | 0                                       |

| 0   | PCI Master PCI State Machine Data Read 0WS Enable 0: Disable (1 WS) 1: Enable (0 WS)                                                                                                                                                                                                                                                  | 0                   | 0                                       |

## Index 35H

| Bit | Function                                                                                                               | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | PCI Master PCI State Machine Data Write 0WS Enable 0: Disable 1: Enable                                                | 0                   | 0                                       |

| 6   | PCI Master PCI State Machine Burst Mode Enable 0: Disable 1: Enable                                                    | 0                   | 0                                       |

| 5   | PCI Master State Machine Fast Interface Enable 0: Disable 1: Enable                                                    | 0                   | 0                                       |

| 4   | PCI Master State Machine Generate Fast ADS Cycle Enable 0: Disable 1: Enable Note: See register 34, Bit6.              | 0                   | 0                                       |

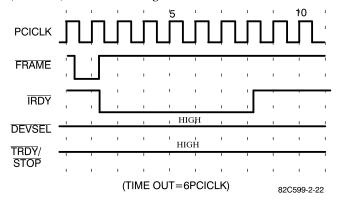

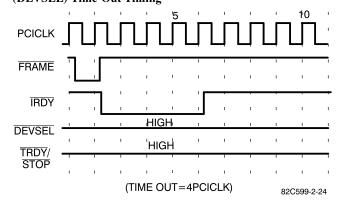

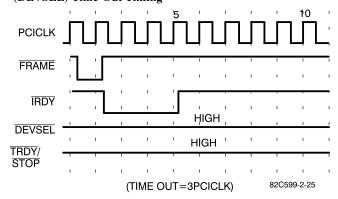

| 3:2 | CPU Master PCI DEVSEL Time Out Period 00: 6 PCICLK (Default) 01: 5 PCICLK 10: 4 PCICLK 11: 3 PCICLK                    | 00                  | 00                                      |

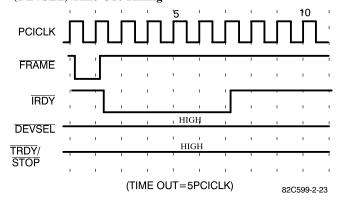

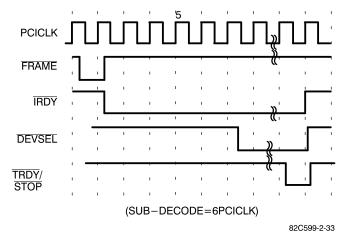

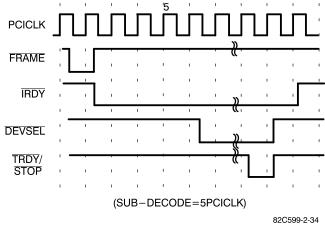

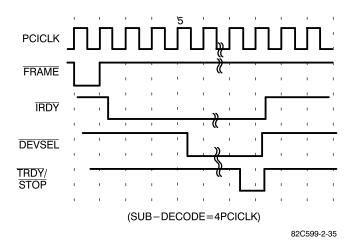

| 1:0 | PCI Master PCI Subtractive Decode DEVSEL Time Out Period 00: 6 PCICLK (Default) 01: 5 PCICLK 10: 4 PCICLK 11: 3 PCICLK | 00                  | 10                                      |

Note: PCI Master PCI Subtractive Decode DEVSEL Time Out Period must be equal or less than CPU Master PCI DEVSEL Time Out Period

# Period Index 36H

| Bit | Function                                                           | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Configuration Address Cycle Enable 0: Disable 1: Enable            | 0                   | 1                                       |

| 6   | Configuration Data Cycle Enable 0: Disable 1: Enable               | 0                   | 1                                       |

| 5   | Configuration Data Special Cycle Enable 0: Disable 1: Enable       | 0                   | 1                                       |

| 4   | PCI Master Configuration Address Cycle Enable 0: Disable 1: Enable | 0                   | 0                                       |

| 3   | Reserved                                                           | 0                   | 0                                       |

| 2   | Reserved.                                                          | 0                   | 0                                       |

| 1   | First Level Arbitration Rotate Enable 0: Disable 1: Enable         | 0                   | 0                                       |

| 0   | Reserved                                                           | 0                   | 1                                       |

# Index 37H

| Bit | Function                                                                   | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:3 | Reserved                                                                   | 00000               | 11111                                   |

| 2   | Configuration Register TARGET ABORT Status Bit Enable 0: Disable 1: Enable | 0                   | 0                                       |

| 1   | PERR External Support Enable 0: Disable 1: Enable                          | 0                   | 0                                       |

| 0   | SERR External Support Enable 0: Disable 1: Enable                          | 0                   | 0                                       |

## Index 38H

| Bit | Function                                                                                              |                                         |                                                   | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block A0000h: A7FFFh Bits 7:6 Function 00: Disable 01: Reserved 10: PCI Read 11: ISA/VESA Read | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Reserved PCI Write ISA/VESAWrite | 0000                | 0000                                    |

| 3:0 | Shadow Block A8000h: AFFFFh Bits 3:2 Function 00: Disable 01: Reserved 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Reserved PCI Write ISA/VESAWrite | 0000                | 1010                                    |

# Index 39H

| Bit | Function                                                                                              |                                         |                                                   | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block B0000h: B7FFFh Bits 7:6 Function 00: Disable 01: Reserved 10: PCI Read 11: ISA/VESA Read | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Reserved PCI Write ISA/VESAWrite | 0000                | User selectable                         |

| 3:0 | Shadow Block B8000h: BFFFFh Bits 3:2 Function 00: Disable 01: Reserved 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Reserved PCI Write ISA/VESAWrite | 0000                | User selectable                         |

# Index 3AH

| Bit | Function                                                                                                      |                                         |                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block C0000h: C3FFFh Bits 7:6 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read  | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

| 3:0 | Shadow Block C4000h : C7FFFh Bits 3:2 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

## **Index 3BH**

| Bit | Function                                                                                                     |                                         |                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block C8000h: CBFFFh Bits 7:6 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

| 3:0 | Shadow Block CC000h: CFFFFh Bits 3:2 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

# Index 3CH

| Bit | Function                                                                                                      |                                         |                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block D0000h: D3FFFh Bits 7:6 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read  | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

| 3:0 | Shadow Block D4000h : D7FFFh Bits 3:2 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

# Index 3DH

| Bit | Function                                                                                                      |                                         |                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block D8000h: DBFFFh Bits 7:6 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read  | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

| 3:0 | Shadow Block DC000h : DFFFFh Bits 3:2 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

## **Index 3EH**

| Bit | Function                                                                                                      |                                         |                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Shadow Block D8000h : EFFFFh Bits 7:6 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read | Bits<br>5:4<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

| 3:0 | Shadow Block F0000h: FFFFFh Bits 3:2 Function 00: Disable 01: Local DRAM Read 10: PCI Read 11: ISA/VESA Read  | Bits<br>1:0<br>00:<br>01:<br>10:<br>11: | Function Disable Local DRAM Write PCI Write ISA/VESA Write | 0000                | User selectable                         |

# **Index 3FH**

| Bit | Function                                                                                                                                | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Reserved.                                                                                                                               | 0000                | 0000                                    |

| 3:2 | Pin 16,17 Function Select Bits 3:2 Function 00: Disabled 01: A30, A29 enabled 10: INTLI/INTEO enable 11: Invalid condition, do not use. | 00                  | User selectable                         |

| 1:0 | Pin 18 function Select Bits  1:0 Function 00: Disabled 01: A28 enabled 10: SLOWCLK enable 11: Invalid condition, do not use.            | 00                  | User selectable                         |

## Index 40H

| Bit | Function                                                          | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | Reserved. Must be set to 1 after power-on.                        | 0                   | 1                                       |

| 6   | Reserved.                                                         | 0                   | 1                                       |

| 5   | Reserved, Must be set to 1 after power-on.                        | 0                   | 1                                       |

| 4   | I/O write 22H, 23H, & 61H LDEV mask enable.                       | 0                   | 0                                       |

| 3   | Reserved, must be set to 1 after power-on.                        | 0                   | 1                                       |

| 2   | Configuration register Read Enable. 0: Write only. 1: Read/Write. | 0                   | 1                                       |

| 1   | Monitor VESA VL Bus LDEV enable.                                  | 0                   | 0                                       |

| 0   | VESA to PCI Stand Alone enable.                                   | 0                   | 0                                       |

# Index 41H

| Bit | Function                         | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|----------------------------------|---------------------|-----------------------------------------|

| 7   | VESA VL Bus BS16 support enable. | 0                   | 0                                       |

| 6:0 | Reserved.                        | 0000000             | 0010111                                 |

# Index 42H

| Bit | Function                                                | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | Reserved.                                               | 0000                | 0001                                    |

| 3   | Write back mode with no PCI Master HOLD support enable. | 0                   | 0                                       |

| 2:1 | Reserved, set to 0 after power-on.                      | 00                  | 00                                      |

| 0   | Level 1 Write back mode enable.                         | 0                   | 0                                       |

## Index 43H

| Bit | Function                    | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|-----------------------------|---------------------|-----------------------------------------|

| 7   | TRDY delay 1 CPUCLK enable. | 0                   | 0                                       |

| 6:0 | Reserved.                   | 0000000             | 0000000                                 |

## Index 44H

| Bit | Function                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Not used, available for BIOS storage. | 00000000            | 00000000                                |

# Index 45H

| Bit | Function                              | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------|---------------------|-----------------------------------------|

| 7:0 | Not used, available for BIOS storage. | 00000000            | 00000000                                |

# Index 46H

| Bit | Function                                                            | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|---------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7   | PCI Memory Block 2 Enable (A31=1, A27=0, A26=1 0: Disable 1: Enable | 0                   | 1                                       |

| 6:4 | PCI Memory Block 2 Address Select A30, A29, A28                     | 000                 | 000                                     |

| 3   | PCI Memory Block 3 Enable (A31=1, A27=1, A26=0 0: Disable 1: Enable | 0                   | 1                                       |

| 2:0 | PCI Memory Block 2 Address Select A30, A29, A28                     | 000                 | 000                                     |

## Index 47H

| Bit | Function                                                                             | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------------------------------------------|---------------------|-----------------------------------------|

| 7:4 | PCI I/O Block 2 base address A15-A12.<br>Note: A15-A12=0H disable PCI I/O block 2.   | 0000                | 0000                                    |

| 3   | Reserved. Set to 0.                                                                  | 0                   | 0                                       |

| 2:1 | PCI I/O block 2 size select S1-S0.  S1 S0 Size.  0 0 1 KB  0 1 2KB  1 0 4KB  1 1 8KB | 00                  | 00                                      |

| 0   | PCI I/O block 2 enable                                                               | 0                   | 0                                       |

## Index 48H

| Bit | Function                                         | Hardware<br>Default | Recommended<br>BIOS power-on<br>setting |

|-----|--------------------------------------------------|---------------------|-----------------------------------------|