# PSoC 6 MCU: CY8C61x4 Datasheet

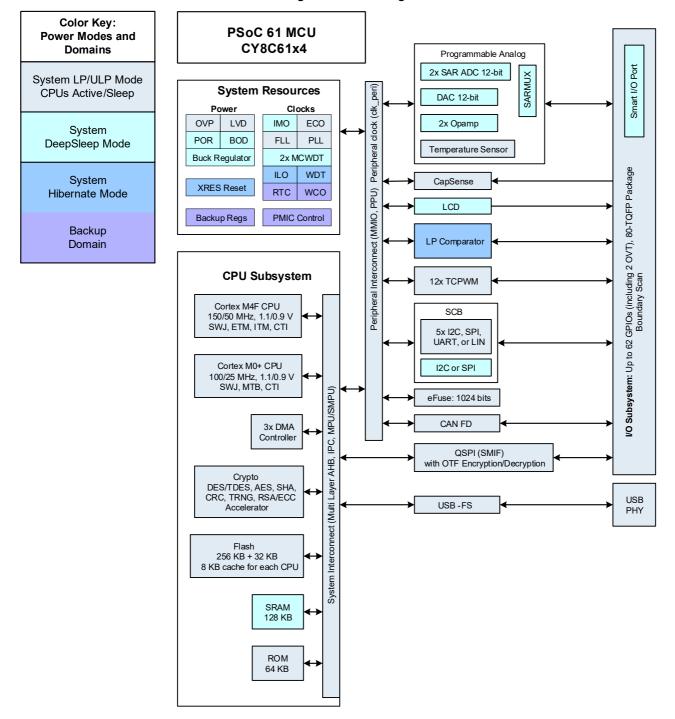

PSoC 61 MCU

# **General Description**

PSoC<sup>®</sup> 6 MCU is a high-performance, ultra-low-power and secured MCU platform, purpose-built for IoT applications. The CY8C61x4 product line, based on the PSoC 6 MCU platform, is a combination of a dual CPU microcontroller with low-power flash technology, digital programmable logic, high-performance analog-to-digital conversion and standard communication and timing peripherals.

# Features

**Note:** In PSoC 61 the Cortex M0+ is reserved for system functions, and is not available for applications.

# 32-bit Dual CPU Subsystem

- 150-MHz Arm<sup>®</sup> Cortex<sup>®</sup>-M4F (CM4) with single-cycle multiply (Floating Point and Memory Protection Unit)

- 100-MHz Cortex-M0+ (CM0+) with single-cycle multiply and MPU

- User-selectable core logic operation at either 1.1 V or 0.9 V

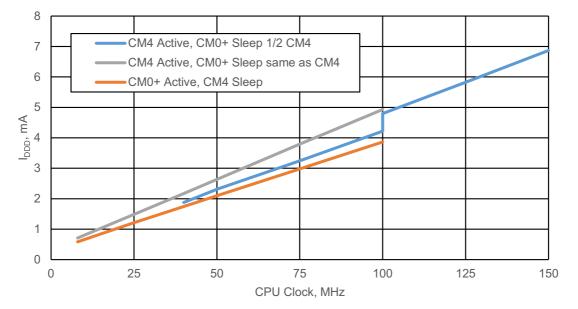

- Active CPU current slope with 1.1-V core operation

□ Cortex-M4: 40 µA/MHz

□ Cortex-M0+: 20 µA/MHz

- Active CPU current slope with 0.9-V core operation □ Cortex-M4: 22 µA/MHz

- □ Cortex-M0+: 15 µA/MHz

- Three DMA controllers

# **Memory Subsystem**

- 256-KB application flash and 32-KB supervisory flash (SFlash); read-while-write (RWW) support. Two 8-KB flash caches, one for each CPU.

- 128-KB SRAM with programmable power control and retention granularity

- One-time-programmable (OTP) 1-Kb eFuse array

# Low-Power 1.7-V to 3.6-V Operation

- Six power modes for fine-grained power management

- Deep Sleep mode current of 7 µA with 64-KB SRAM retention

- On-chip DC-DC Buck converter, <1-µA quiescent current

- Backup domain with 64 bytes of memory and real-time clock

# **Flexible Clocking Options**

- 8-MHz internal main oscillator (IMO) with ±2% accuracy

- Ultra-low-power 32-kHz internal low-speed oscillator (ILO)

- On-chip crystal oscillators (16 to 35 MHz, and 32 kHz)

- Phase-locked loop (PLL) for multiplying clock frequency

- Frequency-locked loop (FLL) for multiplying IMO frequency

# Quad-SPI (QSPI)/Serial Memory Interface (SMIF)

- Execute-In-Place (XIP) from external Quad SPI Flash

- On-the-fly encryption and decryption

- 4-KB cache for greater XIP performance with lower power

- Supports single, dual, and quad interfaces with throughput up to 320 Mbps

# Segment LCD Drive

- Supports up to 61 segments and up to 8 commons

- Operates in System Deep Sleep mode

# **Serial Communication**

- Six run-time configurable serial communication blocks (SCBs)

Five SCBs: configurable as SPI, I<sup>2</sup>C, or UART

One Deep Sleep SCB: configurable as SPI or I<sup>2</sup>C

- USB Full-Speed device interface

- One CAN FD block

# **Timing and Pulse-Width Modulation**

- Twelve timer/counter pulse-width modulators (TCPWMs)

- Center-aligned, Edge, and Pseudo-random modes

- Comparator-based triggering of Kill signals

# **Programmable Analog**

- Two 12-bit 2-Msps SAR ADCs with synchronized sampling, differential and single-ended modes, 16-channel sequencer with result averaging, and Deep Sleep operation

- One 12-bit voltage-mode digital-to-analog converter (DAC) with < 2-µs settling time

- Two low-power comparators available in Deep Sleep and Hibernate modes

- Two opamps with low-power operation modes

- Always-on low frequency Deep Sleep operation

- Built-in temperature sensor connected to ADC

# Up to 62 Programmable GPIOs

- One Smart I/O<sup>™</sup> port (6 I/Os) enables Boolean operations on GPIO pins; available during system Deep Sleep

- Programmable drive modes, strengths, and slew rates

- Two overvoltage-tolerant (OVT) pins

Cypress Semiconductor Corporation Document Number: 002-33480 Rev. \*E 198 Champion Court

# **Capacitive Sensing**

- Cypress CapSense<sup>®</sup> Sigma-Delta (CSD) provides best-in-class SNR, liquid tolerance, and proximity sensing

- Enables dynamic usage of both self and mutual sensing

- Automatic hardware tuning (SmartSense<sup>™</sup>)

# Security Built into Platform Architecture

- Authentication during boot using hardware hashing

- All debug and test ingress paths can be disabled

- Up to eight protection contexts

# Cryptography Accelerators

- Hardware acceleration for symmetric and asymmetric cryptographic methods and hash functions

- True random number generation (TRNG) function

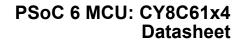

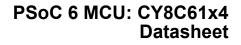

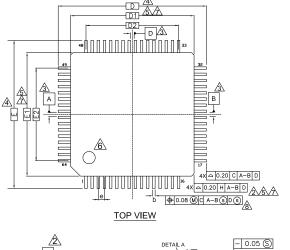

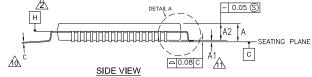

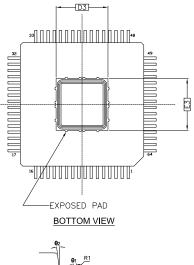

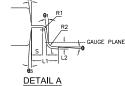

# Packages

■ 80-TQFP, 64-TQFP, 68-QFN

# **Device Identification and Revisions**

- Product line ID (12-bit): 0x10E

- Major/Minor die revision ID: 1/3

- Firmware Revisions: ROM Boot: 8.1, Flash Boot: 3.1.0.528 (see Boot Code section)

This product line has a JTAG ID which is available through the SWJ interface. It is a 32-bit ID, where:

- The most significant digit is the device revision, based on the Major Die Revision

- The next four digits correspond to the part number, for example "E4B0" as a hexadecimal number

- The three least significant digits are the manufacturer ID, in this case "069" as a hexadecimal number

The Silicon ID system call can be used by firmware to get Silicon ID and ROM Boot data. For more information, see the technical reference manual (TRM).

The Flash Boot version can be read directly from designated addresses 0x1600 2004 and 0x1600 2018. For more information, see the technical reference manual (TRM).

# Contents

| Development Ecosystem          | 4 |

|--------------------------------|---|

| PSoC 6 MCU Resources           | 4 |

| ModusToolbox Software          | 5 |

| Blocks and Functionality       | 6 |

| Functional Description         | 8 |

| CPU and Memory Subsystem       | 8 |

| System Resources               |   |

| Programmable Analog Subsystems |   |

| Programmable Digital           |   |

| Fixed-Function Digital         |   |

| GPIO                           |   |

| CapSense Subsystem             |   |

| Pinouts                        |   |

| Power Supply Considerations    |   |

| Electrical Specifications      |   |

| Absolute Maximum Ratings       |   |

| Device-Level Specifications    |   |

|                                |   |

| Analog Peripherals                      | 44 |

|-----------------------------------------|----|

| Digital Peripherals                     | 54 |

| Memory                                  | 57 |

| System Resources                        | 58 |

| Ordering Information                    | 63 |

| PSoC 6 MPN Decoder                      | 63 |

| Packaging                               | 65 |

| Acronyms                                | 69 |

| Document Conventions                    |    |

| Units of Measure                        | 71 |

| Revision History                        | 72 |

| Sales, Solutions, and Legal Information | 73 |

| Worldwide Sales and Design Support      | 73 |

| Products                                | 73 |

| PSoC® Solutions                         | 73 |

| Cypress Developer Community             | 73 |

| Technical Support                       |    |

|                                         |    |

# **Development Ecosystem**

# **PSoC 6 MCU Resources**

Cypress provides a wealth of data at www.cypress.com to help you select the right PSoC device and quickly and effectively integrate it into your design. The following is an abbreviated list of resources for PSoC 6 MCU:

- Overview: PSoC Portfolio, PSoC Roadmap

- Product Selectors: PSoC 6 MCU

- Application Notes cover a broad range of topics, from basic to advanced level, and include the following:

AN221774: Getting Started with PSoC 6 MCU

- □ AN218241: PSoC 6 MCU Hardware Design Guide

- □ AN213924: PSoC 6 MCU Device Firmware Update Guide

- □ AN215656: PSoC 6 MCU Dual-CPU System Design

- □ AN219528: PSoC 6 MCU Power Reduction Techniques

- □ AN2213526.1 SOC 0 MCO 1 ower reduction rechniques

- □ AN85951: PSoC 4, PSoC 6 MCU CapSense Design Guide

- Code Examples demonstrate product features and usage, and are also available on Cypress GitHub repositories.

- Technical Reference Manuals (TRMs) provide detailed descriptions of PSoC 6 MCU architecture and registers.

- PSoC 6 MCU Programming Specification provides the information necessary to program PSoC 6 MCU nonvolatile memory

- Development Tools

- □ The ModusToolbox<sup>®</sup> software enables cross platform code development with a robust suite of tools and software libraries

- □ There is no kit available for the PSoC 61 product line. However, the CY8CKIT-062S4 PSoC 62S4 Pioneer Kit is available: a low-cost hardware platform that enables design and debug of the PSoC 62 CY8C62x5 product line.

- PSoC 6 CAD libraries provide footprint and schematic support for common tools. BSDL files and IBIS models are also available.

- Training Videos are available on a wide range of topics including the PSoC 6 MCU 101 series

- Cypress Developer Community enables connection with fellow PSoC developers around the world, 24 hours a day, 7 days a week, and hosts a dedicated PSoC 6 MCU Community

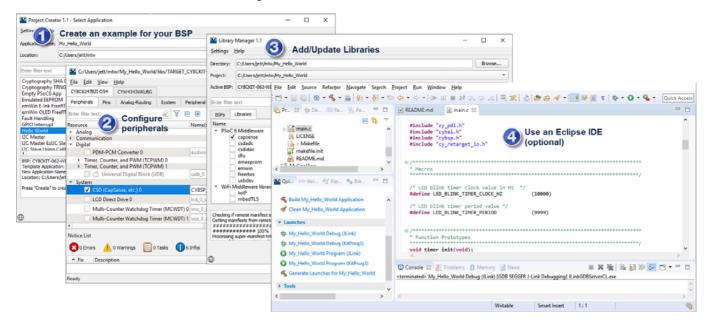

## ModusToolbox Software

ModusToolbox Software is Cypress' comprehensive collection of multi-platform tools and software libraries that enable an immersive development experience for creating converged MCU and wireless systems. It is:

- Comprehensive it has the resources you need

- Flexible you can use the resources in your own workflow

- Atomic you can get just the resources you want

Cypress provides a large collection of code repositories on GitHub. This includes:

- Board Support Packages (BSPs) aligned with Cypress kits

- Low-level resources, including a hardware abstraction layer (HAL) and peripheral driver library (PDL)

- Middleware enabling industry-leading features such as CapSense<sup>®</sup>, Bluetooth Low Energy, and mesh networks

- An extensive set of thoroughly tested code example applications

**Note:** The HAL provides a high-level, simplified interface to configure and use the hardware blocks on Cypress MCUs. It is a generic interface that can be used across multiple product families. For example, it wraps the PSoC 6 PDL with a simplified API, but the PDL exposes all low-level peripheral functionality. You can leverage the HAL's simpler and more generic interface for most of an application, even if one portion requires finer-grained control.

ModusToolbox Software is IDE-neutral and easily adaptable to your workflow and preferred development environment. It includes a project creator, peripheral and library configurators, a library manager, as well as the optional Eclipse IDE for ModusToolbox. For information on using Cypress tools, refer to the documentation delivered with ModusToolbox software, and AN228571: Getting Started with PSoC 6 MCU on ModusToolbox.

#### Figure 1. ModusToolbox Software Tools

# **Blocks and Functionality**

Figure 2 shows the major subsystems and a simplified view of their interconnections. The color coding shows the lowest power mode where a block is still functional. For example, the SRAM is functional down to Sleep Mode.

#### Figure 2. Block Diagram

There are three debug access ports, one each for CM4 and CM0+, and a system port.

PSoC 6 MCU devices include extensive support for programming, testing, debugging, and tracing both hardware and firmware. All device interfaces can be permanently disabled (device security) for applications concerned about attacks due to a maliciously reprogrammed device or attempts to defeat security by starting and interrupting flash programming sequences. All programming, debug, and test interfaces are disabled when maximum device security is enabled. The security level is settable by the user.

Complete debug-on-chip functionality enables full device debugging in the final system using the standard production device. It does not require special interfaces, debugging pods, simulators, or emulators. Only the standard programming connections are required to fully support debug.

The Eclipse IDE for ModusToolbox provides fully integrated programming and debug support for these devices. The SWJ (SWD and JTAG) interface is fully compatible with industry-standard third party probes. With the ability to disable debug features, with very robust flash protection, and by allowing customer-proprietary functionality to be implemented in on-chip programmable blocks, PSoC 6 MCU provides multiple levels of security.

# **Functional Description**

The following sections provide an overview of the features, capabilities and operation of each functional block identified in the block diagram in Figure 2. For more detailed information, refer to the following documentation:

■ Board Support Package (BSP) Documentation

BSPs are available on GitHub. They are aligned with Cypress kits and provide files for basic device functionality such as hardware configuration files, startup code, and linker files. The BSP also includes other libraries that are required to support a kit. Each BSP has its own documentation, but typically includes an API reference such as the example here. This search link finds all currently available BSPs on the Cypress GitHub site.

■ Hardware Abstraction Layer API Reference Manual

The Cypress Hardware Abstraction Layer (HAL) provides a high-level interface to configure and use hardware blocks on Cypress MCUs. It is a generic interface that can be used across multiple product families. You can leverage the HAL's simpler and more generic interface for most of an application, even if one portion requires finer-grained control. The HAL API Reference provides complete details. Example applications that use the HAL download it automatically from the GitHub repository.

Peripheral Driver Library (PDL) Application Programming Interface (API) Reference Manual

The Peripheral Driver Library (PDL) integrates device header files and peripheral drivers into a single package and supports all PSoC 6 MCU product lines. The drivers abstract the hardware functions into a set of easy-to-use APIs. These are fully documented in the PDL API Reference. Example applications that use the PSoC 6 PDL download it automatically from the GitHub repository.

■ Architecture Technical Reference Manual (TRM)

The architecture TRM provides a detailed description of each resource in the device. This is the next reference to use if it is necessary to understand the operation of the hardware below the software provided by PDL. It describes the architecture and functionality of each resource and explains the operation of each resource in all modes. It provides specific guidance regarding the use of associated registers.

Register Technical Reference Manual

The register TRM provides a complete list of all registers in the device. It includes the breakdown of all register fields, their possible settings, read/write accessibility, and default states. All registers that have a reasonable use in typical applications have functions to access them from within PDL. Note that ModusToolbox and PDL may provide software default conditions for some registers that are different from and override the hardware defaults.

# **CPU and Memory Subsystem**

PSoC 6 has multiple bus masters, as Figure 2 shows. They are: CPUs, DMA controllers, QSPI,USB, and a Crypto block. Generally, all memory and peripherals can be accessed and shared by all bus masters through multi-layer Arm AMBA high-performance bus (AHB) arbitration. Accesses between CPUs can be synchronized using an inter-processor communication (IPC) block.

#### CPUs

There are two Arm Cortex CPUs:

The Cortex-M4 (CM4) has single-cycle multiply, a floating-point unit (FPU), and a memory protection unit (MPU). It can run at up to 150 MHz. This is the main CPU, designed for a short interrupt response time, high code density, and high throughput.

CM4 implements a version of the Thumb instruction set based on Thumb-2 technology (defined in the *Armv7-M Architecture Reference Manual*).

The Cortex-M0+ (CM0+) has single-cycle multiply, and an MPU. It can run at up to 100 MHz; however, for CM4 speeds above 100 MHz, CM0+ and bus peripherals are limited to half the speed of CM4. Thus, for CM4 running at 150 MHz, CM0+ and peripherals are limited to 75 MHz.

CM0+ is the secondary CPU; it is used to implement system calls and device-level security, safety, and protection features.

CM0+ implements the Armv6-M Thumb instruction set (defined in the *Armv6-M Architecture Reference Manual*).

The CPUs have the following power draw, at  $V_{DDD}$  = 3.3 V and using the internal buck regulator:

# Table 1. Active Current Slope at $V_{DDD}$ = 3.3 V Using the Internal Buck Regulator

|     |            | System Power Mode |           |

|-----|------------|-------------------|-----------|

|     |            | ULP               | LP        |

| CPU | Cortex-M0+ | 15 μA/MHz         | 20 μA/MHz |

|     | Cortex-M4  | 22 μA/MHz         | 40 μA/MHz |

The CPUs can be selectively placed in their Sleep and Deep Sleep power modes as defined by Arm.

Both CPUs have nested vectored interrupt controllers (NVIC) for rapid and deterministic interrupt response, and wakeup interrupt controllers (WIC) for CPU wakeup from Deep Sleep power mode.

The CPUs have extensive debug support. PSoC 6 has a debug access port (DAP) that acts as the interface for device programming and debug. An external programmer or debugger (the "host") communicates with the DAP through the device serial wire debug (SWD) or Joint Test Action Group (JTAG) interface pins. Through the DAP (and subject to device security restrictions), the host can access the device memory and peripherals as well as the registers in both CPUs.

Each CPU offers debug and trace features as follows:

CM4 supports six hardware breakpoints and four watchpoints, 4-bit embedded trace macrocell (ETM), serial wire viewer (SWV), and printf()-style debugging through the single wire output (SWO) pin.

CM0+ supports four hardware breakpoints and two watchpoints, and a micro trace buffer (MTB) with 4 KB dedicated RAM.

PSoC 6 also has an Embedded Cross Trigger for synchronized debugging and tracing of both CPUs.

#### Interrupts

This product line has 175system and peripheral interrupt sources and supports interrupts and system exception on both CPUs. CM4 has 175 interrupt request lines (IRQ), with the interrupt source 'n' directly connected to IRQn. CM0+ has eight interrupts IRQ[7:0] with configurable mapping of one or more interrupt sources to any of the IRQ[7:0]. CM0+ also supports eight internal (software only) interrupts.

Each interrupt supports configurable priority levels (eight levels for CM4 and four levels for CM0+). Up to four system interrupts can be mapped to each of the CPUs' non-maskable interrupts (NMI). Up to 45 interrupt sources are capable of waking the device from Deep Sleep power mode using the WIC. Refer to the technical reference manual for details.

#### InterProcessor Communication (IPC)

In addition to the Arm SEV and WFE instructions, a hardware InterProcessor Communication (IPC) block is included. It includes 16 IPC channels and 16 IPC interrupt structures. The IPC channels can be used to implement data communication between the processors. Each IPC channel also implements a locking scheme which can be used to manage shared resources. The IPC interrupts let one processor interrupt the other, signaling an event. This is used to trigger events such as notify and release of the corresponding IPC channels. Some IPC channels and other resources are reserved, as Table 2 shows:

| Resources Available                                       | Resources Consumed   |

|-----------------------------------------------------------|----------------------|

| IPC channels,<br>16 available                             | 8 reserved           |

| IPC interrupts,<br>16 available                           | 8 reserved           |

| Other interrupts                                          | 1 reserved           |

| CM0+ NMI                                                  | Reserved             |

| Other resources:<br>clock dividers, DMA<br>channels, etc. | 1 CM0+ interrupt mux |

#### Direct Memory Access (DMA) Controllers

This product line has three DMA controllers, with 32, 30, and 2 channels, which support CPU-independent accesses to memory and peripherals. The descriptors for DMA channels can be in SRAM or flash. Therefore, the number of descriptors are limited only by the size of the memory. Each descriptor can transfer data in two nested loops with configurable address increments to the

source and destination. The size of data transfer per descriptor varies based on the type of DMA channel. Refer to the technical reference manual for details.

#### Cryptography Accelerator (Crypto)

This subsystem consists of hardware implementation and acceleration of cryptographic functions and random number generators.

The Crypto subsystem supports the following:

- Encryption/Decryption Functions

- □ Data Encryption Standard (DES)

- Triple DES (3DES)

- □ Advanced Encryption Standard (AES) (128-, 192-, 256-bit)

- Elliptic Curve Cryptography (ECC)

- RSA cryptography functions

- Hashing functions

- □ Secure Hash Algorithm (SHA)

- □ SHA-1

- □ SHA-224/-256/-384/-512

- Message authentication functions (MAC)

Hashed message authentication code (HMAC)

Cipher-based message authentication code (CMAC)

- 32-bit cyclic redundancy code (CRC) generator

- Random number generators

- □ Pseudo random number generator (PRNG)

- □ True random number generator (TRNG)

#### Protection Units

This product line has multiple types of protection units to control erroneous or unauthorized access to memory and peripheral registers. CM4 and CM0+ have Arm MPUs for protection at the bus master level. Other bus masters use additional MPUs. Shared memory protection units (SMPUs) help implement memory protection for memory/ resources that are shared among multiple bus masters. Peripheral protection units (PPU) are similar to SMPUs but are designed for protecting the peripheral register space.

Protection units support memory and peripheral access attributes including address range, read/write, code/data, privilege level, secured/non-secured, and protection context. Some protection unit resources are reserved for system usage; see the technical reference manual (TRM) for details.

## Memory

PSoC 6 contains flash, SRAM, ROM, and eFuse memory blocks.

#### Flash

There is up to 256 KB of application flash, organized in 128 KB sectors. There is also a 32 KB supervisory flash (SFlash) sector.

Data stored in SFlash includes device trim values, Flash Boot code, and encryption keys. After the device transitions into the "Secure" lifecycle stage, SFlash can no longer be changed.

The flash has 128-bit-wide accesses to reduce power. This enables flash updates during code execution. Write operations can be performed at the row level. A row is 512 bytes. Read operations are supported in both System Low Power and Ultra-Low Power modes, however write operations may not be performed in System Ultra-Low Power mode.

The flash controller has two caches, one for each CPU. Each cache is 8 KB, with 4-way set associativity.

### SRAM

Up to 128 KB of SRAM is provided. Power control and retention granularity is implemented in 32 KB blocks allowing the user to control the amount of memory retained in Deep Sleep. Memory is not retained in Hibernate mode.

#### ROM

The 64-KB ROM, also referred to as the supervisory ROM (SROM), provides code (ROM Boot) for several system functions. The ROM contains device initialization, flash write, security, eFuse programming, and other system-level routines. ROM code is executed only by the CM0+ CPU, in protection context 0. A system function can be initiated by either CPU, or through the DAP. This causes an NMI in CM0+, which causes CM0+ to execute the system function.

#### eFuse

A one-time-programmable (OTP) eFuse array consists of 1024 bits, of which 648 are reserved for system use such as die ID, device ID, initial trim settings, device life cycle, and security settings. The remaining bits are available for storing security key information, hash values, unique IDs or similar custom content.

Each fuse is individually programmed; once programmed (or "blown"), its state cannot be changed. Blowing a fuse transitions it from the default state of 0 to 1. To program an eFuse,  $V_{DDIO0}$  must be at 2.5 V ±5%, at 14 mA.

Because blowing an eFuse is an irreversible process, programming is recommended only in mass production programming under controlled factory conditions. For more information, see PSoC 6 MCU Programming Specifications.

## Boot Code

Two blocks of code, ROM Boot and Flash Boot, are pre-programmed into the device and work together to provide device startup and configuration, basic security features, life-cycle stage management and other system functions.

#### ROM Boot

On a device reset, the boot code in ROM is the first code to execute. This code performs the following:

- Integrity checks of flash boot code

- Device trim setting (calibration)

- Setting the device protection units

- Setting device access restrictions for lifecycle states

ROM cannot be changed and acts as the root of trust in a secured system.

Flash Boot

Flash boot is firmware stored in SFlash that ensures that only a validated application may run on the device. It also ensures that the firmware image has not been modified, such as by a malicious third party.

Flash boot:

- Is validated by ROM Boot

- □ Runs after ROM Boot and before the user application

- Enables system calls

- Configures the Debug Access Port

- Launches the user application

If the user application cannot be validated, then flash boot ensures that the device is transitioned into a safe state.

#### Memory Map

Both CPUs have a fixed address map, with shared access to memory and peripherals. The 32-bit (4 GB) address space is divided into Arm-defined regions shown in Table 3. Note that Code can be executed from the code and External RAM regions.

| Table 3. A | Address | Map f | or CM4 | and CM0+ |

|------------|---------|-------|--------|----------|

|------------|---------|-------|--------|----------|

| Address Range             | Name                         | Use                                                                                                                                        |

|---------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0000 0000 – 0x1FFF FFFF | Code                         | Program code region.<br>Data can also be placed<br>here. It includes the<br>exception vector table,<br>which starts at address<br>0.       |

| 0x2000 0000 – 0x3FFF FFFF | SRAM                         | Data region. This<br>region is not supported<br>in PSoC 6.                                                                                 |

| 0x4000 0000 – 0x5FFF FFFF | Peripheral                   | All peripheral registers.<br>Code cannot be<br>executed from this<br>region. CM4 bit-band in<br>this region is not<br>supported in PSoC 6. |

| 0x6000 0000 – 0x9FFF FFFF | External<br>RAM              | SMIF or Quad SPI, (see<br>the Quad-SPI/Serial<br>Memory Interface<br>(SMIF) section). Code<br>can be executed from<br>this region.         |

| 0xA000 0000 – 0xDFFF FFFF | External<br>Device           | Not used.                                                                                                                                  |

| 0xE000 0000 – 0xE00F FFFF | Private<br>Peripheral<br>Bus | Provides access to<br>peripheral registers<br>within the CPU core.                                                                         |

| 0xE010 A000 – 0xFFFF FFFF | Device                       | Device-specific system registers.                                                                                                          |

The device memory map shown in Table 4 applies to both CPUs. That is, the CPUs share access to all PSoC 6 MCU memory and peripheral registers.

Table 4. Internal Memory Address Map for CM4 and CM0+

| Address Range             | Memory Type       | Size            |

|---------------------------|-------------------|-----------------|

| 0x0000 0000 – 0x0000 FFFF | ROM               | 64 KB           |

| 0x0800 0000 –0x0801 FFFF  | SRAM              | Up to<br>128 KB |

| 0x1000 0000 –0x1003 FFFF  | Application flash | Up to<br>256 KB |

| 0x1600 0000 – 0x1600 7FFF | Supervisory flash | 32 KB           |

Note that the PSoC 6 SRAM is located in the Arm Code region for both CPUs (see Table 3). There is no physical memory located in the CPUs' Arm SRAM regions.

## System Resources

#### Power System

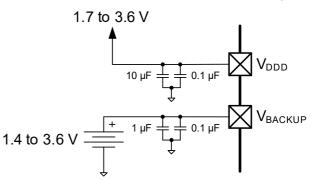

The power system provides assurance that voltage levels are as required for each respective mode and will either delay mode entry (on power-on reset (POR), for example) until voltage levels are as required for proper function or generate resets (brown-out detect (BOD)) when the power supply drops below specified levels. The design guarantees safe chip operation between power supply voltage dropping below specified levels (for example, below 1.7 V) and the reset occurring. There are no voltage sequencing requirements. The V<sub>DDD</sub> supply (1.7 to 3.6 V) powers an on-chip buck regulator or a low-dropout regulator (LDO), selectable by the user. In addition, both the buck and the LDO offer a selectable (0.9 or

1.1 V) core operating voltage ( $\dot{V}_{CCD}$ ).The selection lets users choose between two system power modes:

- System Low Power (LP) operates V<sub>CCD</sub> at 1.1 V and offers high performance, with no restrictions on device configuration.

- System Ultra Low Power (ULP) operates V<sub>CCD</sub> at 0.9 V for exceptional low power, but imposes limitations on maximum clock speeds.

In addition, a backup domain adds an "always on" functionality using a separate power domain supplied by a backup supply  $(V_{BACKUP})$  such as a battery or supercapacitor. It includes a real-time clock (RTC) with alarm feature, supported by a 32.768-kHz watch crystal oscillator (WCO), and power-management IC (PMIC) control. Pin 5 of Port 0 (P0.5) can be assigned as an enable signal for an external PMIC.

RTC alarms can be used as a trigger for the PMIC enable signal. The backup domain can generate a wake-up interrupt to the chip via the RTC timers or an external input.

#### Power Modes

PSoC 6 MCUcan operate in four system and three CPU power modes. These modes are intended to minimize the average power consumption in an application. For more details on power modes and other power-saving configuration options, see the application note, AN219528: PSoC 6 MCU Low-Power Modes and Power Reduction Techniques and the Architecture TRM, Power Modes chapter.

Power modes supported by PSoC 6 MCUs, in the order of decreasing power consumption, are:

- System Low Power (LP) All peripherals and CPU power modes are available at maximum speed

- System Ultra Low Power (ULP) All peripherals and CPU power modes are available, but with limited speed

- CPU Active CPU is executing code in system LP or ULP mode

- CPU Sleep CPU code execution is halted in system LP or ULP mode

- CPU Deep Sleep CPU code execution is halted and system Deep Sleep is requested in system LP or ULP mode

- System Deep Sleep Only low-frequency peripherals are available after both CPUs enter CPU Deep Sleep mode

- System Hibernate Device and I/O states are frozen and the device resets on wakeup

CPU Active, Sleep, and Deep Sleep are standard Arm-defined power modes supported by the Arm CPU instruction set architecture (ISA). LP, ULP, Deep Sleep and Hibernate modes are additional low-power modes supported by PSoC 6 MCU.

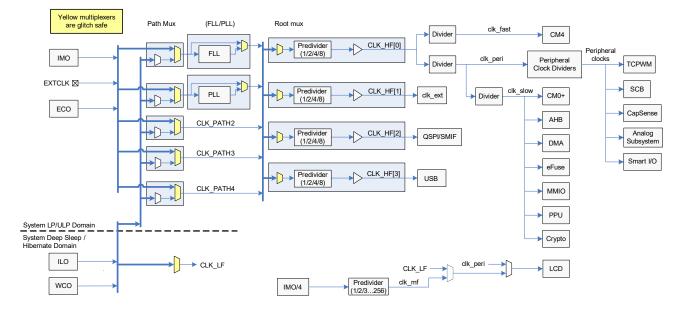

#### Clock System

Figure 3 shows that the clock system of this product line consists of the following:

- Internal main oscillator (IMO)

- Internal low-speed oscillator (ILO)

- Watch crystal oscillator (WCO)

- External MHz crystal oscillator (ECO)

- External clock input

- One phase-locked loop (PLL)

- One frequency locked loop (FLL)

Clocks may be buffered and brought out to a pin on a smart I/O port.

The default clocking when the application starts is CLK\_HF[0] being driven by the IMO and the FLL. CLK\_HF[0], clk\_fast, clk\_peri, and clk\_slow are all either 50 MHz (LP mode) or 25 MHz (ULP mode). All other clocks, including all peripheral clocks, are off.

#### Internal Main Oscillator (IMO)

The IMO is the primary source of internal clocking. It is trimmed at the factory to achieve the specified accuracy. The IMO frequency is 8 MHz and tolerance is  $\pm 2\%$ .

#### Internal Low-speed Oscillator (ILO)

The ILO is a very low power oscillator, nominally 32 kHz, which operates in all power modes. The ILO can be calibrated against a higher accuracy clock for better accuracy.

#### Figure 3. Clocking Diagram

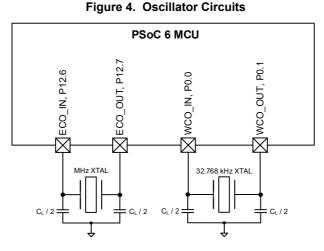

#### External Crystal Oscillators

Figure 4 shows all of the external crystal oscillator circuits for this product line. The component values shown are typical; check the ECO Specifications for the crystal values, and the crystal datasheet for the load capacitor values. The ECO and WCO require balanced external load capacitors. For more information, see the TRM and AN218241, PSoC 6 MCU Hardware Design Considerations.

The crystal oscillator can be sensitive to GPIO switching noise and requires the following constraints for reliable operation with a broad range of crystals over the range of 16 to 35 MHz:

- 1. Port 12 must be used in low slew rate (slow) mode which limits switching frequency to 2.5 MHz.

- 2. Port 11, which includes the QSPI interface, must be limited to 60-MHz operation with the QSPI and in Drive Mode 2; please see the TRM for details.

For more information, see Table 5 and the GPIO section.

#### Watchdog Timers (WDT, MCWDT)

PSoC 6 MCU has one WDT and two multi-counter WDTs (MCWDT). The WDT has a 16-bit free-running counter. Each MCWDT has two 16-bit counters and one 32-bit counter, with multiple operating modes. All of the 16-bit counters can generate a watchdog device reset. All of the counters can generate an interrupt on a match event.

The WDT is clocked by the ILO. It can do interrupt/wakeup generation in LP/ULP, Deep Sleep, and Hibernate power modes. The MCWDTs are clocked by LFCLK (ILO or WCO). It can do periodic interrupt / wakeup generation in LP/ULP and Deep Sleep power modes.

#### Clock Dividers

Integer and fractional clock dividers are provided for peripheral use and timing purposes. There are:

- Four 8-bit clock dividers

- Eight 16-bit integer clock dividers

- Two 16.5-bit fractional clock dividers

- One 24.5-bit fractional clock divider

#### Trigger Routing

PSoC 6 MCU contains a trigger multiplexer block. This is a collection of digital multiplexers and switches that are used for routing trigger signals between peripheral blocks and between GPIOs and peripheral blocks.

There are two types of trigger routing. Trigger multiplexers have reconfigurability in the source and destination. There are also hardwired switches called "one-to-one triggers", which connect a specific source to a destination. The user can enable or disable the route.

### Reset

PSoC 6 MCU can be reset from a variety of sources:

- Power-on reset (POR) to hold the device in reset while the power supply ramps up to the level required for the device to function properly. POR activates automatically at power-up.

- Brown-out detect (BOD) reset to monitor the digital voltage supply V<sub>DDD</sub> and generate a reset if V<sub>DDD</sub> falls below the minimum required logic operating voltage.

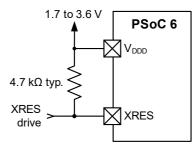

- External reset dedicated pin (XRES) to reset the device using an external source. The XRES pin is active low. It can be connected either to a pull-up resistor to V<sub>DDD</sub>, or to an active drive circuit, as Figure 5 shows. If a pull-up resistor is used, select its value to minimize current draw when the pin is pulled low; 4.7 kΩ to 100 kΩ is typical.

#### Figure 5. XRES Connection Diagram

- Watchdog timer (WDT or MCWDT) to reset the device if firmware fails to service it within a specified timeout period.

- Software-initiated reset to reset the device on demand using firmware.

- Logic-protection fault can trigger an interrupt or reset the device if unauthorized operating conditions occur; for example, reaching a debug breakpoint while executing privileged code.

- Hibernate wakeup reset to bring the device out of the system Hibernate low-power mode.

Reset events are asynchronous and guarantee reversion to a known state. Some of the reset sources are recorded in a register, which is retained through reset and allows software to determine the cause of the reset.

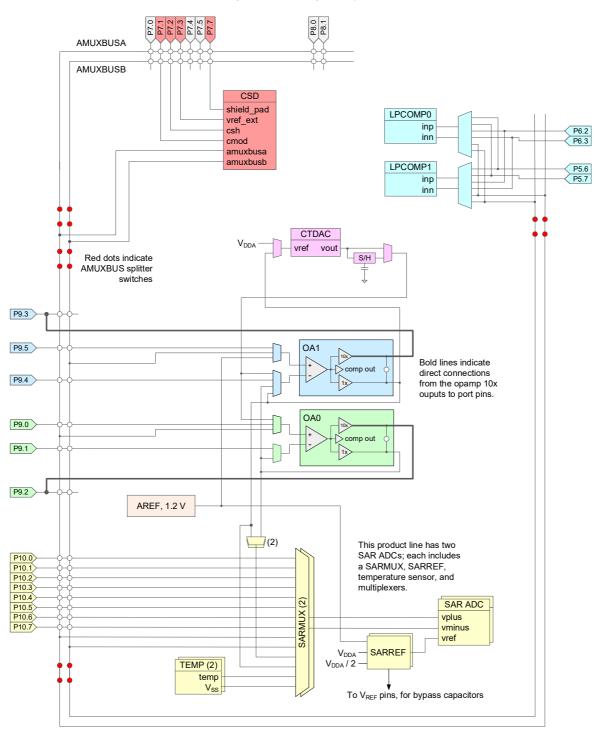

### **Programmable Analog Subsystems**

#### 12-bit SAR ADC

The two 12-bit, 2-Msps SAR ADCs can operate at a maximum clock rate of 36 MHz and require a minimum of 18 clocks at that frequency to do a 12-bit conversion. One of three internal references may be used for an ADC reference voltage:  $V_{DDA}$ ,  $V_{DDA/2}$ , and an analog reference (AREF). AREF is nominally 1.2 V, trimmed to ±1%; see Table 22). An external reference may also be used, by driving a  $V_{REF}$  pin. When using  $V_{DDA/2}$  or AREF as a reference, an external bypass capacitor may be connected to a  $V_{REF}$  pin to improve performance in noisy conditions. These reference options allow ratio-metric readings or absolute readings at the accuracy of the reference used. The input range of the ADCs is the full supply voltage between  $V_{SS}$  and  $V_{DDA}/V_{DDIOA}$ . The ADCs may be configured with a mix of single ended and differential signals in the same configuration.

The ADCs' sample-and-hold (S/H) aperture is programmable to allow sufficient time for signals with a high impedance to settle, if required. System performance is 65 dB for true 12-bit precision provided appropriate references are used and system noise levels permit it.

The ADCs are connected to fixed sets of pins through input sequencers. A sequencer cycles through the selected channels autonomously (sequencer scan) and does so with zero switching overhead (that is, the aggregate sampling bandwidth is equal to 2 Msps whether it is for a single channel or distributed over several channels). The result of each channel is buffered, so that an interrupt may be triggered only when a full scan of all channels is complete. Also, a pair of range registers can be set to detect and cause an interrupt if an input exceeds a minimum and/or maximum value. This allows fast detection of out-of-range values without having to wait for a sequencer scan to be completed and the CPU to read the values and check for out-of-range values in software. An ADC can also be connected, under firmware control, to most other GPIO pins via the analog multiplexer bus (AMUXBUS). The ADCs are not available in Hibernate mode. The ADC operating range is 1.71 to 3.6 V.

The ADCs have synchronous sampling, for applications such as power supply monitoring and motor control. A SAR ADC may be operated in Deep Sleep mode using a clock of either 2 MHz or 8 MHz (LPOSC).

#### Temperature Sensor

Each SAR ADC block contains a temperature sensor. The sensor consists of a diode biased by a current source. It can be disabled to save power. The temperature sensor may be connected directly to a SAR ADC as one of the measurement channels. The ADC digitizes the temperature sensor's output, and a Cypress-supplied software function may be used to convert the reading to a temperature, with calibration and linearization.

#### 12-bit Digital-Analog Converter

There is a 12-bit voltage mode DAC on the chip, which can settle in less than 2  $\mu$ s. The DAC may be driven by the DMA controllers to generate user-defined waveforms. The DAC output from the chip can either be the resistive ladder output (highly linear near ground) or a buffered output using an opamp in the CTBm block.

#### Continuous Time Block mini (CTBm) with Two Opamps

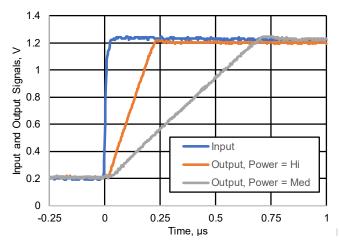

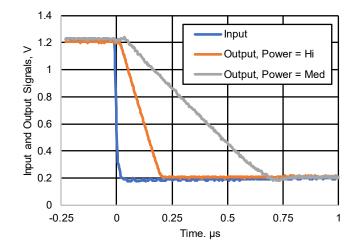

This block consists of two opamps, which have their inputs and outputs connected to pins and other analog blocks, as Figure 6 shows. They have three power modes (high, medium, and low) and a comparator mode. The opamps can be used to buffer SAR inputs and DAC outputs. The non-inverting inputs of these opamps can be connected to either of two pins, thus allowing independent sensors to be used at different times. The pin selection can be made via firmware.

The opamps also support operation in system Deep Sleep mode, with lower performance and reduced power consumption.

#### Low-Power Comparators

Two low-power comparators are provided, which can operate in all power modes. This allows other analog system resources to be disabled while retaining the ability to monitor external voltage levels during system Deep Sleep and Hibernate modes. The comparator outputs are normally synchronized to avoid metastability unless operating in an asynchronous power mode (Hibernate) where the system wake-up circuit is activated by a comparator-switch event.

Figure 6 shows an overview of the analog subsystem. This diagram is a high-level abstraction. See the TRM for detailed connectivity information.

Figure 6. Analog Subsystem

# **Programmable Digital**

#### Smart I/O

Smart I/O<sup>™</sup> is a programmable logic fabric that enables Boolean operations on signals traveling from device internal resources to the GPIO pins or on signals traveling into the device from external sources. The Smart I/O block sits between the GPIO pins and the high-speed I/O matrix (HSIOM) and is dedicated to a single port.

This product line has one Smart I/O block, on Port 9.When the Smart I/O is not enabled, all signals on Port 9 bypass the Smart I/O hardware.

Smart I/O supports:

- System Deep Sleep operation

- Boolean operations without CPU intervention

- Asynchronous or synchronous (clocked) operation

The Smart I/O block contains a data unit (DU) and eight look up tables (LUTs).

The DU:

- Performs unique functions based on a selectable opcode.

- Can source input signals from internal resources, the GPIO port, or a value in the DU register.

Each LUT:

- Has four selectable input sources. The input signals may be sourced from another LUT, an internal resource, an external signal from a GPIO pin, or from the DU.

- Acts as a programmable Boolean logic table.

- Can be synchronous or asynchronous.

# **Fixed-Function Digital**

Timer/Counter/Pulse-width Modulator (TCPWM)

- The TCPWM supports the following operational modes:

- □ Timer-counter with compare

- Timer-counter with capture

- Quadrature decoding

- Pulse width modulation (PWM)

- Pseudo-random PWM

- PWM with dead time

- Up, down, and up/down counting modes.

- Clock prescaling (division by 1, 2, 4, ... 64, 128)

- Double buffering of compare/capture and period values

- Underflow, overflow, and capture/compare output signals

- Supports interrupt on:

- Terminal count Depends on the mode; typically occurs on overflow or underflow

- Capture/compare The count is captured to the capture register or the counter value equals the value in the compare register

- Complementary output for PWMs

Selectable start, reload, stop, count, and capture event signals for each TCPWM; with rising edge, falling edge, both edges, and level trigger options. The TCPWM has a Kill input to force outputs to a predetermined state.

In this device there are:

- Four 32-bit TCPWMs

- Eight 16-bit TCPWMs

Serial Communication Blocks (SCB)

This product line has six SCBs:

- Five can implement either I<sup>2</sup>C, UART, or SPI.

- One SCB (SCB #6) can operate in Deep Sleep mode with an external clock, this SCB can be either SPI slave or I<sup>2</sup>C slave.

**I<sup>2</sup>C Mode:** The SCB can implement a full multi-master and slave interface (it is capable of multimaster arbitration). This block can operate at speeds of up to 1 Mbps (Fast Mode Plus). It also supports EZI2C, which creates a mailbox address range and effectively reduces I<sup>2</sup>C communication to reading from and writing to an array in memory. The SCB supports a 256-byte FIFO for receive and transmit.

The SCB is compatible with  $I^2C$  standard-mode, Fast Mode, and Fast Mode Plus devices as defined in the NXP  $I^2C$ -bus specification and user manual (UM10204). The  $I^2C$  bus I/O is implemented with GPIOs in open-drain mode.

**UART Mode:** This is a full-feature UART operating at up to 8 Mbps. It supports automotive single-wire interface (LIN), infrared interface (IrDA), and SmartCard (ISO7816) protocols, all of which are minor variants of the basic UART protocol. In addition, it supports the 9-bit multiprocessor mode that allows the addressing of peripherals connected over common RX and TX lines. Common UART functions such as parity error, break detect, and frame error are supported. A 256-byte FIFO allows much greater CPU service latencies to be tolerated.

**SPI Mode:** The SPI mode supports full Motorola SPI, TI Secure Simple Pairing (SSP) (essentially adds a start pulse that is used to synchronize SPI Codecs), and National Microwire (half-duplex form of SPI). The SPI block supports an EZSPI mode in which the data interchange is reduced to reading and writing an array in device SRAM. The SPI interface operates with a 25-MHz clock.

#### USB Full-Speed Device Interface

PSoC 6 has a full-speed USB device interface. The device can have up to eight endpoints. A 512-byte SRAM buffer is provided and DMA is supported.

**Note:** In this product line USB is available only in the 68-QFN package.

Note: If the USB pins are not used, connect  $V_{DDUSB}$  to ground and leave the P14.0/USBDP and P14.1/USBDM pins unconnected.

#### CAN FD Block

This device has one CAN FD block, for industrial and automotive applications. The block includes time-stamp support and has a 4-KB message RAM. FD Data rates of up to 5 Mbps are supported. DMA transfers are supported.

#### Quad-SPI/Serial Memory Interface (SMIF)

A serial memory interface is provided, running at up to 80 MHz. It supports single, dual, and quad SPI configurations, and supports up to four external memory devices. It supports two modes of operation:

- Memory-mapped I/O (MMIO), a command mode interface that provides data access via the SMIF registers and FIFOs

- Execute in Place (XIP), in which AHB reads and writes are directly translated to SPI read and write transfers.

In XIP mode, the external memory is mapped into the CPU internal address space, enabling code execution directly from the external memory. To improve performance, a 4-KB cache is included. XIP mode also supports AES-128 on-the-fly encryption and decryption, enabling secured storage and access of code and data in the external memory.

#### LCD

This block drives LCD commons and segments; routing is available to most of the GPIOs. One to eight of the GPIOs must be used for commons, the rest can be used for segments.

The LCD block has two modes of operation: high speed (8 MHz) and low speed (32 kHz). Both modes operate in system LP, ULP, and Deep Sleep modes, however the low-speed mode operates with reduced contrast in system Deep Sleep mode. The 8-MHz IMO is available in system Deep Sleep mode, and can be used to generate a clock for the LCD block. Review the number of common and segment lines, viewing angle requirements, and prototype performance, and then select the appropriate LCD clock frequency before using system Deep Sleep mode.

# GPIO

This device has up to 62 GPIOs. The GPIO block implements the following:

- Eight drive strength modes:

- □ Analog input mode (input and output buffers disabled) □ Input only

- Weak pull-up with strong pull-down

- Strong pull-up with weak pull-down

#### Table 5. DRIVE\_SEL Values

- Open drain with strong pull-down

- □ Open drain with strong pull-up

- Strong pull-up with strong pull-down

- Weak pull-up with weak pull-down

- Input threshold select (CMOS or LVTTL)

- Hold mode for latching previous state (used for retaining the I/O state in system Hibernate mode)

- Selectable slew rates for dV/dt-related noise control to improve EMI

The pins are organized in logical entities called ports, which are up to 8 pins in width. Data output and pin state registers store, respectively, the values to be driven on the pins and the input states of the pins.

Every pin can generate an interrupt if enabled; each port has an interrupt request (IRQ) associated with it.

The port 3 pins are capable of overvoltage-tolerant (OVT) operation, where the input voltage may be higher than  $V_{DDD}$ . OVT pins are commonly used with I<sup>2</sup>C, to allow powering the chip OFF while maintaining a physical connection to an operating I<sup>2</sup>C bus without affecting its functionality.

GPIO pins can be ganged to source or sink higher values of current. GPIO pins, including OVT pins, may not be pulled up higher than the absolute maximum; see Electrical Specifications.

During power-on and reset, the pins are forced to the analog input drive mode, with input and output buffers disabled, so as not to crowbar any inputs and/or cause excess turn-on current.

A multiplexing network known as the high-speed I/O matrix (HSIOM) is used to multiplex between various peripheral and analog signals that may connect to an I/O pin.

Analog performance is affected by GPIO switching noise. In order to get the best Analog performance, the following frequency and drive mode constraints must be applied. The DRIVE\_SEL values (see Table 5) represent drive strengths (please see the CY8C61x4 Architecture and Register TRMs for further detail).

| Ports          | Max Frequency                                                   | Drive Strength for $V_{DDD} \le 2.7 V$ | Drive Strength for $V_{DDD} > 2.7 V$ |

|----------------|-----------------------------------------------------------------|----------------------------------------|--------------------------------------|

| Ports 0, 1     | 8 MHz                                                           | DRIVE_SEL 2                            | DRIVE_SEL 3                          |

| Port 2         | 50 MHz                                                          | DRIVE_SEL 1                            | DRIVE_SEL 2                          |

| Ports 3 to 10  | 16 MHz; 25 MHz for SPI                                          | DRIVE_SEL 2                            | DRIVE_SEL 3                          |

| Ports 11 to 12 | 80 MHz for SMIF (QSPI)                                          | DRIVE_SEL 1                            | DRIVE_SEL 2                          |

| Ports 9 and 10 | Slow slew rate setting for TQFP<br>Packages for ADC performance |                                        | No restrictions                      |

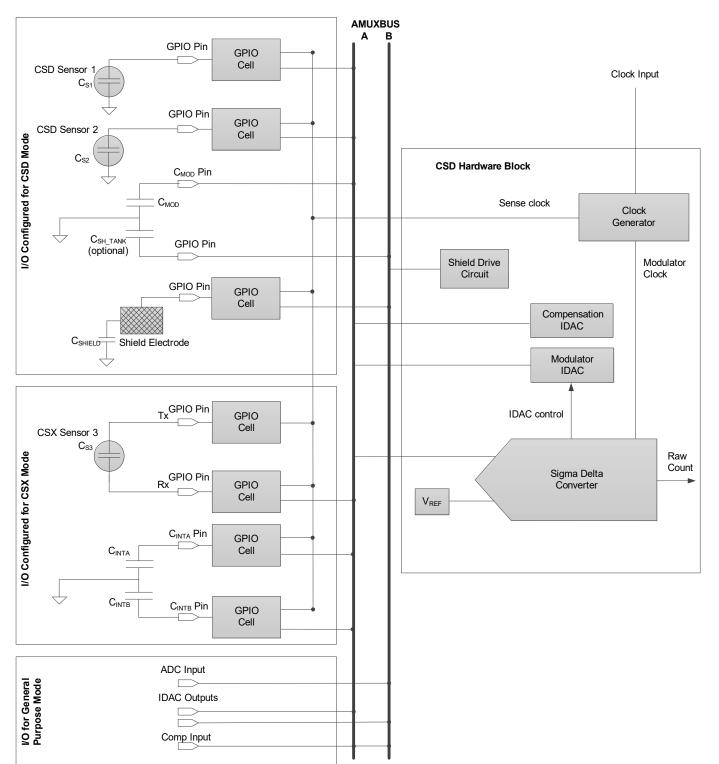

# CapSense Subsystem

CapSense is supported in PSoC 6 MCU through a CapSense sigma-delta (CSD) hardware block. It is designed for high-sensitivity self-capacitance and mutual-capacitance measurements, and is specifically built for user interface solutions.

In addition to CapSense, the CSD hardware block supports three general-purpose functions. These are available when CapSense is not being used. Alternatively, two or more functions can be time-multiplexed in an application under firmware control. The four functions supported by the CSD hardware block are:

- CapSense

- 10-bit ADC

- Programmable current sources (IDAC)

#### Comparator

#### CapSense

Capacitive touch sensors are designed for user interfaces that rely on human body capacitance to detect the presence of a finger on or near a sensor. Cypress CapSense solutions bring elegant, reliable, and simple capacitive touch sensing functions to applications including IoT, industrial, automotive, and home appliances.

The Cypress-proprietary CapSense technology offers the following features:

- Best-in-class signal-to-noise ratio (SNR) and robust sensing under harsh and noisy conditions

- Self-capacitance (CSD) and mutual-capacitance (CSX) sensing methods

- Support for various widgets, including buttons, matrix buttons, sliders, touchpads, and proximity sensors

- High-performance sensing across a variety of materials

- Best-in-class liquid tolerance

- SmartSense auto-tuning technology that helps avoid complex manual tuning processes

- Superior immunity against external noise

- Spread-spectrum clocks for low radiated emissions

- Gesture and built-in self-test libraries

- Ultra-low power consumption

- An integrated graphical CapSense tuner for real-time tuning, testing, and debugging

#### ADC

The CapSense subsystem slope ADC offers the following features:

- Selectable 8- or 10-bit resolution

- Selectable input range: GND to V<sub>REF</sub> and GND to V<sub>DDA</sub> on any GPIO input

- Measurement of V<sub>DDA</sub> against an internal reference without the use of GPIO or external components

## IDAC

The CSD block has two programmable current sources, which offer the following features:

- 7-bit resolution

- Sink and source current modes

- A current source programmable from 37.5 nA to 609 µA

- Two IDACs that can be used in parallel to form one 8-bit IDAC

#### Comparator

The CapSense subsystem comparator operates in the system Low Power and Ultra-Low Power modes. The inverting input is connected to an internal programmable reference voltage and the non-inverting input can be connected to any GPIO via the AMUXBUS.

#### CapSense Hardware Subsystem

Figure 7 shows the high-level hardware overview of the CapSense subsystem, which includes a delta sigma converter, internal clock dividers, a shield driver, and two programmable current sources.

The inputs are managed through analog multiplexed buses (AMUXBUS A/B). The input and output of all functions offered by the CSD block can be provided on any GPIO or on a group of GPIOs under software control, with the exception of the comparator output and external capacitors that use dedicated GPIOs.

Self-capacitance is supported by the CSD block using AMUXBUS A, an external modulator capacitor, and a GPIO for each sensor. There is a shield electrode (optional) for self-capacitance sensing. This is supported using AMUXBUS B and an optional external shield tank capacitor (to increase the drive capability of the shield driver) should this be required. Mutual-capacitance is supported by the CSD block using AMUXBUS A, two external integrated capacitors, and a GPIO for transmit and receive electrodes.

The ADC does not require an external component. Any GPIO that can be connected to AMUXBUS A can be an input to the ADC under software control. The ADC can accept  $V_{DDA}$  as an input without needing GPIOs (for applications such as battery voltage measurement).

The two programmable current sources (IDACs) in general-purpose mode can be connected to AMUXBUS A or B. They can therefore connect to any GPIO pin. The comparator resides in the delta-sigma converter. The comparator inverting input can be connected to the reference. Both comparator inputs can be connected to any GPIO using AMUXBUS B; see Figure 6. The reference has a direct connection to a dedicated GPIO; see Table 8.

The CSD block can operate in active and sleep CPU power modes, and seamlessly transition between LP and ULP system modes. It can be powered down in system Deep Sleep and Hibernate modes. Upon wakeup from Hibernate mode, the CSD block requires re-initialization. However, operation can be resumed without re-initialization upon exit from Deep Sleep mode, under firmware control.

Figure 7. CapSense Hardware Subsystem

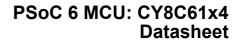

Figure 8 shows the high-level software overview. Cypress provides middleware libraries for CapSense, ADC, and IDAC on GitHub to enable quick integration. The Board Support Package for any kit with CapSense capabilities automatically includes the CapSense library in any application that uses the BSP.

User applications interact only with middleware to implement functions of the CSD block. The middleware interacts with underlying drivers to access hardware as necessary. The CSD driver facilitates time-multiplexing of the CSD hardware if more than one piece of CSD-related middleware is present in a project. It prevents access conflicts in this case.

ModusToolbox Software provides a CapSense configurator to enable fast library configuration. It also provides a tuner for performance evaluation and real-time tuning of the system. The tuner requires an EZI2C communication interface in the application to enable real-time tuning capability. The tuner can update configuration parameters directly in the device as well as in the configurator. CapSense and ADC middleware use the CSD interrupt to implement non-blocking sensing and A-to-D conversion. Therefore, interrupt service routines are a defined part of the middleware, which must be initialized by the application. Middleware and drivers can operate on either CPU. Cypress recommends using the middleware only in one CPU. If both CPUs must access the CSD driver, memory access should be managed in the application.

Refer to AN85951: PSoC 4 and PSoC 6 MCU CapSense Design Guide for more details on CSX sensing, CSD sensing, shield electrode usage and its benefits, and capacitive system design guidelines.

Refer to the API reference guides for CapSense, ADC, and IDAC available on GitHub.

Figure 8. CapSense Software/Firmware Subsystem

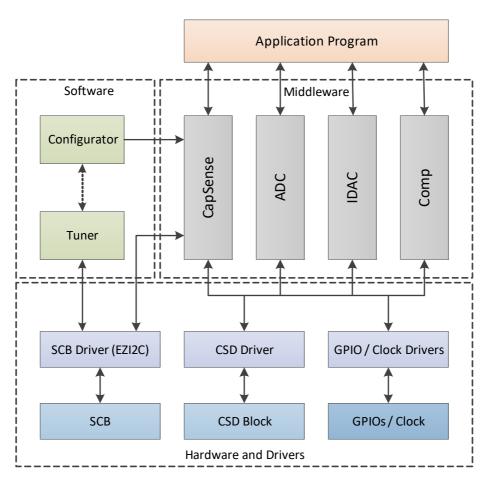

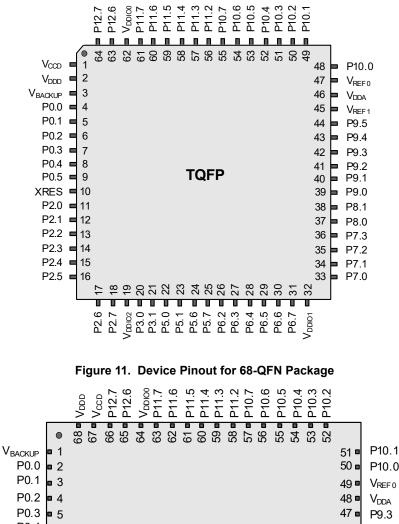

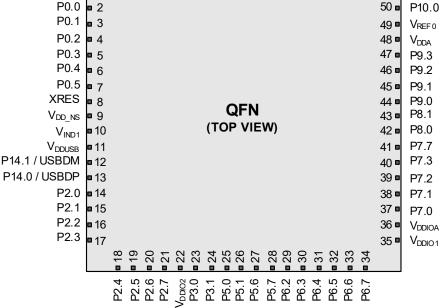

# **Pinouts**

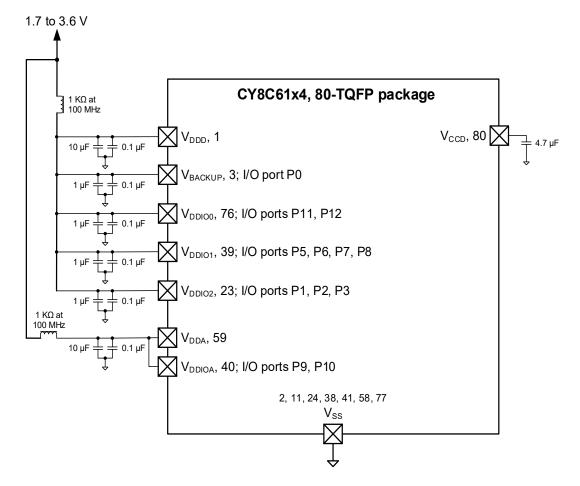

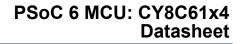

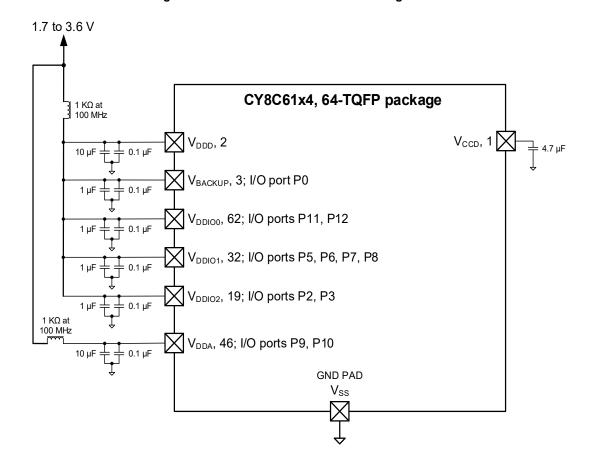

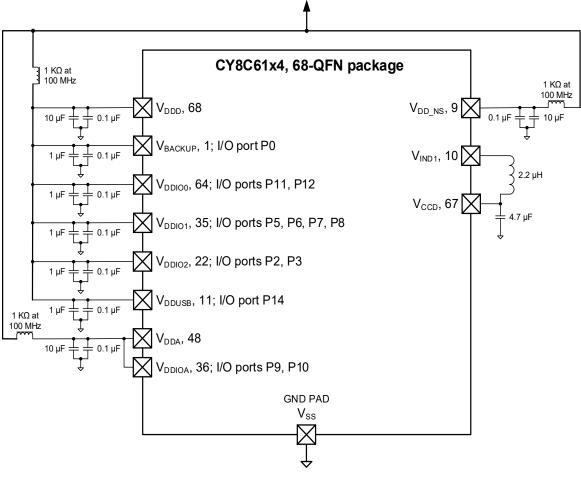

GPIO ports are powered by  $V_{DDx}$  pins as follows:

- P0: V<sub>BACKUP</sub>

- P1, P2, P3: V<sub>DDIO2</sub>. Port 3 pins are overvoltage tolerant (OVT).

- P5, P6, P7, P8: V<sub>DDIO1</sub>

- P9, P10: V<sub>DDIOA</sub>, V<sub>DDA</sub> (V<sub>DDIOA</sub>, when present, and V<sub>DDA</sub> must be connected together on the PCB)

- P11, P12: V<sub>DDIO0</sub>

- P14: V<sub>DDUSB</sub>

# Table 6. Packages and Pin Information

| Din                |                           | Package |         |

|--------------------|---------------------------|---------|---------|

| Pin                | 80-TQFP                   | 64-TQFP | 68-QFN  |

| V <sub>DDD</sub>   | 1                         | 2       | 68      |

| V <sub>CCD</sub>   | 80                        | 1       | 67      |

| V <sub>DDA</sub>   | 59                        | 46      | 48      |

| V <sub>DDIOA</sub> | 40                        | -       | 36      |

| V <sub>DDIO0</sub> | 76                        | 62      | 64      |

| V <sub>DDIO1</sub> | 39                        | 32      | 35      |

| V <sub>DDIO2</sub> | 23                        | 19      | 22      |

| VBACKUP            | 3                         | 3       | 1       |

| V <sub>DDUSB</sub> | -                         | -       | 11      |

| V <sub>SS</sub>    | 2, 11, 24, 38, 41, 58, 77 | GND PAD | GND PAD |

| V <sub>DD_NS</sub> | -                         | -       | 9       |

| V <sub>IND1</sub>  | -                         | -       | 10      |

| XRES               | 10                        | 10      | 8       |

| V <sub>REF</sub>   | 57, 60                    | 45, 47  | 49      |

| P0.0               | 4                         | 4       | 2       |

| P0.1               | 5                         | 5       | 3       |

| P0.2               | 6                         | 6       | 4       |

| P0.3               | 7                         | 7       | 5       |

| P0.4               | 8                         | 8       | 6       |

| P0.5               | 9                         | 9       | 7       |

| P1.0               | 12                        | -       | -       |

| P1.1               | 13                        | -       | -       |

| P1.2               | 14                        | -       | -       |

| P2.0               | 15                        | 11      | 14      |

| P2.1               | 16                        | 12      | 15      |

| P2.2               | 17                        | 13      | 16      |

| P2.3               | 18                        | 14      | 17      |

| P2.4               | 19                        | 15      | 18      |

| P2.5               | 20                        | 16      | 19      |

| P2.6               | 21                        | 17      | 20      |

| P2.7               | 22                        | 18      | 21      |

# Table 6. Packages and Pin Information (continued)

| Pin   | Package |         |        |

|-------|---------|---------|--------|

| Pin   | 80-TQFP | 64-TQFP | 68-QFN |

| P3.0  | 25      | 20      | 23     |

| P3.1  | 26      | 21      | 24     |

| P5.0  | 27      | 22      | 25     |

| P5.1  | 28      | 23      | 26     |

| P5.2  | 29      | -       | -      |

| P5.6  | 30      | 24      | 27     |

| P5.7  | 31      | 25      | 28     |

| P6.2  | 32      | 26      | 29     |

| P6.3  | 33      | 27      | 30     |

| P6.4  | 34      | 28      | 31     |

| P6.5  | 35      | 29      | 32     |

| P6.6  | 36      | 30      | 33     |

| P6.7  | 37      | 31      | 34     |

| P7.0  | 42      | 33      | 37     |

| P7.1  | 43      | 34      | 38     |

| P7.2  | 44      | 35      | 39     |

| P7.3  | 45      | 36      | 40     |

| P7.4  | 46      | -       | -      |

| P7.5  | 47      | -       | -      |

| P7.7  | 48      | -       | 41     |

| P8.0  | 49      | 37      | 42     |

| P8.1  | 50      | 38      | 43     |

| P9.0  | 51      | 39      | 44     |

| P9.1  | 52      | 40      | 45     |

| P9.2  | 53      | 41      | 46     |

| P9.3  | 54      | 42      | 47     |

| P9.4  | 55      | 43      | -      |

| P9.5  | 56      | 44      | -      |

| P10.0 | 61      | 48      | 50     |

| P10.1 | 62      | 49      | 51     |

| P10.2 | 63      | 50      | 52     |

| P10.3 | 64      | 51      | 53     |

| P10.4 | 65      | 52      | 54     |

| P10.5 | 66      | 53      | 55     |

| P10.6 | 67      | 54      | 56     |

| P10.7 | 68      | 55      | 57     |

| P11.1 | 69      | -       | -      |

| P11.2 | 70      | 56      | 58     |

| P11.3 | 71      | 57      | 59     |

| P11.4 | 72      | 58      | 60     |

| P11.5 | 73      | 59      | 61     |

| P11.6 | 74      | 60      | 62     |

# Table 6. Packages and Pin Information (continued)

| Pin           | Package |         |        |

|---------------|---------|---------|--------|

| FIII          | 80-TQFP | 64-TQFP | 68-QFN |

| P11.7         | 75      | 61      | 63     |

| P12.6         | 78      | 63      | 65     |

| P12.7         | 79      | 64      | 66     |

| P14.0 / USBDP | -       | -       | 13     |

| P14.1 / USBDM | -       | -       | 12     |

Note: If the USB pins are not used, connect VDDUSB to ground and leave the P14.0/USBDP and P14.1/USBDM pins unconnected.

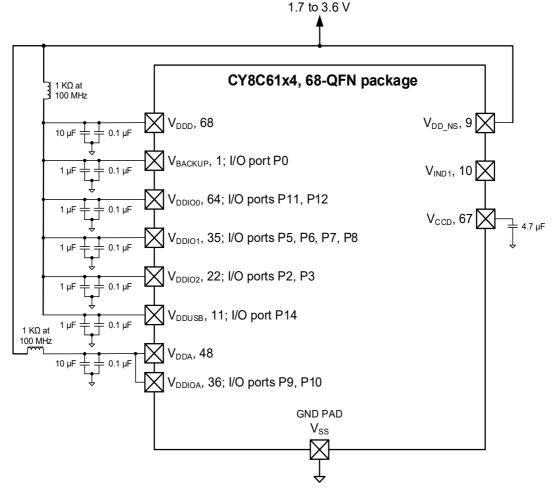

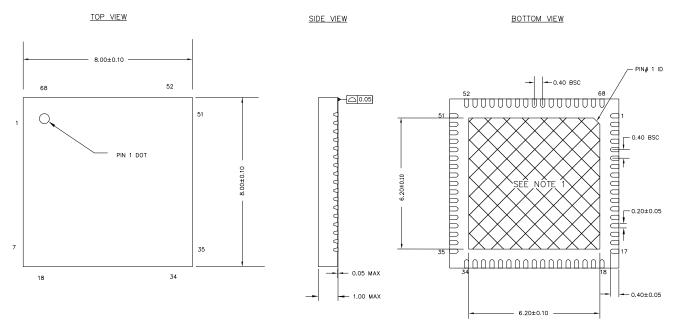

VccD P12.7 P12.6 Vss Vss P11.5 P11.5 P11.3 P11.3 P10.5 P10.6 P10.6 P10.6 P10.2 P10.2 P10.2 P10.2 P10.2 P10.2 0 0 П **=** 1 V<sub>REF0</sub> VDDD 2 Vss 59 🗖 V<sub>DDA</sub> 3 58 🗖 V<sub>SS</sub> VBACKUP **E** P0.0 **=** 4 57 🖬 V<sub>REF 1</sub> P0.1 🗖 5 56 🗖 P9.5 P0.2 🗖 6 55 P9.4 P0.3 🗖 54 P9.3 7 53 **P**9.2 P0.4 **=** 8 P0.5 **=** 9 P9.1 52 51 🗖 P9.0 XRES = 10 50 **E** P8.1 49 **E** P8.0 TQFP V<sub>SS</sub> = 11 P1.0 **=** 12 48 🗖 P7.7 P1.1 **=** 13 P1.2 🗖 14 47 **P**7.5 46 🗖 P7.4 P2.0 **=** 15 45 **•** P7.3 44 **•** P7.2 P2.1 **=** 16 P2.2 **=** 17 43 **P**7.1 P2.3 **=** 18 P2.4 **=** 19 42 🗖 P7.0 P2.5 **=** 20 41 🗖 V<sub>SS</sub> P2.6 P2.7 P2.7 Volue Volue P5.1 P5.1 P5.2 P5.2 P5.2 P5.2 P5.2 P5.2 P5.2 Volue Volue

Figure 9. Device Pinout for 80-TQFP Package

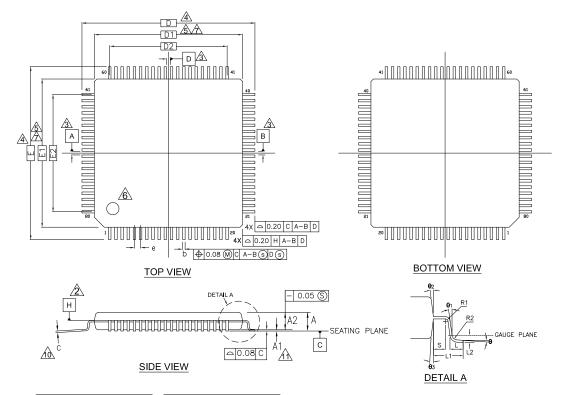

### Figure 10. Device Pinout for 64-TQFP Package

Each port pin has multiple alternate functions. These are defined in Table 7. The columns ACT #x and DS #y denote active (System LP/ULP) and Deep Sleep mode signals respectively.

The notation for a signal is of the form IPName[x].signal\_name[u]:y.

IPName = Name of the block (such as tcpwm), x = Unique instance of the IP, Signal\_name = Name of the signal, u = Signal number where there is more than one signal for a particular signal name, y = Designates copies of the signal name.

For example, the name tcpwm[0].line\_compl[3]:4 indicates that this is instance 0 of a tcpwm block, the signal is line\_compl # 3 (complement of the line output) and this is the fourth occurrence (copy) of the signal. Signal copies are provided to allow flexibility in routing and to maximize use of on-chip resources.

#### Table 7. Multiple Alternate Functions

| Port/<br>Pin | ACT #0                           | ACT #1                             | ACT #2           | ACT #3             | DS #2 | DS #3 | ACT<br>#4              | ACT<br>#5 | ACT<br>#6                 | ACT<br>#7                | ACT<br>#8                    | ACT<br>#9 | ACT<br>#10 | ACT<br>#12                        | ACT<br>#13                      | ACT<br>#14 | ACT<br>#15 | DS #5                   | DS #6 |

|--------------|----------------------------------|------------------------------------|------------------|--------------------|-------|-------|------------------------|-----------|---------------------------|--------------------------|------------------------------|-----------|------------|-----------------------------------|---------------------------------|------------|------------|-------------------------|-------|

| P0.0         | tcpwm[0].l<br>ine[0]:0           | tcpwm[25<br>6].line[0]:<br>0       | csd.csd<br>_tx:0 | csd.csd_<br>tx_n:0 |       |       | srss.e<br>xt_clk:<br>0 |           |                           |                          | scb[0].<br>spi_se<br>lect1:0 |           |            | peri.tr<br>_io_in<br>put[0]:<br>0 |                                 |            |            |                         |       |

| P0.1         | tcpwm[0].l<br>ine_comp<br>I[0]:0 | tcpwm[25<br>6].line_co<br>mpl[0]:0 | csd.csd<br>_tx:1 | csd.csd_<br>tx_n:1 |       |       |                        |           |                           |                          | scb[0].<br>spi_se<br>lect2:0 |           |            | peri.tr<br>_io_in<br>put[1]:<br>0 |                                 |            |            | cpuss.<br>swj_tr<br>stn |       |

| P0.2         | tcpwm[25<br>7].line[1]:<br>0     | tcpwm[25<br>7].line[1]:<br>0       | csd.csd<br>_tx:2 | csd.csd_<br>tx_n:2 |       |       |                        |           | scb[0]<br>.uart_r<br>x:0  | scb[0].<br>i2c_scl<br>:0 | scb[0].<br>spi_m<br>osi:0    |           |            |                                   |                                 |            |            |                         |       |

| P0.3         | tcpwm[0].l<br>ine_comp<br>l[1]:0 | tcpwm[25<br>7].line_co<br>mpl[1]:0 | csd.csd<br>_tx:3 | csd.csd_<br>tx_n:3 |       |       |                        |           | scb[0]<br>.uart_t<br>x:0  | scb[0].<br>i2c_sd<br>a:0 | scb[0].<br>spi_mi<br>so:0    |           |            |                                   |                                 |            |            |                         |       |

| P0.4         | tcpwm[0].l<br>ine[2]:0           | tcpwm[25<br>8].line[2]:<br>0       | csd.csd<br>_tx:4 | csd.csd_<br>tx_n:4 |       |       |                        |           | scb[0]<br>.uart_r<br>ts:0 |                          | scb[0].<br>spi_cl<br>k:0     |           |            | peri.tr<br>_io_in<br>put[2]:<br>0 | peri.tr_io<br>_output[<br>_0]:2 |            |            |                         |       |

| P0.5         | tcpwm[0].l<br>ine_comp<br>I[2]:0 | tcpwm[25<br>8].line_co<br>mpl[2]:0 | csd.csd<br>_tx:5 | csd.csd_<br>tx_n:5 |       |       | srss.e<br>xt_clk:<br>1 |           | scb[0]<br>.uart_<br>cts:0 |                          | scb[0].<br>spi_se<br>lect0:0 |           |            | peri.tr<br>_io_in<br>put[3]:<br>0 | peri.tr_io<br>_output[<br>_1]:2 |            |            |                         |       |

| P1.0         |                                  |                                    | csd.csd<br>_tx:6 | csd.csd_<br>tx_n:6 |       |       |                        |           |                           |                          |                              |           |            |                                   |                                 |            |            |                         |       |

| P1.1         |                                  |                                    | <br>tx:7         | csd.csd_<br>tx_n:7 |       |       |                        |           |                           |                          |                              |           |            |                                   |                                 |            |            |                         |       |

| P1.2         |                                  |                                    | csd.csd<br>_tx:8 | csd.csd_<br>tx_n:8 |       |       |                        |           |                           |                          |                              |           |            |                                   |                                 |            |            |                         |       |

| P2.0         | tcpwm[0].l<br>ine[3]:0           | tcpwm[0].l<br>ine[259]:0           | csd.csd<br>_tx:9 | csd.csd_<br>tx_n:9 |       |       |                        |           | scb[1]<br>.uart_r<br>x:1  | scb[1].<br>i2c_scl<br>:1 | scb[1].<br>spi_m<br>osi:1    |           |            | peri.tr<br>_io_in<br>put[4]:<br>0 |                                 |            |            |                         |       |

| Port/<br>Pin | ACT #0                           | ACT #1                             | ACT #2                | ACT #3                 | DS #2 | DS #3                          | ACT<br>#4 | ACT<br>#5 | ACT<br>#6                 | ACT<br>#7                | ACT<br>#8                    | ACT<br>#9 | ACT<br>#10                   | ACT<br>#12                         | ACT<br>#13 | ACT<br>#14 | ACT<br>#15 | DS #5 | DS #6 |

|--------------|----------------------------------|------------------------------------|-----------------------|------------------------|-------|--------------------------------|-----------|-----------|---------------------------|--------------------------|------------------------------|-----------|------------------------------|------------------------------------|------------|------------|------------|-------|-------|

| P2.1         | tcpwm[0].l<br>ine_comp<br>I[3]:0 | tcpwm[0].l<br>ine_compl<br>[259]:0 | csd.csd<br>_tx:10     | csd.csd_<br>tx_n:10    |       |                                |           |           | scb[1]<br>.uart_t<br>x:1  | scb[1].<br>i2c_sd<br>a:1 | scb[1].<br>spi_mi<br>so:1    |           |                              | peri.tr<br>_io_in<br>put[5]:<br>0  |            |            |            |       |       |

| P2.2         | tcpwm[0].l<br>ine[0]:1           | tcpwm[0].l<br>ine[260]:0           | csd.csd<br>_tx:11     | csd.csd_<br>tx_n:11    |       |                                |           |           | scb[1]<br>.uart_r<br>ts:1 |                          | scb[1].<br>spi_cl<br>k:1     |           |                              |                                    |            |            |            |       |       |

| P2.3         | tcpwm[0].l<br>ine_comp<br>l[0]:1 | tcpwm[0].l<br>ine_compl<br>[260]:0 | csd.csd<br>_tx:12     | csd.csd_<br>tx_n:12    |       |                                |           |           | scb[1]<br>.uart_<br>cts:1 |                          | scb[1].<br>spi_se<br>lect0:1 |           |                              |                                    |            |            |            |       |       |

| P2.4         | tcpwm[0].l<br>ine[1]:1           | tcpwm[0].l<br>ine[261]:0           | csd.csd<br>_tx:13     | csd.csd_<br>tx_n:13    |       |                                |           |           |                           |                          | scb[1].<br>spi_se<br>lect1:1 |           |                              |                                    |            |            |            |       |       |

| P2.5         | tcpwm[0].l<br>ine_comp<br>l[1]:1 | tcpwm[0].l<br>ine_compl<br>[261]:0 | csd.csd<br>_tx:14     | csd.csd_<br>tx_n:14    |       |                                |           |           |                           |                          | scb[1].<br>spi_se<br>lect2:1 |           |                              |                                    |            |            |            |       |       |

| P2.6         | tcpwm[0].l<br>ine[1]:5           | tcpwm[1].l<br>ine[262]:1           | csd.csd<br>_tx:15     | csd.csd_<br>tx_n:15    |       | lpcom<br>p.dsi_<br>comp<br>0:0 |           |           |                           |                          | scb[1].<br>spi_se<br>lect3:1 |           |                              | peri.tr<br>_io_in<br>put[8]:<br>0  |            |            |            |       |       |

| P2.7         | tcpwm[0].l<br>ine_comp<br>l[2]:1 | tcpwm[0].l<br>ine_compl<br>[262]:0 | csd.csd<br>_tx:16     | csd.csd_<br>tx_n:16    |       | lpco<br>mp.ds<br>i_com<br>p1:0 |           |           |                           |                          |                              |           |                              | peri.tr<br>_io_in<br>put[9]:<br>0  |            |            |            |       |       |

| P3.0         | tcpwm[0].l<br>ine[3]:1           | tcpwm[0].l<br>ine[263]:0           | csd.csd<br>_tx:17     | csd.csd_<br>tx_n:17    |       |                                |           |           | scb[2]<br>.uart_r<br>x:1  | scb[2].<br>i2c_scl<br>:1 |                              |           |                              | peri.tr<br>_io_in<br>put[6]:<br>0  |            |            |            |       |       |

| P3.1         | tcpwm[0].l<br>ine_comp<br>l[3]:1 | tcpwm[0].l<br>ine_compl<br>[263]:0 | csd.csd<br>_tx:18     | csd.csd_<br>tx_n:18    |       |                                |           |           | scb[2]<br>.uart_t<br>x:1  | scb[2].<br>i2c_sd<br>a:1 |                              |           |                              | peri.tr<br>_io_in<br>put[7]:<br>0  |            |            |            |       |       |

| P5.0         | tcpwm[0].l<br>ine[0]:2           | tcpwm[0].l<br>ine[256]:1           | csd.csd<br>_tx:19     | csd.csd_<br>tx_n:19    |       |                                |           |           | scb[5]<br>.uart_r<br>x:0  | scb[5].<br>i2c_scl<br>:0 | scb[5].<br>spi_m<br>osi:0    |           | canfd[0]<br>.ttcan_r<br>x[0] | peri.tr<br>_io_in<br>put[10<br>]:0 |            |            |            |       |       |

| P5.1         | tcpwm[0].l<br>ine_comp<br>I[0]:2 | tcpwm[0].l<br>ine_compl<br>[256]:1 | csd.csd<br>_tx:20     | csd.csd_<br>tx_n:20    |       |                                |           |           | scb[5]<br>.uart_t<br>x:0  | scb[5].<br>i2c_sd<br>a:0 | scb[5].<br>spi_mi<br>so:0    |           | canfd[0]<br>.ttcan_t<br>x[0] | peri.tr<br>_io_in<br>put[11<br>]:0 |            |            |            |       |       |

| P5.2         |                                  |                                    | csd.csd<br>tx:21      | csd.csd_<br>tx_n:21    |       |                                |           |           |                           |                          |                              |           |                              |                                    |            |            |            |       |       |

| P5.6         | tcpwm[0].l<br>ine[1]:2           | tcpwm[0].l<br>ine[257]:1           | _<br>csd.csd<br>tx:22 | <br>csd.csd<br>tx_n:22 |       |                                |           |           |                           |                          |                              |           |                              |                                    |            |            |            |       |       |

| P5.7         | tcpwm[0].l<br>ine_comp<br>I[1]:2 | tcpwm[0].l<br>ine_compl<br>[257]:1 | csd.csd<br>tx:23      | csd.csd_<br>tx_n:23    |       |                                |           |           |                           |                          |                              |           |                              |                                    |            |            |            |       |       |

| Port/<br>Pin | ACT #0                           | ACT #1                             | ACT #2            | ACT #3              | DS #2                    | DS #3 | ACT<br>#4 | ACT<br>#5 | ACT<br>#6                 | ACT<br>#7                | ACT<br>#8                    | ACT<br>#9                     | ACT<br>#10 | ACT<br>#12                         | ACT<br>#13                     | ACT<br>#14                | ACT<br>#15 | DS #5                            | DS #6                            |