# CYFP1-8080 Datasheet

#### **Features**

#### **■** Fingerprint Sensor

- □ BGA package consisting of a die mounted on a polymer substrate sensor

- □ 8.0 mm × 8.0 mm active imaging area fingerprint sensor

- □ 340 DPI 107 × 107 pixel array at 8-bits per pixel resolution

- □ Great image quality with polymer, plastic, and ceramic coatings < 100µ in overall thickness

- □ Superior image quality with polymer coatings, and ceramic and glass cover over sensor

- □ 32-bit Arm® Cortex®-M0 CPU

- □ Noise-suppression technologies for battery chargers, displays, and radios in the device

- Self-calibration and self-testing

- □ Factory tuned with on-chip baseline storage, no field tuning required

- □ Secure firmware upgrades via bootloader

#### **■** System Performance

- □ Live Finger Complete Acquisition Time (Get\_Image): ~160ms)

- □ 14 Finger Identify Match Time: ~500ms (average)

- □ <1.5% FRR at FAR >1:100K using CY-supplied matching SW

- □ 360 degree finger placement

#### **■** Embedded Environment

- □ Embedded framework (CYFPEF) provided for porting into host processor

- □ Recommended MCU Features: Cortex M4, 256KB of flash, and 96KB of RAM

- Ability to import and export templates securely

- □ Configurable security levels (1:10K to 1:1000K)

- □ Simple secure external communication protocol over MCU UART Interface

#### ■ Sensor Communication Interface

- ☐ SPI slave bit rates up to 7.8 Mbps

- □ Strong 256-bit AES encryption secures the system interface from the sensor to the host processor

### ■ Power (configuration-dependent)

- □ Operation of single 3.3-V supply

- 1.71 V to 1.95 V direct digital supply or 2.0 V to 5.5 V via LDO

- □ 2.65 V to 5.5 V analog supply

- □ <80-mW active power (average power while sensing)

- □ 8-µW typical deep-sleep power

- □ 400-µW Finger detection power @ 10 detects per second

#### ■ Operating Temperature Range

□ -40 °C to +85 °C

#### **■ Package Options**

□ 73 BGA package, 8.87 × 9.26 mm rectangular sensor

## **Optional Features**

- False finger rejection limiting host processor interruptions

- Fake finger rejection (anti-spoofing)

- Programmable finger detection timing (Wake-on-Finger)

- Navigation

#### **Sensor Shown With Coating**

Front of the Sensor

Cypress Semiconductor Corporation

Document Number: 002-11233 Rev. \*D

198 Champion Court

San Jose, CA 95134-1709

408-943-2600

# **Contents**

| System Overview                         | (  |

|-----------------------------------------|----|

| Functional Overview                     |    |

| Features Overview                       |    |

| Power Supply Information                | б  |

| Power Configurations                    | б  |

| Primary Power Configurations            |    |

| Secondary Power Configurations          |    |

| Voltage Coefficient                     |    |

| Power States Summary                    | 9  |

| Active                                  |    |

| Sleep                                   | 9  |

| Deep Sleep                              |    |

| Wake-On-Finger and Wait-For-Finger      | 9  |

| Pin Information                         |    |

| Example Schematic and Layout Guidelines | 12 |

| Electrical Specifications               |    |

| Operating Temperature                   |    |

| Flash Specifications                    |    |

| Chin-Level DC Specifications            |    |

| I/O Port 0 (P0[0:7]) DC Specifications  | 17 |

|-----------------------------------------|----|

| Chip-Level AC Specifications            | 17 |

| SPI Specifications                      | 18 |

| Packaging Information                   | 20 |

| Ordering Information                    | 21 |

| Part Ordering Code Definitions          | 21 |

| Acronyms and Abbreviations              | 22 |

| Document Conventions                    | 22 |

| Units of Measure                        | 22 |

| Port Nomenclature                       | 22 |

| Glossary                                | 23 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 25 |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         | 25 |

| Cypress Developer Community             | 25 |

| Technical Support                       | 25 |

# **System Overview**

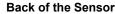

Figure 1. CYFP1 Typical System Diagram

CYFP1 is a fingerprint reader that can read a fingerprint image from the attached polymer substrate, which contains a grid of row and column electrodes. CYFP1 securely transfers the fingerprint image to a host processor for feature extraction and pattern matching against a fingerprint template.

A typical fingerprint system consists of a fingerprint reader mounted on a flexible printed circuit board (FPC). The FPC connects the fingerprint reader to the host processor. Users interact with the system by placing a finger they intend to enroll or verify on the sensor.

CYFP1 detects the change in capacitance and scans the sensor electrodes creating a capacitive map representing the ridge and valley flow of the specific user. The capacitive map is converted to digital values, encrypted and transferred to the host for creating a template or matching against an existing template.

### **Functional Overview**

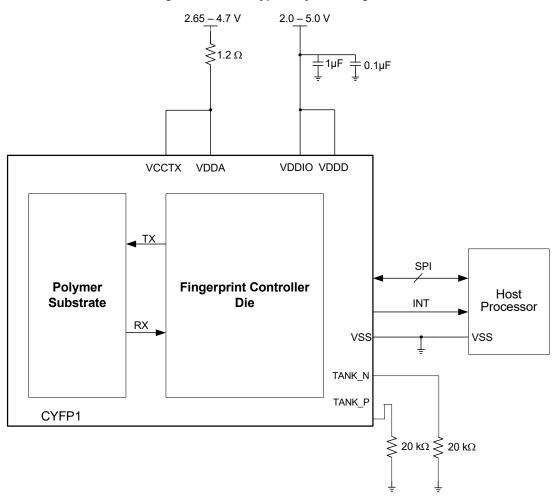

Figure 2 shows the CYFP1 block diagram. This device contains a high-performance Arm 32-bit CPU with an integrated hardware multiply unit. This CPU controls all sensing and processing of measured capacitance results to allow creating a fingerprint map from touches detected on the sensor. The controller is optimized for low power and fast response time, with built-in support for manufacturing test. CYFP1 communicates with a host through a slave SPI interface at up to 7.8 Mbps.

CYFP1 scans the sensor information using the fingerprint subsystem. This fingerprint subsystem consists of a 5-V TX pump, TX driver, RX channel, and a transmit/receive (TX/RX) multiplexer. The multiplexer electrically connects the RX channel and TX driver to the appropriate row and column electrodes of the fingerprint sensor.

Figure 2. Functional Block Diagram

### **Features Overview**

- Provides great image quality with polymer coatings, ceramic and, glass cover over sensor:

- □ CYFP1 requires a cosmetic cover that conceals and protects the fingerprint sensor. This cover needs to be thick enough to endure impacts, hard enough to survive scratches, yet thin enough to not interfere with imaging performance. CYFP1 employs proprietary technologies to optimize fingerprint image capture and boost SNR.

#### ■ Encryption

□ To ensure secure communication between the host and CYFP1, AES-256 encryption and SHA message authentication is included in CYFP1. Encryption is used to securely transfer a fingerprint image to the host processor. Each image is uniquely signed preventing replay attacks. Additionally, for firmware upgrades, signed firmware can be delivered to CYFP1 over an encrypted session.

#### ■ Responsive to user inputs

□ CYFP1 response reliably identifies the user quickly after a physical finger touch. This feature is enabled by the wakeup performance, acquisition speed, and biometric performance of the solution. The reader quickly wakes up to touch, acquires and transfers the fingerprint image to the host within 375 milliseconds, and optimizes and tunes the fingerprint software framework to allow the host to identify a user reliably within 225 milliseconds.

#### ■ Works with all finger types

□ CYFP1 is capable of dealing with a variety of fingers and variations to fingers due to external conditions. The diversity of finger types, dry and moist fingers, temporary damage to fingers, and other environmental and behavioral conditions are challenges to reliably enroll and match a finger over time. Enrollment and matching algorithms provided with CYFP1 can reliably detect these situations and dynamically update to fingerprint template to track these changes.

#### ■ Configurable and secure enrollment schemes

□ Using CYFP1, the end user can enroll reliably and in reasonable time, and with a reasonable number of touches. Enrollment schemes are configurable based on user experience including the level of security desired. The enrolment template is augmented dynamically as new pattern information becomes available during the authentication process.

#### ■ Reliable identification

□ CYFP1 strikes a balance between security and convenience for a great end-user experience. Fingerprint matching is performed by a proprietary software algorithm using the feature set extracted from the fingerprint image created during the enrollment process. The matching algorithm browses all the templates created during enrollment until it finds one that matches the required security setting. The fingerprint matching software is provided along with the CYFP1 sensor.

#### ■ Common-mode noise rejection

□ CYFP1 employs techniques that strongly suppress common-mode noise. This is especially important in dealing with the charger, LCD, and radio noise that is typical in most mobile devices.

# **Power Supply Information**

CYFP1 power supplies are shown in the following table.

Table 1. CYFP1 Power Supplies

| Supply               | Function                          | Range (V) | Operating<br>Mode   |

|----------------------|-----------------------------------|-----------|---------------------|

| VCCD                 | Core low-voltage logic and analog | 1.71–1.95 | All                 |

| VDDD                 | Core LDO                          | 1.71–1.95 | LDO bypassed        |

| VUUU                 | Cole LDO                          | 2.0-5.5   | LDO enabled         |

| VDDA                 | TSS RX, TX pump, and TX driver    | 2.65–5.50 | TX pump<br>disabled |

| VDDA                 | supply                            | 2.65-4.70 | TX pump<br>enabled  |

| VCCTX                | External VCCTX                    | 2.65–5.50 | TX pump<br>disabled |

| VCCIX                | TX pump reservoir                 | 4.7–5.3   | TX pump<br>enabled  |

| VDDIO <sup>[1]</sup> | XRES and GPIO supply              | 1.71–5.50 | All                 |

# **Power Configurations**

For those power configurations where the TX pump is used, the VCCTX supply in CYFP1 always requires an external reservoir cap. In addition to the primary power options described in the following section, which make use of the TX pump, multiple secondary power options that use a direct VCCTX supply are also available.

All bypass, filter, and reservoir capacitors require an X5R dielectric characteristic or better. While selecting components, ensure that the required resistance and capacitance is present when combined with the associated voltage and temperature coefficients of each component.

All external passives, when mounted to the circuit board, must not exceed the mounted device package thickness.

#### **Primary Power Configurations**

All primary power configurations make use of the internal TX pump. In these primary configurations, the digital and FPSS analog elements of CYFP1 may be powered in three base configurations:

- Separate digital and analog supplies, with the digital supply ≥ 2.0 V (core LDO enabled)

- Separate digital and analog supplies, with the digital supply 1.71 V-1.95 V (core LDO bypassed)

- Common (shared) digital and analog supply

A 1.2- $\Omega$  ±5 percent resistor in series with the VDDA supply is used to filter high-frequency noise and limit the slew rate into VDDA. For VDDA supplies with significant noise in the integration passband, the 1- $\mu$ F low-frequency capacitor can be replaced with a 2.2- $\mu$ F capacitor. This larger capacitor moves the pole in the LPF around one octave lower, and reduces the VDDA noise in the integration passband by 6 dB.

#### Note

1. VDDD should be ≥ VDDIO.

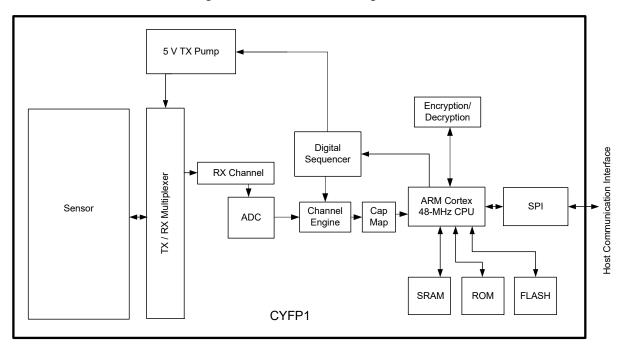

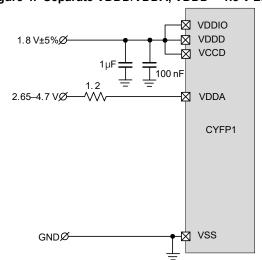

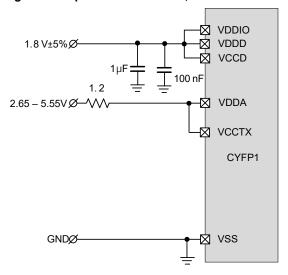

#### Primary - Separate VDDD/VDDA, VDDD ≥ 2.0 V

This configuration should be used for systems requiring communications at voltages other than a nominal 1.8 V. In this configuration, VDDA is powered separately from VDDD, and VDDD provides power to the logic core through an internal LDO. The output of this LDO connects to a filter capacitor attached to the VCCD output. This configuration is shown in Figure 3.

Figure 3. Separate VDDD/VDDA, VDDD ≥ 2.0 V

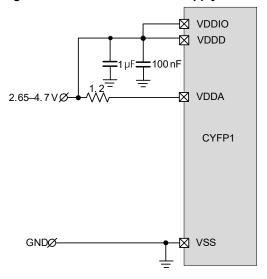

Primary - Separate VDDD/VDDA, VDDD = 1.8 V±5%

In this configuration, the I/O and logic core operate from the  $1.8\text{-V} \pm 5\%$  supply; the core LDO is bypassed. The VCCD pin is an input to the device and provides power to the logic core, while the VDDD supply provides power to the GPIO pins. This configuration is shown in Figure 4.

Figure 4. Separate VDDD/VDDA, VDDD = 1.8 V ±5%

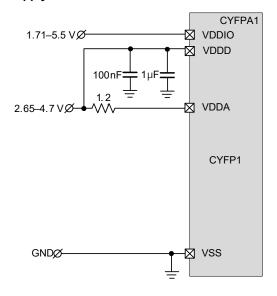

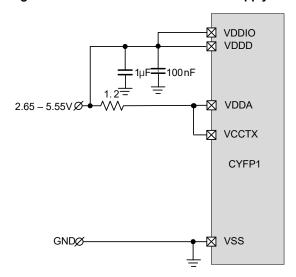

#### Primary - Shared VDDD/VDDA Supply

This configuration allows operation from a single supply. Because the minimum supply for the analog domain is 2.65 V, the digital domain will also be powered from this same supply. In this configuration, the internal logic LDO is enabled, and VCCD is an output. This configuration is shown in Figure 5.

Figure 5. Shared VDDD/VDDA Supply

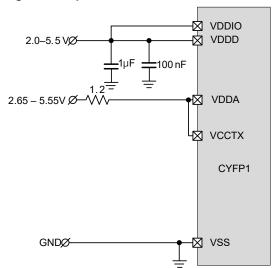

Primary - Shared VDDD/VDDA Supply, Separate VDDIO Supply

This configuration is an example of a separate VDDIO supply and a shared primary supply for VDDD and VDDA. All the examples described above can use a separate VDDIO supply. This configuration is shown in Figure 6.

Figure 6. Shared VDDD/VDDA Supply, Separate VDDIO Supply

### **Secondary Power Configurations**

All secondary power configurations disable the internal TX pump, and power for the TX drivers is provided through the VCCTX pin. In the secondary configurations, the digital and FPSS analog elements of CYFP1 may be powered in three base configurations:

- Separate digital and analog supplies, with the digital supply >2.0 V (core LDO enabled)

- Separate digital and analog supplies, with the digital supply 1.71–1.95 V (core LDO bypassed)

- Common (shared) digital and analog supply

Each of these base configurations support only a shared VDDD/VCCTX supply. Note that the allowed supply voltage ranges for all secondary configurations require VDDA to always be equal to VCCTX.

#### Secondary - Separate VDDD/VDDA, VDDD ≥ 2.0 V

This configuration is similar to the primary configuration illustrated in Figure 3, but with the TX pump disabled and VCCTX connected externally to VDDA. This configuration is shown in Figure 7.

Figure 7. Separate VDDD/VDDA, VDDD ≥ 2.0 V

# Secondary - Separate VDDD/VDDA, VDDD = 1.8 V ±5%

This configuration is similar to the primary documented in Figure 4, but with the TX pump disabled and VCCTX connected externally to VDDA. This configuration is shown in Figure 8.

Figure 8. Separate VDDD/VDDA, VDDD = 1.8 V ±5%

### Secondary - Shared VDDD/VDDA Supply

This configuration is similar to the primary configuration illustrated in Figure 5, but with the TX pump disabled and VCCTX connected externally to VDDA. This configuration is shown in Figure 9.

Figure 9. Shared VDDD/VDDA/VCCTX Supply

## **Voltage Coefficient**

The actual capacitance of external capacitors may be reduced with higher bias voltage. Check the capacitor datasheet for the voltage coefficient. External capacitors require an X5R dielectric characteristic or better. It is recommended to use an X7R dielectric characteristic or better for high-frequency 0.1-µF capacitors. Capacitors used for power supply decoupling or filtering are operated under a continuous DC bias. Many capacitors used with DC power across them provide less than their target capacitance, and their capacitance is not constant across their working voltage range. When selecting capacitors for use with this device, verify that the selected components provide the required capacitance under the specific operating conditions of temperature and voltage used in your design.

While the temperature ratings of a capacitor are normally found as part of its catalog part number (for example, X7R, C0G, Y5V), the matching voltage coefficient may only be available on the component datasheet or direct from the manufacturer. Use of components that do not provide the required capacitance under the actual operating conditions may cause the device to perform at less than the datasheet specifications.

**Table 2. External Components**

| Component                 | Number of Components | Suggested Part Number | t Number Usage                       |          |

|---------------------------|----------------------|-----------------------|--------------------------------------|----------|

| 100 nF X5R 20%            | 1                    | C0603X5R1A104K030BC   | VDDD decoupling capacitor            | U12, V12 |

| 1 μF X5R 20%              | 1                    | C0603X5R0J105M030BC   | VDDD decoupling capacitor            | U12, V12 |

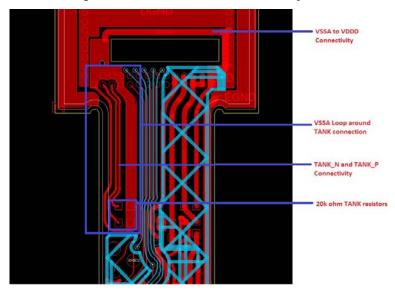

| 20 kΩ 5% 1/20 W           | 2                    | ERJ-1GEJ203C          | TANK filtering resistors             | V3, V4   |

| 1.2 Ω –200/+300 ppm/°C 5% | 1                    | RC0603J1R2CS          | VDDA series noise filtering resistor | U13, V13 |

# **Power States Summary**

#### **Active**

In the Active mode, the CPU and other peripherals are functional. In this mode, power varies dynamically as the different sections of the device are enabled for operation.

When active, the CPU controls the power circuits for the RX and TX domains. These may be cycled up or down as needed for sensing. Internal blocks must automatically enter a power-down mode when they are not being used.

#### Sleep

In the Sleep mode, all device operations remain functional; however, the clock to the M0 CPU is stopped and the CPU waits for an interrupt. Device scanning and communications on the COMM interface may operate with the M0 CPU stopped in this mode. All regulators remain in their last programmed state. Sleep and watchdog timers may be enabled and functional. The communications interface may be configured to transfer data and to wake the device on receipt of a command or data. The CPU may be configured to wake on an external interrupt.

#### Deep Sleep

In the Deep Sleep mode, the CPU and IMO are both stopped. The low-speed oscillator (LSO) is active and is used to time the duration of deep-sleep events. The COMM port may remain active, and can wake the device on a host-SPI transaction. The COMM port may both send and receive data in this mode. The sleep/watchdog timers or GPIO may also be used to wake the device from deep sleep.

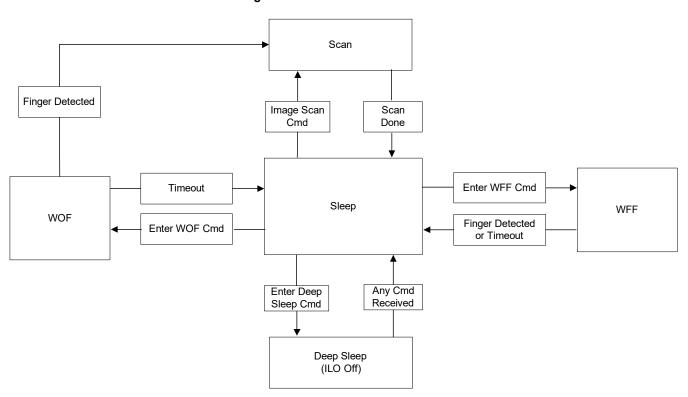

#### Wake-On-Finger and Wait-For-Finger

These are low-power modes under which the CYFP1 automatically detects the presence of a finger and triggers a scan. These modes provide the ability to shut down most of the CYFP1 blocks and periodically turn on some of them to check for fingers.

Wait-For-Finger is the lowest power consumption mode available.

Figure 10. Power Mode Transitions

# Pin Information

CYFP1 is available in square BGA packages. All pins described in the following table are available on both packages. This section lists pin names, descriptions, and mapping to the physical packages.

- P0[0:7]: 8-pin port, four SPIs, one INT, and three GPIOs

- XRES: Reset pin, to be connected to VDDD if not used

Table 3. 8.87 × 9.26 mm Rectangular Sensor and 12.20 × 12.20 mm Square Sensor Pin List

| Ball# | Name | Digital | Analog | Description    |

|-------|------|---------|--------|----------------|

| A2    | VSSD | Pov     | wer    | Digital ground |

| A3    | VSSD | Pov     | wer    | Digital ground |

| A4    | VSSD | Pov     | wer    | Digital ground |

| A5    | VSSD | Pov     | wer    | Digital ground |

| A6    | VSSD | Pov     | wer    | Digital ground |

| A7    | VSSD | Pov     | wer    | Digital ground |

| A8    | VSSD | Pov     | wer    | Digital ground |

| A9    | VSSD | Pov     | wer    | Digital ground |

| A10   | VSSD | Pov     | wer    | Digital ground |

| A11   | VSSD | Pov     | wer    | Digital ground |

| A12   | VSSD | Pov     | wer    | Digital ground |

| A13   | VSSD | Pov     | wer    | Digital ground |

| A14   | VSSD | Pov     | wer    | Digital ground |

| A15   | VSSD | Pov     | wer    | Digital ground |

| C1    | VSSD | Pov     | wer    | Digital ground |

| C17   | VSSD | Pov     | wer    | Digital ground |

| D1    | VSSD | Pov     | wer    | Digital ground |

| D17   | VSSD | Pov     | wer    | Digital ground |

| E1    | VSSD | Pov     | wer    | Digital ground |

| E17   | VSSD | Pov     | wer    | Digital ground |

| F1    | VSSD | Pov     | wer    | Digital ground |

| F17   | VSSD | Pov     | wer    | Digital ground |

| G1    | VSSD | Pov     | wer    | Digital ground |

| G17   | VSSD | Pov     | wer    | Digital ground |

| H1    | VSSD | Pov     | wer    | Digital ground |

| H17   | VSSD | Pov     | wer    | Digital ground |

| J1    | VSSD | Pov     | wer    | Digital ground |

| J17   | VSSD | Pov     | wer    | Digital ground |

| K1    | VSSD | Power   |        | Digital ground |

| K17   | VSSD | Power   |        | Digital ground |

| L1    | VSSD | Power   |        | Digital ground |

| L17   | VSSD | Pov     | wer    | Digital ground |

| M1    | VSSD | Pov     | wer    | Digital ground |

| M17   | VSSD | Pov     | wer    | Digital ground |

Table 3. 8.87 × 9.26 mm Rectangular Sensor and 12.20 × 12.20 mm Square Sensor Pin List (continued)

| Ball# | Name   | Digital | Analog | Description                        |

|-------|--------|---------|--------|------------------------------------|

| N1    | VSSD   | Pov     | ver    | Digital ground                     |

| N17   | VSSD   | Pov     | ver    | Digital ground                     |

| P1    | VSSD   | Pov     | ver    | Digital ground                     |

| P17   | VSSD   | Pov     | ver    | Digital ground                     |

| R1    | VSSD   | Pov     | ver    | Digital ground                     |

| R17   | VSSD   | Pov     | ver    | Digital ground                     |

| T1    | VSSD   | Pov     | ver    | Digital ground                     |

| T17   | VSSD   | Pov     | ver    | Digital ground                     |

| U1    | VSSD   | Pov     | ver    | Digital ground                     |

| U3    | VSSA   | Pov     | ver    | Analog ground                      |

| U4    | VSSA   | Pov     | ver    | Analog ground                      |

| U5    | VSSA   | Pov     | ver    | Analog ground                      |

| U6    | XRES   | _       | -      | Reset                              |

| U7    | P01    | _       | -      | GPIO                               |

| U8    | P03    | _       | -      | Interrupt                          |

| U9    | P05    | _       | -      | SPI SELECT                         |

| U10   | P07    | _       | -      | SPI MOSI                           |

| U11   | VCCD   | Pov     | ver    | Core low-voltage and analog supply |

| U12   | VDDD   | Pov     | ver    | Core LDO supply                    |

| U13   | VDDA   | Pov     | ver    | Analog supply                      |

| U14   | VCCTX  | Pov     | ver    | TX pump supply                     |

| U15   | VSSD   | Pov     | ver    | Digital ground                     |

| U17   | VSSD   | Pov     | ver    | Digital ground                     |

| V2    | VSSA   | Pov     | ver    | Analog ground                      |

| V3    | TANK_P | _       | -      | Connect to 20-kΩ resistor          |

| V4    | TANK_N | _       | -      | Connect to 20-kΩ resistor          |

| V5    | VSSA   | Pov     | ver    | Analog ground                      |

| V6    | P00    | _       | -      | GPIO                               |

| V7    | P02    | _       | -      | GPIO                               |

| V8    | P04    | _       | -      | SPI MISO                           |

| V9    | P06    | _       | -      | SPI clock                          |

| V10   | N/C    | _       | -      | No connect                         |

| V11   | N/C    | -       |        | No connect                         |

| V12   | VDDIO  | Power > |        | XRES and GPIO supply               |

| V13   | VDDA   | Pov     | ver    | Analog supply                      |

| V14   | VCCTX  | Pov     | ver    | TX Pump supply                     |

| V15   | VSSD   | Pov     | ver    | Digital ground                     |

| V16   | VSSD   | Pov     | ver    | Digital ground                     |

<sup>■</sup> Connect TANK\_P and TANK\_N to analog ground through 20-kΩ resistors as specified in the external component list.

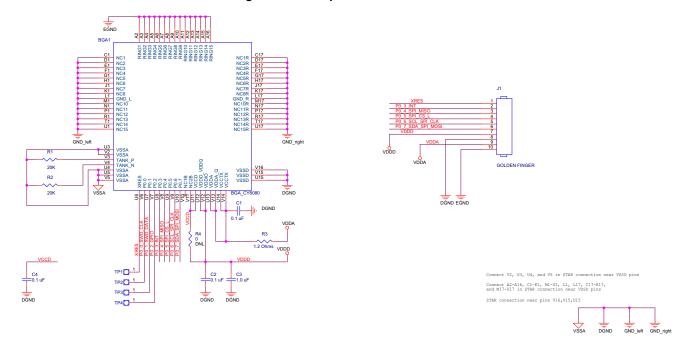

# **Example Schematic and Layout Guidelines**

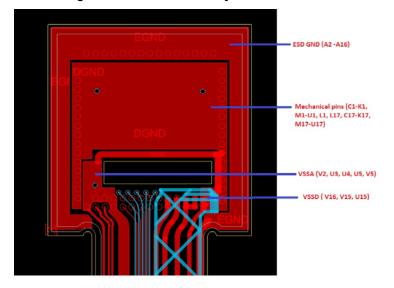

- Sensor VSSD pins (V16, V15, U15) must be connected to the System GND by wide wire trace with minimal resistance.

- Sensor VDDD pins must be connected to the System digital power supply by wide wire trace with minimal resistance.

- Sensor VSSA pins (V2, U3, U4, U5, V5) must be connected to VSSD close to the VSSD pins (V16, V15, U15).

- Sensor pins (C1-K1, M1-U1,L1, L17, C17-K17, M17-U17) must be connected to VSSD pins (V16, V15, U15) close to the VSSD pins. These pins are in place for mechanical stability of the BGA package.

- Sensor pins (A2-A16) must be connected to a copper ring placed around the sensor. An ESD decorative ring of a conductive material must be soldered or glued to the copper ring using conductive adhesive. This net must be connected to the System GND close to VSSD pins (V16, V15, U15) or anywhere else in the system.

- Connect VDDA pin to VCCTX pin for TX pump disabled.

- Connect VDDD pin to VCCD pin in case of 1.8V ±5% digital power supply.

- Keep TANK\_P and TANK\_N traces to the 20-KΩ resistor as short as possible. A loop from and to VSSA pins (V2, U3, U4, U5, V5) must be placed around the TANK resistors.

- It is not recommended to have noisy lines under the sensor, if not possible use solid plate shield.

- Minimize cross talk from SPI interface into the VDDA net. Do not route VDDA net next to SPI nets.

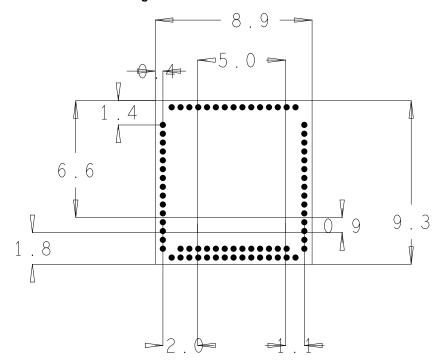

- A cutout on the PCB under the BGA must be provided to allow the passives on the bottom of the BGA package to protrude through the PCB and for the BGA to be soldered down.

Figure 11. Examples of Flex Schematic

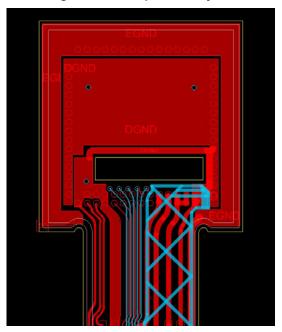

Figure 12. Example Flex Layout

Figure 13. GND Connectivity

Figure 14. VSSA and TANK Connectivity

Figure 15. Passive PCB Cutout

# **Electrical Specifications**

# Table 4. CYFP1 Electrical Specifications

| Symbol             | Description                                          | Conditions                                                                                                                                      | Min   | Тур  | Max  | Units |

|--------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|-------|

| VDDD_D             | Core supply, direct-LDO bypass                       | –40°C to 85°C T <sub>A</sub> , min/max limits are simultaneous conditions with DC and supply noise                                              | 1.71  | 1.80 | 1.95 | V     |

| VDDD_L             | Core supply, LDO enabled                             | –40°C to 85°C T <sub>A</sub>                                                                                                                    | _     | _    | 5.50 | V     |

| VDDIO              | Digital I/O supply                                   | –40°C to 85°C T <sub>A</sub>                                                                                                                    | 1.71  | _    | 5.50 | V     |

| VDDA               | Analog supply, TX pump disabled                      | -40°C to 85°C TA, input to the external low-pass filter, output of the filter connected to VDDA/VCCTX pins                                      | 2.65  | _    | 5.50 | V     |

| VDDA               | Analog supply, TX pump enabled                       | –40°C to 85°C T <sub>A</sub> , input to the external low-pass filter                                                                            | 2.65  | _    | 4.70 | ٧     |

| VDDD_AMAX          | Core supply                                          | –40°C to 85°C T <sub>A</sub> , absolute maximum                                                                                                 | -0.50 | _    | 6    | V     |

| VDDIO_AMAX         | Digital I/O supply                                   | –40°C to 85°C T <sub>A</sub> , absolute maximum                                                                                                 | -0.50 | _    | 6    | V     |

| VCCD_AMAX          | Direct digital core voltage input                    | −40°C to 85°C T <sub>A</sub> , absolute maximum                                                                                                 | -0.50 | _    | 2.30 | V     |

| VDDA_AMAX          | Analog supply                                        | −40°C to 85°C T <sub>A</sub> , absolute maximum                                                                                                 | -0.50 | _    | 6    | V     |

| VDDA_XRIP          | VDDA external regulator ripple,<br>TX Pump enabled   | -40°C to 85°C T <sub>A</sub> , DC to 20 MHz, measured at the input to the external LPF                                                          | -     | -    | 100  | mV pp |

| VDDD_XRIP_LE       | VDDD external regulator ripple,<br>LDO enabled       | -40°C to 85°C T <sub>A</sub> ; VDDD ≥ 2 V, DC to 20 MHz                                                                                         | -     | -    | 100  | mV pp |

| VDDD_XRIP_LB       | VDDD external regulator ripple,<br>LDO bypassed      | -40°C to 85°C T <sub>A</sub> ; 1.71 V ≤ VDDD ≤ 1.95 V, DC to 20 MHz                                                                             | -     | -    | 50   | mV pp |

| VCCTX_XRIP         | VCCTX external regulator ripple,<br>TX pump disabled | -40°C to 85°C T <sub>A</sub> , DC to 150 kHz, +20 dB/decade for >150 kHz, max of 100 mV up to 20 MHz, measured at the input to the external LPF | -     | -    | 15   | mV pp |

| VCCTX              | VCCTX supply operating voltage range                 | -40°C to 85°C T <sub>A</sub> , input to the external low-pass filter, external VCCTX configuration                                              | 2.65  | _    | 5.50 | ٧     |

| ESD <sub>CDM</sub> | Electrostatic discharge voltage                      | Charge device model                                                                                                                             | 1000  | _    | _    | V     |

| ESD <sub>HBM</sub> | Electrostatic discharge voltage                      | Human body model                                                                                                                                | 3000  | _    | _    | V     |

# **Operating Temperature**

# **Table 5. Operating Temperature**

| Symbol | Description         | Conditions | Min | Тур | Max | Units |

|--------|---------------------|------------|-----|-----|-----|-------|

| $T_A$  | Ambient temperature | _          | -40 | _   | 85  | °C    |

### Flash Specifications

The specifications in Table 6 are valid under these conditions:  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ ,  $1.71~\text{V} \le \text{V}_{DDD} \le 1.95~\text{V}$  or  $2.0~\text{V} \le \text{V}_{DDD} \le 5.5~\text{V}$ ,  $1.71~\text{V} \le \text{V}_{CCD} \le 1.95~\text{V}$ , and  $2.65~\text{V} \le \text{V}_{DDA} \le 4.7~\text{V}$ . Typical values are specified at  $T_{A} = 25~^{\circ}\text{C}$ ,  $V_{DDD} = V_{CCD} = V_{DDIO} = 1.8~\text{V}$ , core LDO bypassed, and  $V_{DDA} = 2.7~\text{V}$ .

**Table 6. Flash Specifications**

| Symbol                | Description           | Conditions                                                                            | Min               | Тур | Max | Units  |

|-----------------------|-----------------------|---------------------------------------------------------------------------------------|-------------------|-----|-----|--------|

| Flash <sub>ENPB</sub> | Flash write endurance | Erase/write cycles per block                                                          | 10,000            | -   | _   | cycles |

| Flash <sub>DR</sub>   | Elash data retention  | Following maximum flash write cycles (Flash <sub>ENPB</sub> ), $T_A \le 55$ °C        | 20 <sup>[2]</sup> | _   | _   | years  |

| I IdanDR              | Flash data retention  | Following maximum flash write cycles (Flash <sub>ENPB</sub> ), $T_J \le 85~^{\circ}C$ | 10 <sup>[2]</sup> | _   | -   | years  |

#### Chip-Level DC Specifications

The specifications in Table 7 are valid under these conditions:  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ ,  $1.71~\text{V} \le \text{V}_{DDD} \le 1.95~\text{V}$  or  $2.0~\text{V} \le \text{V}_{DDD} \le 5.5~\text{V}$ ,  $1.71~\text{V} \le \text{V}_{CCD} \le 1.95~\text{V}$ , and  $2.65~\text{V} \le \text{V}_{DDA} \le 4.7~\text{V}$ . Typical values are specified at  $T_{A} = 25~^{\circ}\text{C}$ ,  $V_{DDD} = V_{CCD} = V_{DDIO} = 1.8~\text{V}$ , core LDO bypassed, and  $V_{DDA} = 2.7~\text{V}$ .

Table 7. Chip-Level DC Specifications

| Symbol                           | Description                                                 | Conditions                                                | Min  | Тур  | Max  | Units |

|----------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|------|------|------|-------|

| V                                | Digital supply voltage                                      | Core LDO enabled (V <sub>CCD</sub> output)                | 2.00 | -    | 5.50 | V     |

| $V_{DDD}$                        | Digital supply voltage                                      | Core LDO bypassed (V <sub>CCD</sub> input) <sup>[4]</sup> | 1.71 | 1.80 | 1.95 | V     |

| V <sub>DDIO</sub> <sup>[3]</sup> | XRES and GPIO supply                                        |                                                           | 1.71 | -    | 5.50 | V     |

| V                                | Digital core supply voltage                                 | Core LDO enabled (V <sub>CCD</sub> output)                | -    | 1.80 | _    | V     |

| V <sub>CCD</sub>                 | Digital core supply voltage                                 | Core LDO bypassed (V <sub>CCD</sub> input) <sup>[4]</sup> | 1.71 | 1.80 | 1.95 | V     |

| V <sub>DDA</sub> <sup>[4]</sup>  | Analog supply voltage                                       | TX pump enabled                                           | 2.65 | _    | 4.70 | V     |

| PSA <sub>RAMP</sub>              | V <sub>DDA</sub> ramp up                                    | -                                                         | _    | -    | 100  | mV/μs |

| I <sub>DDD_ACT</sub>             | V <sub>DDD</sub> active current                             | -                                                         | -    | 15   | 30   | mA    |

| I <sub>DDA_ACT</sub>             | V <sub>DDA</sub> active current                             | _                                                         | _    | 11   | 13   | mA    |

| I <sub>DDD_DS</sub>              | V <sub>DDD</sub> deep sleep current                         | _                                                         | _    | 3    | _    | μA    |

| I <sub>DDA_DS</sub>              | V <sub>DDA</sub> deep sleep current                         | _                                                         | _    | 1    | _    | μA    |

| I <sub>DDD_XR</sub>              | V <sub>DDD</sub> current, XRES = LOW                        | _                                                         | I    | 2    | _    | μA    |

| I <sub>DDA_XR</sub>              | $V_{DDA}$ current, $\overline{XRES} = LOW$                  | _                                                         | 1    | 25   | _    | μA    |

| I <sub>DDD_P</sub>               | V <sub>DDD</sub> flash programming and flash verify current | _                                                         | -    | 5    | 25   | mA    |

Document Number: 002-11233 Rev. \*D

Storing programmed devices at or above the ambient temperature specified by Flash<sub>DR</sub> may reduce flash data retention time.

V<sub>DDD</sub> should be ≥ V<sub>DDIO</sub>.

These Min and Max limits are absolute limits, inclusive of noise. For proper operation, V<sub>DDA</sub> or V<sub>DDD</sub> with combined noise cannot go below or above the specified Min

# I/O Port 0 (P0[0:7]) DC Specifications

The Port 0 specifications in Table 8 are valid under these conditions:  $-40\,^{\circ}\text{C} \le \text{T}_{\text{A}} \le 85\,^{\circ}\text{C}$ ,  $1.71\,\text{V} \le \text{V}_{\text{DDD}} \le 1.95\,\text{V}$  or  $2.0\,\text{V} \le \text{V}_{\text{DDD}} \le 5.5\,\text{V}$ ,  $1.71\,\text{V} \le \text{V}_{\text{DDIO}} \le 5.5\,\text{V}$ ,  $1.71\,\text{V} \le \text{V}_{\text{CCD}} \le 1.95\,\text{V}$ , and  $2.65\,\text{V} \le \text{V}_{\text{DDA}} \le 4.7\,\text{V}$ . Typical values are specified at  $\text{T}_{\text{A}} = 25\,^{\circ}\text{C}$ ,  $\text{V}_{\text{DDD}} = \text{V}_{\text{CCD}} = \text{V}_{\text{DDIO}} = 1.8\,\text{V}$ , core LDO bypassed, and  $\text{V}_{\text{DDA}} = 2.7\,\text{V}$ .

Table 8. I/O Port 0 (P0[0:7]) DC Specifications

| Symbol                          | Description                           | Conditions                                               | Min                     | Тур | Max                   | Units |

|---------------------------------|---------------------------------------|----------------------------------------------------------|-------------------------|-----|-----------------------|-------|

| V                               | Input high voltage                    | CMOS mode                                                | $0.7 \times V_{DDIO}$   | _   | -                     | ٧     |

| V <sub>IH</sub>                 | Input high voltage                    | 1.8-V mode, 1.71 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V | 1.26                    | _   | -                     | ٧     |

| V                               | Input low voltage                     | CMOS mode                                                | -                       | _   | $0.3 \times V_{DDIO}$ | ٧     |

| $V_{IL}$                        | Input low voltage                     | 1.8-V mode, 1.71 V $\leq$ V <sub>DDIO</sub> $\leq$ 5.5 V | _                       | _   | 0.54                  | V     |

| V <sub>OH</sub>                 | High output voltage                   | I <sub>OH</sub> = 1 mA at 1.8-V V <sub>DDIO</sub>        | V <sub>DDIO</sub> – 0.5 | _   | -                     | ٧     |

| VOH                             | I light output voltage                | I <sub>OH</sub> = 4 mA at 3.0-V V <sub>DDIO</sub>        | V <sub>DDIO</sub> – 0.6 | _   | -                     | V     |

| V                               | Low output voltage                    | I <sub>OL</sub> = 8 mA at 3.3-V V <sub>DDIO</sub>        | _                       | _   | 0.6                   | V     |

| VOL                             | √ <sub>OL</sub> Low output voltage    | $I_{OL}$ = 4 mA at 1.8-V $V_{DDIO}$                      | -                       | _   | 0.6                   | V     |

| V <sub>H</sub>                  | Input hysteresis                      | T <sub>A</sub> = -40 °C to 85 °C                         | 0.1 × V <sub>DDIO</sub> | _   | -                     | V     |

| I <sub>IL</sub> <sup>[5]</sup>  | Input leakage current (absolute       | T <sub>A</sub> = 25 °C, V <sub>DDIO</sub> = 3.0 V        | _                       | _   | 14                    | nA    |

| IIL.                            | value)                                | T <sub>A</sub> = 25 °C, V <sub>DDIO</sub> = 0.0 V        | _                       | _   | 10                    | μA    |

| C <sub>IN</sub>                 | Input pin capacitance                 | Package and pin dependent<br>T <sub>A</sub> = 25 °C      | -                       | _   | 7                     | pF    |

| C <sub>OUT</sub>                | Output pin capacitance                | Package and pin dependent<br>T <sub>A</sub> = 25 °C      | -                       | _   | 7                     | pF    |

| R <sub>INT</sub> <sup>[6]</sup> | Internal pull-up/pull-down resistance | Pin configured for internal pull-up or pull-down         | 3.5                     | 5.6 | 8.5                   | kΩ    |

# **Chip-Level AC Specifications**

The specifications in Table 9 are valid under these conditions:  $-40~^{\circ}\text{C} \le T_{A} \le 85~^{\circ}\text{C}$ ,  $1.71~\text{V} \le \text{V}_{CCD} \le 1.95~\text{V}$ , and  $2.65~\text{V} \le \text{V}_{DDA} \le 4.7~\text{V}$ . Typical values are specified at  $T_{A}$  = 25  $^{\circ}\text{C}$ ,  $V_{DDD}$  =  $V_{DDO}$  =  $V_{CCD}$  = 1.8 V, core LDO bypassed, and  $V_{DDA}$  = 2.7 V.

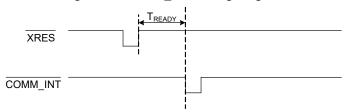

Table 9. Chip-Level AC Specifications

| Symbol               | Description                               | Conditions                                       | Min | Тур | Max | Units |

|----------------------|-------------------------------------------|--------------------------------------------------|-----|-----|-----|-------|

| T <sub>XRST</sub>    | External reset (XRES) pulse width         | After V <sub>DDD</sub> is valid                  | 10  | _   | _   | μs    |

| T <sub>READY</sub>   | Time from deassertion of XRES to COMM_INT | -                                                | -   | -   | 10  | ms    |

| T                    | Output rise time Fast-Strong              | 25-pF load, 10%–90%<br>V <sub>DDIO</sub> = 3.3 V | 2   | -   | 12  | ns    |

| T <sub>RISE_OV</sub> | Output rise time Slow-Strong              | 25-pF load, 10%–90%<br>V <sub>DDIO</sub> = 3.3 V | 10  | -   | 60  | ns    |

| т                    | Output fall time Fast-Strong              | 25-pF load, 10%–90%<br>V <sub>DDIO</sub> = 3.3 V | 2   | -   | 12  | ns    |

| T <sub>FALL_OV</sub> | Output fall time Slow-Strong              | 25-pF load, 10%–90%<br>V <sub>DDIO</sub> = 3.3 V | 10  | _   | 60  | ns    |

#### Notes

Document Number: 002-11233 Rev. \*D

<sup>5.</sup> Gang tested with all I/Os to 1  $\mu$ A.

<sup>6.</sup> XRES is input only with no internal pull-up or pull-down resistor.

Figure 16. COMM\_INT Timing Diagram

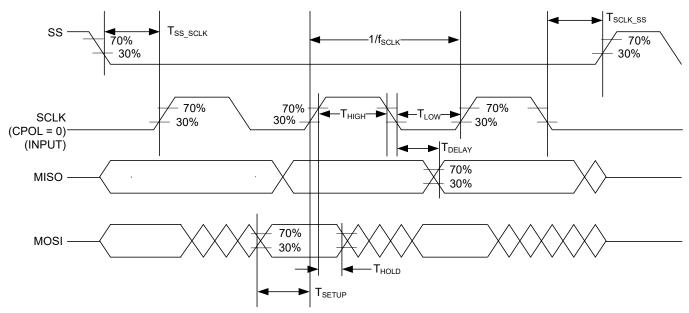

# **SPI Specifications**

The specifications listed in Table 10 are valid under these conditions:  $-40~^{\circ}\text{C} \le T_A \le 85~^{\circ}\text{C}$ ,  $1.71~\text{V} \le \text{V}_{DDD} \le 5.5~\text{V}$ ,  $1.71~\text{V} \le \text{V}_{DDD} \le 5.5~\text{V}$ ,  $1.71~\text{V} \le \text{V}_{DDD} \le 5.5~\text{V}$ ,  $1.71~\text{V} \le \text{V}_{CCD} \le 1.95~\text{V}$ ,  $2.65~\text{V} \le \text{V}_{DDA} \le 4.7~\text{V}$ , and  $C_{LOAD} = 25~\text{pF}$ . Typical values are specified at  $T_A = 25~^{\circ}\text{C}$ ,  $V_{DDD} = V_{CCD} = 1.8~\text{V}$ , core LDO bypassed, and  $V_{DDA} = 2.7~\text{V}$ .

Figure 17. SPI Timing Diagram

Table 10. AC Characteristics of the SPI Pins

| Parameter            | Description                                                                                                  | Conditions              | Min | Тур | Max | Units |

|----------------------|--------------------------------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|

| f <sub>SCLK</sub>    | SCLK clock frequency                                                                                         | _                       | _   | _   | 8   | MHz   |

| 1/f <sub>SCLK</sub>  | SPI SCLK cycle time (period)                                                                                 | _                       | 125 | _   | _   | ns    |

| SDR <sub>SPI</sub>   | Sustained data rate for SPI transaction                                                                      | _                       | _   | _   | 8   | Mbps  |

| T <sub>IDLESPI</sub> | Time between consecutive SPI transactions (duration between SS deactivation and the following SS activation) | _                       | 125 | -   | -   | ns    |

| T <sub>LOW</sub>     | SCLK LOW time                                                                                                | _                       | 50  | _   | _   | ns    |

| T <sub>HIGH</sub>    | SCLK HIGH time                                                                                               | _                       | 50  | _   | _   | ns    |

| T <sub>SETUP</sub>   | MOSI setup to SCLK                                                                                           | _                       | 30  | _   | _   | ns    |

| T <sub>HOLD</sub>    | MOSI hold from SCLK                                                                                          | _                       | 30  | _   | _   | ns    |

| T <sub>DELAY</sub>   | MISO delay (hold) high voltage                                                                               | V <sub>DDIO</sub> ≥ 3 V | 0   | _   | 45  | ns    |

|                      | MISO delay (hold) low voltage                                                                                | V <sub>DDIO</sub> < 3 V | 0   | _   | 65  | ns    |

| T <sub>SS_SCLK</sub> | Time from SS LOW to first SCLK                                                                               | _                       | 125 | _   | _   | ns    |

| T <sub>SCLK_SS</sub> | Time from last SCLK to SS HIGH                                                                               | _                       | 125 | _   | _   | ns    |

# **Packaging Information**

This section provides the CYFP1 device packaging specifications.

В 0.32±0.05 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 . 4 15 16 17 A ABCDEFGH \$00000000000 J K LMNPRTU leD -- eE 0.422 A E **TOP VIEW** SIDE VIEW **BOTTOM VIEW** – DIE T = 200um ± 25um DETAIL A

Figure 18. 73-Ball BGA 8.87 × 9.26 × 0.70 mm

| 0)/14001 | DIMENSIONS |          |       |  |

|----------|------------|----------|-------|--|

| SYMBOL   | MIN.       | NOM.     | MAX.  |  |

| А        | -          | -        | 0.70  |  |

| A1       | 0.16       | -        | 0.26  |  |

| A2       | 0.414      | 0.514    | 0.614 |  |

| D        |            | 9.26 BSC |       |  |

| E        | 8.87 BSC   |          |       |  |

| D1       | 8.50 BSC   |          |       |  |

| E1       | 8.00 BSC   |          |       |  |

| MD       | 17         |          |       |  |

| ME       | 17         |          |       |  |

| N        | 73         |          |       |  |

| Ø b      | 0.27       | -        | 0.37  |  |

| eD       | 0.50 BSC   |          |       |  |

| eE       |            | 0.50 BSC |       |  |

#### NOTES:

- 1. ALL DIMENSIONS ARE IN MILLIMETERS.

- 2. SOLDER BALL POSITION DESIGNATION PER JEP95, SECTION 3, SPP-020.

- 3. "e" REPRESENTS THE SOLDER BALL GRID PITCH.

- 4. SYMBOL "MD" IS THE BALL MATRIX SIZE IN THE "D" DIRECTION.

SYMBOL "ME" IS THE BALL MATRIX SIZE IN THE "E" DIRECTION.

N IS THE NUMBER OF POPULATED SOLDER BALL POSITIONS FOR MATRIX SIZE MD X ME.

- (5) DIMENSION "b" IS MEASURED AT THE MAXIMUM BALL DIAMETER IN A PLANE PARALLEL TO DATUM C.

- 6 "SD" AND "SE" ARE MEASURED WITH RESPECT TO DATUMS A AND B AND DEFINE THE POSITION OF THE CENTER SOLDER BALL IN THE OUTER ROW.

WHEN THERE IS AN ODD NUMBER OF SOLDER BALLS IN THE OUTER ROW,

"SD" OR "SE" = 0.

- WHEN THERE IS AN EVEN NUMBER OF SOLDER BALLS IN THE OUTER ROW, "SD" = eD/2 AND "SE" = eE/2.

- 1 A1 CORNER TO BE IDENTIFIED BY CHAMFER, LASER OR INK MARK METALIZED MARK, INDENTATION OR OTHER MEANS.

- 8. "+" INDICATES THE THEORETICAL CENTER OF DEPOPULATED SOLDER BALLS.

002-10940 \*G

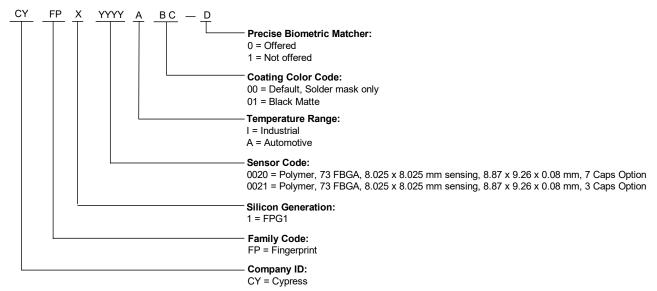

# Ordering Information

Table 11. CYFP1 Device Key Features and Ordering Information

| Silicon Type   | Package Type | Package Size             | Operating Temperature |  |

|----------------|--------------|--------------------------|-----------------------|--|

| CYFP10020I00   |              |                          |                       |  |

| CYFP10020I01   |              | 8.87 × 9.26 × 0.80 mm    |                       |  |

| CYFP10020I01-1 | 73-Ball BGA  |                          | Industrial            |  |

| CYFP10021I00   | 73-Dall DGA  | 12.20 × 12.20 × 0.80 mm  | เทนเรเทสเ             |  |

| CYFP10021I01   |              | 8.87 × 9.26 × 0.80 mm    |                       |  |

| CYFP10021I01-1 |              | 0.07 ^ 9.20 ^ 0.00 11111 |                       |  |

## **Part Ordering Code Definitions**

All devices in the CYFP1 family comply with the RoHS-6 specifications, demonstrating Cypress's commitment to Pb-free products. Lead (Pb) is an alloying element in solders, which has resulted in environmental concerns due to potential toxicity. Cypress uses the nickel-palladium-gold (NiPdAu) technology for a majority of the lead frame-based packages.

A high-level review of the Cypress Pb-free position is available on our website. Specific package information is also available. Package Material Declaration Datasheets (PMDDs) identify all substances contained within Cypress packages. PMDDs also confirm the absence of many banned substances. The information in the PMDDs will help Cypress customers plan for recycling or other "end-of-life" requirements.

# **Acronyms and Abbreviations**

Table 12. Acronyms Used in this Document

| Acronym                   | Description                  |

|---------------------------|------------------------------|

| AES                       | Advanced Encryption Standard |

| CPU                       | central processing unit      |

| Cu                        | copper                       |

| DNU                       | do not use                   |

| I/O                       | input/output                 |

| LDO                       | low dropout regulator        |

| MTK                       | manufacturing test kit       |

| SHA                       | Secure Hash Algorithm        |

| SNR signal-to-noise ratio |                              |

| SPI                       | serial peripheral interface  |

# **Document Conventions**

### **Units of Measure**

Table 13. Units of Measure

| Symbol   | Unit of Measure     |  |  |

|----------|---------------------|--|--|

| °C       | degrees celsius     |  |  |

| μA       | microampere         |  |  |

| μF       | microfarad          |  |  |

| μH       | microhenry          |  |  |

| μs       | microsecond         |  |  |

| μW       | microwatt           |  |  |

| Ω        | ohm                 |  |  |

| Hz       | hertz               |  |  |

| kΩ       | kilo-ohm            |  |  |

| kbps     | kilobits per second |  |  |

| kHz      | kilohertz           |  |  |

| mA       | milliampere         |  |  |

| mm       | millimeter          |  |  |

| ms       | millisecond         |  |  |

| mV       | millivolt           |  |  |

| mW       | milliwatt           |  |  |

| Mbps     | megabits per second |  |  |

| MHz      | Hz megahertz        |  |  |

| nA       | nanoampere          |  |  |

| ns       | nanosecond          |  |  |

| pF       | picofarad           |  |  |

| s second |                     |  |  |

## **Port Nomenclature**

$\label{eq:pxy} Px[y] \ describes a particular bit "y" available within an I/O port "x." \\ For example, P4[2] \ reads "port 4, bit 2."$

$\label{eq:pxyz} Px[y:z] \ describes \ a \ particular \ range \ of \ bits \ "y \ to \ z" \ within \ an \ I/O \ port \ named \ "Px." \ For \ example, \ P4[0:5] \ refers \ to \ bits \ 0 \ through \ 5 \ within \ an \ I/O \ port \ named \ P4.$

# Glossary

| core LDO                       | Low drop out regulator that sources power to the digital core when enabled. Input to the LDO is VDDD. Output of the LDO is connected to the digital supply pin VCCD. When the core LDO is bypassed, power must be externally applied to the digital core supply pin, VCCD.                                                |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RX                             | Receive. A touchscreen electrode or touchscreen controller sense pin, mapped or switched to a charge-sensing circuit within the controller (known as a receive channel).                                                                                                                                                  |  |  |

| scan                           | The conversion of all sensor capacitances to digital values.                                                                                                                                                                                                                                                              |  |  |

| signal-to-noise<br>ratio (SNR) | The ratio between a capacitive finger signal and system noise.                                                                                                                                                                                                                                                            |  |  |

| TEE                            | Trusted execution environment                                                                                                                                                                                                                                                                                             |  |  |

| тх                             | Transmit. A touchscreen electrode or touchscreen controller sense pin, mapped or switched to a charge-forcing circuit within the controller. This charge-forcing circuit drives a periodic waveform onto one or more touchscreen electrodes, which are coupled through mutual capacitance to adjacent receive electrodes. |  |  |

# **Document History Page**

| Document Title: CYFP1002XXXX, CYFP1-8080 Datasheet<br>Document Number: 002-11233 |         |                 |                    |                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------|---------|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                         | ECN     | Orig. of Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                 |

| **                                                                               | 5142522 | HFO             | 02/18/2016         | New datasheet.                                                                                                                                                                                                                                                                                                                        |

| *A                                                                               | 5359069 | HFO             | 08/19/2016         | Added CYFP1002XXXX to the title. Updated Features. Added board image on page 1. Updated Figure 1. Added Features Overview. Updated Table 1 and Table 2. Updated Figure 10. Updated Pin Information. Updated Example Schematic and Layout Guidelines. Added V <sub>DDIO</sub> spec in Table 6. Updated Part Ordering Code Definitions. |

| *B                                                                               | 5523251 | HFO             | 11/16/2016         | Updated Copyright and Disclaimer. Updated Features and Ordering Information. Updated Example Schematic and Layout Guidelines. Added Figure 12 through Figure 15.                                                                                                                                                                      |

| *C                                                                               | 5975003 | RLIT            | 11/23/2017         | Updated template<br>Updated package drawing (002-10940)                                                                                                                                                                                                                                                                               |

| *D                                                                               | 6288118 | PMAD            | 08/22/2018         | Updated template. Updated Features, Packaging Information, and Ordering Information.                                                                                                                                                                                                                                                  |

# Sales, Solutions, and Legal Information

#### **Worldwide Sales and Design Support**

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### **Products**

Wireless Connectivity

Arm® Cortex® Microcontrollers

Automotive

Clocks & Buffers

Interface

Internet of Things

Memory

Arm® Cortex® Microcontrollers

cypress.com/automotive

cypress.com/clocks

cypress.com/interface

cypress.com/iot

cypress.com/memory

cypress.com/mcu

PSoC cypress.com/psoc

Power Management ICs cypress.com/pmic

Touch Sensing cypress.com/touch

USB Controllers cypress.com/usb

cypress.com/wireless

# PSoC® Solutions

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6 MCU

#### **Cypress Developer Community**

Community | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

Cypress, the Cypress logo, Spansion, the Spansion logo, and combinations thereof, WICED, PSoC, CapSense, EZ-USB, F-RAM, and Traveo are trademarks or registered trademarks of Cypress in the United States and other countries. For a more complete list of Cypress trademarks, visit cypress.com. Other names and brands may be claimed as property of their respective owners.

Document Number: 002-11233 Rev. \*D Revised August 22, 2018 Page 25 of 25

<sup>©</sup> Cypress Semiconductor Corporation, 2016-2018. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and does not, except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress hereby grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.

TO THE EXTENT PERMITTED BY APPLICABLE LAW, CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS DOCUMENT OR ANY SOFTWARE OR ACCOMPANYING HARDWARE, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. No computing device can be absolutely secure. Therefore, despite security measures implemented in Cypress hardware or software products, Cypress does not assume any liability arising out of any security breach, such as unauthorized access to or use of a Cypress product. In addition, the products described in these materials may contain design defects or errors known as errata which may cause the product to deviate from published specifications. To the extent permitted by applicable law, Cypress reserves the right to make changes to this document without further notice. Cypress does not assume any individual composes of the application or use of any product or circuit described in this document. Any information provided in this document, including any sample design information or programming code, is provided only for reference purposes. It is the responsibility of the user of this document to properly design, program, and test the functionality and safety of any application made of this information and any resulting product. Cypress products are not designed, intended, or authorized for use as critical components in systems designed or intended for the operation of weapons, weapons systems, nuclear installations, life-support devices or systems devices or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances management, or other uses where the failure of the device or systems (including resuscitation equipment and surgical implants), pollution control or hazardous substances resulted to a proper the proper devices. Cypress from any claim, damage, or other liability arising from or related to all Unintended Uses of Cypress products. You shall indemnify and hold Cypress harmless f