### CYIWOSC1300AA

### Features

- 1.3-megapixel resolution (1297H x 1041V)

- 2.8µ x 2.8µ pixel size

- 1/4" optical format image sensor

- Progressive scan

- On-board readout sequencer

- Up to 17 frames per second at full resolution

- Fast preview/snapshot switching with dynamic power management

- · Bidirectional serial command interface

- 10-bit parallel data port

- Low-power high frame rate preview mode

- Programmable frame size/rate, gain, exposure, blanking, left-right and up-down image reversal, windowing, auto black level offset correction, and panning

### Applications

- Cellular phone camera modules

- Pocket PCs

- PDAs

- Toys

- Battery operated device

www.DataSheet4U.com

# 1.3 Megapixel CMOS Sensor

### Table 0-1. Key Performance Parameters

| Parameter                 | Typical Value                                                                                            |

|---------------------------|----------------------------------------------------------------------------------------------------------|

| Pixel size                | 2.8μ x 2.8μ                                                                                              |

| Array format              | 1297H x 1041V                                                                                            |

| Imaging area              | 3.6 mm x 2.9 mm                                                                                          |

| Color filter array        | RGB Bayer                                                                                                |

| Optical format            | 1/4 inch                                                                                                 |

| Frame rate                | 15 fps @ 1280H x 1024V<br>60 fps @ 640H x 480V                                                           |

| Scan mode                 | Progressive                                                                                              |

| Sensitivity               | ТВА                                                                                                      |

| Dynamic range             | ТВА                                                                                                      |

| Shutter type              | Electronic rolling shutter                                                                               |

| ADC                       | 10-bit                                                                                                   |

| Programmable controls     | Frame size, frame rate, gain,<br>exposure, black, offset<br>correction, all directions<br>image flipping |

| Flash support             | LED and Xenon                                                                                            |

| Pixel rate                | 24 Mps @ 24-MHz clock                                                                                    |

| Input clock range         | 4–27 MHz                                                                                                 |

| Exposure time range       | 64 µs–66 ms                                                                                              |

| On-chip voltage regulator | 2.65–3.1V / 1.8V                                                                                         |

| Supply voltage            | Analog: 2.6–3.1V<br>Digital: 1.7–1.9V or<br>2.65–3.1V<br>IO: 1.7–3.1V                                    |

| Power consumption         | ТВА                                                                                                      |

| Operating temperature     | –20 to +70°C                                                                                             |

| Package                   | ТВА                                                                                                      |

### CYIWOSC1300AA

### TABLE OF CONTENTS

| FEA        | ATURES                                                                                                                                                                                                                                                                                                                                                                    | .1                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| APF        | PLICATIONS                                                                                                                                                                                                                                                                                                                                                                | .1                                                                               |

| 1.0        | GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       | .4                                                                               |

| 2.0        | FUNCTIONAL OVERVIEW                                                                                                                                                                                                                                                                                                                                                       | .5                                                                               |

| 3.0        | SIGNAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                        | .6                                                                               |

| 4.0        | PIXEL ARRAY STRUCTURE                                                                                                                                                                                                                                                                                                                                                     | .7                                                                               |

| 5.0        | TYPICAL USE SCENARIO                                                                                                                                                                                                                                                                                                                                                      | .8                                                                               |

| 6.0        | DATA READ OUT                                                                                                                                                                                                                                                                                                                                                             | .9                                                                               |

|            | 6.1 Frame Timing         6.2 Frame Sequence Structure         6.3 Controlling the Sequencer                                                                                                                                                                                                                                                                               | 10                                                                               |

| 7.0        | SERIAL BUS DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    | 12                                                                               |

|            | 7.1 16-bit Write Access Procedure                                                                                                                                                                                                                                                                                                                                         | 12<br>13                                                                         |

| 8.0        | REGISTERS                                                                                                                                                                                                                                                                                                                                                                 | 15                                                                               |

|            | 8.1 Register Map                                                                                                                                                                                                                                                                                                                                                          | 15                                                                               |

| 9.0        | FEATURE DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                      | 26                                                                               |

| www.DataSt | 9.1 Efficient Well Pixel<br>9.2 Windowing<br>9.3 Subsampling<br>9.4 Flash Synchronization<br>9.5 Xenon Flash<br>9.6 LED Flash<br>9.7 Normal Operation Mode<br>9.8 Standby Mode<br>9.9 Idle Mode<br>9.9 Idle Mode<br>9.10 Readout Modes<br>9.11 Viewfinder Mode<br>9.12 Snapshot Mode<br>9.13 Power-on Reset<br>9.14 On-Chip Pixel Binning<br>0.1.3MP IMAGER PAD NUMBERING | 26<br>26<br>26<br>27<br>27<br>27<br>27<br>27<br>27<br>28<br>28<br>28<br>28<br>28 |

|            | DELECTRICAL SPECIFICATIONS                                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|            | 11.1 Absolute Maximum Ratings         11.2 Operating Conditions         11.3 Electrical Characteristics <b>D ENVIRONMENTAL SPECIFICATIONS</b>                                                                                                                                                                                                                             | 31<br>31<br>31                                                                   |

| 12.0       |                                                                                                                                                                                                                                                                                                                                                                           | )                                                                                |

### CYIWOSC1300AA

### LIST OF FIGURES

| Figure 1-1. Block Diagram<br>Figure 2-1. Typical Configuration using On-chip Regulator | 4    |

|----------------------------------------------------------------------------------------|------|

| Figure 2-1. Typical Configuration using On-chip Regulator                              | 5    |

| Figure 2-2. Typical Configuration without On-chip Regulator                            | 5    |

| Figure 4-1 Pixel Array                                                                 | 7    |

| Figure 5-1. Typical Usage                                                              | 8    |

| Figure 6-1. Regular Frame Readout Sequence with Accompanying Signals                   | 9    |

| Figure 6-2. FRAME and LINE Timing                                                      |      |

| Figure 6-3. Horizontal Timing with PIX_CLK the Inverse of the Internal Chip Clock CLK  | 9    |

| Figure 6-4. Typical Frame Sequence                                                     |      |

| Figure 6-5. Frame Sequence with Addition of a Very Large Number of Dummy Lines         | .10  |

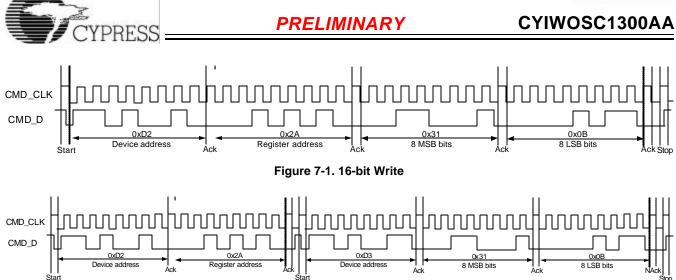

| Figure 7-1 16-bit Write                                                                | 13   |

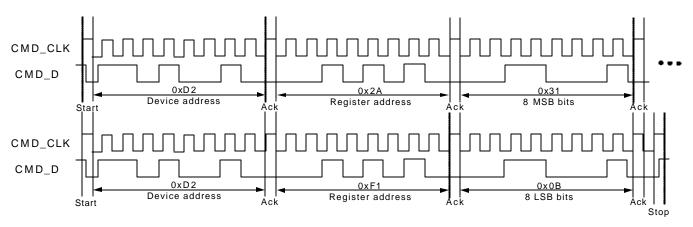

| Figure 7-2. 16-bit Read                                                                | . 13 |

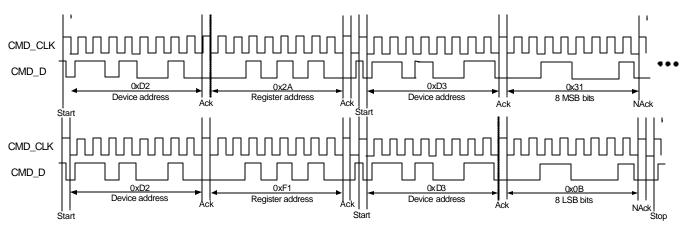

| Figure 7-2. 16-bit Read<br>Figure 7-3. 8-bit Write                                     | . 13 |

| Figure 7-4. 8-bit Read                                                                 | . 14 |

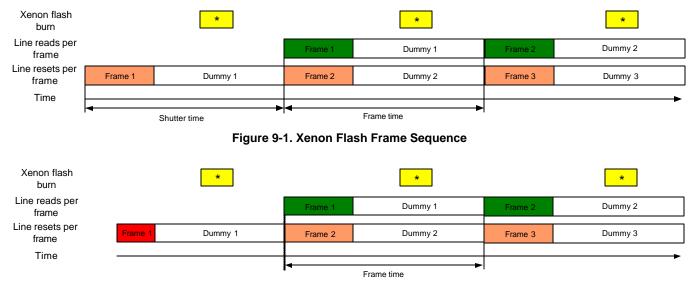

| Figure 9-1. Xenon Flash Frame Sequence                                                 | . 26 |

| Figure 9-2. Xenon Flash Sequence with Accelerated Initial Reset                        | .26  |

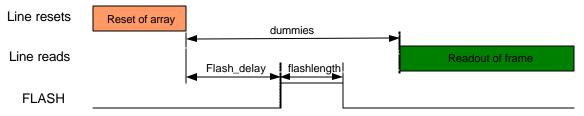

| Figure 9-3. Xenon FLASH Strobe Timing Configuration                                    |      |

### LIST OF TABLES

| Table 0-1. Key Performance Parameters  | 1 |

|----------------------------------------|---|

| Table 10-1. Pin Map Table (Left Side)  |   |

| Table 10-2. Pin Map Table (Right Side) |   |

| Table 11-1.                            |   |

| Table 12-1                             |   |

www.DataSheet4U.com

### **1.0 General Description**

Cypress Semiconductor Corporation's (Cypress's) CYIWOSC1300AA is a 1.3-megapixel (SXGA) CMOS digital image sensor. It has a 1/4-inch active-pixel format, with an active imaging pixel array of 1297x1041 pixels and on-board readout sequencer. The device captures Bayer-pattern color still pictures, and offers a low-power video preview mode. Defective pixels are interpolated instantaneously to make them invisible in the output image.

Most of the chip's image readout parameters are doubled-up into two separate records, allowing the user to change from preview mode to snapshot and back in a minimum of time.

The imager also integrates features like programmable gain/exposure control and black level calibration. The sensor equips cameras with a frame rate of up to 15 fps at full resolution and image windowing to any size, while sustaining smooth, continuous video preview at reduced power consumption. The CMOS technology has the advantage of having a smaller form factor, lower power consumption, lower cost and ease of design compared to CCD.

The 1.3-Mp sensor operates in a system accepting commands from a bidirectional serial interface and deliver raw single images or video-like streams of raw Bayer-patterned images through a 10-bit parallel data interface. The low-power viewfinder mode enhances the support for battery-operated platforms. Automatic flash sequencing and single-supply operation provides reduced complexity of the camera system. The device runs off an external clock, ideally in the range of 20 to 27 MHz.

This sensor has no micro-lenses and yet can achieve a 70% fillfactor ratio, using Cypress proprietary process technology. It helps increase process yield and lower system cost.

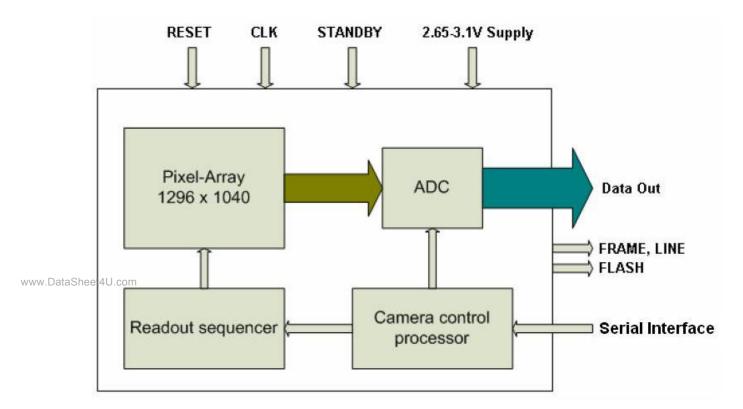

Figure 1-1. Block Diagram

# CYPRESS

### 2.0 Functional Overview

The analog core of the chip is comprised of the actual image sensor with its column amplifiers and addressing logic, and an analog processing block with a Programmable Gain Amplifier (PGA), and a 10-bit ADC. The column amplifiers perform double sampling on the pixel signals, thus reducing fixed pattern noise due to pixel non-uniformity.

The output of the column amplifiers is a single analog signal stream of Bayer-colored pixels, which is sent to the PGA for additional gain and offset conditioning. The single ADC accepts this stream and turns it into a 10-bit digitized stream of Bayer-colored pixel values.

The readout sequencer performs automated readout of images with given exposure time and gain settings. Mirrored readout and frame time adjustments are programmable.

Most of the chip's image readout parameters are doubled-up into two separate records, allowing the user to change from preview mode to snapshot and back in a minimum of time.

The output from the sensor is a Bayer pattern: alternate rows are a sequence of either green/red pixels or blue/green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

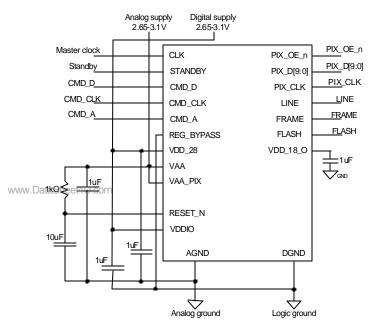

Figure 2-1. Typical Configuration using On-chip Regulator

*Figure2-1* shows a typical module wiring diagram. When using the on-chip regulator REG\_BYPASS has to be connected to ground. VDD\_28 can be connected to a 2.65–3.1V supply like all other power supplies. There must be sufficient decoupling on the supplies to insure clean supply voltages. Note that RESET\_N is typically connected with an RC circuit to hold RESET\_N low until all power supplies have reached their proper level.

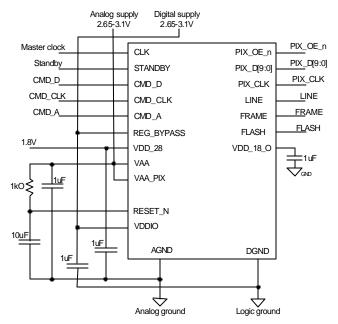

Figure 2-2. Typical Configuration without On-chip Regulator

*Figure2-2* shows a typical module wiring diagram. When not using the on-chip regulator REG\_BYPASS and the VDD\_28 have to be connected to their appropriate levels. VDD\_28 has to be connected to a 1.8V supply. There must be sufficient decoupling on the supplies to insure clean supply voltages. Note that RESET\_N is typically connected with an RC circuit to hold RESET\_N low until all power supplies have reached their proper level.

### 3.0 Signal Description

| Signal Name | I/O | #Pins | Function                                                                                                     |  |  |  |

|-------------|-----|-------|--------------------------------------------------------------------------------------------------------------|--|--|--|

| CLK         | Ι   | 1     | System clock, 4 27 MHz                                                                                       |  |  |  |

| RESET_n     | Ι   | 1     | Asynchronous reset                                                                                           |  |  |  |

| STANDBY     | Ι   | 1     | Turns off device                                                                                             |  |  |  |

| CMD_D       | I/O | 1     | Interface serial data in and out                                                                             |  |  |  |

| CMD_CLK     | Ι   | 1     | Interface bit clock, up to 400 kHz                                                                           |  |  |  |

| CMD_A       | Ι   | 1     | Interface device address selector                                                                            |  |  |  |

| PIX_OE_n    | I   | 1     | Output enable for PIX_D, PIX_CLK, FRAME, LINE, EXT, FLASH                                                    |  |  |  |

| PIX_D[9:0]  | O/Z | 10    | Output pixel data                                                                                            |  |  |  |

| PIX_CLK     | O/Z | 1     | Output pixel data word clock                                                                                 |  |  |  |

| EXT[1:0]    | O/Z | 2     | Extension port for debug                                                                                     |  |  |  |

| FRAME       | O/Z | 1     | Frame valid strobe                                                                                           |  |  |  |

| LINE        | O/Z | 1     | Line valid strobe                                                                                            |  |  |  |

| FLASH       | O/Z | 1     | Flash strobe                                                                                                 |  |  |  |

| VAA         | PWR | 2     | Sensor core/ADC analog supply (2.65–3.1V)                                                                    |  |  |  |

| VAA_PIX     | PWR | 1     | Pixel array supply (2.65–3.1V)                                                                               |  |  |  |

| AGND        | GND | 3     | Sensor core/ADC analog ground                                                                                |  |  |  |

| VAA_DIG     | PWR | 1     | Sensor core digital supply (2.65–3.1V)                                                                       |  |  |  |

| AGND_DIG    | GND | 1     | Sensor core/ADC digital ground                                                                               |  |  |  |

| VDD_28      | PWR | 1     | Raw logic supply in; connect to 2.65–3.1V when regulator is used, otherwise to 1.7–1.9V                      |  |  |  |

| DGND        | GND | 2     | Logic ground                                                                                                 |  |  |  |

| REG_BYPASS  | Ι   | 1     | Puts regulator in bypass, use only when VDD_28 = 1.8V                                                        |  |  |  |

| VDD_18_0    | PWR | 2     | Regulated 1.8V logic supply out; connect to bypass capacitor only (two pads, for bonding to one package pin) |  |  |  |

| VDDIO       | PWR | 3     | IO supply (1.7–3.1V)                                                                                         |  |  |  |

| DGNDIO      | GND | 3     | IO ground                                                                                                    |  |  |  |

| RESET_OUT   | 0   | 1     | Internal reset net out (POR test only)                                                                       |  |  |  |

www.DataSheet4U.com

### 4

### 4.0 Pixel Array Structure

The sensor device is a camera on a CMOS chip imager with 1.3-megapixel resolution (SXGA) in a 1/4" optical format.

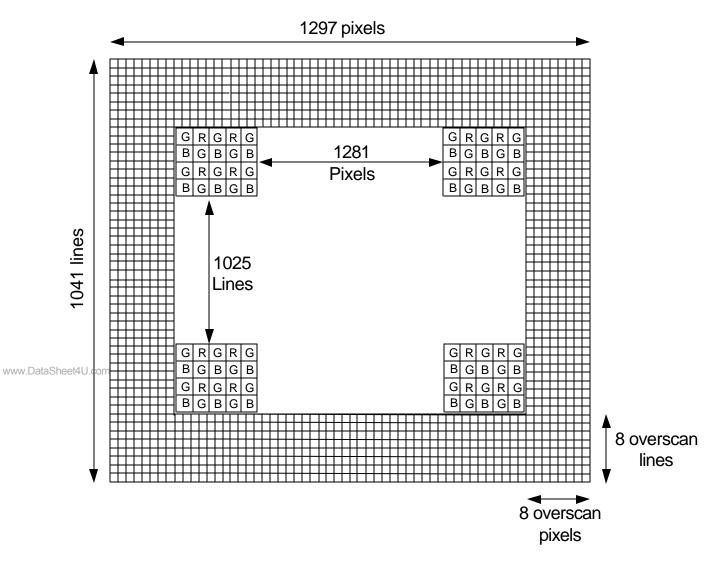

*Figure4-1* below shows the layout of the Pixel Array. The pixel plane consists of a total of 1041 lines, numbered 0 to 1040, each of 1297 pixels, numbered 0 to 1296. All lines are sensitive to light and pixels are optically active and addressable. All pixels can be addressed for readout. A border of width 8 at the periphery of the array, the overscan area, will be used only for image processing boundary conditioning, while

the central 1281x1025 area can be output to the end-user. The number of lines and pixels is odd to assure invariance of color pattern when mirrored readout is used.

The sensor is designed with a mosaic of color filters arranged in a standard Bayer pattern shown in *Figure4-1*. The even numbered columns contain green and red pixels and the even rows contain red and green pixels. The imager will output either all Bayer patterned pixels or all physical pixels based upon register settings.

Figure 4-1. Pixel Array

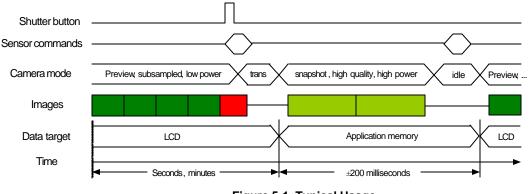

### 5.0 Typical Use Scenario

The following describes a typical scenario of camera usage.

The camera starts in a viewfinder mode, displaying images at video rate (15 to 30 frames/s) on the mobile application LCD. As LCDs are typically of low resolution and low accuracy, the sensor can be run at a smaller image size and a lower image quality. This then allows power consumption to be reduced. This is relevant in a battery-powered application, as most users will run their cameras in viewfinder/preview mode for 99% of the camera-on time. When the end-user then wants to take a picture and store it in the camera's memory, he pushes the shutter release button. This action is communicated to the application processor, which then sends a stream of commands to the sensor chip.

These commands cause the sensor chip to:

- 1. Stop the present image acquisition

- 2. If the present image was an incomplete acquisition, eliminate any effect its data might have on the ISP (red frame in the figure).

- 3. Reconfigure itself for high-quality, high-power, full-frame image capture.

- Capture a short sequence of images, one or more of them to be written by the application processor into cellphone memory

- 5. When finished, await a new command to re-enter the preview mode.

Figure 5-1. Typical Usage

www.DataSheet4U.com

#### www.DataSheet4U.com

### CYIWOSC1300AA

### 6.0 Data Read Out

The imager is read out in a progressive scan fashion. This means that each successive row is read out in an increasing row number. The data are digitized via on-chip A/D converters and the output resolution is at a 10-bit resolution.

All of the lines are scanned at the same speed, all of them being scanned in the line time. The frame rate is the inverse of the total sum of line times, and the maximum exposure time is the total sum of line times.

The resolution is set by three factors. The resolution may be decreased by sub-windowing a smaller region of interest (ROI) as set in the internal registers. The imager can also be programmed to sub-sample the array to read out as much as at a 4-time rate. In 4x4 subsampling mode both lines and pixels are read in a 1:1:0:0:0:0:0:0 pattern (read-2-skip-6). This quarters the number of lines in a frame, as well as the number of pixels in a line. Also a 2x2 subsampling mode is user programmable. Finally, the imager can be programmed to bin (combine) adjacent pixels of similar color in one direction with strength of2.

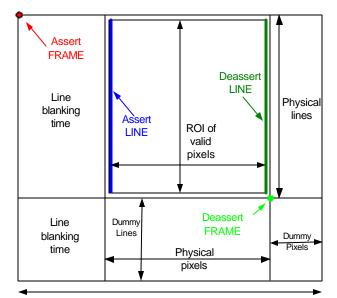

#### 6.1 Frame Timing

Figure 6-1 shows a regular frame readout sequence with accompanying strobe signals. The FRAME and LINE strobe signals depend on the LN\_FORM and FR\_FORM register settings. We assume here that they are both set to 1. The FRAME pulse is asserted at the start of the first line that is physically read from the pixel array. This and the following lines are typically overscan lines used for preconditioning processing pipelines. These overscan areas are defined by the physical pixel area as shown in Figure 6-1. FRAME is not asserted whenever the present image is blanked out (see \*\_BLANK\_FIRST and \*\_BLANK\_PERIOD). LINE is asserted to qualify those lines that belong to the ROI, and is asserted at the first pixel in the ROI of each such line. LINE is deasserted at the last pixel belonging to the ROI. FRAME is deasserted at the last line and last pixel of the overscan area, or the lowerright edge of the physically-scanned area.

www.

As can be seen from *Figure6-1* it is possible to set a number of dummy lines/pixels. These pixels will follow the same

#### Figure 6-1. Regular Frame Readout Sequence with Accompanying Signals

readout rate as the pixels in the ROI but will fall outside the Line/FRAME pulses. Therefore they should be discarded by the camera system. The number of dummy lines/pixels is programmable to set integration times longer than the ROI readout time and to give the accompanying peripheral devices (e.g., ISP) time to process the image data. The minimum amount of dummy pixels/lines should be a multiple of 8. Using the appropriate registers the number of overscan pixels (physical pixels) is also programmable for image processing boundary conditioning.

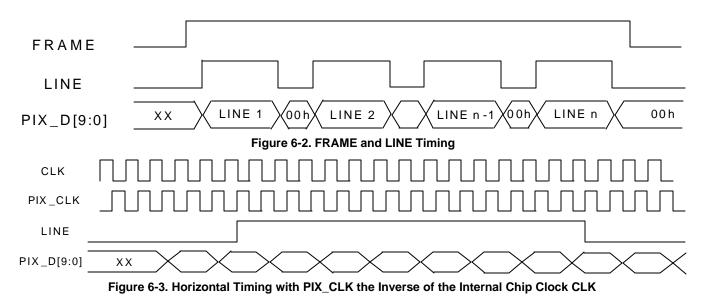

*Figure6-2* indicates the timing of the FRAME and LINE synchronization signals relative to the datastream on the PIX\_D bus.

*Figure6-3* depicts the horizontal/pixel timing on the parallel data interface.

PIX\_D bytes change state on a falling edge of PIX\_CLK, and are to be sampled on the rising edge, or vice versa, as programmed by the user.

PIX\_CLK is active for all physically scanned pixels (also for dummy pixels) and is inactive during line blanking intervals.

PIX\_CLK is a gated and possibly inverted copy of the internal chip clock. In normal operation the internal clock is equal to the system clock CLK, but in low-power operation the internal clock, and thus PIX\_CLK, can be divided by 2 or 4.

### 6.2 Frame Sequence Structure

#### 6.2.1 Overview

The acquisition of a number of frames is an operation that is started by the CCP (camera control processor), following which the sequencer first initializes the sequence, then takes the frames in a regular, periodic fashion, and (when needed) terminates the sequence. The frame sequence itself can be adorned by optional attributes such as blanking out of a specific number of frames, blanking out of bad frames, Xenon flash ignition between two frames, etc.

Within the sequence of frames will be specific synchronization points for updating image-sensitive parameters such as exposure time and gain, without disrupting the frame sequence itself.

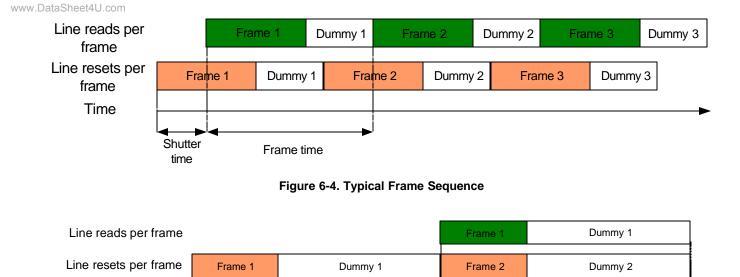

#### 6.2.2 Frame Timelines Examples

The following timelines indicate a number of possible scenarios. The lower/orange band in each diagram houses the periods during which the lines of a frame are reset (top to bottom), the upper/green band the periods during which the lines are read out (top to bottom).

The frame size is kept constant (number of valid lines), but the number of dummy lines is varied to demonstrate several concepts of readout.

In *Figure6-4*, the shutter time is considerably shorter than the frame time. A moderate amount of dummy lines is included, extending the frame time somewhat.

As the diagram indicates, the acquisition of a sequence of frames is a periodic, regular process: at all times is one line of a particular frame being read, while a line belonging to that same frame, or to the next frame, is being reset.

The one exception to this rule is during sequence initialization: the first N lines (N corresponding to the desired exposure time) of the first frame are reset, while no lines of frame 1 are being read.

*Figure6-5* illustrates a typical frame sequence with the exposure/shutter time (almost) equal to the total frame time.

This increases the maximally-allowed exposure time much more than in previous diagrams, while the frame rate is severely reduced. It illustrates increased exposure time at the cost of a lowered frame rate. This is only to be done when sufficient light is lacking and when the camera is held stable.

#### 6.3 Controlling the Sequencer

An image or sequence acquisition is started when a positive edge is seen on the RUN bit in the CCP\_CTRL register.

When CCP\_CTRL is updated with a RUN transition from '0' to '1' (or remains at '1', see AUTO\_START bit), any present image acquisition sequence is stopped (also see FAST\_STOP bit) and a new acquisition is started in a potentially new record (see CTXT bit).

A frame sequence ends normally when the frame counter (N\_FRAMES) is at zero after the last (dummy) line of a frame has been produced be the sequencer.

Deassertion of RUN at any time makes the sequencer finish its present line, after which it stops scanning and enters its idle state (also see FAST\_STOP bit in the CCP\_CTRL register).

Frame time Frame time Frame time

Time

### 7.0 Serial Bus Description

The CYIWOSC1300AA interfaces with an external ISP through a bidirectional serial command interface and a unidirectional parallel data bus, in addition to a small number of direct-control pins for frame, line and flash synchronization, for device reset, for regulator configuration, and for the standby mode.

The device requires an external clock oscillator (up to 27 MHz) and a small number of strap connections to configure the device.

All I/O is CMOS IO with a programmable voltage range of 1.7–3.1V. All logic inputs have no leakage when they are driven high while the chip supply voltage is low/off.

The device control interface is compatible with the Philips I2C version 2.1 bus specification.

The device acts as a slave only, requiring the system host to act as the master. The device address can be selected from two addresses that are hard-wired on the chip, enabling the use of up to two identical devices simultaneously on the same bus. The address selection happens with the CMD\_A pin.

| CMD_A | Internal I2C Device Address |

|-------|-----------------------------|

| 0     | 0xD2                        |

| 1     | 0xD4                        |

The D2h address is the same slave address as used on Cypress's programmable clock chips. This address does not collide with the most obvious competing image sensor chips.

The D4h address is an arbitrary modification of the device address to allow two identical sensor chips on the same command bus.

The command interface supports writing to and reading from 16-bit internal registers, with 8-bit address locations, at speeds of up to 400 kbits/s.

The interface clock CMD\_CLK and the address pin CMD\_A

up to a positive supply voltage by an off-chip resistor and can be pulled down both by the master and the slave device. The serial interface protocol determines which device can drive the data pin at any given time.

Data transfers to/from each 16-bit register can be 16 bits at once, the upper 8 bits, or the lower 8 bits. After any complete 16-bit transfer the internal register address is incremented automatically, anticipating the next similar transfer. There is no auto address increment for 8 bit transfers.

The bus is idle when both the CMD\_CLK and CMD\_D pins are HIGH. Control of the bus is initiated by a start bit (beginning of an access) and the bus is released again with a stop bit (end of the access). Only the master can generate these signals.

The transmission protocol defines several transmission codes:

- A start bit: The start bit is defined as a HIGH-to-LOW transition of the data line when the clock line is HIGH.

- The slave 8-bit address: The 7 MSB bits contain the device address: 0xD4 when CMD\_A is HIGH and 0xD2 when CMD\_A is LOW. The LSB bit of this address determines whether the request is a write (value is "0") or a read (value is "1").

- An acknowledge or no-acknowledge bit: This is the way for the receiver (either the slave in write mode or the master in read mode) to acknowledge the data sent by the transmitter. The master generates the acknowledge clock pulse. When the receiver pulls down the data line during that clock pulse, the previous byte is acknowledged. When the data line is not pulled down, the previous byte is NOT acknowledged. A no-acknowledge is used to terminate a read or a write sequence.

- An 8-bit message (register address or data byte): One data bit is transferred during each clock pulse. Data is always transferred 8 bits at a time, starting with the MSB bit, during 8 consecutive clock cycles, followed by an acknowledge bit.

- A stop bit: The stop bit is defined as a LOW-to-HIGH transition of the data line while the clock line is HIGH.

Except for the start and the stop bit, the data pin must always be stable during the HIGH period of the serial interface clock. It can only change when the clock is LOW.

### 7.1 16-bit Write Access Procedure

A 16-bit write access is performed as follows

- 1. The master sends a Start bit.

- 2. The master sends the 8-bit slave device address. The last bit will be set to "0".

- 3. The slave acknowledges the address by sending the acknowledge bit back to the master.

- 4. The master sends the 8-bit register address to which a write should take place.

- 5. The slave sends an acknowledge bit to indicate that the register address was correctly received.

- 6. The master then transfers the data, 8 bits at a time. Internally, all register addresses have 16 bits, thus requiring two 8-bit transfers to write to one register.

- 7. The slave acknowledges every 8-bit word.

- 8. After every two 8-bit words written, the register address is automatically incremented, so that the next 16 bits are written to the next register address.

- 9. Steps 6, 7, and 8 are repeated for writing batches of data on consecutive register addresses.

- 10.The master stops the access by sending a Start or a Stop bit.

*Figure7-1* gives an example of a 16-Bit write access (value 0x310b) to register 0x2a.

### 7.2 16-bit Read Access Procedure

A typical 16-bit read access is performed as follows:

- 1. The master sends a Start bit.

- 2. The master sends the 8-bit slave device address. The last bit will be set to "0" because the register address will be written first.

- 3. The slave acknowledges the address by sending the acknowledge bit back to the master.

- 4. The master sends the 8-bit register address to which a read should take place.

### Figure 7-2. 16-bit Read

- 5. The slave sends an acknowledge bit to indicate that the register address was correctly received. The write access to set the register address is now finished.

- 6. The master sends a new Start bit.

- 7. The master sends the 8-bit slave device address. The last bit will be set to "1" for the actual read accesses.

- 8. The slaves transfers the data, 8 bits at a time. Internally, all register addresses have 16 bits, thus requiring two 8-bit transfers to read one register.

- 9. The master acknowledges every 8-bit word.

- 10.After every two data bytes written, the register address is automatically incremented, so that the next 16 bits are read from the next register address.

- 11.Steps 8, 9, and 10 are repeated for reading batches of data on consecutive addresses.

- 12. The data transfer is stopped when the master or slave sends a no-acknowledge bit.

- www. D3 The master generates a Start or Stop bit to finish the read access.

#### 7.3 8-bit Write Access Procedure

To be able to write one byte at a time to the register, a special register address is added. The 8-bit write is started by writing the 8 MSB bits to the desired register, then writing the lower 8

bits to the special register (0xF1). The register is not updated until all 16 bits have been written. It is not possible to update just half of a register.

An 8-bit write access is performed as follows

- 1. The master sends a Start bit.

- 2. The master sends the 8 bit slave device address. The last bit will be set to "0".

- 3. The slave acknowledges the address by sending the acknowledge bit back to the master.

- 4. The master sends the 8-bit register address to which a write should take place.

- 5. The slave sends an acknowledge bit to indicate that the register address was correctly received.

- 6. The master then transfers the 8 MSB bits of the data.

- 7. The slave acknowledges the 8-bit word.

- 8. The master sends a Stop bit when the second part of the word is not written immediately.

- Steps 1 to 8 are repeated for writing the 8 LSB bits. The only differences are the usage of the special address register (0xf1) instead of the real register address and replacing the MSB bits by the LSB bits.

The register address and the 8 MSB bits need to be stored temporarily.

Figure 7-3. 8-bit Write

### 7.4 8-bit Read Access Procedure

To read one byte at a time, the same special register address is used for the lower byte. The 8 MSB bits are read from the desired register. By following this with a read from the special register, the 8 LSB bits are accessed. The master sets the noacknowledge bits shown.

- A typical 8-bit read access is performed as follows:

- 1. The master sends a Start bit.

- 2. The master sends the 8-bit slave device address. The last bit will be set to "0" because the register address will be written first.

- 3. The slave acknowledges the address by sending the acknowledge bit back to the master.

- 4. The master sends the 8-bit register address to which a read should take place.

- 5. The slave sends an acknowledge bit to indicate that the register address was correctly received. The write access to set the register address is now finished.

- 6. The master sends a new Start bit.

- 7. The master sends the 8-bit slave device address. The last bit will be set to "1" for the actual read accesses.

- 8. The slaves transfers the 8 MSB bits.

- 9. The master sends a no-acknowledge.

Steps 1 to 9 are repeated for the read procedure of the 8 LSB bits. This time, the register address used is the special register address (0xf1) and the slave will return the 8 LSB bits.

Figure 7-4. 8-bit Read

www.DataSheet4U.com

CYIWOSC1300AA

### 8.0 Registers

### 8.1 Register Map

The imager has 8-bit-wide register addresses that contain 16-bit-wide register values. All registers are explained in the tables below.

| Address            | Register Name           | Reset Value | R/W | Description                                                                                                |

|--------------------|-------------------------|-------------|-----|------------------------------------------------------------------------------------------------------------|

| 0                  | CONFIG1                 | 0x0000      | R/W | configuration register 1, only upload value as described ir this table                                     |

| 1                  | CCP_ID                  | 0x0350      | R/- | device identification code                                                                                 |

| 3 CCP_CTRL         |                         | 0x0000      | R/W | camera control register (start/stop, record switch, Xenon flash)                                           |

| 4 CCP_CONFIG       |                         | 0x0000      | R/W | camera control configuration register (record clock division, Xenon flash arming)                          |

| 5                  | CCP_GLOBAL              | 0x0000      | R/W | camera control global settings (gain change synchroni-<br>zation, subsampling, binning, LED flash control) |

| 6                  | CCP_STAT                | 0x0000      | R/- | camera control status (record, clock, and run status)                                                      |

| 16                 | CONFIG2                 | 0x5F9C      | R/W | Configuration register 2, see CONFIG2 table below for more details                                         |

| 17                 | CONFIG3                 | 0x0077      | R/W | Configuration register 3 see CONFIG3 table below for more details                                          |

| 18                 | CONFIG4                 | 0x0077      | R/W | Configuration register 4 see CONFIG4 table below for more details                                          |

| 19                 | CONFIG5                 | 0x0077      | R/W | Configuration register 5 see CONFIG5 table below for more details                                          |

| 22                 | CONFIG6                 | 0x0777      | R/W | Configuration register 6, see CONFIG6 table below for more details                                         |

| 23                 | SEQ_A_FRAMES            | 0x0000      | R/W | record A number of frames to grab and blank frame(s) configuration                                         |

| 24                 | SEQ_B_FRAMES            | 0x0000      | R/W | record B number of frames to grab and blank frame(s) configuration                                         |

| 25                 | SEQ_A_ORIG              | 0x0000      | R/W | record A start of physical scan window                                                                     |

| <b>26</b> Sheet4U. | <sub>C</sub> ŞEQ_B_ORIG | 0x0000      | R/W | record B start of physical scan window                                                                     |

| 27                 | SEQ_A_SIZE              | 0x82A2      | R/W | record A size of physical scan window                                                                      |

| 28                 | SEQ_B_SIZE              | 0x82A2      | R/W | record B size of physical scan window                                                                      |

| 29                 | SEQ_A_ORIG_ROI          | 0x0101      | R/W | record A start of region of interest window                                                                |

| 30                 | SEQ_B_ORIG_RO           | 0x0101      | R/W | record B start of region of interest window                                                                |

| 31                 | SEQ_A_SIZE_ROI          | 0x80A0      | R/W | record A size of ROI window                                                                                |

| 32                 | SEQ_B_SIZE_ROI          | 0x80A0      | R/W | record B size of ROI window                                                                                |

| 33                 | SEQ_A_DUMMY             | 0x0100      | R/W | record A number of dummy lines and pixels                                                                  |

| 34                 | SEQ_B_DUMMY             | 0x0100      | R/W | record B number of dummy lines and pixels                                                                  |

| 38                 | SEQ_FLASH1              | 0x0041      | R/W | flash configuration 1: flash firing delay, Xenon strobe leng                                               |

| 39                 | SEQ_FLASH2              | 0x0011      | R/W | flash configuration 2: flash frame definition, number of frames to flash in                                |

| 40                 | CONFIG7                 | 0x2F85      | R/W | Configuration register 7, see CONFIG7 table below for more details                                         |

| 41                 | CONFIG8                 | 0x4C7E      | R/W | Configuration register 8, see CONFIG8 table below for more details                                         |

| 42                 | CONFIG9                 | 0x1097      | R/W | Configuration register 9, see CONFIG9 table below for more details                                         |

| 43                 | CONFIG10                | 0x000A      | R/W | configuration register 10, only upload value as describe in this table                                     |

| Address      | Register Name | Reset Value | R/W | Description                                                                                                                                                                                                                                                                                                         |

|--------------|---------------|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44           | SEQ_STATUS    | 0x0000      | R/- | sequencer status and BIST result: present black residue<br>BIST result, flicker detection results                                                                                                                                                                                                                   |

| 45           | SEQ_EXP       | 0x0400      | R/W | exposure time                                                                                                                                                                                                                                                                                                       |

| 46           | SEQ_GAIN      | 0x3F80      | R/W | gain and offset for preamp and PGA                                                                                                                                                                                                                                                                                  |

| 64           | OUT_CONFIG    | 0x0000      | R/W | output interface configuration: timing and polarity of PIX_CLK, FRAME, LINE                                                                                                                                                                                                                                         |

| 128          | ISP_DEFECT    | 0x0002      | R/W | defect pixel interpolator configuration                                                                                                                                                                                                                                                                             |

| 241          | ACCESS_MODE   | 0x0000      | R/W | special access mode register for 8-bit serial register reac<br>and write                                                                                                                                                                                                                                            |

| Address      | Register Name | Reset Value | R/W | Clients / Description                                                                                                                                                                                                                                                                                               |

| 1            | CCP_ID        | 0x0350      | R/- | Interface registers Device identification code                                                                                                                                                                                                                                                                      |

| Bits         |               |             |     |                                                                                                                                                                                                                                                                                                                     |

| 3:0          | REV[3:0]      | 0d          |     | revision                                                                                                                                                                                                                                                                                                            |

| 5:4          | TYPE[1:0]     | 1d          |     | 1 - imager                                                                                                                                                                                                                                                                                                          |

| 11:6         | FORMAT[5:0]   | 13d         |     | 6 - VGA                                                                                                                                                                                                                                                                                                             |

| 15:12        | PROCESS[3:0]  | 0d          |     |                                                                                                                                                                                                                                                                                                                     |

|              |               |             |     |                                                                                                                                                                                                                                                                                                                     |

| Address      | Register Name | Reset Value | R/W | Clients / Description                                                                                                                                                                                                                                                                                               |

| 3            | CCP_CTRL      | 0x0000      |     | Central chip control register                                                                                                                                                                                                                                                                                       |

| Bits<br>0    | RUN           | 0           |     | When CCP_CTRL is updated and RUN transitions from '                                                                                                                                                                                                                                                                 |

| •            |               |             |     | to '1' (or remains at '1', see AUTO_START bit), any presering acquisition sequence is stopped (also see FAST_STOP bit) and a new acquisition is started in a potentially new record (see CTXT bit).<br>When CCP_CTRL is updated and RUN transitions to '0' the present acquisition is stopped and the sensor enters |

| ataSheet4U.o | com           |             |     | idle/sleep mode (see FAST_STOP).<br>When CCP_CTRL is updated and no new RUN conditionexists the present acquisition is stopped and the sensor<br>enters idle/sleep mode (see FAST_STOP).                                                                                                                            |

| 1            | СТХТ          | 0           |     | 0 - record A: execute commanded image acquisition usin<br>record A register settings                                                                                                                                                                                                                                |

|              |               |             |     | 1 - record B: execute commanded image acquisition usin<br>record B register settings                                                                                                                                                                                                                                |

| 2            | AUTO_CTXT     | 0           |     | 0 - when an acquisition in record B ends (also see registe SEQ_B_FRAMES), no auto record return to A is done.                                                                                                                                                                                                       |

|              |               |             |     | 1 - automatically return to record A, and start a new acquisition there, when record B has finished its image acquisition sequence (see SEQ_B_FRAMES). This allows to execute a fully automatic preview-snapshot-preview sequence.                                                                                  |

| 3            | AUTO_START    | 0           |     | Chooses between starting an acquisition when RUN is explicitly set, or whenever CCP_CTRL is written.                                                                                                                                                                                                                |

|              |               |             |     | <ul> <li>0 - RUN bit needs a transition from 0 to 1 to trigger an image acquisition</li> <li>1 - RUN bit is level sensitive: any writing to CCP_CTRL</li> </ul>                                                                                                                                                     |

| Address | Register Name | Reset Value | R/W | Clients / Description                                                                                                                                     |

|---------|---------------|-------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4       | FAST_STOP     | 0           |     | 0 - finish present frame completely when asked to stop or restart                                                                                         |

|         |               |             |     | 1 - accelerated stop procedure, aborting present frame<br>quickly (also see SEQ_CONFIG2.ABORT_DUMMY)                                                      |

| 5       | XE_FLASH_EN   | 0           |     | 0 - no Xenon flash                                                                                                                                        |

|         |               |             |     | 1 - fire Xenon flash when a new image acquisition starts<br>(and Xenon flash has been armed in the record of that new<br>acquisition, see 0:4 CCP_CONFIG) |

| 14:6    | -             |             |     |                                                                                                                                                           |

| 15      | RESET         | 0           |     | 0 - chip operational                                                                                                                                      |

|         |               |             |     | 1 - execute a soft reset, which resets this register too; the other chip parameter registers are not reset.                                               |

| Address               | Register Name    | Reset Value | R/W | Clients / Description                                                        |

|-----------------------|------------------|-------------|-----|------------------------------------------------------------------------------|

| 4                     | CCP_CONFIG       | 0x0000      | R/W | CCP configuration                                                            |

| Bits                  |                  |             |     |                                                                              |

| 3-2                   | B_CLK_DIV[1:0]   | "00"        |     | record B internal clock division:                                            |

|                       |                  |             |     | "00" - /1                                                                    |

|                       |                  |             |     | "01" - /2                                                                    |

|                       |                  |             |     | "10" - /4                                                                    |

|                       |                  |             |     | "11" - N/A                                                                   |

|                       |                  |             |     | set to /1 if record B is to be used for snapshot image capture (recommended) |

| 5-4                   | A_CLK_DIV[1:0]   | "00"        |     | record A internal clock division:                                            |

|                       |                  |             |     | "00" - /1                                                                    |

|                       |                  |             |     | "01" - /2                                                                    |

|                       |                  |             |     | "10" - /4                                                                    |

|                       |                  |             |     | "11" - N/A                                                                   |

|                       |                  |             |     | set to /2 or /4 if record A is to be used for video preview (recommended)    |

| a <b>7:a6</b> heet4U. | DLE_CLK_DIV[1:0] | "00"        |     | idle mode internal clock division:                                           |

|                       |                  |             |     | "00" - /1                                                                    |

|                       |                  |             |     | "01" - /2                                                                    |

|                       |                  |             |     | "10" - /4                                                                    |

|                       |                  |             |     | "11" - N/A                                                                   |

|                       |                  |             |     | set to /4 for lowest power consumption when idling (recom-<br>mended)        |

| 8                     | IDLE_SEQ_SLEEP   | 0           |     | 0 - do not assert SEQ_SLEEP when idling                                      |

|                       |                  |             |     | 1 - assert SEQ_SLEEP for minimal analog power when<br>idling                 |

| 9                     | B_ARM_XE         | 0           |     | record B arm Xenon flash (see 0: 3 CCP_CTRL for firing the flash)            |

| 10                    | A_ARM_XE         | 0           |     | record A arm Xenon flash                                                     |

| Address    | Register Name | Reset Value | R/W | Clients / Description                                                                                                                 |

|------------|---------------|-------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|

| 5          | CCP_GLOBAL    | 0x0000      | R/W | settings for CCP, SEQ, ISP                                                                                                            |

| Bits       |               |             |     |                                                                                                                                       |

| 0          | LED_FLASH_EN  | 0           |     | SEQ                                                                                                                                   |

|            |               |             |     | 0 - LED flash off (also see 0:39 SEQ_FLASH2 for automat-<br>ed flash turn-off)                                                        |

|            |               |             |     | 1 - LED flash on; the switching of the FLASH strobe is not synchronized to the frame capture.                                         |

| 1          | -             | 0           |     |                                                                                                                                       |

| 2          | A_BINNING     | 0           |     | SEQ                                                                                                                                   |

|            |               |             |     | record A horizontal pixel binning                                                                                                     |

|            |               |             |     | 0 - binning off (snapshot mode)                                                                                                       |

|            |               |             |     | 1 - binning on (to be combined with subsampling)                                                                                      |

| 3          | B_BINNING     | 0           |     | SEQ                                                                                                                                   |

| -          | _             | -           |     | record B horizontal pixel binning                                                                                                     |

|            |               |             |     | 0 - binning off                                                                                                                       |

|            |               |             |     | 1 - binning on (to be combined with subsampling)                                                                                      |

| 5:4        | A_SUB[1:0]    | "00"        |     | SEQ, ISP, CCP<br>record A subsampling in X and Y                                                                                      |

|            |               |             |     | 0 - 1:1:1:1:                                                                                                                          |

|            |               |             |     | 1 - 1:1:0:0:1:1:0:0:                                                                                                                  |

|            |               |             |     | 2 - 1:1:0:0:0:0:0:0:1:1:0:0:                                                                                                          |

|            |               |             |     | 3 - N/A                                                                                                                               |

|            |               |             |     | use subsampling when record A is used for video preview                                                                               |

|            |               |             |     | (recommended)                                                                                                                         |

| 7:6        | B_SUB[1:0]    | "00"        |     | SEQ, ISP, CCP<br>record B subsampling in X and Y                                                                                      |

|            |               |             |     | 0 - 1:1:1:1:                                                                                                                          |

|            |               |             |     | 1 - 1:1:0:0:1:1:0:0:                                                                                                                  |

|            |               |             |     | 2 - 1:1:0:0:0:0:0:0:1:1:0:0:                                                                                                          |

| ataSheet4U | com           |             |     | 3 - N/A                                                                                                                               |

|            |               |             |     | do not use subsampling when record B is used for snap-<br>shot (recommended)                                                          |

| 8          | FAST_RESET    | 0           |     | SEQ                                                                                                                                   |

|            |               |             |     | 0 - the frame reset cycle at the start of a Xe flashed acqui-<br>sition is at normal frame rate (slow)                                |

|            |               |             |     | 1 - the frame reset cycle at the start of a Xe flashed acqui-<br>sition is at accelerated frame rate (fast) to reduce shutter<br>lag. |

| 10         | SEQ_GAIN_SYNC | 0           |     | SEQ                                                                                                                                   |

|            |               |             |     | 0 - analog gain updates immediately take effect (for test/de-<br>bug only)                                                            |

|            |               |             |     | 1 - gain updates are post-synced to frames to bring them<br>in line with exposure time updates                                        |

| Address | Register Name | Reset Value | R/W | Clients / Description      |  |

|---------|---------------|-------------|-----|----------------------------|--|

| 6       | CCP_STAT      | 0x0000      | R/- | CCP status and diagnostics |  |

| Bits    |               |             | 1   |                            |  |

| 0       | STAT_RUN      | 0           |     | present running status     |  |

|         |               |             |     | 0 - idle or halting        |  |

|         |               |             |     | 1 - running                |  |

| Address | Register Name | Reset Value | R/W | Clients / Description  |

|---------|---------------|-------------|-----|------------------------|

| 1       | STAT_CTXT     | 0           |     | present record         |

|         |               |             |     | 0 - record A           |

|         |               |             |     | 1 - record B           |

| 3:2     | STAT_DIV[1:0] | "00"        |     | present clock division |

|         |               |             |     | 0 - /1                 |

|         |               |             |     | 1 - /2                 |

|         |               |             |     | 2 - /4                 |

|         |               |             |     | 3 - not used           |

| 4       | STAT_SLEEP    | 0           |     | Sleep mode             |

| 15:5    | -             | 0           |     |                        |

| Address                 | Register Name   | Reset Value | R/W | Clients / Description                                                                      |

|-------------------------|-----------------|-------------|-----|--------------------------------------------------------------------------------------------|

| 16                      | CONFIG2         | 0x5F9C      | R/W | sets bias (power) of the ADC                                                               |

|                         |                 |             |     | recommended value for record A preview, record B snap shot, and low-power idling is 0x5F9B |

| Bits                    |                 |             |     |                                                                                            |

| 0                       | A_ADC_FPB_n     | '0'         |     | record A ADC bias                                                                          |

|                         |                 |             |     | value for preview: '1'                                                                     |

|                         |                 |             |     | value for snapshot: '0'                                                                    |

| 4:1                     | A_ADC_SB_n[3:0] | "1110"      |     | record A ADC bias                                                                          |

|                         |                 |             |     | value for preview: "1101"                                                                  |

|                         |                 |             |     | value for snapshot: "1110"                                                                 |

| 5                       | B_ADC_FPB_n     | '0'         |     | record B ADC bias                                                                          |

|                         |                 |             |     | value for preview: '1'                                                                     |

|                         |                 |             |     | value for snapshot: '0'                                                                    |

| 9:6                     | B_ADC_SB_n[3:0] | "1110"      |     | record B ADC bias                                                                          |

|                         |                 |             |     | value for preview: "1101"                                                                  |

|                         |                 |             |     | value for snapshot: "1110"                                                                 |

| <b>10</b><br>ataSheet4U | CONFIG2A        | '1'         |     | Fixed value                                                                                |

| 14:11                   | CONFIG2B        | "1011"      |     | Fixed value                                                                                |

| 15                      | CONFIG2C        | '0'         |     | Fixed value                                                                                |

| Address | Register Name   | Reset Value | R/W | Clients / Description                                                                                                                        |

|---------|-----------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------|

| 17      | CONFIG3         | 0x0077      | R/W | sets bias (power) of the column amplifiers<br>recommended value for record A preview, record B snap-<br>shot, and low-power idling is 0x0073 |

| Bits    |                 |             |     |                                                                                                                                              |

| 3:0     | A_COL_BIAS[3:0] | "0111"      |     | record A COL bias                                                                                                                            |

|         |                 |             |     | snapshot value: "0111"                                                                                                                       |

|         |                 |             |     | preview value: "0011"                                                                                                                        |

| 7:4     | B_COL_BIAS[3:0] | "0111"      |     | record B COL bias                                                                                                                            |

|         |                 |             |     | snapshot value: "0111"                                                                                                                       |

|         |                 |             |     | preview value: "0011"                                                                                                                        |

| 11:8    | CONFIG3A        | "0000"      |     | Fixed value                                                                                                                                  |

| Address | Register Name   | Reset Value | R/W | Clients / Description                                                                          |

|---------|-----------------|-------------|-----|------------------------------------------------------------------------------------------------|

| 18      | CONFIG4         | 0x0077      | R/W | sets bias (power) of the PGA                                                                   |

|         |                 |             |     | recommended value for record A preview, record B snap-<br>shot, and low-power idling is 0x0073 |

| Bits    |                 |             |     |                                                                                                |

| 3:0     | A_PGA_BIAS[3:0] | "0111"      |     | record A PGA bias                                                                              |

|         |                 |             |     | snapshot value: "0111"                                                                         |

|         |                 |             |     | preview value: "0011"                                                                          |

| 7:4     | B_PGA_BIAS[3:0] | "0111"      |     | record B PGA bias                                                                              |

|         |                 |             |     | snapshot value: "0111"                                                                         |

|         |                 |             |     | preview value: "0011"                                                                          |

| 11:8    | CONFIG4A        | "0000"      |     | Fixed value                                                                                    |

| Address | Register Name   | Reset Value | R/W | Clients / Description                                                                          |