# USER'S MANUAL

# NEC

# $\mu$ PD17120 SUBSERIES

# **4-BIT SINGLE-CHIP MICROCONTROLLER**

μ**PD17120** μ**PD17121** μ**PD17132** μ**PD17133** μ**PD17P132** μ**PD17P133**

# NOTES FOR CMOS DEVICES -

# **1** PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

#### Note:

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

# (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

#### Note:

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

#### **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

#### Note:

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

SIMPLEHOST is a trademark of NEC Corporation. MS-DOS<sup>TM</sup> and WINDOWS<sup>TM</sup> are trademarks of Microsoft Corporation. PC/AT and PC DOS are trademarks of IBM Corporation. The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or reexport of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

#### The information in this document is subject to change without notice.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document.

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customer must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

- Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

- Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

- Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices in "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact NEC Sales Representative in advance.

Anti-radioactive design is not implemented in this product.

# INTRODUCTION

| Targeted Reader |                                                                                                                               | the user engineers who understand functions of the ign their application systems using the $\mu$ PD17120 sub-                                                                                                                                                                                                                                              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Purpose         | The purpose of this manual is the $\mu$ PD17120 subseries.                                                                    | for the user to understand the hardware functions of                                                                                                                                                                                                                                                                                                       |

| Use             | The manual assumes that the circuits, microcontrollers.                                                                       | e reader has a general knowledge of electricity, logic                                                                                                                                                                                                                                                                                                     |

|                 | <ul> <li>To understand the functi</li> <li>→ Read the manual from</li> </ul>                                                  | ions of the $\mu$ PD17120 subseries in a general way; CHAPTER 1.                                                                                                                                                                                                                                                                                           |

|                 | <ul> <li>To look up instruction fu<br/>an instruction;</li> <li>→ Use APPENDIX D INS</li> </ul>                               | nctions in detail when you know the mnemonic of<br>TRUCTION LIST.                                                                                                                                                                                                                                                                                          |

|                 | outlines of the function; $\rightarrow$ Refer to <b>18.3 LIST OF</b>                                                          | n when you do not know its mnemonic but know<br>THE INSTRUCTION SET for search for the mnemonic<br>see 18.5 INSTRUCTIONS for the function.                                                                                                                                                                                                                 |

|                 | <ul> <li>To look up electrical cha</li> <li>→ Refer to DATA SHEET.</li> </ul>                                                 | racteristics of the $\mu$ PD17120 subseries;                                                                                                                                                                                                                                                                                                               |

| Legend          | Data representation weight                                                                                                    | : High-order and low-order digits are indicated from                                                                                                                                                                                                                                                                                                       |

|                 | Active low representation<br>Address of memory map<br><b>Note</b><br><b>Caution</b><br><b>Remark</b><br>Number representation | <ul> <li>left to right.</li> <li>: xxx (pin or signal name is overlined)</li> <li>: Top: low, Bottom: high</li> <li>: Explanation of <b>Note</b> in the text</li> <li>: Caution to which you should pay attention</li> <li>: Supplementary explanation to the text</li> <li>: Binary number xxxx or xxxxB</li> <li>Decimal number xxxx or xxxxD</li> </ul> |

**Relevant Documents** The following documents are provided for the  $\mu$ PD17120 subseries.

The numbers listed in the table are the document numbers. Some related documents are preliminary versions. This document, however, is not indicated as "Preliminary".

| Part Number<br>Document Name                         | μPD17120                                                            | μPD17121               | μPD17132             | μPD17133             | μPD17P132            | μPD17P133            |  |

|------------------------------------------------------|---------------------------------------------------------------------|------------------------|----------------------|----------------------|----------------------|----------------------|--|

| Data sheet                                           | IC-8407<br>[IC-2972]                                                | IC-8399<br>[IC-2976]   | IC-8412<br>[IC-2973] | IC-8411<br>[IC-2974] | ID-8419<br>[ID-2971] | ID-8426<br>[ID-2983] |  |

| User's manual                                        |                                                                     | This manual [IEU-1367] |                      |                      |                      |                      |  |

| IE-17K<br>CLICE Ver.1.6<br>User's manual             |                                                                     | EEU-929 [EEU-1467]     |                      |                      |                      |                      |  |

| IE-17K-ET<br>CLICE-ET Ver.1.6<br>User's manual       |                                                                     | EE                     | U-931 [EEU-14        | 66]                  |                      |                      |  |

| SE board<br>User's manual                            |                                                                     | EE                     | U-847 [EEU-14        | 12]                  |                      |                      |  |

| SIMPLEHOST <sup>TM</sup><br>User's manual            | EEU-723 [EEU-1336] (Introduction)<br>EEU-724 [EEU-1337] (Reference) |                        |                      |                      |                      |                      |  |

| AS17K (Ver.1.11)<br>User's manual EEU-603 [EEU-1287] |                                                                     |                        |                      |                      |                      |                      |  |

| Device file<br>User's manual                         |                                                                     | EE                     | U-907 [EEU-14        | 64]                  |                      |                      |  |

**Remark** The numbers inside [ ] indicate English document number.

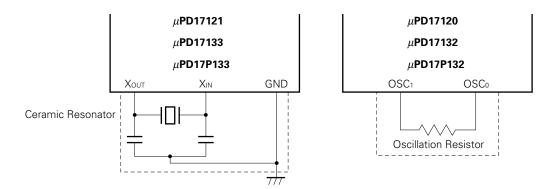

The  $\mu$ PD17120 subseries has different pin names and signal names depending on the system clock type, as shown in the table below.

| System Clock           | RC Oscillation   | Ceramic Oscillation |

|------------------------|------------------|---------------------|

|                        | μPD17120         | (µPD17121)          |

|                        | μPD17132         | μPD17133            |

| Pin/Signal Names       | (µPD17P132)      | _μPD17P133_         |

| System Clock           | OSC1             | Xin                 |

| Oscillation Pin        | OSC <sub>0</sub> | Хоит                |

| System Clock Frequency | fcc              | fx                  |

Unless otherwise specified, this manual uses  $X_{IN}$ ,  $X_{OUT}$ , and fx for descriptions. When using the  $\mu$ PD17120, 17132, and 17P132, please change the readings to OSC<sub>1</sub>, OSC<sub>0</sub> and fcc.

# **TABLE OF CONTENTS**

| СНАРТЕ | R 1 GI  | ENERAL                                                                     | 1  |

|--------|---------|----------------------------------------------------------------------------|----|

| 1.1    | FUNC    | TION LIST                                                                  | 2  |

| 1.2    |         | RING INFORMATION                                                           | 3  |

| 1.3    | BLOC    | K DIAGRAM                                                                  | 4  |

| 1.4    |         | ONFIGURATION (Top View)                                                    | 6  |

|        | _       |                                                                            |    |

| CHAPTE | R 2 PI  | N FUNCTIONS                                                                | 9  |

| 2.1    | PIN F   | UNCTIONS                                                                   | 9  |

|        | 2.1.1   | Pins in Normal Operation Mode                                              | 9  |

|        | 2.1.2   | Pins in Program Memory Write/Verify Mode $\mu$ PD17P132, 17P133 only       | 11 |

| 2.2    | PIN IN  | NPUT/OUTPUT CIRCUIT                                                        | 12 |

| 2.3    | HAND    | DLING UNUSED PINS                                                          | 17 |

| 2.4    | CAUT    | IONS ON USE OF THE RESET AND INT PINS                                      |    |

|        | (in No  | ormal Operation Mode only)                                                 | 18 |

| СНАРТЕ | ER 3 PF | ROGRAM COUNTER (PC)                                                        | 19 |

| 3.1    | PROG    | RAM COUNTER CONFIGURATION                                                  | 19 |

| 3.2    |         | RAM COUNTER OPERATION                                                      | 19 |

|        | 3.2.1   | Program Counter at Reset                                                   | 20 |

|        | 3.2.2   | Program Counter during Execution of the Branch Instruction (BR)            | 20 |

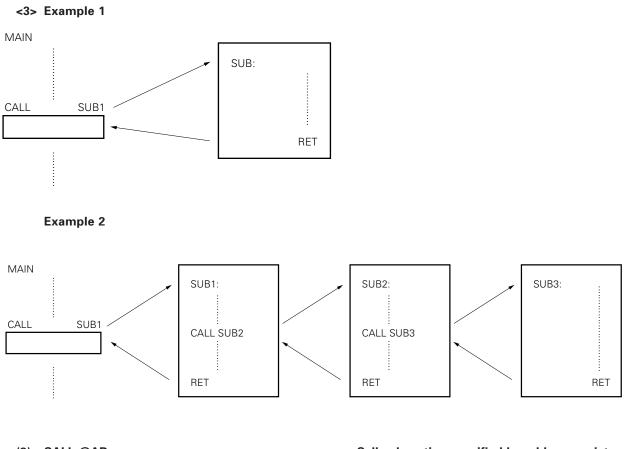

|        | 3.2.3   | Program Counter during Execution of Subroutine Calls (CALL)                | 21 |

|        | 3.2.4   | Program Counter during Execution of Return Instructions (RET, RETSK, RETI) | 22 |

|        | 3.2.5   | Program Counter during Table Reference (MOVT)                              | 22 |

|        | 3.2.6   | Program Counter during Execution of Skip Instructions                      |    |

|        | 0.2.10  | (SKE, SKGE, SKLT, SKNE, SKT SKF)                                           | 22 |

|        | 3.2.7   | Program Counter When an Interrupt Is Received                              | 22 |

| 3.3    |         | IONS ON PROGRAM COUNTER OPERATION                                          | 22 |

|        |         |                                                                            |    |

| CHAPTE | R 4 PF  | ROGRAM MEMORY (ROM)                                                        | 23 |

| 4.1    |         | RAM MEMORY CONFIGURATION                                                   | 23 |

| 4.2    | PROG    | RAM MEMORY USAGE                                                           | 24 |

|        | 4.2.1   | Flow of the Program                                                        | 24 |

|        | 4.2.2   | Table Reference                                                            | 27 |

| СНАРТЕ | R 5 D/  | ATA MEMORY (RAM)                                                           | 31 |

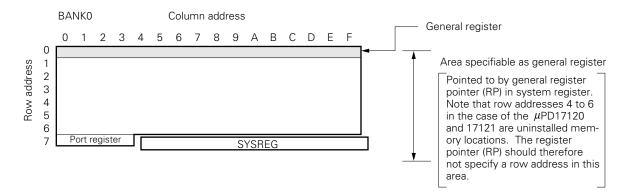

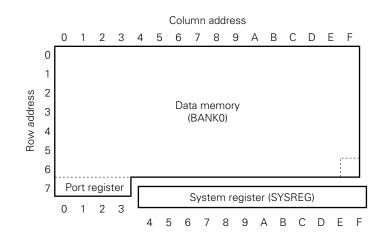

| 5.1    | DATA    | MEMORY CONFIGURATION                                                       | 31 |

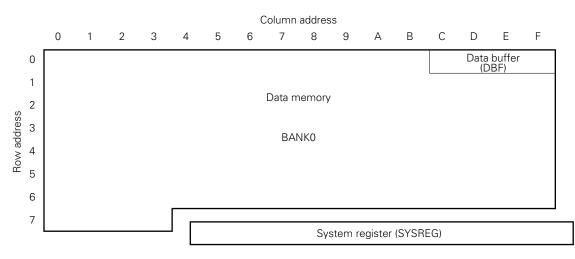

|        | 5.1.1   | System Register (SYSREG)                                                   | 32 |

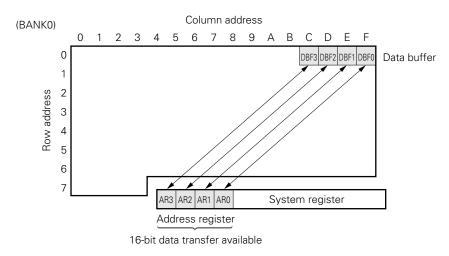

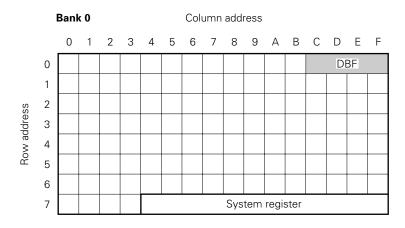

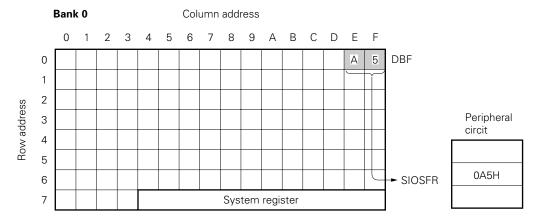

|        | 5.1.2   | Data Buffer (DBF)                                                          | 32 |

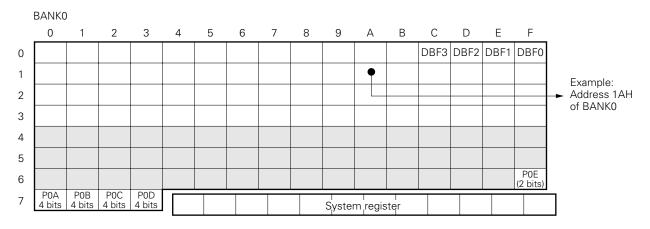

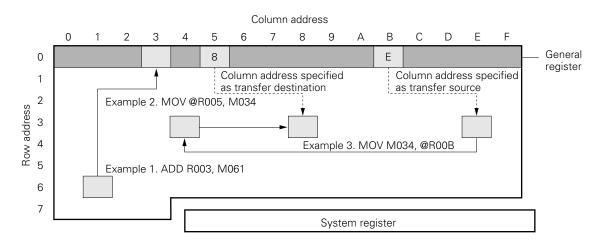

|        | 5.1.3   | General Register (GR)                                                      | 32 |

|        | 5.1.4   | Port Registers                                                             | 33 |

|        | 5.1.5          | General Data Memory                                                                                | . 33 |

|--------|----------------|----------------------------------------------------------------------------------------------------|------|

|        | 5.1.6          | Uninstalled Data Memory                                                                            | . 33 |

|        |                |                                                                                                    |      |

| СНАРТЕ | ER6 S          | ТАСК                                                                                               | 35   |

|        |                |                                                                                                    |      |

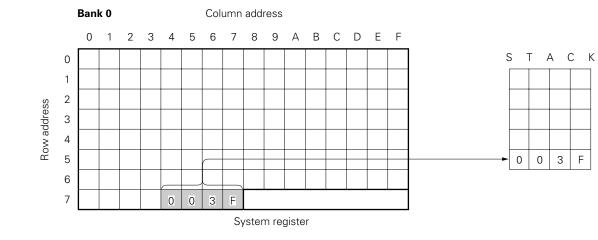

| 6.1    | STAC           | K CONFIGURATION                                                                                    | . 35 |

| 6.2    | FUNC           | TIONS OF THE STACK                                                                                 | . 35 |

| 6.3    |                | RESS STACK REGISTER                                                                                |      |

| 6.4    |                | RUPT STACK REGISTER                                                                                |      |

| 6.5    | STAC           | K POINTER (SP) AND INTERRUPT STACK REGISTER                                                        | 36   |

| 6.6    |                | K OPERATION DURING SUBROUTINES, TABLE REFERENCES,                                                  |      |

|        | AND            | INTERRUPTS                                                                                         | . 37 |

|        | 6.6.1          | Stack Operation during Subroutine Calls (CALL) and Returns (RET, RETSK)                            | . 37 |

|        | 6.6.2          | Stack Operation during Table Reference (MOVT DBF, @AR)                                             |      |

|        | 6.6.3          | Executing RETI Instruction                                                                         |      |

| 6.7    | STAC           | K NESTING LEVELS AND THE PUSH AND POP INSTRUCTIONS                                                 | . 39 |

|        |                |                                                                                                    |      |

| СНАРТЕ | ER 7 S         | YSTEM REGISTER (SYSREG)                                                                            | 41   |

|        | <u></u>        |                                                                                                    |      |

| 7.1    |                |                                                                                                    |      |

| 7.2    |                | RESS REGISTER (AR)                                                                                 |      |

|        | 7.2.1          | Address Register Configuration                                                                     |      |

| 7.0    | 7.2.2          | Address Register Functions                                                                         |      |

| 7.3    |                | OOW REGISTER (WR)                                                                                  |      |

|        | 7.3.1          | Window Register Configuration                                                                      |      |

| 7.4    | 7.3.2          | Window Register Functions                                                                          |      |

| 7.4    |                | ( REGISTER (BANK)                                                                                  | 46   |

| 7.5    |                | X REGISTER (IX) AND DATA MEMORY ROW ADDRESS POINTER                                                | 47   |

|        |                | hory Pointer: MP)                                                                                  |      |

|        | 7.5.1          | Index Register (IX)<br>Data Memory Row Address Pointer (Memory Pointer: MP)                        |      |

|        | 7.5.2<br>7.5.3 | MPE=0 and IXE=0 (No Data Memory Modification)                                                      |      |

|        |                | MPE=0 and IXE=0 (No Data Memory Modification)<br>MPE=1 and IXE=0 (Diagonal Indirect Data Transfer) |      |

|        | 7.5.4<br>7.5.5 | MPE=1 and IXE=0 (Diagonal Indirect Data Transfer)                                                  |      |

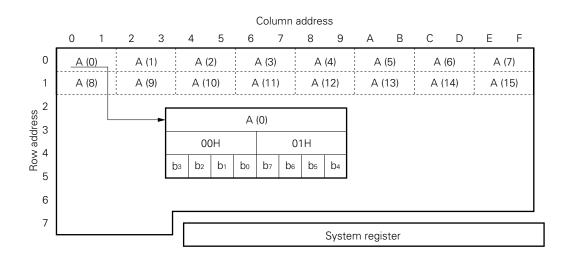

| 7.6    |                | RAL REGISTER POINTER (RP)                                                                          |      |

| 7.0    | 7.6.1          | General Register Pointer Configuration                                                             |      |

|        | 7.6.2          | Functions of the General Register Pointer                                                          |      |

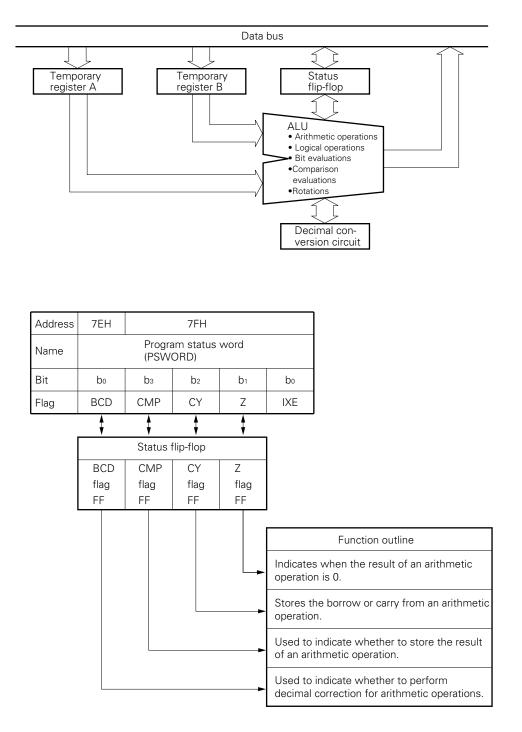

| 7.7    |                | SRAM STATUS WORD (PSWORD)                                                                          |      |

|        | 7.7.1          | Program Status Word Configuration                                                                  |      |

|        | 7.7.2          | Functions of the Program Status Word                                                               |      |

|        | 7.7.3          | Index Enable Flag (IXE)                                                                            |      |

|        | 7.7.4          | Zero Flag (Z) and Compare Flag (CMP)                                                               |      |

|        | 7.7.5          | Carry Flag (CY)                                                                                    |      |

|        | 7.7.6          | Binary-Coded Decimal Flag (BCD)                                                                    |      |

|        | 7.7.7          | Caution on Use of Arithmetic Operations on the Program Status Word                                 |      |

| 7.8    |                | TIONS ON USE OF THE SYSTEM REGISTER                                                                |      |

|        | 7.8.1          | Reserved Words for Use with the System Register                                                    |      |

|        | 7.8.2          | Handling of System Register Addresses Fixed at 0                                                   |      |

|        |                |                                                                                                    |      |

| CHAPTE | R 8 GENERAL REGISTER (GR)                                                           | 69 |

|--------|-------------------------------------------------------------------------------------|----|

| 8.1    | GENERAL REGISTER CONFIGURATION                                                      | 69 |

| 8.2    | FUNCTIONS OF THE GENERAL REGISTER                                                   | 69 |

| CHAPTE | R 9 REGISTER FILE (RF)                                                              | 71 |

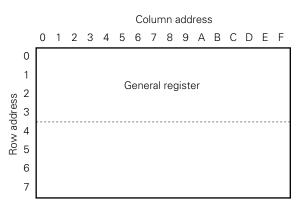

| 9.1    | REGISTER FILE CONFIGURATION                                                         | 71 |

| 0.1    | 9.1.1 Configuration of the Register File                                            | 71 |

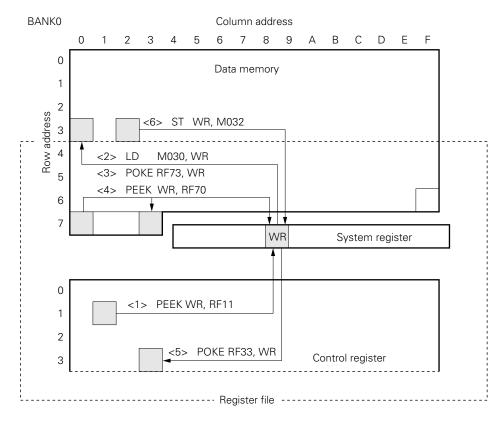

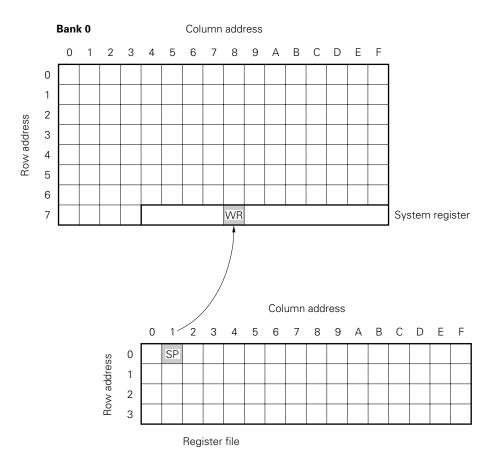

|        | 9.1.2 Relationship between the Register File and Data Memory                        | 71 |

| 9.2    | FUNCTIONS OF THE REGISTER FILE                                                      | 72 |

| •      | 9.2.1 Functions of the Register File                                                | 72 |

|        | 9.2.2 Control Register Functions                                                    | 72 |

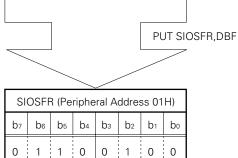

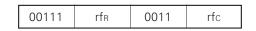

|        | 9.2.3 Register File Manipulation Instructions                                       | 73 |

| 9.3    |                                                                                     | 75 |

| 9.4    | CAUTIONS ON USING THE REGISTER FILE                                                 | 75 |

|        | 9.4.1 Concerning Operation of the Control Register (Read-Only and Unused Registers) | 75 |

|        | 9.4.2 Register File Symbol Definitions and Reserved Words                           | 76 |

|        |                                                                                     |    |

| CHAPTE | R 10 DATA BUFFER (DBF)                                                              | 79 |

| 10.1   | DATA BUFFER CONFIGURATION                                                           | 79 |

| 10.2   | FUNCTIONS OF THE DATA BUFFER                                                        | 80 |

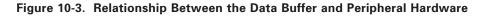

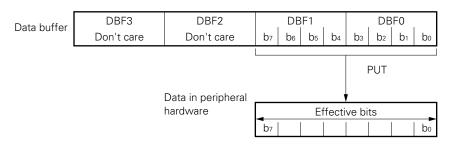

|        | 10.2.1 Data Buffer and Peripheral Hardware                                          | 81 |

|        | 10.2.2 Data Transfer with Peripheral Hardware                                       | 82 |

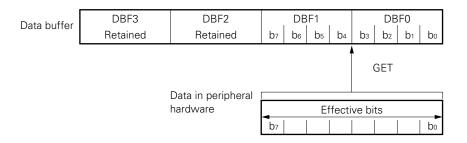

|        | 10.2.3 Table Reference                                                              | 83 |

| СНАРТЕ | R 11 ARITHMETIC AND LOGIC UNIT                                                      | 85 |

|        |                                                                                     | 00 |

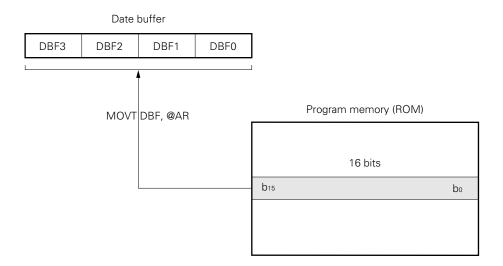

|        | ALU BLOCK CONFIGURATION                                                             | 85 |

| 11.2   | FUNCTIONS OF THE ALU BLOCK                                                          | 85 |

|        | 11.2.1 Functions of the ALU                                                         | 85 |

|        | 11.2.2 Functions of Temporary Registers A and B                                     | 90 |

|        | 11.2.3 Functions of the Status Flip-flop                                            | 90 |

|        | 11.2.4 Performing Operations in 4-Bit Binary                                        | 91 |

|        | 11.2.5 Performing Operations in BCD                                                 | 91 |

|        | 11.2.6 Performing Operations in the ALU Block                                       | 93 |

| 11.3   | ARITHMETIC OPERATIONS (ADDITION AND SUBTRACTION IN 4-BIT                            |    |

|        | BINARY AND BCD)                                                                     | 94 |

|        | 11.3.1 Addition and Subtraction When CMP=0 and BCD=0                                | 95 |

|        | 11.3.2 Addition and Subtraction When CMP=1 and BCD=0                                | 95 |

|        | 11.3.3 Addition and Subtraction When CMP=0 and BCD=1                                | 95 |

|        | 11.3.4 Addition and Subtraction When CMP=1 and BCD=1                                | 96 |

|        | 11.3.5 Cautions on Use of Arithmetic Operations                                     | 96 |

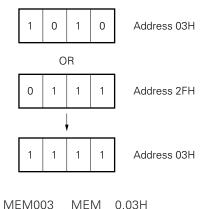

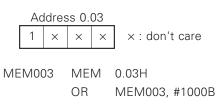

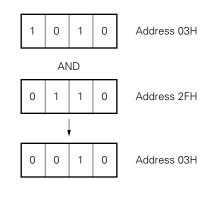

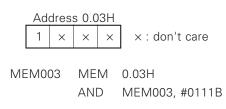

|        | LOGICAL OPERATIONS                                                                  | 96 |

| 11.5   | BIT JUDGEMENT                                                                       | 97 |

|        | 11.5.1 TRUE (1) Bit Judgement                                                       | 98 |

|        | 11.5.2 FALSE (0) Bit Judgement                                                      | 98 |

| 11.6   | COMPARISON JUDGEMENT                                                                                                                                                                          | 99         |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|        | 11.6.1 "Equal to" Judgement                                                                                                                                                                   | 100        |

|        | 11.6.2 "Not Equal to" Judgement                                                                                                                                                               | 100        |

|        | 11.6.3 "Greater Than or Equal to" Judgement                                                                                                                                                   | 101        |

|        | 11.6.4 "Less Than" Judgement                                                                                                                                                                  | 101        |

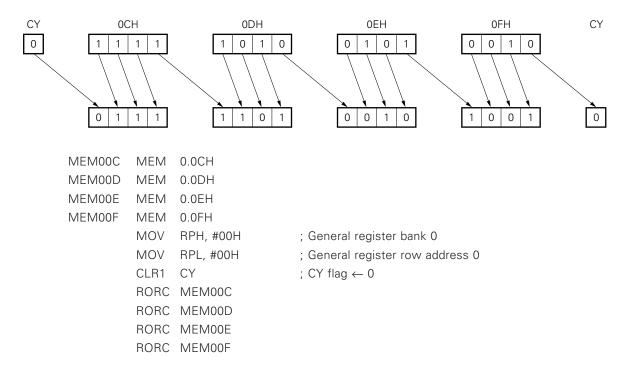

| 11.7   | ROTATIONS                                                                                                                                                                                     | 102        |

|        | 11.7.1 Rotation to the Right                                                                                                                                                                  | 102        |

|        | 11.7.2 Rotation to the Left                                                                                                                                                                   | 103        |

| CUADTE | R 12 PORTS                                                                                                                                                                                    | 105        |

| CHAFTE |                                                                                                                                                                                               | 105        |

| 12.1   | PORT 0A (P0A0, P0A1, P0A2, P0A3)                                                                                                                                                              | 105        |

|        | PORT 0B (P0B0, P0B1, P0B2, P0B3)                                                                                                                                                              | 106        |

|        | PORT 0C (P0C <sub>0</sub> , P0C <sub>1</sub> , P0C <sub>2</sub> , P0C <sub>3</sub> ) in the case of the $\mu$ PD17120 and 17121                                                               | 107        |

| 12.4   | PORT 0C (P0C <sub>0</sub> /Cin <sub>0</sub> , P0C <sub>1</sub> /Cin <sub>1</sub> , P0C <sub>2</sub> /Cin <sub>2</sub> , P0C <sub>3</sub> /Cin <sub>3</sub> ) in the case of the $\mu$ PD17132 |            |

|        | 17133, 17P132, and 17P133                                                                                                                                                                     | 108        |

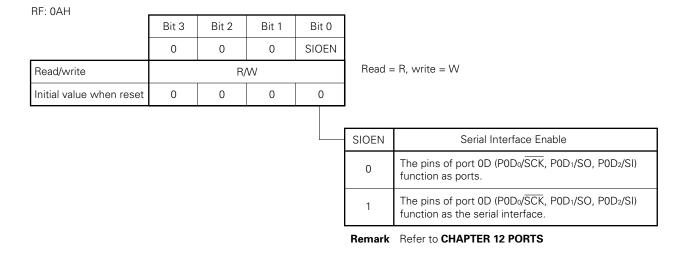

|        | PORT 0D (P0D0/SCK, P0D1/SO, P0D2/SI, P0D3/TMOUT)                                                                                                                                              | 109        |

| 12.6   | PORT 0E (P0E0, P0E1/V <sub>ref</sub> ) V <sub>ref</sub> , μPD17132, 17133, 17P132, and                                                                                                        |            |

|        | 17P133 only                                                                                                                                                                                   | 111        |

| 40.7   | 12.6.1 Cautions when Operating Port Registers                                                                                                                                                 | 112        |

| 12.7   | PORT CONTROL REGISTER                                                                                                                                                                         | 113        |

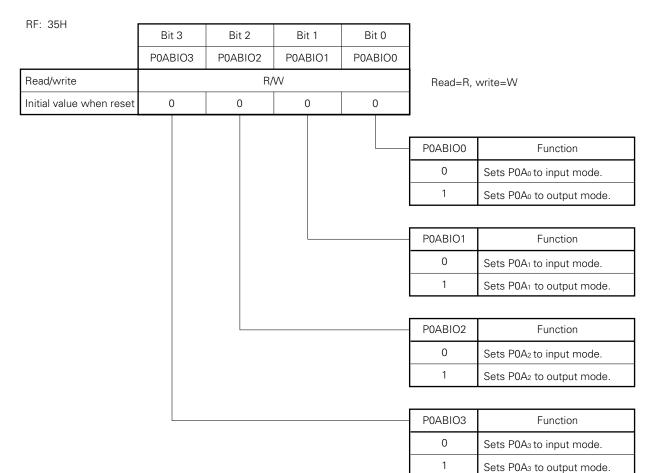

|        | <ul><li>12.7.1 Input/Output Switching by Group I/O</li><li>12.7.2 Input/Output Switching by Bit I/O</li></ul>                                                                                 | 113<br>114 |

|        |                                                                                                                                                                                               | 114        |

| CHAPTE | R 13 PERIPHERAL HARDWARE                                                                                                                                                                      | 117        |

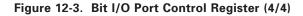

| 13 1   | 8-BIT TIMER COUNTER (TM)                                                                                                                                                                      | 117        |

| 10.1   | 13.1.1 8-Bit Timer Counter Configuration                                                                                                                                                      | 117        |

|        | 13.1.2 8-bit Timer Counter Control Register                                                                                                                                                   | 119        |

|        | 13.1.3 Operation of 8-bit Timer Counters                                                                                                                                                      | 120        |

|        | 13.1.4 Selecting Count Pulse                                                                                                                                                                  | 120        |

|        | 13.1.5 Setting a Count Value in Modulo Register and Calculation Method                                                                                                                        | 121        |

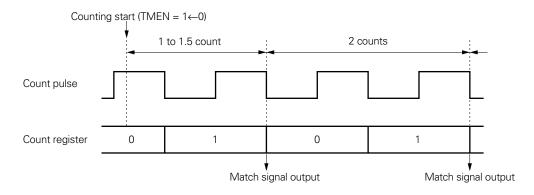

|        | 13.1.6 Margin of Error of Interval Time                                                                                                                                                       | 124        |

|        | 13.1.7 Reading Count Register Values                                                                                                                                                          | 126        |

|        | 13.1.8 Timer Output                                                                                                                                                                           | 129        |

|        | 13.1.9 Timer Resolution and Maximum Setting Time                                                                                                                                              | 130        |

| 13.2   | COMPARATOR (mPD17132, 17133, 17P132, AND 17P133 ONLY)                                                                                                                                         | 131        |

|        | 13.2.1 Configuration of Comparator                                                                                                                                                            | 131        |

|        | 13.2.2 Functions of Comparator                                                                                                                                                                | 132        |

| 13.3   | SERIAL INTERFACE (SIO)                                                                                                                                                                        | 135        |

|        | 13.3.1 Functions of the Serial Interface                                                                                                                                                      | 135        |

|        | 13.3.2 3-wire Serial Interface Operation Modes                                                                                                                                                | 137        |

|        | 13.3.3 Setting Values in the Shift Register                                                                                                                                                   | 141        |

|        | 13.3.4 Reading Values from the Shift Register                                                                                                                                                 | 142        |

|        | 13.3.5 Program Example of Serial Interface                                                                                                                                                    | 143        |

| CHAPTE | R 14 II | NTERRUPT FUNCTIONS                                                               | 145        |

|--------|---------|----------------------------------------------------------------------------------|------------|

| 14.1   | INTER   | RUPT SOURCES AND VECTOR ADDRESS                                                  | 146        |

| 14.2   | HARD    | WARE COMPONENTS OF THE INTERRUPT CONTROL CIRCUIT                                 | 147        |

|        | 14.2.1  | Interrupt Request Flag (IRQxxx) and the Interrupt Enable Flag (IPxxx)            | 147        |

|        | 14.2.2  | EI/DI Instruction                                                                | 147        |

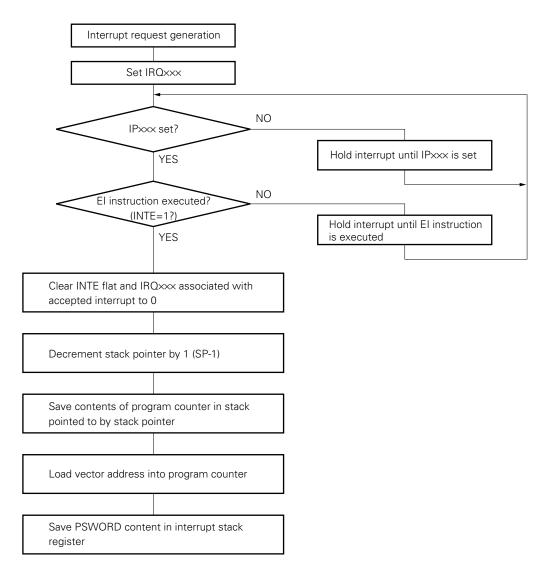

| 14.3   |         | RUPT SEQUENCE                                                                    | 152        |

|        | 14.3.1  | Acceptance of Interrupts                                                         | 152        |

|        | 14.3.2  | Return from the Interrupt Routine                                                | 154        |

|        | 14.3.3  | Interrupt Acceptance Timing                                                      | 155        |

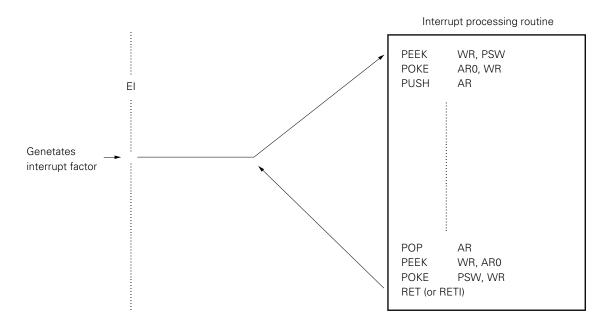

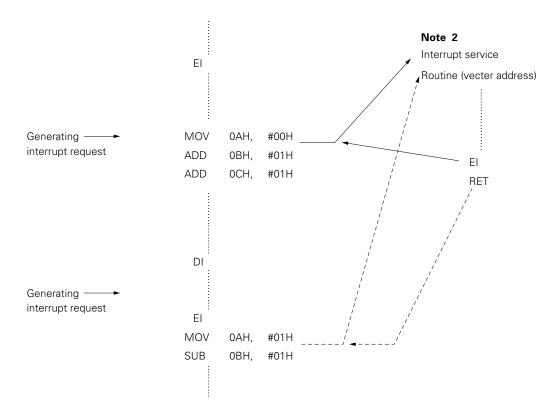

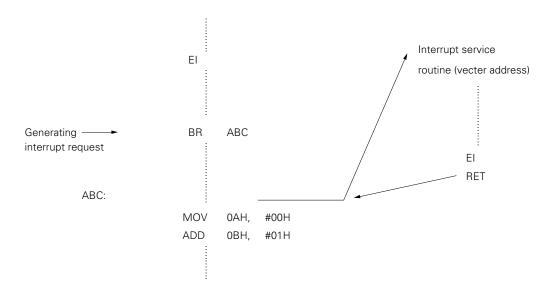

| 14.4   | PROG    | RAM EXAMPLE OF INTERRUPT                                                         | 158        |

| CHAPTE | R 15 S  | TANDBY FUNCTIONS                                                                 | 161        |

| 15.1   | OUTL    | INE OF STANDBY FUNCTION                                                          | 161        |

| 15.2   | HALT    | MODE                                                                             | 163        |

|        | 15.2.1  | HALT Mode Setting                                                                | 163        |

|        | 15.2.2  | Start Address after HALT Mode is Canceled                                        | 163        |

|        | 15.2.3  | HALT Setting Condition                                                           | 165        |

| 15.3   | STOP    | MODE                                                                             | 167        |

|        | 15.3.1  | STOP Mode Setting                                                                | 167        |

|        | 15.3.2  | Start Address after STOP Mode Cancellation                                       | 167        |

|        | 15.3.3  | STOP Setting Condition                                                           | 169        |

| СНАРТЕ | R 16 R  | ESET                                                                             | 171        |

| 16.1   | RESE    | FUNCTIONS                                                                        | 171        |

| 16.2   | RESE    | ITING                                                                            | 172        |

| 16.3   | POWE    | R-ON/POWER-DOWN RESET FUNCTION                                                   | 173        |

|        | 16.3.1  | Conditions Required to Enable the Power-On Reset Function                        | 173        |

|        | 16.3.2  | Description and Operation of the Power-On Reset Function                         | 174        |

|        | 16.3.3  | Condition Required for Use of the Power-Down Reset Function                      | 176        |

|        | 16.3.4  | Description and Operation of the Power-Down Reset Function                       | 176        |

| СНАРТЕ | R 17 O  | ONE-TIME PROM WRITING/VERIFYING                                                  | 179        |

| 17.1   |         | RENCES BETWEEN MASK ROM VERSION AND                                              | 470        |

| 47.0   |         |                                                                                  | 179        |

|        |         | ATING MODE IN PROGRAM MEMORY WRITING/VERIFYING<br>NG PROCEDURE OF PROGRAM MEMORY | 180        |

|        |         | ING PROCEDURE OF PROGRAM MEMORY                                                  | 181<br>182 |

| 17.4   | NEAD    |                                                                                  | 102        |

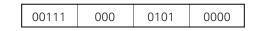

| CHAPTE | R 18 II | NSTRUCTION SET                                                                   | 185        |

| 18.1   | OVER    | VIEW OF THE INSTRUCTION SET                                                      | 185        |

| 18.2   | LEGE    | ND                                                                               | 186        |

| 18.3   | LIST C  | OF THE INSTRUCTION SET                                                           | 187        |

| 18.4   | ASSEI   | MBLER (AS17K) MACRO INSTRUCTIONS                                                 | 188        |

| 18.5   | INSTR   | UCTIONS                                                           | 189          |

|--------|---------|-------------------------------------------------------------------|--------------|

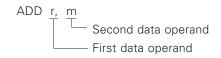

|        | 18.5.1  | Addition Instructions                                             | 189          |

|        | 18.5.2  | Subtraction Instructions                                          | 202          |

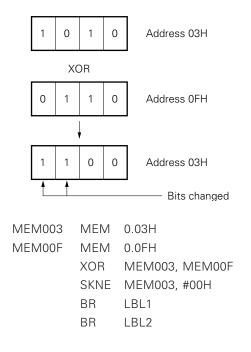

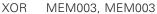

|        | 18.5.3  | Logical Operation Instructions                                    | 211          |

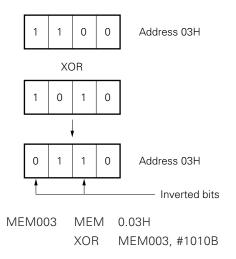

|        | 18.5.4  | Judgment Instruction                                              | 216          |

|        | 18.5.5  | Comparison Instructions                                           | 218          |

|        | 18.5.6  | Rotation Instructions                                             | 221          |

|        | 18.5.7  | Transfer Instructions                                             | 222          |

|        | 18.5.8  | Branch Instructions                                               | 239          |

|        | 18.5.9  | Subroutine Instructions                                           | 241          |

|        | 18.5.10 | Interrupt Instructions                                            | 247          |

|        | 18.5.11 | Other Instructions                                                | 249          |

| СНАРТЕ | R 19 A  | SSEMBLER RESERVED WORDS                                           | 251          |

| 19.1   | MASK    | OPTION PSEUDO INSTRUCTIONS                                        | 251          |

|        | 19.1.1  | OPTION and ENDOP Pseudo Instructions                              | 251          |

|        | 19.1.2  | Mask Option Definition Pseudo Instructions                        | 252          |

| 19.2   | RESER   | VED SYMBOLS                                                       | 254          |

|        | 19.2.1  | List of Reserved Symbols (µPD17120, 17121)                        | 254          |

|        | 19.2.2  | List of Reserved Symbols (µPD17132, 17133, 17P132, 17P133)        | 260          |

| APPEND |         | EVELOPMENT TOOLS                                                  | 267          |

| APPEND | IX B O  | RDERING MASK ROM                                                  | 269          |

|        |         |                                                                   |              |

| APPEND |         | AUTIONS TO TAKE IN SYSTEM CLOCK OSCILLATION CIRCUIT ONFIGURATIONS | 271          |

|        |         |                                                                   | <i>L</i> / I |

| APPEND | IX D IN | ISTRUCTION LIST                                                   | 273          |

| APPEND | IX E RE | EVISION HISTORY                                                   | 275          |

# LIST OF FIGURES (1/2)

| Figure No.   | Title                                                                           | Р |

|--------------|---------------------------------------------------------------------------------|---|

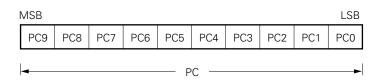

| 3-1          | Program Counter                                                                 |   |

| 3-2          | Value of the Program Counter after an Instruction Is Executed                   |   |

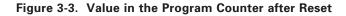

| 3-3          | Value in the Program Counter after Reset                                        |   |

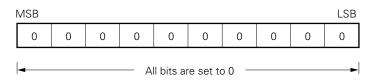

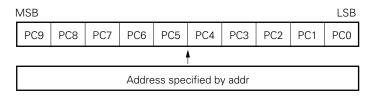

| 3-4          | Value in the Program Counter during Execution of a Direct Branch Instruction    |   |

| 3-5          | Value in the Program Counter during Execution of an Indirect Branch Instruction |   |

| 3-6          | Value in the Program Counter during Execution of a Direct Subroutine Call       |   |

| 3-0<br>3-7   | Value in the Program Counter during Execution of an Indirect Subroutine Call    |   |

| 3-8          | Value in the Program Counter during Execution of a Return Instruction           |   |

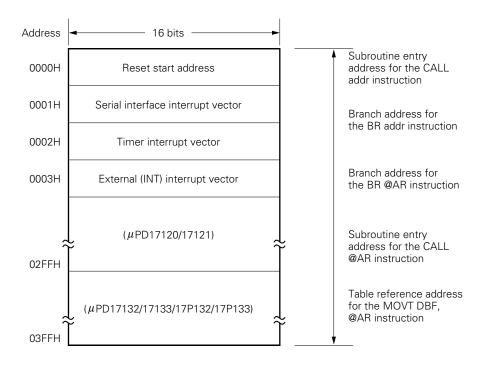

| 4-1          | Program Memory Map for the $\mu$ PD17120 Subseries                              |   |

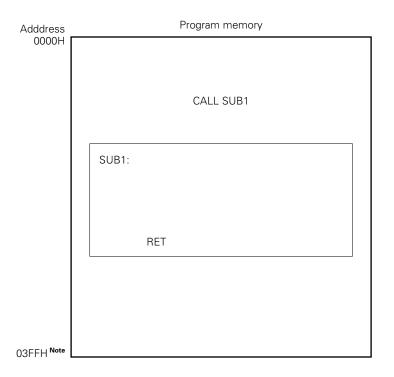

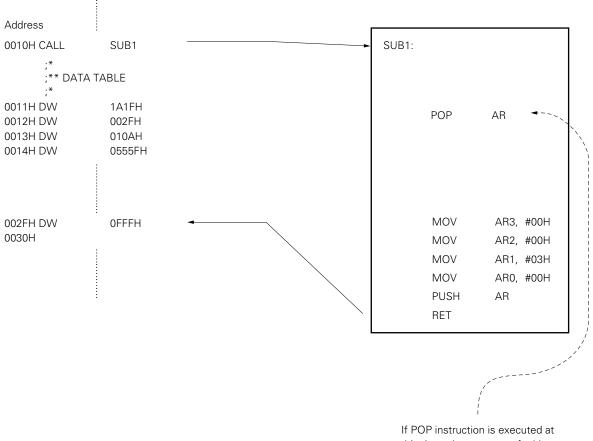

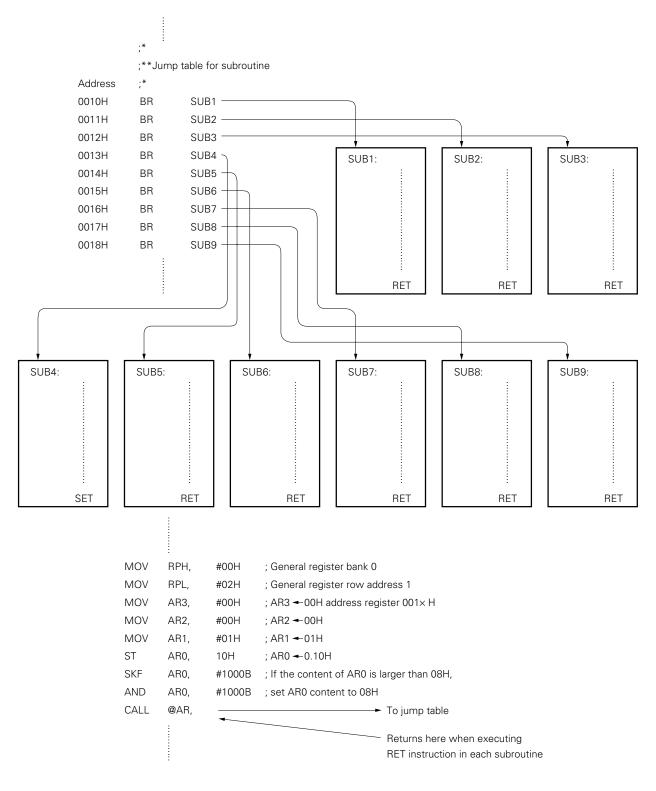

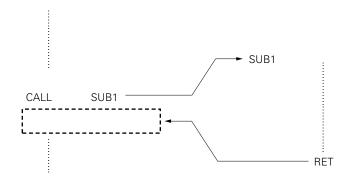

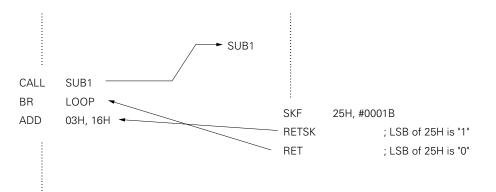

| 4-2          | Direct Subroutine Call (CALL addr)                                              |   |

| 4-3          | Table Reference (MOVT DBF, @AR)                                                 |   |

| 5-1          | Configuration of Data Memory                                                    |   |

| 5-2          | System Register Configuration                                                   |   |

| 5-3          | Data Buffer Configuration                                                       |   |

| 5-4          | General Register (GR) Configuration                                             |   |

| 5-5          | Port Register Configuration                                                     |   |

| 6-1          | Stack Configuration                                                             |   |

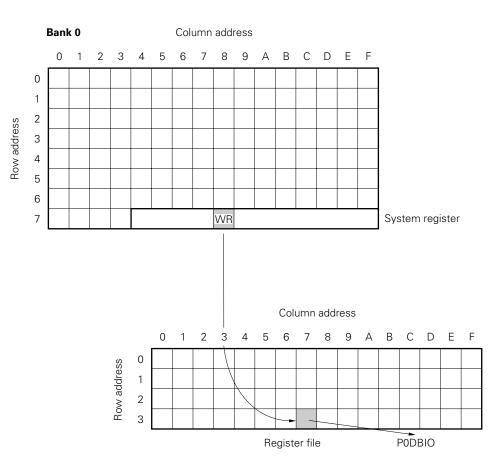

| 7-1          | Allocation of System Register in Data Memory                                    |   |

| 7-2          | System Register Configuration                                                   |   |

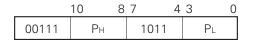

| 7-3          | Address Register Configuration                                                  |   |

| 7-4          | Address Register Used as a Peripheral Register                                  |   |

| 7-5          | Window Register Configuration                                                   |   |

| 7-6          | Bank Register Configuration                                                     |   |

| 7-7          | Index Register and Memory Pointer Configuration                                 |   |

| 7-8          | Data Memory Address Modification by Index Register and Memory Pointer           |   |

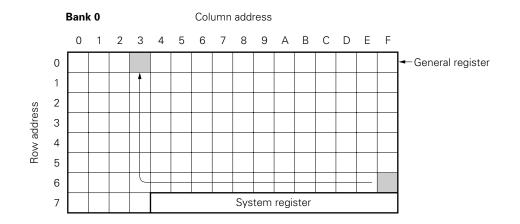

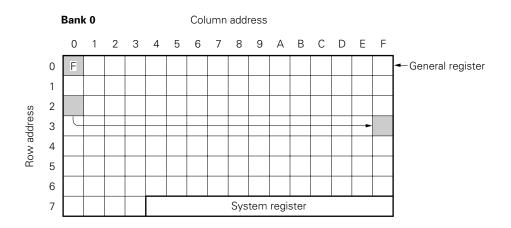

| 7-9          | Example of Operation When MPE=0 and IXE=0                                       |   |

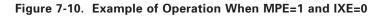

| 7-10         | Example of Operation When MPE=1 and IXE=0                                       |   |

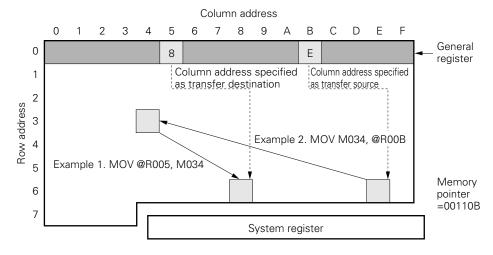

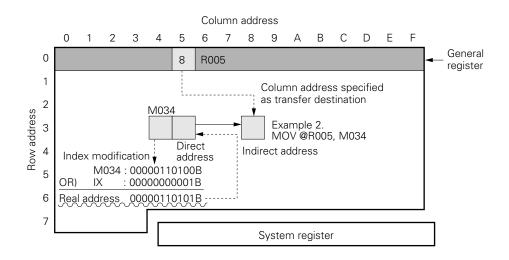

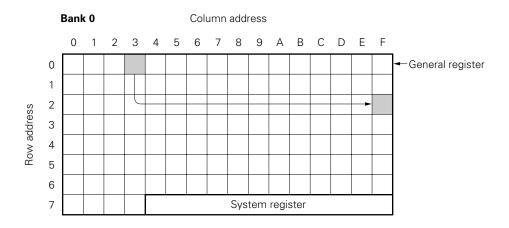

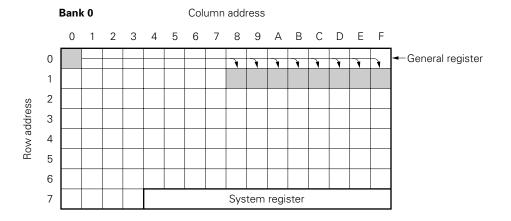

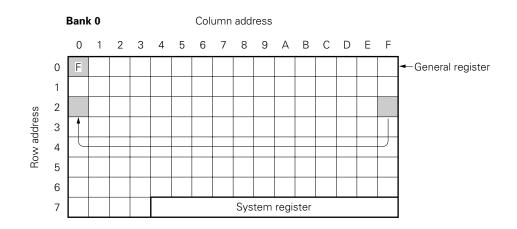

| 7-11         | Example of Operation When MPE=0 and IXE=1                                       |   |

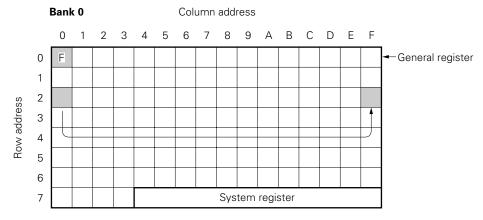

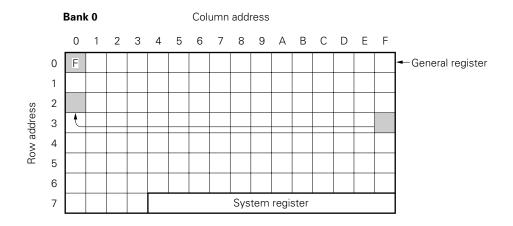

| 7-12         | Example of Operation When MPE=0 and IXE=1                                       |   |

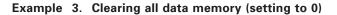

| 7-13         | Example of Operation When MPE=0 and IXE=1 (Array Processing)                    |   |

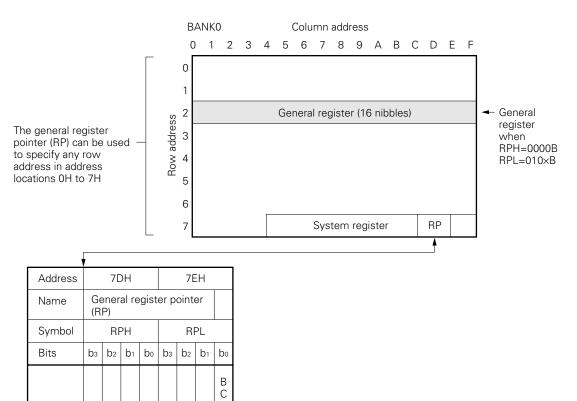

| 7-14         | General Register Pointer Configuration                                          |   |

| 7-14<br>7-15 | General Register Configuration                                                  |   |

| 7-16         | Program Status Word Configuration                                               |   |

| 7-17         | Outline of Functions of the Program Status Word                                 |   |

| 8-1          | General Register Configuration                                                  |   |

| 9-1          | Register File Configuration                                                     |   |

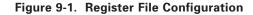

| 9-2          | Relationship Between the Register File and Data Memory                          |   |

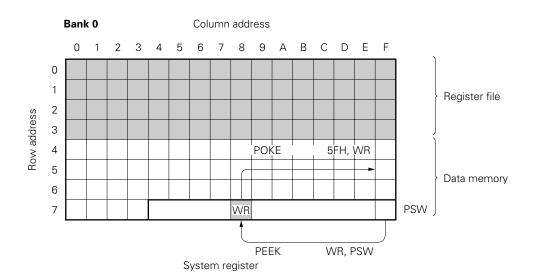

| 9-3          | Accessing the Register File Using the PEEK and POKE Instructions                |   |

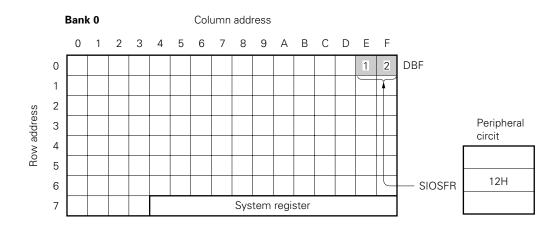

| 10-1         | Allocation of the Data Buffer                                                   |   |

| 10-2         | Data Buffer Configuration                                                       |   |

| 10-3         | Relationship Between the Data Buffer and Peripheral Hardware                    |   |

| 11-1         | Configuration of the ALU                                                        |   |

| 12-1         | Changes in port register due to execution of the CLR1 P0E1 instruction          |   |

| 12-2         | Input/Output Switching by Group I/O                                             |   |

| 12-3         | Bit I/O Port Control Register                                                   |   |

# LIST OF FIGURES (2/2)

| Figure No. | Title                                                                      | Pag |

|------------|----------------------------------------------------------------------------|-----|

| 13-1       | Configuration of the 8-bit Timer Counter                                   | 118 |

| 13-2       | Timer Mode Register                                                        | 119 |

| 13-3       | Setting the Count Value in a Modulo Register                               | 122 |

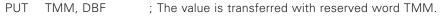

| 13-4       | Error in Zero-Clearing the Count Registe during Counting                   |     |

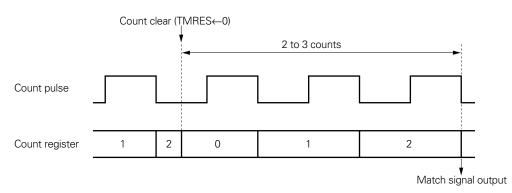

| 13-5       | Error in Starting Counting from the Count Halt State                       |     |

| 13-6       | Reading 8-Bit Counter Count Values                                         | 12  |

| 13-7       | Timer Output Control Mode Register                                         |     |

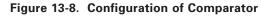

| 13-8       | Configuration of Comparator                                                |     |

| 13-9       | Comparator Input Channel Selection Register                                | 13  |

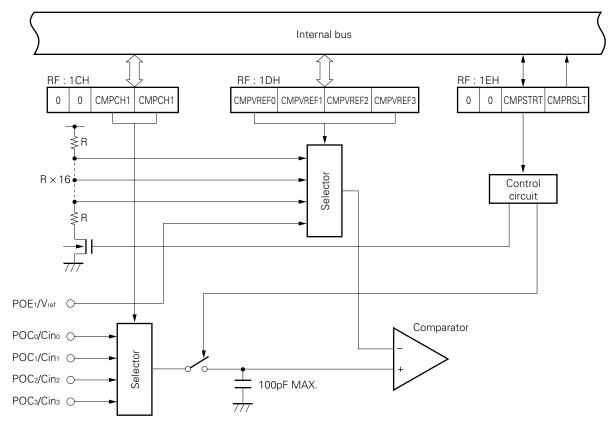

| 13-10      | Reference Voltage Selection Register                                       |     |

| 13-11      | Comparator Operation Control Register                                      | 134 |

| 13-12      | Block Diagram of the Serial Interface                                      | 13  |

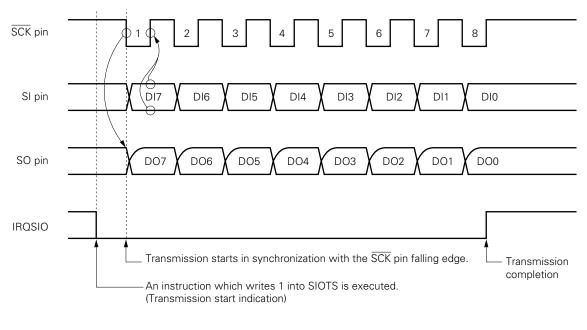

| 13-13      | Timing of 8-Bit Transmission and Reception Mode                            | 10  |

| 10-10      | (Simultaneous Transmission Reception)                                      | 13  |

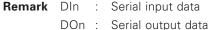

| 13-14      | Timing of the 8-Bit Reception Mode                                         | 13  |

| 13-14      |                                                                            | 13  |

| 13-15      | Serial Interface Control Register<br>Setting a Value in the Shift Register | 13  |

| 13-10      | Reading a Value from the Shift Register                                    |     |

| 13-17      | Reading a value from the Shirt Register                                    | 14  |

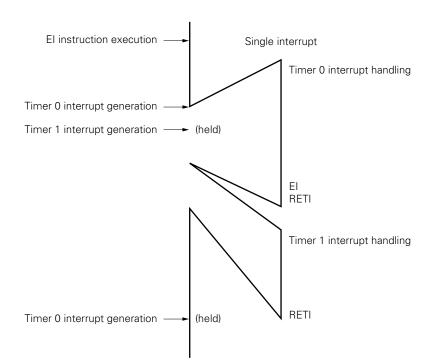

| 14-1       | Interrupt Control Register                                                 | 14  |

| 14-2       | Interrupt Handling Procedure                                               | 15  |

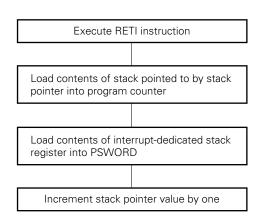

| 14-3       | Return from Interrupt Handling                                             | 15  |

| 14-4       | Interrupt Acceptance Timing Chart (when INTE=1 and IPxxx=1)                | 15  |

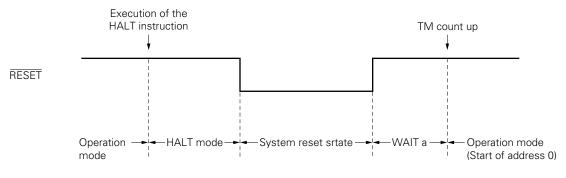

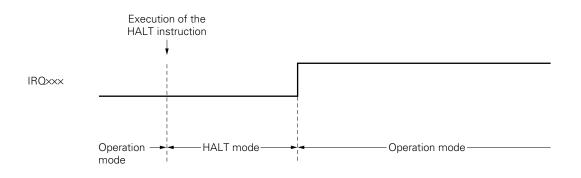

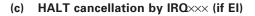

| 15-1       | Cancellation of HALT Mode                                                  | 16  |

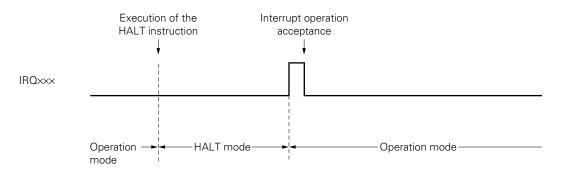

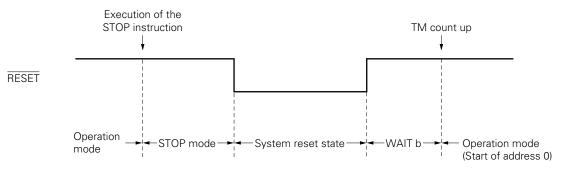

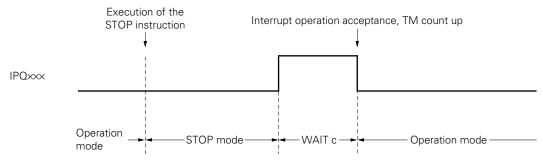

| 15-2       | Cancellation of STOP Mode                                                  | 16  |

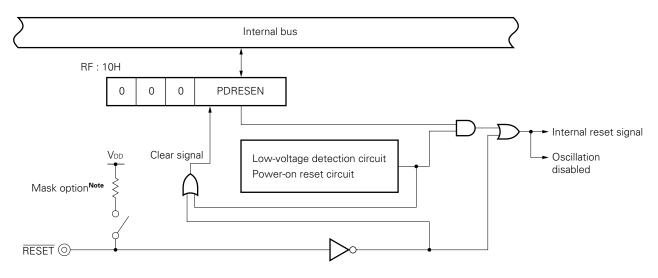

| 16-1       | Reset Block Configuration                                                  | 17  |

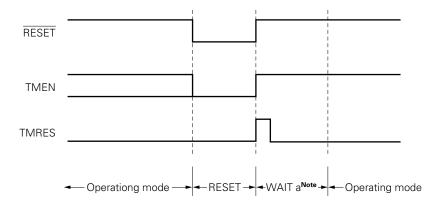

| 16-2       | Resetting                                                                  | 17  |

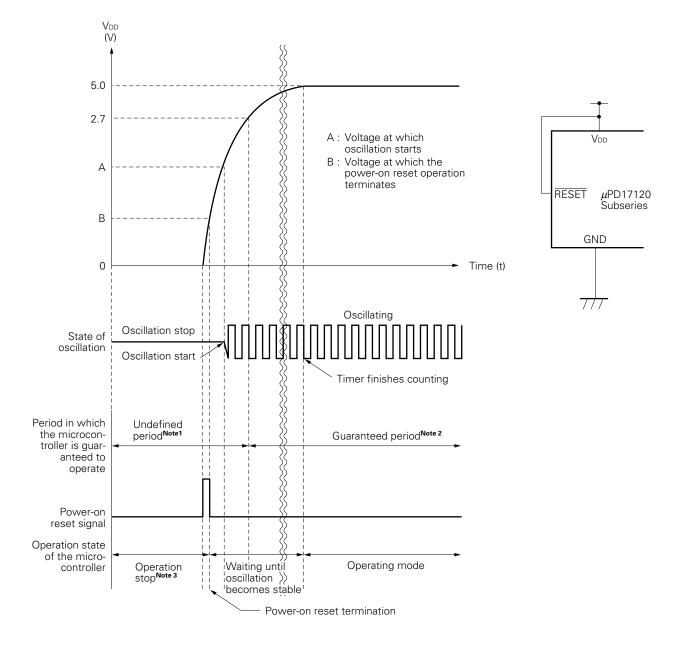

| 16-3       | Example of the Power-On Reset Operation                                    | 17  |

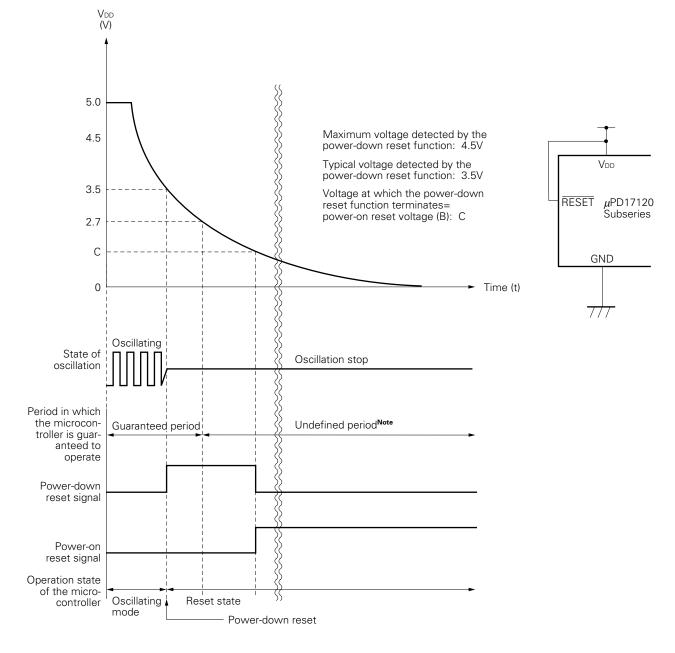

| 16-4       | Example of the Power-Down Reset Operation                                  |     |

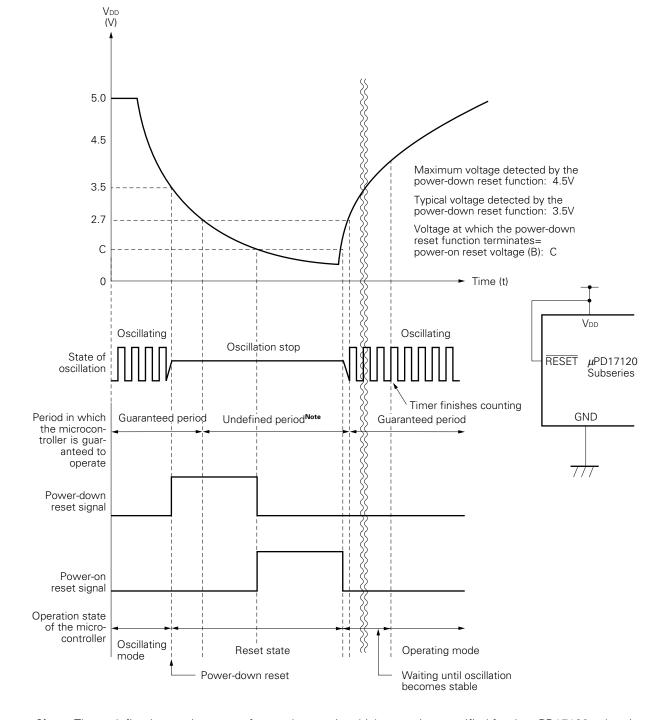

| 16-5       | Example of Reset Operation during the Period from Power-Down Reset to      | .,  |

| 100        | Power Recovery                                                             | 17  |

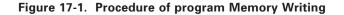

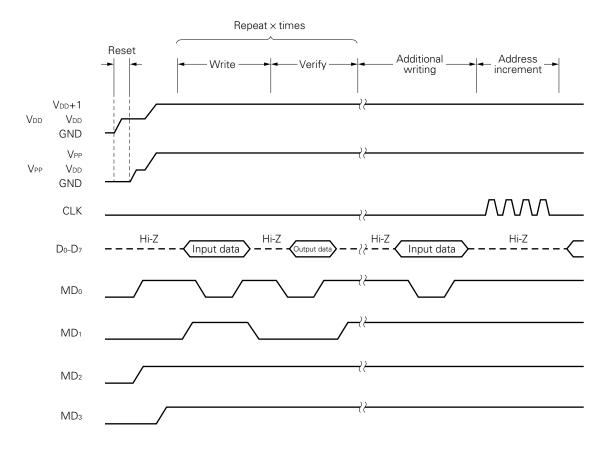

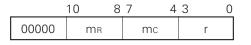

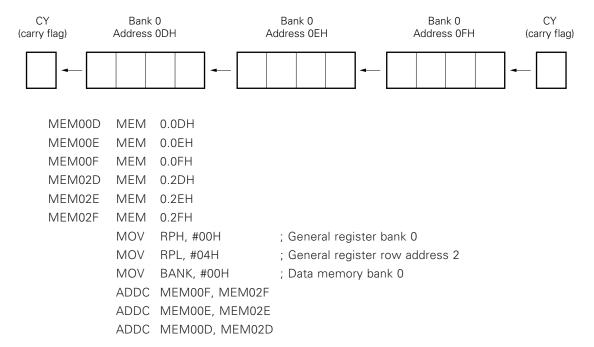

| 17-1       | Procedure of program Memory Writing                                        | 18  |

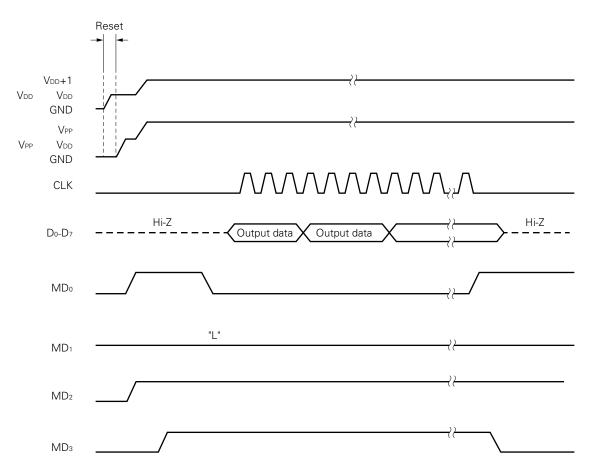

| 17-1       | Procedure of Program Memory Reading                                        | 18  |

| 19-1       | Configuration of Control Register (µPD17120, 17121)                        |     |

|            |                                                                            |     |

| 19-2       | Configuration of Control Register (µPD17132, 17133, 17P132, 17P133)        | 26  |

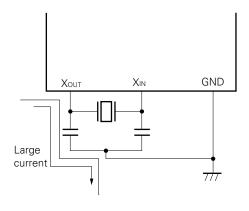

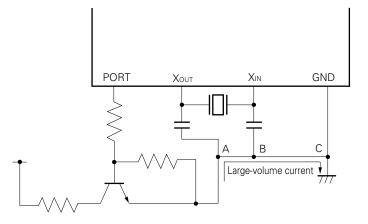

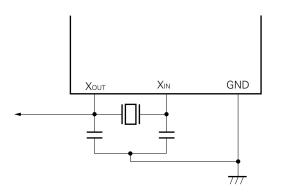

| C-1        | Externally Installed System Clock Oscillation Circuit                      |     |

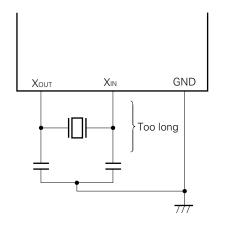

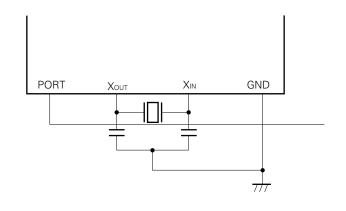

| C-2        | Unsatisfactory Oscillation Circuit Examples                                | 27  |

# LIST OF TABLES (1/1)

| Table No. | Title                                                                              | Page |

|-----------|------------------------------------------------------------------------------------|------|

| 2-1       | Handling Unused Pins                                                               | 17   |

| 4-1       | Vector Address for the $\mu$ PD17120 Subseries                                     | 25   |

| 6-1       | Operation of the Stack Pointer                                                     | 37   |

| 6-2       | Operation of the Stack Pointer during Execution                                    |      |

| 6-3       | Stack Operation during Table Reference                                             |      |

| 6-4       | Stack Operation during Interrupt Receipt and Return                                |      |

| 6-5       | Stack Operation during the PUSH and POP Instructions                               |      |

| 7-1       | Address-modified Instruction Statements                                            | 49   |

| 7-2       | Zero Flag (Z) and Compare Flag (CMP)                                               | 63   |

| 10-1      | Peripheral Hardware                                                                | 81   |

| 11-1      | List of ALU Instructions                                                           |      |

| 11-2      | Results of Arithmetic Operations Performed in 4-Bit Binary and BCD                 |      |

| 11-3      | Types of Arithmetic Operations                                                     |      |

| 11-4      | Logical Operations                                                                 | 97   |

| 11-5      | Table of True Values for Logical Operations                                        | 97   |

| 11-6      | Bit Judgement Instructions                                                         | 97   |

| 11-7      | Comparison Judgement Instructions                                                  | 99   |

| 12-1      | Writing into and Reading from the Port Register (0.70H)                            |      |

| 12-2      | Writing into and Reading from the Port Register (0.71H)                            | 106  |

| 12-3      | Writing/reading to/from Port Register (0.72Η) (μPD17120, 17121)                    | 107  |

| 12-4      | Writing into and Reading from the Port Register (0.72H) and Pin Function Selection | 108  |

| 12-5      | Register File Contents and Pin Functions                                           | 110  |

| 12-6      | Contents Read from the Port Register (0.73H)                                       | 110  |

| 12-7      | Writing into and Reading from the Port Registers (0.6FH.0, 0.6FH.1)                | 111  |

| 13-1      | Timer Resolution and Maximum Setting Time                                          | 130  |

| 13-2      | List of Serial Clock                                                               | 135  |

| 13-3      | Serial Interface's Operation Mode                                                  | 137  |

| 14-1      | Interrupt Source Types                                                             | 146  |

| 14-2      | Interrupt Request Flag and Interrupt Enable Flag                                   | 147  |

| 15-1      | States during Standby Mode                                                         | 162  |

| 15-2      | HALT Mode Cancellation Condition                                                   |      |

| 15-3      | Start Address After HALT Mode Cancellation                                         | 163  |

| 15-4      | STOP Mode Cancellation Condition                                                   | 167  |

| 15-5      | Start Address After STOP Mode Cancellation                                         | 167  |

| 16-1      | State of Each Hardware Unit When Reset                                             | 171  |

| 17-1      | Pins Used for Writing/Verifying Program Memory                                     | 179  |

| 17-2      | Differences Between Mask ROM Version and One-Time PROM Version                     |      |

| 17-3      | Operating Mode Setting                                                             | 180  |

| 19-1      | Mask Option Definition Pseudo Instructions                                         | 252  |

|           |                                                                                    |      |

# [MEMO]

# **CHAPTER 1 GENERAL**

The  $\mu$ PD17120, 17121, 17132 and 17133 are 4-bit single-chip microcontrollers employing the 17K architecture and containing 8-bit timer (1 channel), 3-wire serial interface, and power-on/power-down reset circuit.

The  $\mu$ PD17P132 and 17P133 are the one-time PROM version of the  $\mu$ PD17132 and 17133, respectively, and are suitable for program evaluation at system development and for small-scale production.

The following are features of the  $\mu$ PD17120 subseries.

- Comparator input (μPD17132, 17133, 17P132, 17P133 only)

- · Comparison function with external reference voltage (Vref)

- Can be used as 4-bit A/D converter by using 15 types of internal reference voltage (1/16 to 15/16 Vbb) depending on the software

- 3-wire serial interface: 1 channel

- Power-on/power-down reset circuit (reducing external circuits)

- $\mu$ PD17P132 and 17P133 can operate in the same way as mask ROM version

- · VDD = 2.7 to 5.5 V

These features of the  $\mu$ PD17120 subseries are suitable for use as a controller or a sub-microcomputer device in the following application fields;

- Electric fan

- Hot plate

- Audio equipment

- Mouse

- Printer

- Plain paper copier

# **1.1 FUNCTION LIST**

| Item<br>Product Name                 | μPD17120                                                                | μPD17132                                          | μPD17P132                                                                                  | μPD17121                            | μPD17133                                           | μPD17P133            |  |

|--------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------|----------------------|--|

|                                      | Maske                                                                   | d ROM                                             | One-time PROM                                                                              | Maske                               | d ROM                                              | One-time PROM        |  |

| ROM Capacity                         | 1.5K bytes<br>(768 × 16 bits)                                           |                                                   | oytes<br>< 16 bits)                                                                        | 1.5K bytes<br>(768 × 16 bits)       | 2K bytes<br>(1024 × 16 bits)                       |                      |  |

| RAM Capacity                         | $64 \times 4$ bits                                                      | 111 ×                                             | 4 bits                                                                                     | $64 \times 4$ bits                  | 111 >                                              | 4 bits               |  |

| Stack                                | 5 address stac                                                          | ks; 1 interrupt                                   | stack                                                                                      |                                     |                                                    |                      |  |

| Input/output port count              | 19 ports                                                                | 3 input/output p<br>sense input (IN               |                                                                                            |                                     |                                                    |                      |  |

| Comparator<br>(Supply voltage)       | None         4-channel<br>(V <sub>DD</sub> = 2.7 to 5.5 V)         None |                                                   |                                                                                            |                                     |                                                    | annel<br>7 to 5.5 V) |  |

| Timer                                | 1-channel (8-bi                                                         | t timer)                                          |                                                                                            |                                     |                                                    |                      |  |

| Serial Interface                     | 1-channel (3-w                                                          | ire)                                              |                                                                                            |                                     |                                                    |                      |  |

| Interrupt                            | <ul><li>1 external in</li><li>2 internal ir</li></ul>                   |                                                   | Detection of the<br>Detection of the<br>Detection of bot<br>Timer (TM)<br>Serial interface | trailing edge<br>h rising and trail |                                                    | lectable             |  |

| System clock                         |                                                                         | RC oscillation                                    |                                                                                            | С                                   | eramic oscillati                                   | on                   |  |

| Instruction Execution Time           | 8 µs                                                                    | (when fcc = $2$                                   | MHz)                                                                                       | 2 με                                | s (when fx = 8 l                                   | ЛНz)                 |  |

| Standby Function                     | HALT, STOP                                                              |                                                   |                                                                                            |                                     |                                                    |                      |  |

| Power-on/Power-down<br>Reset Circuit |                                                                         | Incorporated<br>used on an appl<br>of Vdd=5 V±10% |                                                                                            |                                     | Incorporated<br>used on an appl<br>10%; fx = 400 k |                      |  |

| Operating Supply Voltage             | • 2.7 to 5.5 V<br>• 4.5 to 5.5 V (                                      | When using the                                    | power-on powe                                                                              | r/down reset fun                    | iction)                                            |                      |  |

| Package                              | <ul><li> 24-pin plastic</li><li> 24-pin plastic</li></ul>               | shrink DIP (300<br>SOP (375 mil)                  | ) mil)                                                                                     |                                     |                                                    |                      |  |

| One-time PROM Product                | µPD1                                                                    | 7P132                                             | _                                                                                          | µPD1                                | 7P133                                              | -                    |  |

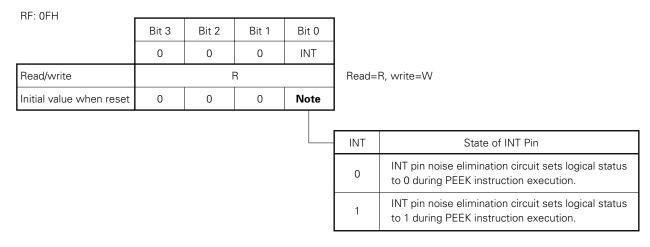

**Note** When not using the external interrupt function, the INT pin can be used as an input-only pin (sense input). As a sense input, the pin status is read not by the port register but by the control register's INT flag.

Caution Despite a high level of functional compatibility with the masked ROM product, the PROM product is different in terms of the internal ROM circuit and some electric features. When switching from a PROM to a masked ROM product, be sure to sufficiently evaluate the application of the masked ROM product based on its sample.

# **1.2 ORDERING INFORMATION**

| Part Number         | Package                             | Internal ROM  |

|---------------------|-------------------------------------|---------------|

| µPD17120CS-×××      | 24-pin plastic shrink DIP (300 mil) | Mask ROM      |

| $\mu$ PD17120GT-xxx | 24-pin plastic SOP (375 mil)        | Mask ROM      |

| µPD17121CS-×××      | 24-pin plastic shrink DIP (300 mil) | Mask ROM      |

| $\mu$ PD17121GT-xxx | 24-pin plastic SOP (375 mil)        | Mask ROM      |

| µPD17132CS-×××      | 24-pin plastic shrink DIP (300 mil) | Mask ROM      |

| $\mu$ PD17132GT-xxx | 24-pin plastic SOP (375 mil)        | Mask ROM      |

| µPD17133CS-×××      | 24-pin plastic shrink DIP (300 mil) | Mask ROM      |

| $\mu$ PD17133GT-xxx | 24-pin plastic SOP (375 mil)        | Mask ROM      |

| μPD17P132CS         | 24-pin plastic shrink DIP (300 mil) | One-time PROM |

| μPD17P132GT         | 24-pin plastic SOP (375 mil)        | One-time PROM |

| μPD17P133CS         | 24-pin plastic shrink DIP (300 mil) | One-time PROM |

| $\mu$ PD17P133GT    | 24-pin plastic SOP (375 mil)        | One-time PROM |

Remark xxx: ROM code number

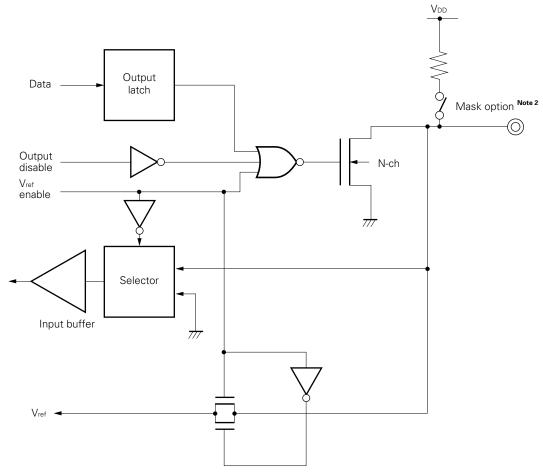

# 1.3 BLOCK DIAGRAM

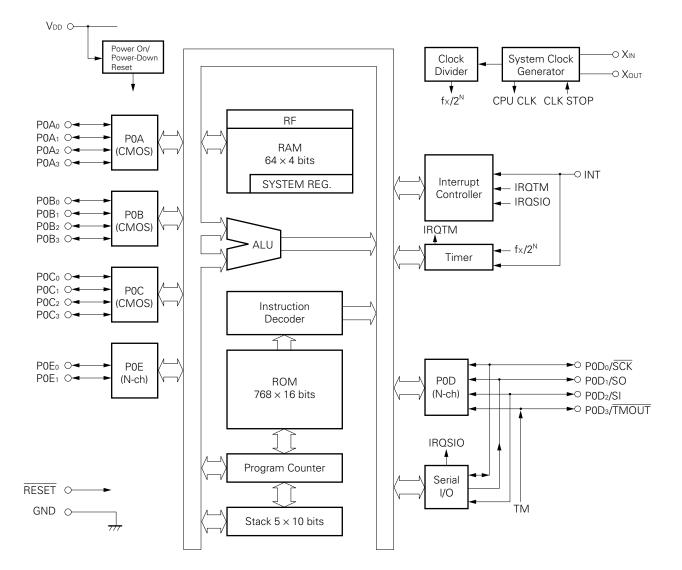

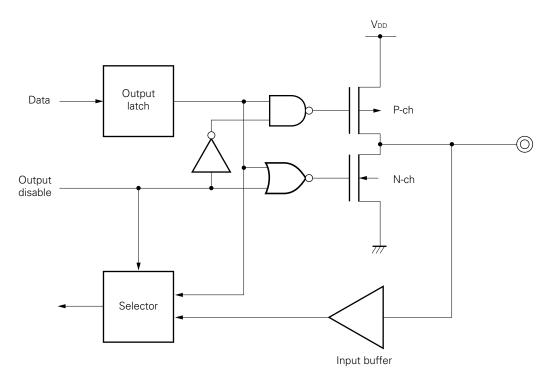

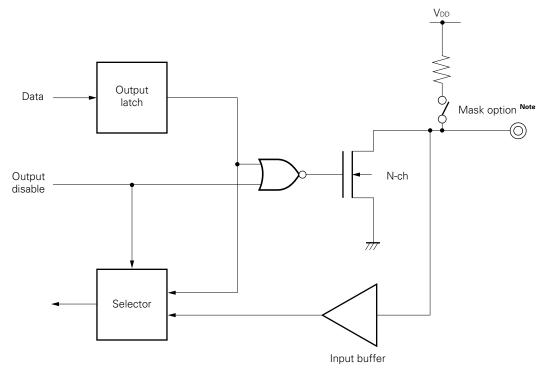

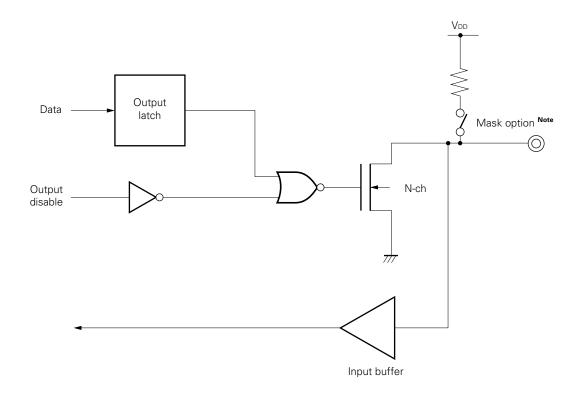

# - Block diagram of the $\mu$ PD17120 and 17121

Remark

The terms CMOS and N-ch in parentheses indicate the output form of the port.

CMOS:

CMOS push-pull output

N-ch: N-channel open-drain output (Each pin can contain pull-up resistor as specified using a mask option.)

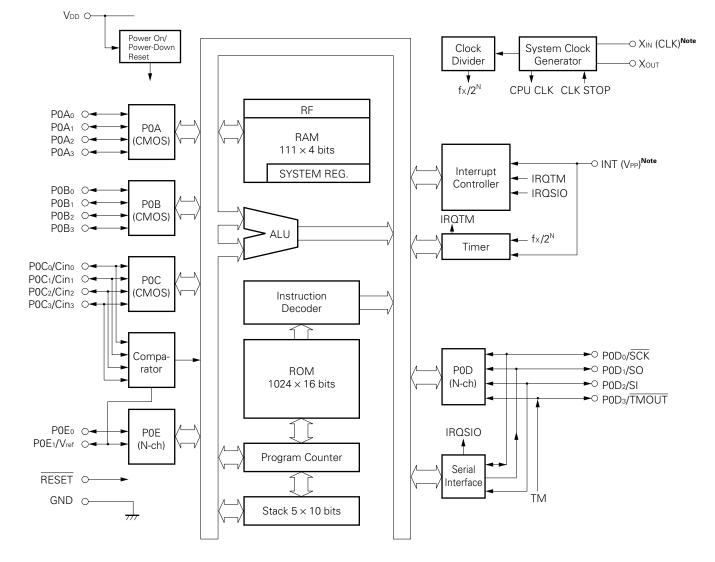

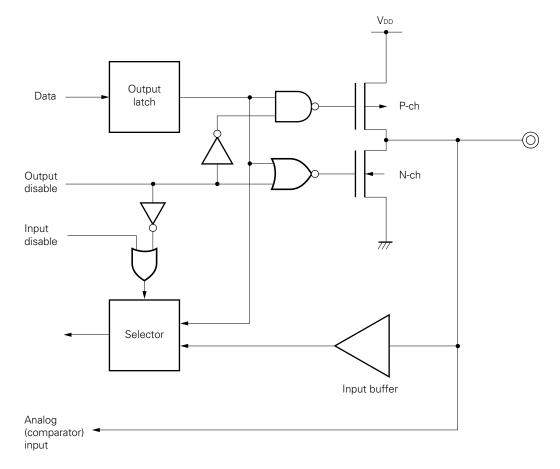

# • Block diagram of μPD17132, 17133, 17P132, and 17P133

- **Remark** The terms CMOS and N-ch in parentheses indicate the output form of the port. CMOS: CMOS push-pull output

- N-ch: N-channel open-drain output (Each pin can contain pull-up resistor as specified using a mask option.)

- **Note** The devices in parentheses are effective only in the case of program memory write/verify mode of the  $\mu$ PD17P132 and  $\mu$ PD17P133.

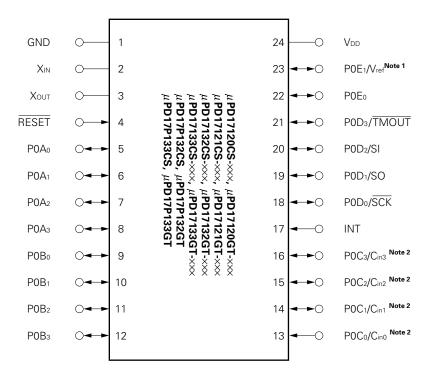

# 1.4 PIN CONFIGURATION (Top View)

## (1) Normal operating mode

24-pin plastic shrink DIP 24-pin plastic SOP

**Notes** 1. There is no  $V_{ref}$  pin for the  $\mu$ PD17120 and 17121.

**2.** Pins Cin<sub>0</sub> to Cin<sub>3</sub> do not exist in the  $\mu$ PD17120 and 17121.

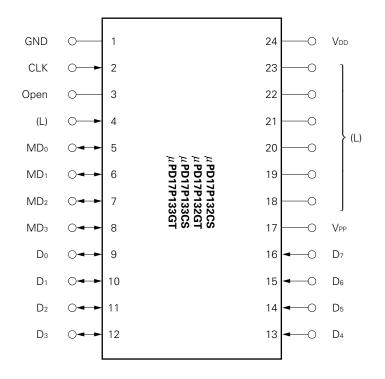

## (2) Program memory write/verify mode

# $\label{eq:caution} \ \ \text{()} represents processing of the pins which are not used in program memory write/verify mode.$

- L : Connect to GND via pull-down resistor one by one.

- Open : This pin should not be connected.

# (3) Pin name

| Cino to Cin3                         | : | Comparator input                     |

|--------------------------------------|---|--------------------------------------|

| CLK                                  | : | Clock input for address verification |

| Do to D7                             | : | Data input/output                    |

| GND                                  | : | Ground                               |

| INT                                  | : | External interrupt input             |

| MD <sub>0</sub> to MD <sub>3</sub>   | : | Operating mode selection             |

| P0A <sub>0</sub> to P0A <sub>3</sub> | : | Port 0A                              |

| P0Bo to P0B3                         | : | Port 0B                              |

| POC <sub>0</sub> to POC <sub>3</sub> | : | Port 0C                              |

| P0D <sub>0</sub> to P0D <sub>3</sub> | : | Port 0D                              |

| P0E <sub>0</sub> to P0E <sub>3</sub> | : | Port 0E                              |

| RESET                                | : | Reset input                          |

| SCK                                  | : | Serial clock input/output            |

| SI                                   | : | Serial data input                    |

| SO                                   | : | Serial data output                   |

| TMOUT                                | : | Timer output                         |

| Vdd                                  | : | Power supply                         |

| Vpp                                  | : | Programming voltage supply           |

| Vref                                 | : | External reference voltage           |

| Xin, Xout                            | : | System clock oscillation             |

# [MEMO]

# **CHAPTER 2 PIN FUNCTIONS**

# 2.1 PIN FUNCTIONS

# 2.1.1 Pins in Normal Operation Mode

| Pin No.   | Symbol           | Function                                                                          | Output    | At Power- |

|-----------|------------------|-----------------------------------------------------------------------------------|-----------|-----------|

| 1 11 110. | Symbol           | i unction                                                                         | Format    | on/Reset  |

| 1         | GND              | Grounded                                                                          | _         | _         |

| 2         | Xin              | μ <b>PD17121, 17133, 17P133</b>                                                   |           |           |

| 3         | Хоит             | • Xin, Xout                                                                       |           |           |

|           |                  | · Pins for system clock resonator oscillation                                     |           |           |

|           |                  | · Connected to ceramic resonator                                                  | -         | -         |

| 2         | OSC1             | μ <b>PD17120, 17132, 17P132</b>                                                   |           |           |

| 3         | OSC0             | • OSC0, OSC1                                                                      |           |           |

|           |                  | <ul> <li>Pins for system clock oscillation</li> </ul>                             |           |           |

|           |                  | $\cdot$ Resistor is connected between OSC0 and OSC1                               |           |           |

| 4         | RESET            | System reset input                                                                | _         | Input     |

|           |                  | Pull-up resistor can be incorporated by mask option $\ensuremath{^{\hbox{Note}}}$ |           |           |

| 5         | P0A <sub>0</sub> | Port 0A                                                                           | CMOS      | Input     |

| I         | I                | · 4-bit I/O port                                                                  | Push-pull |           |

| 8         | P0A3             | · Input/output can be set by each bit                                             |           |           |

| 9         | P0B <sub>0</sub> | Port 0B                                                                           | CMOS      | Input     |

| I         | I                | · 4-bit I/O port                                                                  | Push-pull |           |

| 12        | P0B3             | · Input/output can be set by 4-bit unit                                           |           |           |

| 13        | P0Co/Cino        | Port 0C and analog voltage input of comparator                                    | CMOS      | Input     |

| I         | I                | • P0Co to P0C3                                                                    | Push-pull | (P0C)     |

| 16        | P0C3/Cin3        | · 4-bit I/O port                                                                  |           |           |

|           |                  | · Input/output can be set by each bit                                             |           |           |

|           |                  | • Cino to Cin3 (μPD17132, 17133, 17P132, 17P133 only)                             |           |           |

|           |                  | · Analog input of comparator                                                      |           |           |

| 17        | INT              | External interrupt request signal input and sense input                           | -         | Input     |

**Note** The  $\mu$ PD17P132 and 17P133 have no pull-up resistor by mask option.

| Pin No. Symbo |                      | Function                                                                                                              | Output     | At Power- |

|---------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|------------|-----------|

| FIII NO.      | Symbol               |                                                                                                                       | Format     | on/Reset  |