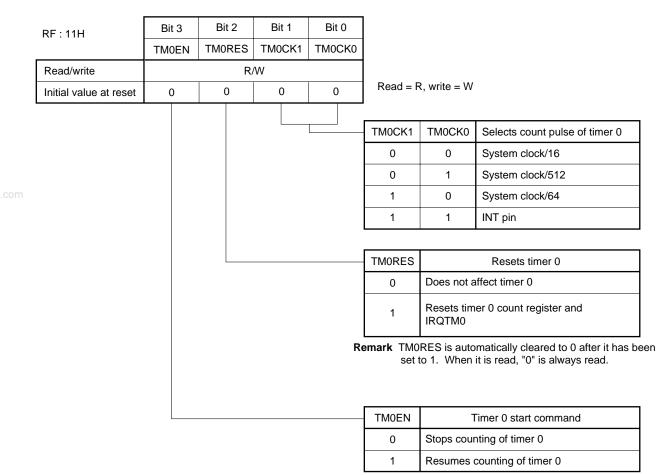

# mos integrated circuit $\mu$ PD17145(A1), 17147(A1), 17149(A1)

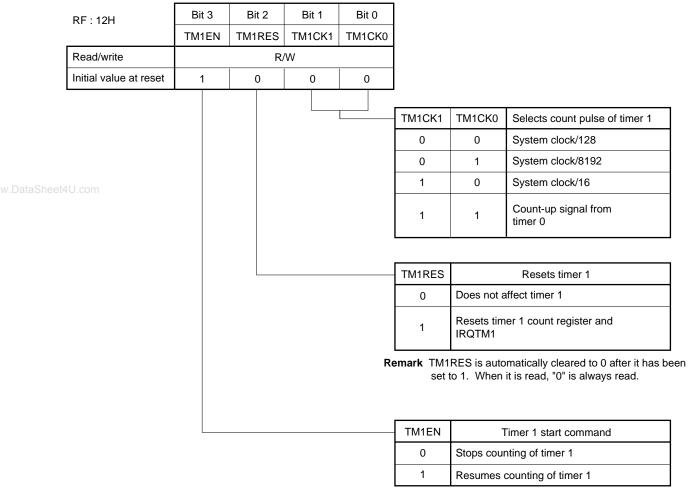

# SMALL, GENERAL-PURPOSE 4-BIT SINGLE-CHIP MICROCONTROLLERS

The  $\mu$ PD17145(A1), 17147(A1), and 17149(A1) are 4-bit single-chip microcontrollers integrating an 8-bit A/D converter (4 channels), a timer function (3 channels), and a serial interface.

These microcontrollers employ a CPU of the general-purpose register type that can execute direct memory operations and direct memory-to-memory data transfer for efficient programming. All the instructions consist of 16 bits per word.

In addition, a one-time PROM version, the  $\mu$ PD17P149, is also available for program evaluation.

The functions of these microcontrollers are described in detail in the following User's Manual. Be sure to read the following manual when designing your system:

$\mu$ PD17145 Subseries User's Manual: IEU-1383

#### **FEATURES**

17K architecture : General-purpose register type

: Instruction length fixed to 16 bits

• Program memory (ROM) :  $\mu$ PD17145(A1) : 2 KB (1024 × 16 bits)

:  $\mu$ PD17147(A1) : 4 KB (2048  $\times$  16 bits)

:  $\mu$ PD17149(A1) : 8 KB (4096 × 16 bits)

• Data memory (RAM) : 110 × 4 bits

External interrupt : 1 (INT pin, with sense input)

• Instruction execution time : 2  $\mu$ s (at 8 MHz: ceramic oscillation)

8-bit A/D converter

4 channels, absolute accuracy: ±1.5 LSB MAX. (VDD = 4.0 to 5.5 V)

Timer : 3 channels

Serial interface : 1 channel (clocked 3-wire)

POC circuit (mask option)

Operating voltage : VDD = 2.7 to 5.5 V (at 400 kHz to 2 MHz)

:  $V_{DD} = 4.5 \text{ to } 5.5 \text{ V (at } 400 \text{ kHz to } 8 \text{ MHz)}$

• Operating temperature :  $T_a = -40 \text{ to } +110 ^{\circ}\text{C}$

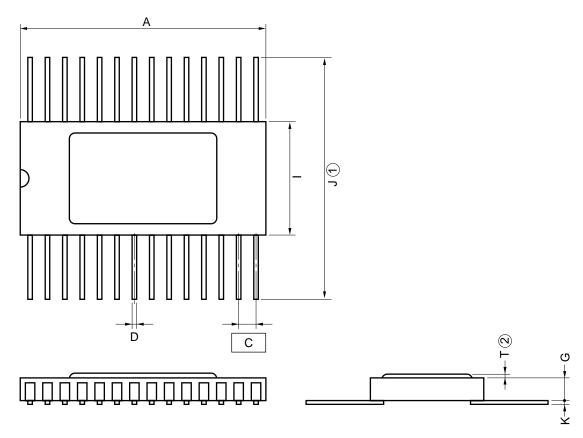

#### **APPLICATIONS**

Automotive electronics, etc.

Unless contextually excluded, references in this data sheet to the  $\mu$ PD17149 (A1) mean the  $\mu$ PD17145 (A1) and  $\mu$ PD17147 (A1).

The information in this document is subject to change without notice.

# **ORDERING INFORMATION**

| Part Number                            | Package                             | Quality Grade |  |

|----------------------------------------|-------------------------------------|---------------|--|

| μPD17145CT(A1)-×××                     | 28-pin plastic shrink DIP (400 mil) | Special       |  |

| $\mu$ PD17145GT(A1)- $\times$ $\times$ | 28-pin plastic SOP (375 mil)        | Special       |  |

| $\mu$ PD17147CT(A1)- $\times\times$    | 28-pin plastic shrink DIP (400 mil) | Special       |  |

| $\mu$ PD17147GT(A1)- $\times\times$    | 28-pin plastic SOP (375 mil)        | Special       |  |

| $\mu$ PD17149CT(A1)- $\times\times$    | 28-pin plastic shrink DIP (400 mil) | Special       |  |

| $\mu$ PD17149GT(A1)- $\times$ $\times$ | 28-pin plastic SOP (375 mil)        | Special       |  |

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document No. C11531E) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications.

#### **FUNCTION LIST**

| Part Number                | μPD17145 (A1)                                                                                                                                                    | μPD17147 (A1)                          | μPD17149 (A1) |  |  |

|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------|--|--|

| ROM capacity               | 2 KB (1024 × 16 bits) 4 KB (2048 × 16 bits) 8 KB (4096 × 16 bits                                                                                                 |                                        |               |  |  |

| RAM capacity               | 110 × 4 bits                                                                                                                                                     |                                        |               |  |  |

| Stack                      | Address stack × 5, interrup                                                                                                                                      | t stack × 3                            |               |  |  |

| I/O ports                  | 23 (• I/O • Input • Sense input (INT pi                                                                                                                          | : 20<br>: 2<br>n <sup>Note</sup> ) : 1 |               |  |  |

| A/D converter input        | 4 channels (shared with po                                                                                                                                       | rt pins), absolute accuracy: ±         | 1.5 LSB MAX.  |  |  |

| Timer                      | 3 channels  • 8-bit timer/counter: 2 channels (can be used as 1 channel of 16-bit timer) • 7-bit basic interval timer: 1 channel (can be used as watchdog timer) |                                        |               |  |  |

| Serial interface           | 1 channel (3-wire)                                                                                                                                               |                                        |               |  |  |

| Interrupt                  | • Multiple interrupt by hardware (3 levels MAX.)     • External interrupt (INT): 1                                                                               |                                        |               |  |  |

| Instruction execution time | 2 μs (at 8 MHz, ceramic os                                                                                                                                       | cillation)                             |               |  |  |

| Standby function           | HALT, STOP                                                                                                                                                       |                                        |               |  |  |

| POC circuit                | Mask option (Can be used in application circuit that operates on $V_{DD}$ = 5 V $\pm$ 10 %, 400 kHz to 4 MHz)                                                    |                                        |               |  |  |

| Operating voltage          | 2.7 to 5.5 V (at 400 kHz to 2 MHz) 4.5 to 5.5 V (at 400 kHz to 8 MHz)                                                                                            |                                        |               |  |  |

| Package                    | 28-pin plastic shrink DIP (400 mil) 28-pin plastic SOP (375 mil)                                                                                                 |                                        |               |  |  |

| One-time PROM version      | $\mu$ PD17P149 (Quality grade is "standard" and not (A1).  Operating temperature range: T <sub>a</sub> = -40 to +85 °C                                           |                                        |               |  |  |

Note The INT pin is used as an input pin (sense input) when the external interrupt function is not used. The status of this pin is read by using the INT flag of a control register, not by a port register.

Caution The PROM version is functionally compatible with the mask ROM versions but its internal circuit and part of the electrical characteristics are different from those of the mask ROM versions. To replace the PROM version with a mask ROM version, thoroughly conduct application evaluation by using a sample of the mask ROM version.

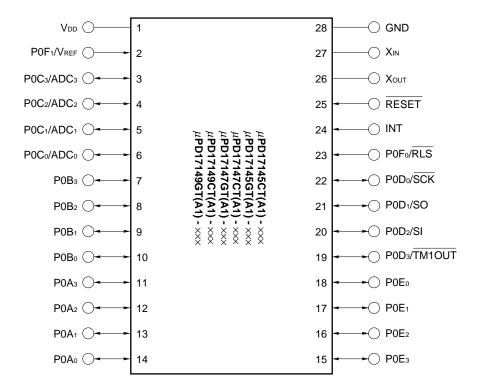

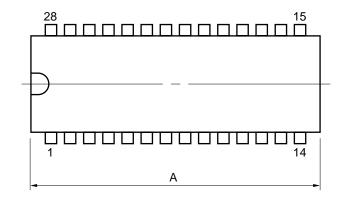

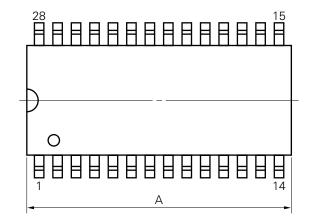

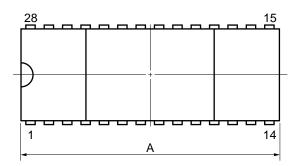

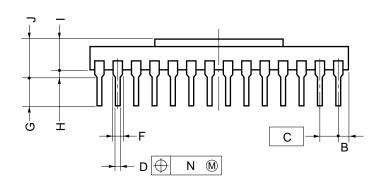

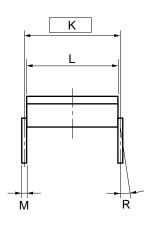

## PIN CONFIGURATION (Top View)

28-pin plastic shrink DIP (400 mil) 28-pin plastic SOP (375 mil)

ww.DataSheet4U.com

ADC<sub>0</sub>-ADC<sub>3</sub> : analog input GND : ground

INT : external interrupt input

P0A0 to P0A3 : port 0A

P0B0 to P0B3 : port 0B

P0C0 to P0C3 : port 0C

P0D0 to P0D3 : port 0D

P0E0 to P0E3 : port 0E

P0F0 and P0F1 : port 0F

RESET : reset input

RLS : standby release signal input

SCK : serial clock I/O

SI : serial data input

SO : serial data output

TM1OUT : timer 1 output

V<sub>DD</sub> : power

VREF : A/D converter reference voltage XIN, XOUT : for system clock oscillation

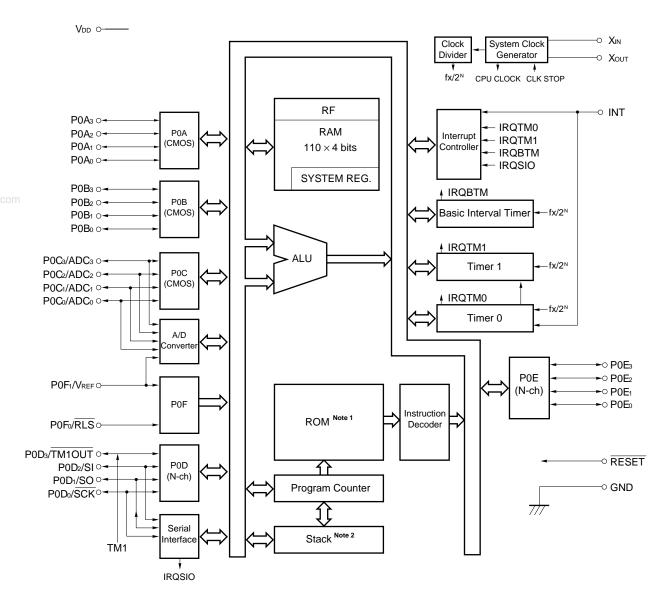

#### **BLOCK DIAGRAM**

Notes 1. The ROM capacity of each product is as follows:

1024 × 16 bits:  $\mu$ PD17145(A1) 2048 × 16 bits:  $\mu$ PD17147(A1) 4096 × 16 bits:  $\mu$ PD17149(A1)

2. The stack capacity of each product is as follows:

$5 \times 10$  bits:  $\mu$ PD17145(A1)  $5 \times 11$  bits:  $\mu$ PD17147(A1)  $5 \times 12$  bits:  $\mu$ PD17149(A1)

Remark CMOS or N-ch in ( ) indicate the output format of the port.

CMOS: CMOS push-pull output N-ch : N-ch open-drain output

MMM DataSheet411

# **CONTENTS**

| 1.                  | PIN                                                                                                                                                          | 9  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1.                | Pin Function                                                                                                                                                 | 9  |

| 1.2                 | Equivalent Circuit of Pin                                                                                                                                    | 11 |

| 1.3                 | Handling of Unused Pins                                                                                                                                      |    |

| 1.4                 | Note on Using RESET and P0Fo/RLS Pins                                                                                                                        | 16 |

| 2.                  | PROGRAM MEMORY (ROM)                                                                                                                                         | 17 |

| <b>2.1</b><br>J.com | Configuration of Program Memory                                                                                                                              | 17 |

| 3.                  | PROGRAM COUNTER (PC)                                                                                                                                         | 18 |

| 3.1                 | Configuration of Program Counter                                                                                                                             | 18 |

| 3.2                 | Operation of Program Counter                                                                                                                                 | 18 |

| 4.                  | STACK                                                                                                                                                        | 19 |

| 4.1                 | Configuration of Stack                                                                                                                                       | 19 |

| 4.2                 | Stack Function                                                                                                                                               | 19 |

| 5.                  | DATA MEMORY (RAM)                                                                                                                                            | 20 |

| 5.1                 | Configuration of Data Memory                                                                                                                                 | 20 |

| 6.                  | GENERAL REGISTER (GR)                                                                                                                                        | 21 |

| 6.1                 | General Register Pointer (RP)                                                                                                                                | 21 |

| 7.                  | SYSTEM REGISTER (SYSREG)                                                                                                                                     | 22 |

| 7.1                 | Configuration of System Register                                                                                                                             | 22 |

| 8.                  | REGISTER FILE (RF)                                                                                                                                           | 24 |

| 8.1                 | Configuration of Register File                                                                                                                               | 24 |

| 8.2                 | Function of Register File                                                                                                                                    | 25 |

| 9.                  | DATA BUFFER (DBF)                                                                                                                                            | 26 |

| 9.1                 | Configuration of Data Buffer                                                                                                                                 | 26 |

| 9.2                 | Function of Data Buffer                                                                                                                                      | 27 |

| 10.                 | ALU BLOCK                                                                                                                                                    | 28 |

| 10.1                | Configuration of ALU Block                                                                                                                                   | 28 |

| 11.                 | PORTS                                                                                                                                                        | 30 |

|                     | Port 0A (P0A <sub>0</sub> , P0A <sub>1</sub> , P0A <sub>2</sub> , P0A <sub>3</sub> )                                                                         |    |

|                     | Port 0B (P0B <sub>0</sub> , P0B <sub>1</sub> , P0B <sub>2</sub> , P0B <sub>3</sub> )                                                                         |    |

|                     | Port 0C (P0C <sub>0</sub> /ADC <sub>0</sub> , P0C <sub>1</sub> /ADC <sub>1</sub> , P0C <sub>2</sub> /ADC <sub>2</sub> , P0C <sub>3</sub> /ADC <sub>3</sub> ) |    |

|                     | Port 0D (P0D <sub>0</sub> /SCK, P0D <sub>1</sub> /SO, P0D <sub>2</sub> /SI, P0D <sub>3</sub> /TM1OUT)                                                        |    |

|                     | 5 Port 0E (P0E <sub>0</sub> , P0E <sub>1</sub> , P0E <sub>2</sub> , P0E <sub>3</sub> )                                                                       |    |

| 11.6                | 6 Port 0F (P0F <sub>0</sub> /RLS, P0F <sub>1</sub> /V <sub>REF</sub> )                                                                                       | 34 |

| 12.  | 8-BIT TIMERS/COUNTERS (TM0, TM1)               | . 35 |

|------|------------------------------------------------|------|

| 12.1 | Configuration of 8-Bit Timers/Counters         | 35   |

| 40   | DAGIO INTERVAL TIMER (DTM)                     |      |

|      | BASIC INTERVAL TIMER (BTM)                     |      |

|      | Configuration of Basic Interval Timer          |      |

|      | Registers Controlling Basic Interval Timer     |      |

| 13.3 | Watchdog Timer Function                        | 43   |

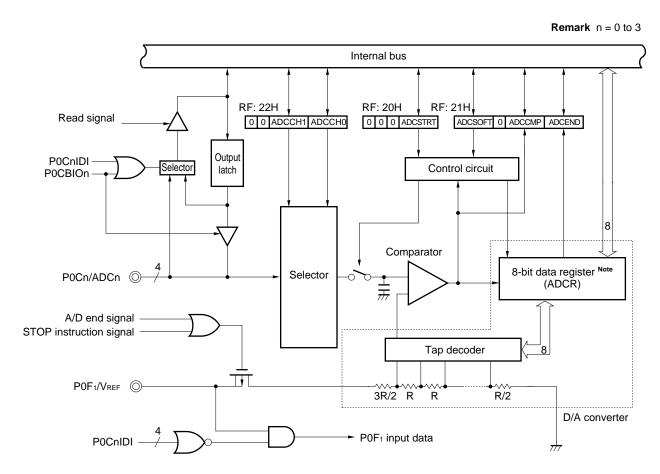

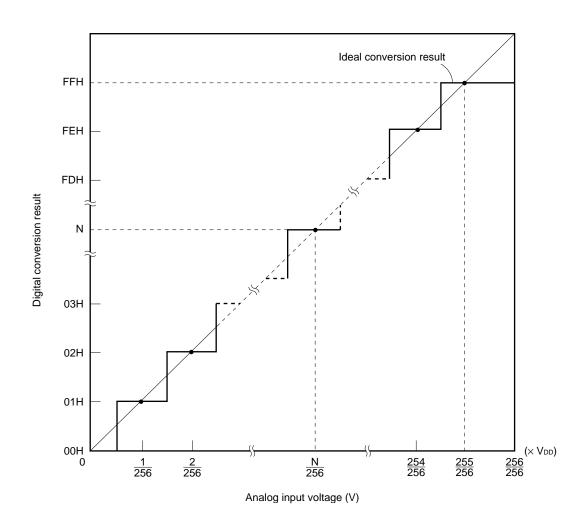

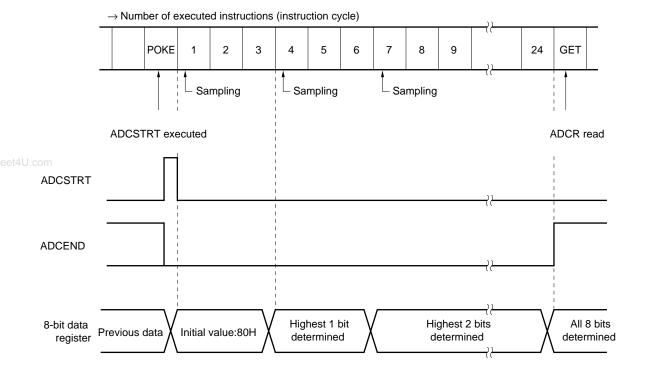

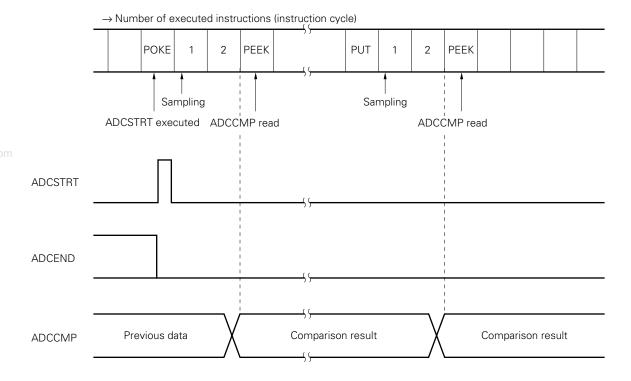

| 14.  | A/D CONVERTER                                  | 45   |

| 14.1 | Configuration of A/D Converter                 | 45   |

| 14.2 | Function of A/D Converter                      | 46   |

| 14.3 | Operation of A/D Converter                     | 47   |

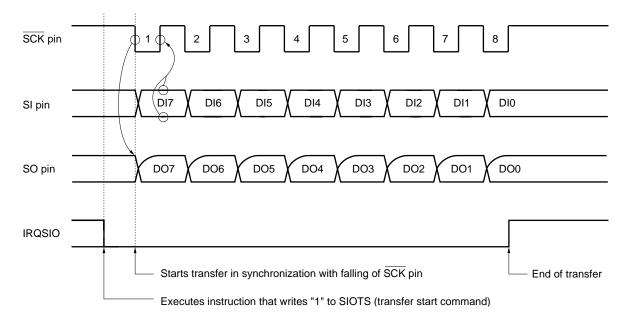

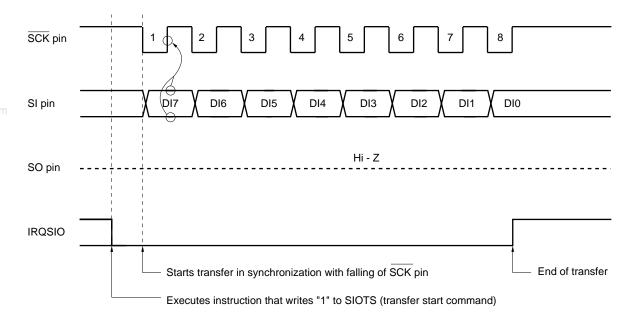

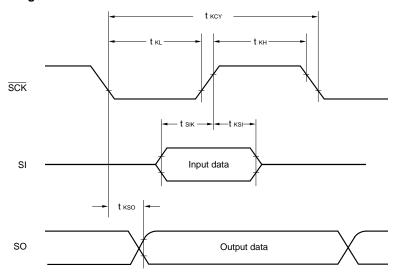

| 15.  | SERIAL INTERFACE (SIO)                         | 50   |

|      | Function of Serial Interface                   |      |

|      | Operation Mode of 3-Wire Serial Interface      |      |

|      |                                                |      |

|      | INTERRUPT FUNCTION                             |      |

|      | Types of Interrupt Causes and Vector Addresses |      |

| 16.2 | Hardware of Interrupt Control Circuit          | 55   |

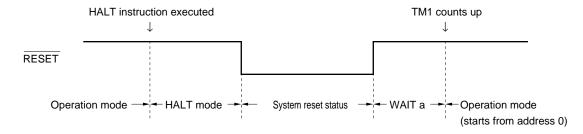

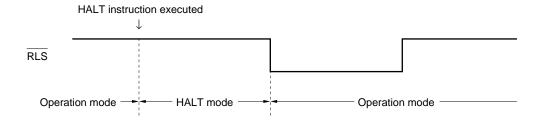

| 17.  | STANDBY FUNCTION                               | . 56 |

| 17.1 | Outline of Standby Function                    | 56   |

| 17.2 | HALT Mode                                      | 58   |

| 17.3 | STOP Mode                                      | 60   |

| 18.  | RESET                                          | 63   |

| 18.1 | Reset Function                                 | 63   |

|      | Reset Operation                                |      |

| 10   | POC CIRCUIT (MASK OPTION)                      | 65   |

|      | Function of POC Circuit                        |      |

|      | Conditions to Use POC Circuit                  |      |

|      |                                                |      |

|      | INSTRUCTION SET                                |      |

|      | Outline of Instruction Set                     |      |

|      | Legend                                         |      |

|      | Instruction Set                                |      |

| 20.4 | Assembler (AS17K) Embedded Macro Instruction   | 71   |

| 21.  | ASSEMBLER RESERVED WORDS                       | . 72 |

| 21.1 | Mask Option Directive                          | 72   |

| 21.2 | Reserved Symbols                               | 74   |

| 22.  | ELECTRICAL SPECIFICATIONS                      | 82   |

|      |                                                |      |

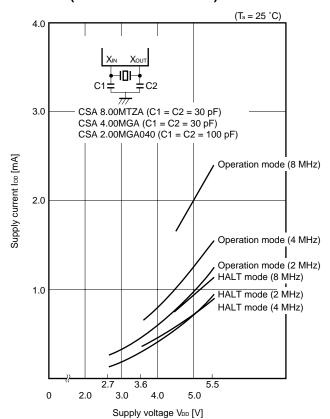

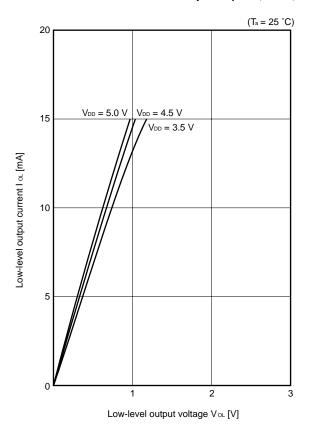

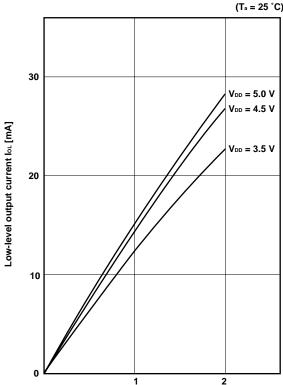

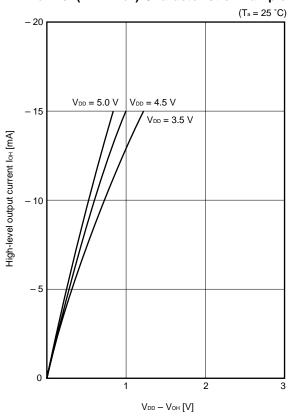

| 23.  | CHARACTERISTIC CURVE (REFERENCE VALUE)         | . 88 |

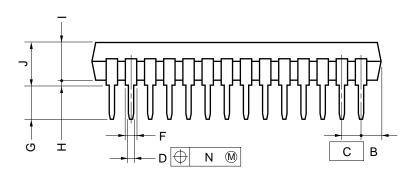

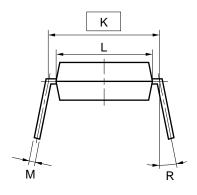

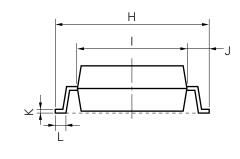

| 24. | PACKAGE DRAWINGS                                                                                | 90 |

|-----|-------------------------------------------------------------------------------------------------|----|

| 25. | RECOMMENDED SOLDERING CONDITIONS                                                                | 94 |

| APF | PENDIX A. FUNCTION COMPARISON BETWEEN $\mu$ PD17145 SUBSERIES AND THE $\mu$ PD17135A AND 17137A | 96 |

| APF | PENDIX B. DEVELOPMENT TOOLS                                                                     | 98 |

# 1. PIN

# 1.1. Pin Function

| ı | Pin Number           | Symbol                                                                         | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Output Format                                                                                                                                         | After Reset               |

|---|----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

|   | 1                    | V <sub>DD</sub>                                                                | Power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                                                                                                                                                     | _                         |

| n | 2                    | P0F1/VREF                                                                      | Reference voltage input to port 0F and A/D converter.  • Pull-up resistor can be connected by mask option.  • P0F1  • Bit 1 of 2-bit input port (P0F)  • VREF  • Reference voltage input pin of A/D converter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Input                                                                                                                                                 | Input (P0F <sub>1</sub> ) |

|   | 3 to 6               | P0C <sub>3</sub> /ADC <sub>3</sub><br>to<br>P0C <sub>0</sub> /ADC <sub>0</sub> | Analog input to port 0C and A/D converter.  • P0C <sub>3</sub> -P0C <sub>0</sub> • 4-bit I/O port  • Can be set in input or output mode bitwise.  • ADC <sub>3</sub> -ADC <sub>0</sub> • Analog inputs to A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | P0C <sub>3</sub> -P0C <sub>0</sub> • 4-bit I/O port  • Can be set in input or output mode bitwise.  ADC <sub>3</sub> -ADC <sub>0</sub> CMOS push-pull |                           |

|   | 7<br>8<br>9          | P0B <sub>3</sub><br>P0B <sub>2</sub><br>P0B <sub>1</sub><br>P0B <sub>0</sub>   | Port 0B.  • 4-bit I/O port  • Can be set in input or output mode in 4-bit units.  • Pull-up resistor can be connected in 4-bit units via software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CMOS push-pull                                                                                                                                        | Input                     |

|   | 11<br>12<br>13       | P0A <sub>3</sub><br>P0A <sub>2</sub><br>P0A <sub>1</sub>                       | Port 0A.  • 4-bit I/O port.  • Can be set in input or output mode in 4-bit units.  • Pull-up resistor can be connected in 4-bit units via software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMOS push-pull                                                                                                                                        | Input                     |

|   | 15<br>16<br>17<br>18 | P0E <sub>3</sub><br>P0E <sub>2</sub><br>P0E <sub>1</sub>                       | Port 0E.  • 4-bit I/O port.  • Can be set in input or output mode in 4-bit units.  • Pull-up resistor can be connected in 4-bit units via software.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | N-ch<br>open-drain                                                                                                                                    | Input                     |

|   | 19                   | P0D <sub>3</sub> /TM1OUT                                                       | Port 0D that is also used for timer 1 output, serial data input, serial data output, and serial clock I/O.  • Pull-up resistor can be connected bitwise via software.  • P0D <sub>3</sub> -P0D <sub>0</sub> • 4-bit I/O port.  • Can be set in input or output mode bitwise.  • TM10UT  • Timer 1 output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                       | Input (P0D)               |

|   | 20<br>21<br>22       | P0D <sub>2</sub> /SI<br>P0D <sub>1</sub> /SO<br>P0D <sub>0</sub> /SCK          | Solution Solution Solution Serial data output Solution S |                                                                                                                                                       |                           |

|              | Pin Number   | Symbol      | Function                                                                                                                                                                                  | Output Format | After Reset               |

|--------------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------------------|

|              | 23           | P0F₀/RLS    | Port 0F or standby mode release signal input.  • Pull-up resistor can be connected by mask option.  • R0F0  • Bit 0 of 2-bit input port (P0F)  • RLS  • Standby mode release signal input | Input         | Input (P0F <sub>0</sub> ) |

| www.DataShee | 24           | INT         | External interrupt request signal input. Also used to release standby mode.  • Pull-up resistor can be connected by mask option.                                                          | Input         | Input                     |

|              | 4U.com<br>25 | RESET       | System reset input.  • Pull-up resistor can be connected by mask option.                                                                                                                  | Input         | Input                     |

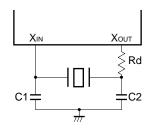

|              | 26<br>27     | Xout<br>Xin | For system clock oscillation. Connect ceramic resonator across X <sub>IN</sub> and X <sub>OUT</sub> .                                                                                     | _             | _                         |

| 1            | 28           | GND         | GND                                                                                                                                                                                       | _             | _                         |

# 1.2 Equivalent Circuit of Pin

The input/output circuit of each pin is shown below, partially simplified.

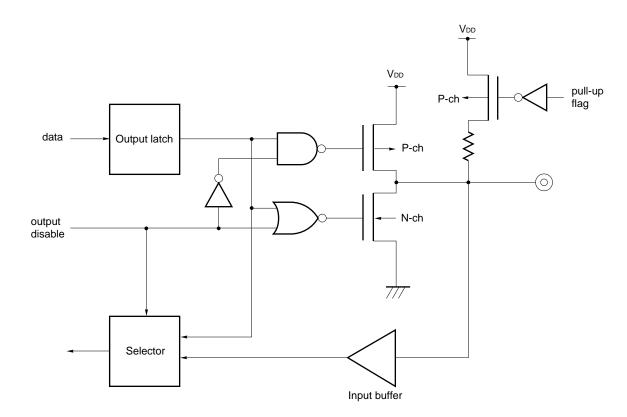

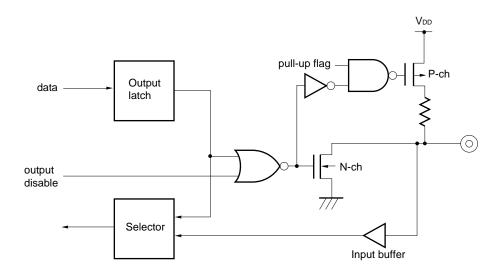

# (1) P0Ao to P0A3 and P0Bo to P0B3

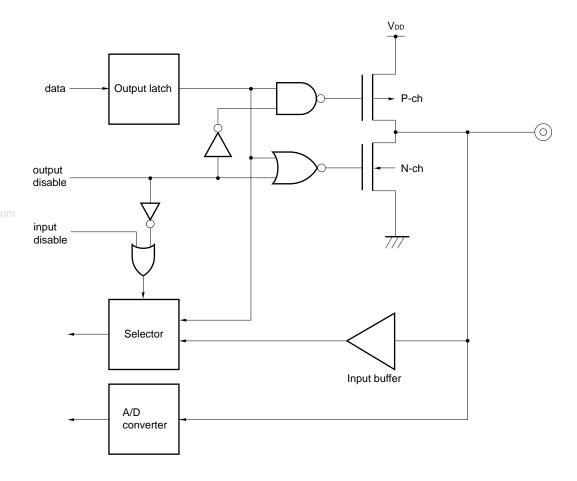

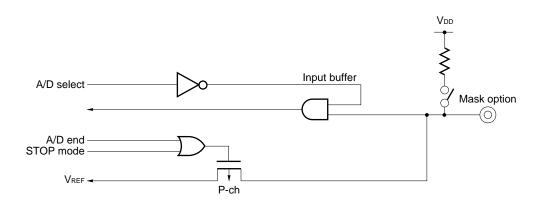

# (2) POC<sub>0</sub>/ADC<sub>0</sub> to POC<sub>3</sub>/ADC<sub>3</sub>

# (3) P0D<sub>3</sub>/TM1OUT and P0D<sub>1</sub>/SO

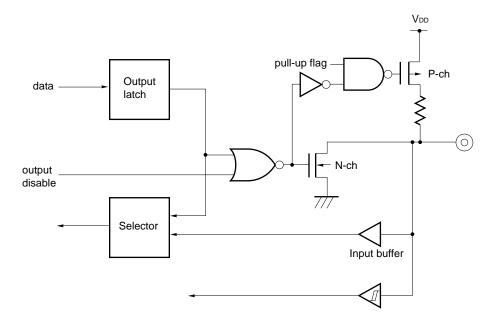

# (4) P0D<sub>2</sub>/SI and P0D<sub>0</sub>/SCK

# (5) P0E<sub>0</sub> to P0E<sub>3</sub>

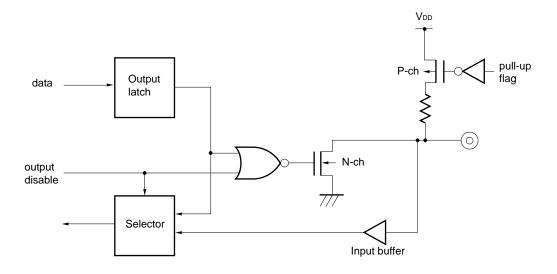

# (6) P0F<sub>0</sub>/RLS

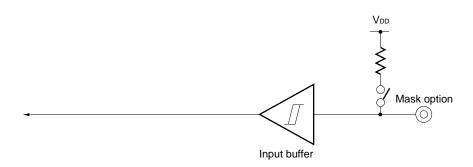

# (7) P0F1/VREF

ww.DataSheet4U.com

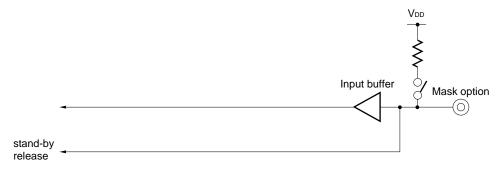

# (8) RESET and INT

## 1.3 Handling of Unused Pins

Handle unused pins as shown in the table below.

Table 1-1. Handling of Unused Pins

|      | Pin Name                                                                                             |                               | Handling                                                                    |                                                                                                       |  |                                             |

|------|------------------------------------------------------------------------------------------------------|-------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--|---------------------------------------------|

|      |                                                                                                      | i iii ivallie                 | Internally                                                                  | Externally                                                                                            |  |                                             |

|      | POA, POB, POD, POE                                                                                   |                               | Connect on-chip pull-up resistor via software.                              | Open                                                                                                  |  |                                             |

|      |                                                                                                      | POC                           | _                                                                           | Connect to V <sub>DD</sub> via pull-up resistor, or to GND via pull-down resistor <sup>Note 1</sup> . |  |                                             |

| n    | Input<br>mode                                                                                        | P0F <sub>1</sub>              | Do not connect on-chip pull-up resistor by mask option.                     | Directly connect to V <sub>DD</sub> or GND.                                                           |  |                                             |

|      |                                                                                                      | 1 01 1                        | Connect on-chip pull-up resistor by mask option.                            | Open                                                                                                  |  |                                             |

| Port |                                                                                                      | P0F <sub>0</sub> Note 2       | Do not connect on-chip pull-up resistor by mask option.                     | Directly connect to GND.                                                                              |  |                                             |

|      |                                                                                                      | P0A, P0B, P0C (CMOS port)     | _                                                                           |                                                                                                       |  |                                             |

|      | Output                                                                                               | P0D<br>(N-ch open-drain port) | Output low level.                                                           | Open                                                                                                  |  |                                             |

|      |                                                                                                      | P0E                           | Do not connect pull-up on-chip resistor via software, but output low level. | open .                                                                                                |  |                                             |

|      |                                                                                                      | (N-ch open-drain port)        | Connect on-chip pull-up resistor via software and output high level.        |                                                                                                       |  |                                             |

|      | by mask option.  Connect on-chip pull-up resistor by mask option.  RESETNote 3  by mask option.  Ope |                               | by ma                                                                       |                                                                                                       |  | Directly connect to V <sub>DD</sub> or GND. |

|      |                                                                                                      |                               | , , , , , , , , , , , , , , , , , , , ,                                     | Open                                                                                                  |  |                                             |

|      |                                                                                                      |                               | by mask option.                                                             | Directly connect to Vpb.                                                                              |  |                                             |

|      |                                                                                                      |                               |                                                                             |                                                                                                       |  |                                             |

- Notes 1. Take into consideration the drive capability and current dissipation of a port when the port is externally pulled up or down. To pull up or down the port with a high resistance, exercise care so that noise is not superimposed on the port pin. The appropriate value of the pull-up or pulldown resistor differs depending on the application circuit. Generally, select a resistor of several 10 k $\Omega$ .

- 2. The P0F<sub>0</sub>/RLS pin is also used to set a test mode. When this pin is not used, do not connect a pull-up resistor to it by mask option, but directly connect it to GND.

- 3. In an application circuit where a high reliability is required, be sure to input the RESET signal from an external source. The RESET pin is also used to set a test mode. When this pin is not used, directly connect it to VDD.

Caution It is recommended to fix the input/output mode, pull-up resistor by software, and the output level of the pin by repeatedly setting them in each loop of the program.

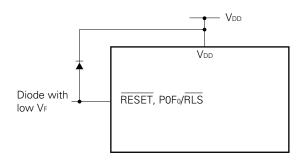

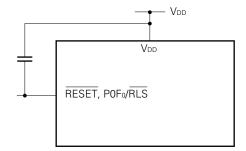

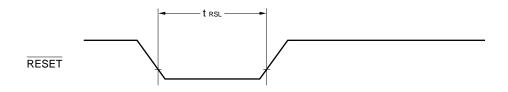

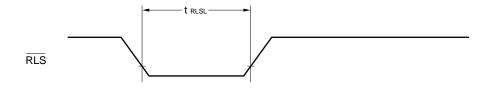

# 1.4 Note on Using RESET and P0F<sub>0</sub>/RLS Pins

The  $\overline{\text{RESET}}$  and P0F<sub>0</sub>/ $\overline{\text{RLS}}$  pins also have a function to set a test mode in which the internal operation of the  $\mu$ PD17149(A1) is tested (for IC test only), in addition to the function described in **1.1 Pin Function**.

If a voltage higher than VDD is applied to these pins, the test mode is set. If a noise higher than VDD is superimposed on these pins during normal operation, therefore, the test mode is set by mistake, affecting normal operation.

If the wiring length of the  $\overline{RESET}$  or  $P0F_0/\overline{RLS}$  pin is too long, for example, noise may be superimposed on the pin.

To prevent this, the wiring length must be kept as short as possible. Otherwise, use a diode or capacitor as shown below

# www.DataSheet4U.com Connect a low-V<sub>F</sub> diode between V<sub>DD</sub> and RESET, P0F<sub>0</sub>/RLS

# ○ Connect a capacitor between VDD and RESET, P0Fo/RLS

## 2. PROGRAM MEMORY (ROM)

Table 2-1 shows the program memory configuration of the μPD17145(A1), 17147(A1), and 17149(A1).

**Table 2-1. Program Memory Configuration**

| Part Number  | Program Memory Capacity | Program Memory Address |

|--------------|-------------------------|------------------------|

| μPD17145(A1) | 2 KB (1024 × 16 bits)   | 0000H-03FFH            |

| μPD17147(A1) | 4 KB (2048 × 16 bits)   | 0000H-07FFH            |

| μPD17149(A1) | 8 KB (4096 × 16 bits)   | 0000H-0FFFH            |

The program memory stores programs and constant data tables.

The program memory is addressed by the program counter.

Addresses 0000H-0005H are allocated to a reset start address and various interrupt vector addresses.

# 2.1 Configuration of Program Memory

Figure 2-1 shows the program memory map. The program memory is divided in units called "pages" each of which consists of 2K steps with one step made up of 16 bits.

Addresses 0000H-07FFH (page 0) of the program memory can be specified by the direct subroutine call instruction. The entire address range of the program memory, 0000H-0FFFH, can be specified by the branch, indirect subroutine call, and table reference instructions.

Address 0000H Reset start address 0001H Serial interface interrupt vector 0002H Basic interval timer interrupt vector BR addr instruction 0003H branch address Timer 1 interrupt vector BR @AR instruction 0004H Timer 0 interrupt vector CALL addr branch address instruction subroutine Page 0 0005H External (INT) interrupt vector entry address CALL @AR instruction subroutine entry address MOVT DBF. @AR instruction (With μPD17145(A1)) table reference address 03FFH (With  $\mu$ PD17147(A1)) 07FFH Page 1 (With  $\mu$ PD17149(A1)) 0FFFH 16 bits

Figure 2-1. Program Memory Map

## 3. PROGRAM COUNTER (PC)

The program counter is used to address the program memory.

## 3.1 Configuration of Program Counter

The program counter is a 10-/11-/12-bit binary counter as shown in Figure 3-1.

MSB LSB PC2 PC11 PC10 PC9 PC8 PC7 PC6 PC5 PC4 PC3 PC1 PC<sub>0</sub> PC (μPD17145(A1)) PC (μPD17147(A1))-PC (μPD17149(A1))

Figure 3-1. Program Counter

3.2 Operation of Program Counter

Usually, the contents of the program counter are automatically incremented each time an instruction has been executed. When reset has been effected, when a branch, subroutine call, return, or table reference instruction has been executed, or when an interrupt has been acknowledged, the address of the program memory to be executed next is set to the program counter.

Bit of Program Counter Value of Program Counter PC11 PC10 PC9 PC8 PC3 PC0 Instruction PC7 PC6 PC5 PC4 PC2 PC1 At reset 0 0 0 0 O n 0 0 0 0 0 BR addr 1 Value specified by addr

Contents of address register (AR)

Vector address of each interrupt

0

Figure 3-2. Value of Program Counter after Instruction Execution

**Remark** The  $\mu$ PD17145(A1) does not have PC11 and PC10. The  $\mu$ PD17147(A1) does not have PC11.

Contents of address stack indicated by stack pointer (return address)

www.DataSheet4U.com

CALL addr

BR @AR CALL @AR

RET RETSK

RETI

(MOVT DBF, @AR)

When interrupt is acknowledged

#### 4. STACK

The stack is a register to which the return address of the program or the contents of the system registers, which are described later, are saved when a subroutine call instruction is executed or when an interrupt is acknowledged.

# 4.1 Configuration of Stack

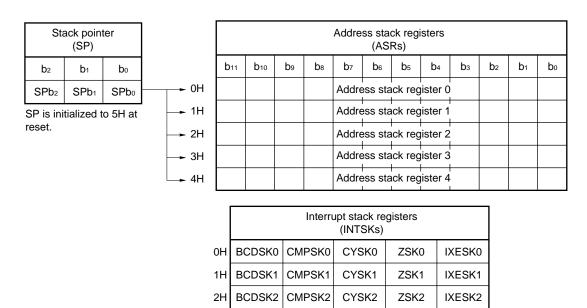

Figure 4-1 shows the configuration of the stack.

The stack consists of a 3-bit binary counter, stack pointer (SP), five 10-bit ( $\mu$ PD17145(A1)), 11-bit ( $\mu$ PD17147(A1)), or 12-bit ( $\mu$ PD17149(A1)) address stack registers (ASRs), and three 5-bit interrupt stack registers (INTSKs).

/w.DataSheet4U.com

Figure 4-1. Configuration of Stack

# 4.2 Stack Function

The stack is used to save a return address when the subroutine call or table reference instruction is executed. When an interrupt is acknowledged, the return address of the program and the contents of the program status word (PSWORD) are automatically saved to the stack. After they are saved to the stack, all the bits of PSWORD are cleared to 0.

## 5. DATA MEMORY (RAM)

The data memory is used to store data for operation and control. Data can always be written to or read from this memory by using an instruction.

# 5.1 Configuration of Data Memory

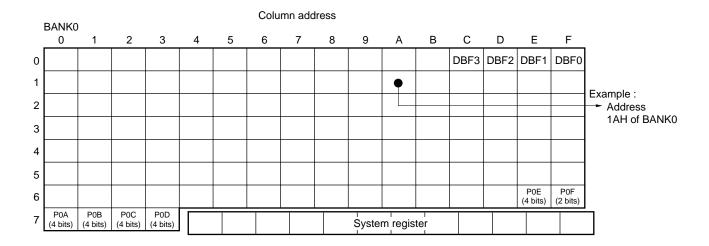

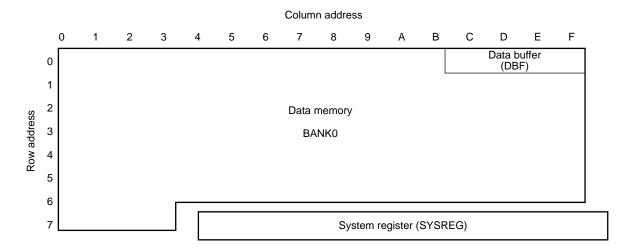

The data memory is assigned addresses each consisting of 7 bits. The higher 3 bits of an address are called a "row address", while the lower 4 bits are called a "column address".

Take address 1AH for example. The row address of this address is 1H and the column address is 0AH. One address consists of 4 bits (= 1 nibble) of memory.

The data memory consists of an area to which the user can save data, and areas to which special functions www.DataSheelareallocated in advance. These areas are:

• System register (SYSREG) (Refer to 7. SYSTEM REGISTER (SYSREG).)

• Data buffer (DBF) (Refer to 9. DATA BUFFER (DBF).)

• Port register (Refer to 11. PORT.)

Figure 5-1. Configuration of Data Memory

## 6. GENERAL REGISTER (GR)

As its name implies, the general register is used for general purposes such as data transfer and operation. The general register of the 17K series is not a fixed area, but an area specified on the data memory by using the general register pointer (RP). Therefore, a part of the data memory area can be specified as a general register as necessary, so that data can be transferred between data memory areas and the data in the data memory can be operated with a single instruction.

# 6.1 General Register Pointer (RP)

0 0

Reset

0 0 0

RP is a pointer that specifies part of the data memory as the general register. RP specifies the bank and row addresses of a data memory area that is to be specified as the general register. Consisting of a total of www.DataSheet4U.com 7 bits, RP is assigned to 7DH (RPH) and 7EH (RPL), and the higher 3 bits of the system register (refer to 7. SYSTEM REGISTER (SYSREG)).

RPH specifies a bank, and RPL specifies a data memory row address.

Column address BANK0 С E F 0 1 General register 2 General register (16 nibbles) area when Row addresses RPH = 0000B,0H to 7H can be  $RPL = 010 \times B$ 3 Row specified by address general register 4 pointer (RP). 5 6 System register RP 7 Address 7DH 7EH General register Name pointer (RP) Symbol **RPH RPL** bз b<sub>1</sub> Bit bз  $b_2$ b<sub>1</sub>  $b_0$  $b_2$ bο В С Data 0 0 0 D 0

Figure 6-1. Configuration of General Register Pointer

## 7. SYSTEM REGISTER (SYSREG)

The system register (SYSREG) is a register that directly controls the CPU, and is located on the data memory.

# 7.1 Configuration of System Register

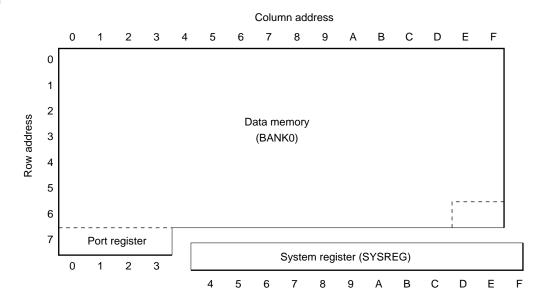

Figure 7-1 shows the location of the system register on the data memory. As shown in this figure, the system register is located at addresses 74H-7FH of the data memory.

Because the system register is located on the data memory, it can be manipulated by all the data memory manipulation instructions. It is therefore possible to specify the system register as a general register.

Figure 7-1. Location of System Register on Data Memory

w.DataSheet4U.com

Figure 7-2 shows the configuration of the system register. As shown in this figure, the system register consists of the following seven registers:

| Address register                             | (AR)     |

|----------------------------------------------|----------|

| Window register                              | (WR)     |

| Bank register                                | (BANK)   |

| Index register                               | (IX)     |

| Data memory row address pointer              | (MP)     |

| <ul> <li>General register pointer</li> </ul> | (RP)     |

| Program status word                          | (PSWORD) |

Address 74H 75H 76H 79H 7AH 7BH 7CH 7DH 7EH 7FH 77H 78H Index register Program (IX) General register Window Bank Address register status pointer Name register register Data memory word (AR) (WR) (BANK) (RP) (PSWORD) row address pointer (MP) IXH IXM Symbol AR3 AR2 AR1 AR0 WR IXL RPH **RPL PSW** BANK MPH MPL Bit 0 0 0 0 M 0 0 0 0 B C C Data<sup>Note1</sup> 0 0 0 0 Note2 0 0 0 0 CMYZX DΡ (BANK) Е E (MP) (RP) (AR) Initial Undefi-ned

Figure 7-2. Configuration of System Register

- Notes 1. 0 in this field means that the bit is "fixed to 0".

- b<sub>3</sub> and b<sub>2</sub> of AR2 of the  $\mu$ PD17145(A1) are fixed to 0. b<sub>3</sub> of AR2 of the  $\mu$ PD17147(A1) is fixed to

## 8. REGISTER FILE (RF)

The register file is a register that mainly sets the conditions of the peripheral hardware.

# 8.1 Configuration of Register File

# 8.1.1 Configuration of register file

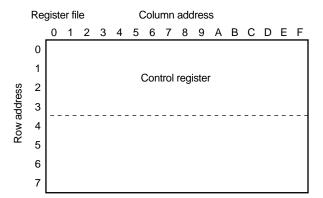

Figure 8-1 shows the configuration of the register file.

As shown in this figure, the register file consists of 128 nibbles (128 × 4 bits). Like the data memory, the register file is assigned addresses in 4-bit units, with row addresses 0H-7H and column addresses 0H-0FH. Addresses 00H-3FH of the register file are called a control register.

ww.DataSheet4U.com

Figure 8-1. Configuration of Register File

# 8.1.2 Register file and data memory

Figure 8-2 shows the relationships between the register file and data memory.

As shown in this figure, addresses 40H to 7FH of the register file overlaps the data memory.

It seems from the program as if addresses 40H to 7FH of the data memory exist at addresses 40H-7FH of the register file.

Column address 0 1 Data memory 2 Row address 3 4 5 6 BANK0 Port register System register 0 1 Control register 2 3

Figure 8-2. Relationships between Register File and Data Memory

# 8.2 Function of Register File

# 8.2.1 Function of register file

The register file is a collection of registers that set the conditions of the peripheral hardware by using the PEEK or POKE instruction.

The registers that control the peripheral hardware are allocated to addresses 00H-3FH. These registers are called control registers.

Addresses 40H-7FH of the register file overlap the ordinary data memory. These addresses can therefore be read or written by not only the MOV instruction but also the PEEK and POKE instructions.

#### 8.2.2 Functions of control registers

The control registers are used to set the conditions of the peripheral hardware listed below.

For the details of the peripheral hardware and control registers, refer to the description of each peripheral hardware.

- Port

- 8-bit timers/counters (TM0, TM1)

- Basic interval timer (BTM)

- A/D converter

- Serial interface (SIO)

- · Interrupt function

- · Stack pointer (SP)

## 9. DATA BUFFER (DBF)

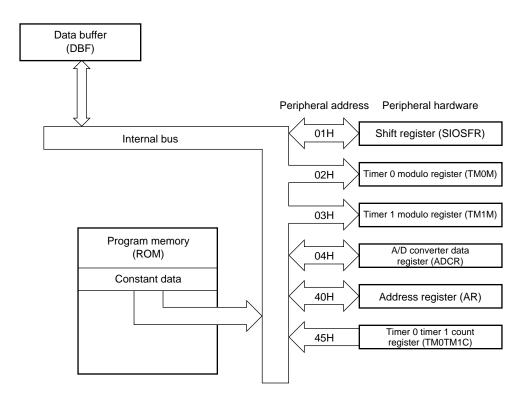

The data buffer consists of 4 nibbles allocated to addresses 0CH-0FH of BANK0 of the data memory.

This area is a data storage area that transfers data with the peripheral hardware of the CPU (address register, serial interface, timers 0 and 1, and A/D converter) by using the GET or PUT instruction. Moreover, the constants on the program memory can be read to the data buffer by using the MOVT DBF, @AR instruction.

## 9.1 Configuration of Data Buffer

Figure 9-1 shows the location of the data buffer on the data memory.

As shown in this figure, the data buffer is allocated addresses 0CH-0FH of the data memory, and consists of a total of 16 bits or 4 nibbles ( $4 \times 4$  bits).

w DataSheet4LLcom

Figure 9-1. Location of Data Buffer

Figure 9-2 shows the configuration of the data buffer. As shown in this figure, the data buffer consists of 16 bits of the data memory, with the bit 0 of address 0FH as the LSB and bit 3 of address 0CH as the MSB.

0CH 0DH 0EH 0FH Address Data memory BANK0 Bit b<sub>1</sub>  $b_0 \\$ b<sub>1</sub>  $b_0$  $b_2$  $b_0$ bз  $b_2$ b<sub>1</sub>  $b_0$  $b_2$ b<sub>14</sub> **b**13 b<sub>9</sub> b<sub>8</sub> b<sub>7</sub>  $b_6$  $b_2$  $b_1$  $b_0$ Bit **b**15 **b**12 b11 **b**10 b<sub>5</sub>  $b_4$ bз Data buffer DBF3 DBF2 DBF1 DBF0 Symbol Λ Μ L S B V S B V Data Data

Figure 9-2. Configuration of Data Buffer

Because the data buffer is located on the data memory, it can be manipulated by all the data memory manipulation instructions.

#### 9.2 Function of Data Buffer

The data buffer has two main functions.

One is to transfer data with the peripheral hardware, and the other is to read the constant data on the program memory (table reference). Figure 9-3 shows the relationships between the data buffer and peripheral hardware.

Figure 9-3. Data Buffer and Peripheral Hardware

#### 10. ALU BLOCK

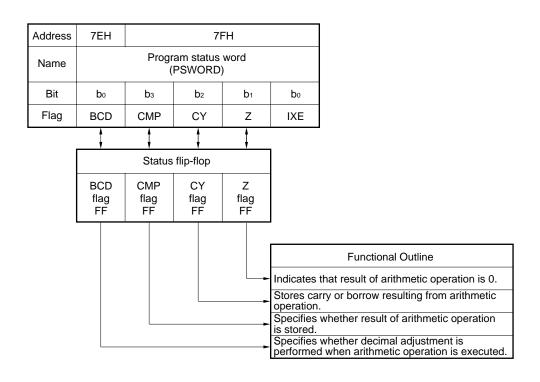

The ALU executes arithmetic and logical operations, bit judgment, and rotation processing of 4-bit data.

# 10.1 Configuration of ALU Block

Figure 10-1 shows the configuration of the ALU block.

As shown, the ALU block consists of an ALU that processes 4-bit data, and peripheral circuits such as temporary registers A and B, status flip-flops that control the status of the ALU, and a decimal adjustment circuit that is used when a BCD operation is performed.

The status flip-flops are a zero flag FF, carry flag FF, compare flag FF, and BCD flag FF, as shown in Figure 10-1.

www.DataSheet4UThe status flip-flops correspond to the zero flag (Z), carry flag (CY), compare flag (CMP), and BCD flag (BCD) of the program status word (PSWORD: addresses 7EH, 7FH) on a one-to-one basis.

Temporary register

A

ALU

Arithmetic operation

Logical operation

Bit judgment

Compare judgment

Rotation processing

Decimal adjustment circuit

Figure 10-1. Configuration of ALU Block

ww DataSheet4U con

#### 11. PORTS

# 11.1 Port 0A (P0A<sub>0</sub>, P0A<sub>1</sub>, P0A<sub>2</sub>, P0A<sub>3</sub>)

Port 0A is a 4-bit I/O port with an output latch. It is mapped at address 70H of BANK0 of the data memory. The output format is CMOS push-pull output.

This port can be set in the input or output mode in 4-bit units. The input or output mode is specified by P0AGIO (bit 0 of address 2CH) on the register file.

When P0AGIO = 0, all the pins of port 0A are set in the input mode. When an instruction that reads the data of the port register is executed at this time, the pin status is read.

When POAGIO = 1, all the pins of port 0A are set in the output mode, and the contents written to the output latch are output to the pins. When an instruction that reads the port status is executed with the port set in the output mode, the contents of the output latch, instead of the pin status, are read.

A pull-up resistor can be connected on-chip to this port through software. Whether the pull-up resistor is connected is specified by P0AGPU (bit 0 at address 0CH) of the register file. All the four pins are pulled up when P0AGPU = 1. When P0AGPU = 0, the pull-up resistor is not connected.

P0AGIO and P0AGPU are cleared to "0" at reset, and all the P0A pins are set in the input mode without the pull-up resistor connected. The value of the output latch is also cleared to "0".

P0AGIO

Input/Output

BANK0 70H

RF: 2CH, bit 0

Mode of Pin

Write

Read

0

Input

Enabled

P0A pin status

1

Output

Write to P0A latch

P0A latch contents

Table 11-1. Writing and Reading Port Register (0.70H)

## 11.2 Port 0B (P0B<sub>0</sub>, P0B<sub>1</sub>, P0B<sub>2</sub>, P0B<sub>3</sub>)

Port 0B is a 4-bit I/O port with an output latch. It is mapped at address 71H of BANK0 of the data memory. The output format is CMOS push-pull output.

This port can be set in the input or output mode in 4-bit units. The input or output mode is specified by P0BGIO (bit 1 of address 2CH) on the register file.

When P0BGIO = 0, all the pins of port 0B are set in the input mode. When an instruction that reads the data of the port register is executed at this time, the pin status is read.

When P0BGIO = 1, all the pins of port 0B are set in the output mode, and the contents written to the output latch are output to the pins. When an instruction that reads the port status is executed with the port set in the output mode, the contents of the output latch, instead of the pin status, are read.

A pull-up resistor can be connected on-chip to this port through software. Whether the pull-up resistor is comconnected is specified by P0BGPU (bit 1 at address 0CH) of the register file. All the four-bit pins are pulled up when P0BGPU = 1. When P0BGPU = 0, the pull-up resistor is not connected.

P0BGIO and P0BGPU are cleared to "0" at reset, and all the P0B pins are set in the input mode without the pull-up resistor connected. The value of the output latch is also cleared to "0".

P0BGIO Input/Output BANK0 71H

RF: 2CH, bit 1 Mode of Pin Write Read

0 Input Enabled P0B pin status

1 Output Write to P0B latch P0B latch contents

Table 11-2. Writing and Reading Port Register (0.71H)

## 11.3 Port 0C (P0C<sub>0</sub>/ADC<sub>0</sub>, P0C<sub>1</sub>/ADC<sub>1</sub>, P0C<sub>2</sub>/ADC<sub>2</sub>, P0C<sub>3</sub>/ADC<sub>3</sub>)

Port 0C is a 4-bit I/O port with an output latch. It is mapped at address 72H of BANK0 of the data memory. The output format is CMOS push-pull output.

This port can be set in the input or output mode in 1-bit units. The input or output mode is specified by P0CBIO0-P0CBIO3 (address 1CH) on the register file.

When POCBIOn = 0 (n = 0 to 3), the corresponding port pin, POCn, is set in the input mode. When an instruction that reads the data of the port register is executed at this time, the pin status is read. When POCBIOn = 1 (n = 0 to 3), the POCn pin is set in the output mode, and the contents written to the output latch are output to the pin. When an instruction that reads the port status is executed with a port pin set in the output mode, the contents of the output latch, instead of the pin status, are read.

At reset, P0CBIO0-P0CBIO3 are cleared to "0", setting all the P0C pins in the input mode. The contents of the output latch are also cleared to "0" at this time.

Port 0C is also used to input analog voltages to the A/D converter. Whether each pin of the port is used as a port pin or analog input pin is specified by P0C0IDI-P0C3IDI (address 1BH) on the register file.

When P0CnIDI = 0 (n = 0-3), the P0Cn/ADCn pin functions as a port pin. When P0CnIDI = 1 (n = 0 to 3), the P0Cn/ADCn pin functions as an analog input pin of the A/D converter. If any of the P0CnIDI (n = 0 to 3) bits is set to "1", the P0F1/VREF pin is used as the VREF pin.

When a pin of port 0C is used as an analog input pin of the A/D converter, set the P0CnIDI corresponding to the pin to which an analog voltage is applied to 1, to disable the port input function. Moreover, clear P0CBIOn (n = 0-3) to 0 to set the input port mode. The pin used as an analog input pin is selected by ADCCH0 and ADCCH1 (bits 1 and 0 of address 22H) on the register file.

At reset, P0CBIO0-P0CBIO3, P0C0IDI-P0C3IDI, ADCCH0, and ADCCH1 are cleared to 0, setting the input port mode.

|         |         |                                           |                    | (11 = 0 to 3)         |

|---------|---------|-------------------------------------------|--------------------|-----------------------|

| P0CnIDI | P0CBIOn | Function                                  | BANK               | 0 72H                 |

| RF:1BH  | RF:1CH  | T dilotion                                | Write              | Read                  |

| 0       | 0       | Input port                                | Enabled. P0C latch | Pin status            |

| 0       | 1       | Port output                               | Enabled. P0C latch | Contents of P0C latch |

|         | 0       | Analog input of A/DNote 1                 | Enabled. P0C latch | Contents of P0C latch |

| 1       | 1       | Output port and analog input of A/DNote 2 | Enabled. P0C latch | Contents of P0C latch |

Table 11-3. Selecting Port or A/D Converter Mode

(n = 0 to 3)

Notes 1. Normal setting when the POC pins are used as the analog input pins of the A/D converter.

The POC pins function as output port pins. At this time, the analog input voltages change with the output from the port. To use the pins as analog input pins, be sure to clear POCBIOn to 0.

# 11.4 Port 0D (P0D<sub>0</sub>/SCK, P0D<sub>1</sub>/SO, P0D<sub>2</sub>/SI, P0D<sub>3</sub>/TM1OUT)

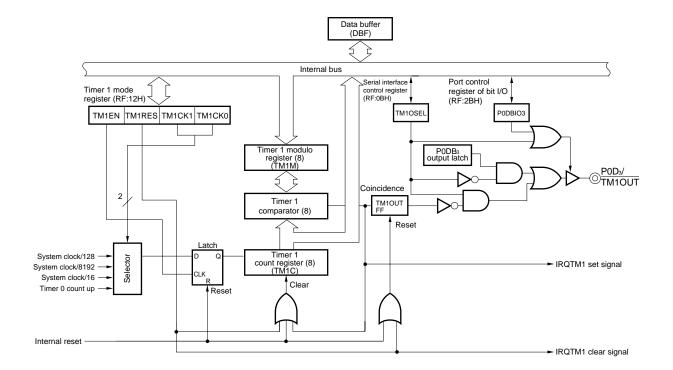

Port 0D is a 4-bit I/O port with an output latch. It is mapped at address 73H of BANK0 of the data memory. The output format is N-ch open-drain output.

This port can be set in the input or output mode in 1-bit units. The input or output mode is specified by P0DBIO0-P0DBIO3 (address 2BH) on the register file.

When P0DBIOn = 0 (n = 0 to 3), the corresponding port pin, P0Dn, is set in the input mode. When an instruction that reads the data of the port register is executed at this time, the pin status is read. When P0DBIOn = 1, the P0Dn pin is set in the output mode, and the contents written to the output latch are output to the pin. When an instruction that reads the port status is executed with a port pin set in the output mode, the contents of the output latch, instead of the pin status, are read.

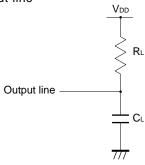

A pull-up resistor can be connected on-chip to this port through software. Whether the pull-up resistor is connected or not is specified bitwise by using P0DBPU0-P0DBPU3 (address 0DH) on the register file. When P0DBPUn = 1, the P0Dn pin is pulled up. When P0DBPUn = 0, the pull-up resistor is not connected.

At reset, P0DBIOn is cleared to "0", setting all the P0D pins in the input mode. The contents of the output latch are also cleared to "0" at this time. Note that the contents of the output latch are not changed even if the status of P0DBIOn is changed from "1" to "0".

Port 0D is also used as serial interface input/output and timer 1 output pins. Whether the P0Do to P0Do pins are used as port pins or serial interface I/O pins (SCK, SO, and SI) is specified by SIOEN (bit 0 of 0BH) on the register file. Whether the P0D3 pin is used as a port pin or timer 1 output (TM1OUT) pin is specified by TM1OSEL (bit 3 of 0BH) on the register file. If TM1OSEL = 1, "1" is output when timer 1 is reset, and the output is inverted each time the count value of timer 1 coincides with the contents of the modulo register.

Table 11-4. Contents of Register File and Pin Function

(n = 0 to 3)

| Value of Register File |         | Pin Function |             |                      |                      |                          |    |            |

|------------------------|---------|--------------|-------------|----------------------|----------------------|--------------------------|----|------------|

| TM1OSEL                | SIOEN   | P0DBIOn      |             |                      |                      |                          |    |            |

| RF: 0BH                | RF: 0BH | RF: 2BH      | P0D₀/SCK    | P0D <sub>1</sub> /SO | P0D <sub>2</sub> /SI | P0D <sub>3</sub> /TM1OUT |    |            |

| Bit 3                  | Bit 0   | Bit n        |             |                      |                      |                          |    |            |

|                        | 0       | 0            | Input port  |                      |                      |                          |    |            |

| 0                      |         | 1            | Output port |                      |                      |                          |    |            |

| U                      | 1       | 0            | SCK         | so                   | 80                   | <b>S</b> O               | SI | Input port |

|                        | _       | 1            | 3010        |                      | OI .                 | Output port              |    |            |

|                        | 0       | 0            | Input port  |                      |                      |                          |    |            |

| 1                      |         | 1            | Output port |                      | TM1OUT               |                          |    |            |

| •                      | 1       | 0            | SCK         | 80                   | C.I                  | TIMITOOT                 |    |            |

|                        | 1       | 1            | JUN         | SO                   | SI                   |                          |    |            |

| Port Mode   |                                         | Read Contents of Port Register (0.73H) |

|-------------|-----------------------------------------|----------------------------------------|

| Input port  |                                         | Pin status                             |

| Output port |                                         | Contents of output latch               |

| SCK         | Internal clock selected as serial clock | Contents of output latch               |

|             | External clock selected as serial clock | Pin status                             |

| SI          |                                         | Pin status                             |

| so          |                                         | Contents of output latch               |

| TM1OUT      |                                         | Contents of output latch               |

Table 11-5. Read Contents of Port Register (0.73H)

#### DataShee 11.5 Port 0E (P0E<sub>0</sub>, P0E<sub>1</sub>, P0E<sub>2</sub>, P0E<sub>3</sub>)

Port 0E is a 4-bit I/O port with an output latch. It is mapped at address 6EH of BANK0 of the data memory. The output format is N-ch open-drain output.

This port can be set in the input or output mode in 4-bit units. The input or output mode is specified by P0EGIO (bit 2 of address 2CH) on the register file.

When P0EGIO = 0, all the pins of port 0E are set in the input mode. When an instruction that reads the data of the port register is executed at this time, the pin status is read.

When P0EGIO = 1, all the pins of port 0E are set in the output port, and the contents written to the output latch are output to the pins. When an instruction that reads the port status is executed with the port set in the output mode, the contents of the output latch, instead of the pin status, are read.

A pull-up resistor can be connected on-chip to this port through software. Whether the pull-up resistor is connected is specified by P0EGPU (bit 2 at address 0CH) of the register file. All the four-bit pins are pulled up when P0EGPU = 1. When P0EGPU = 0, the pull-up resistor is not connected.

P0EGIO is cleared to "0" at reset, and all the P0E pins are set in the input mode. The value of the output latch is also cleared to "0".

P0EGIO Input/Output BANK0 6EH

RF: 2CH, bit 2 Mode of Pin Write Read

0 Input Enabled P0E pin status

1 Output Write to P0E latch P0E latch contents

Table 11-6. Writing and Reading Port Register (0.6EH)

### (n = 0 to 3)

# 11.6 Port 0F (P0F<sub>0</sub>/RLS, P0F<sub>1</sub>/V<sub>REF</sub>)

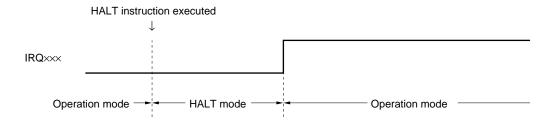

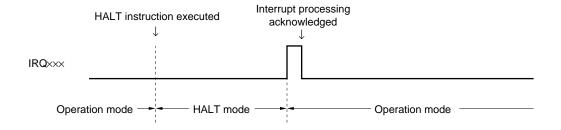

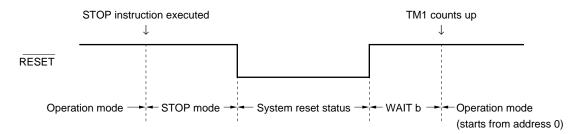

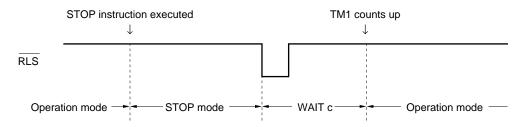

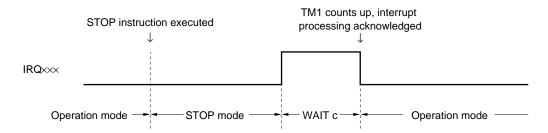

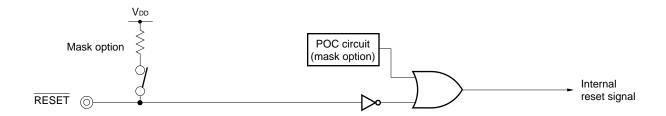

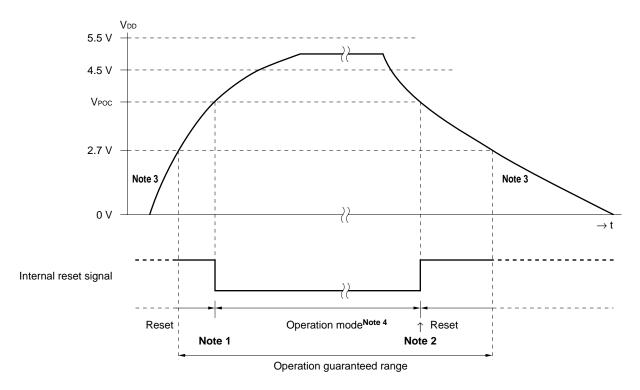

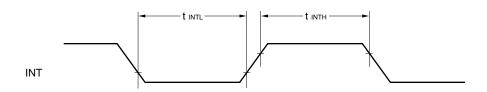

Port 0F is a 2-bit input port and mapped at address 6FH of BANK0 of the data memory. A pull-up resistor can be connected on-chip bitwise to this port by mask option.