### DATA SHEET

# μ**PD78363A,78365A,78366A,78368A**

## **16/8-BIT SINGLE-CHIP MICROCONTROLLERS**

#### DESCRIPTION

EC

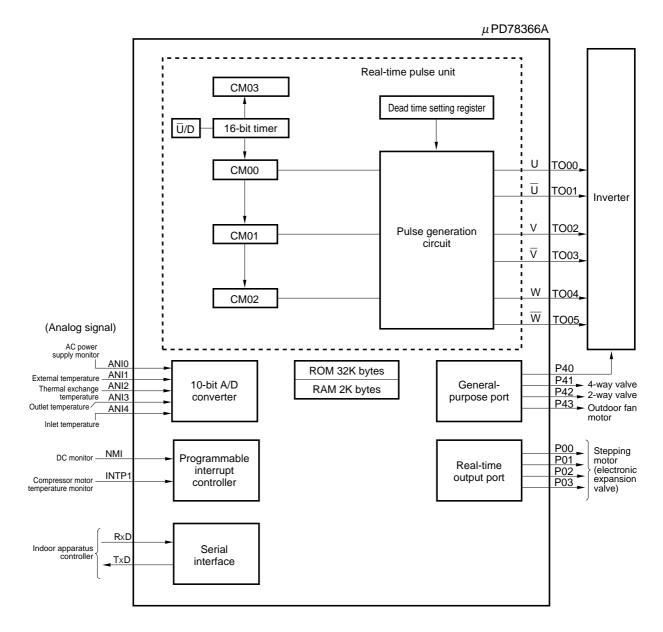

$\mu$ PD78366A is provided with a high-speed, high-performance CPU and powerful operation functions. Unlike the existing  $\mu$ PD78328,  $\mu$ PD78366A is also provided with a high-resolution PWM signal output function which substantially contributes to improving the performance of the inverter control.

A PROM model,  $\mu$ PD78P368A, is also available.

Detailed functions, etc. are described in the following user's manual. Be sure to read the manual to design systems.

$\mu$ PD78366A User's Manual Hardware: U10205E

μPD78356 User's Manual : U12117E

#### FEATURES

- Internal 16-bit architecture, external 8-bit data bus

- High-speed processing by pipeline control method and high- speed operating clock

- Minimum instruction execution time: 125 ns (internal clock: at 16 MHz, external clock: 8 MHz)

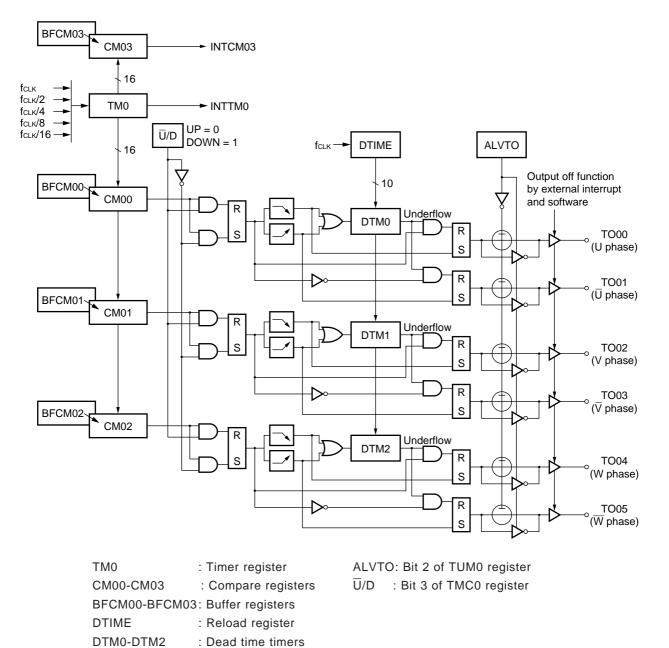

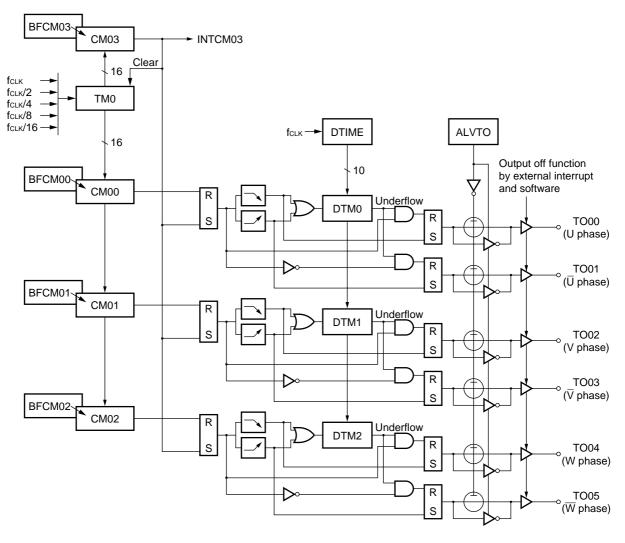

- Real-time pulse unit for inverter control

- 10-bit resolution A/D converter: 8 channels

- 8-/9-/10-/12-bit resolution variable PWM signal output function: 2 channels

- Powerful serial interface: 2 channels

- Internal memory:

- ROM: none (µPD78365A)

24K bytes (μPD78363A)

32K bytes (µPD78366A)

48K bytes (µPD78368A)

RAM: 768 bytes (μPD78363A) 2K bytes (μPD78365A, 78366A, 78368A)

#### APPLICATION EXAMPLES

- Inverter air conditioner

- Factory automation fields, such as industrial robots and machine tools.

#### ORDERING INFORMATION

| Part Number              | Package                               | Internal ROM |

|--------------------------|---------------------------------------|--------------|

| μPD78363AGF-×××-3B9      | 80-pin plastic QFP (14 $	imes$ 20 mm) | Mask ROM     |

| $\mu$ PD78365AGF-3B9     | 80-pin plastic QFP (14 $	imes$ 20 mm) | None         |

| $\mu$ PD78366AGF-×××-3B9 | 80-pin plastic QFP (14 $	imes$ 20 mm) | Mask ROM     |

| μPD78368AGF-×××-3B9      | 80-pin plastic QFP (14 $	imes$ 20 mm) | Mask ROM     |

**Remark** ××× indicates a ROM code suffix.

Unless otherwise specified, the functions and performances of the µPD78366 are described throughout this document.

The information in this document is subject to change without notice.

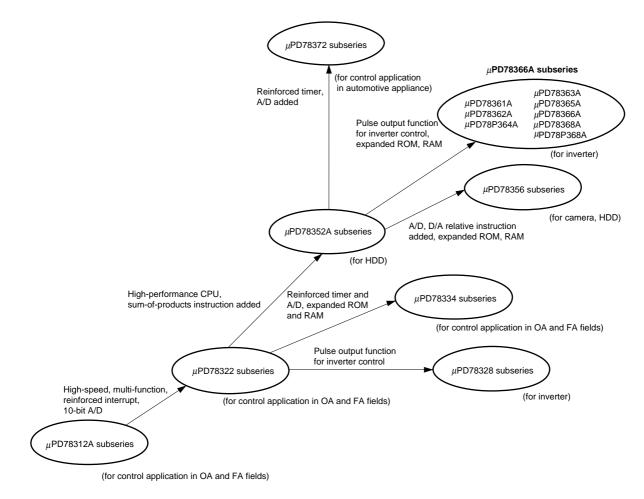

#### **78K/III Series Product Development**

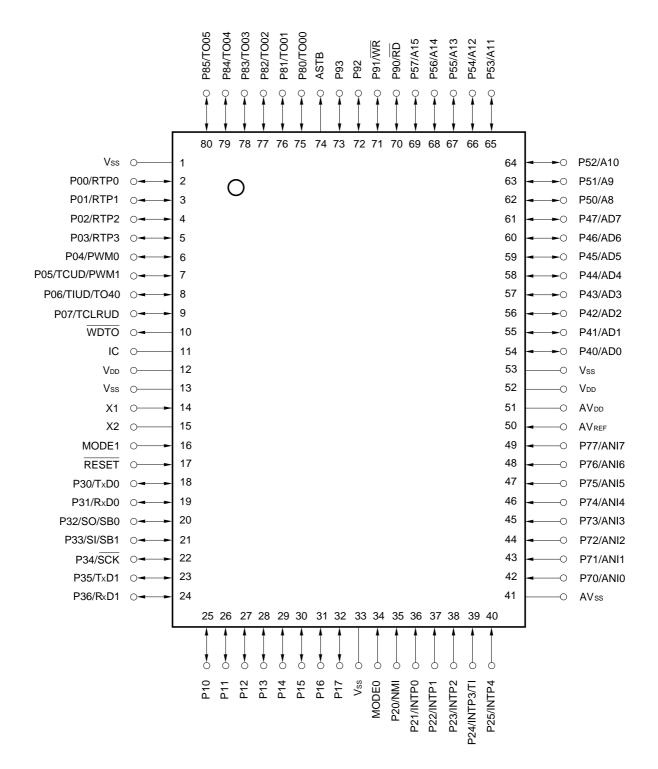

#### PIN CONFIGURATION (TOP VIEW)

- 80-pin plastic QFP (14 × 20 mm)

- μPD78363AGF-xxx-3B9, 78365AGF-3B9, 78366AGF-xxx-3B9, 78368AGF-xxx-3B9

Caution Connect the IC pin directly to Vss.

Remark ××× indicates a ROM code suffix

| P00-P07         | : Port0                         |

|-----------------|---------------------------------|

| P10-P17         | : Port1                         |

| P20-P25         | : Port2                         |

| P30-P36         | : Port3                         |

| P40-P47         | : Port4                         |

| P50-P57         | : Port5                         |

| P70-P77         | : Port7                         |

| P80-P85         | : Port8                         |

| P90-P93         | : Port9                         |

| RTP0-RTP3       | : Real-time Port                |

| NMI             | : Nonmaskable Interrupt         |

| INTP0-INTP4     | : Interrupt From Peripherals    |

| TO00-TO05, TO04 | : Timer Output                  |

| ТІ              | : Timer Input                   |

| TIUD            | : Timer Input Up Down Counter   |

| TCUD            | : Timer Control Up Down Counter |

| TCLRUD          | : Timer Clear Up Down Counter   |

| ANIO-ANI7       | : Analog Input                  |

| TxD0, TxD1      | : Transmit Data                 |

| R×D0, R×D1      | : Receive Data                  |

| SI              | : Serial Input                  |

| SO              | : Serial Output                 |

| SB0, SB1        | : Serial Bus                    |

| SCK             | : Serial Clock                  |

| PWM0, PWM1      | : Pulse Width Modulation Output |

| WDTO            | : Watchdog Timer Ouput          |

| MODE0, MODE1    | : Mode                          |

| AD0-AD7         | : Address/Data Bus              |

| A8-A15          | : Address Bus                   |

| ASTB            | : Address Strobe                |

| RD              | : Read Strobe                   |

| WR              | : Write Strobe                  |

| RESET           | : Reset                         |

| X1, X2          | : Crystal                       |

| AVdd            | : Analog VDD                    |

| AVss            | : Analog Vss                    |

| AVREF           | : Analog Reference Voltage      |

| Vdd             | : Power Supply                  |

| Vss             | : Ground                        |

| IC              | : Internally Connected          |

|                 |                                 |

#### FUNCTIONAL OUTLINE

| Item Prod                          | uct name   | μPD78363A                                                                                                                                                                                                                                                                      | μPD78365A                                                                                                                                                                                               | μPD78366A           | μPD78368A |  |  |

|------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------|--|--|

| Minimum instruction execution time | 1          | 125 ns (internal cloci                                                                                                                                                                                                                                                         | k: 16 MHz, external clo                                                                                                                                                                                 | ock: 8 MHz)         |           |  |  |

| Internal memory                    | ROM        | 24K bytes                                                                                                                                                                                                                                                                      | None                                                                                                                                                                                                    | 32K bytes 48K bytes |           |  |  |

|                                    | RAM        | 768 bytes                                                                                                                                                                                                                                                                      | 2K bytes                                                                                                                                                                                                | 1                   | 1         |  |  |

| Memory space                       |            | 64K bytes (externally                                                                                                                                                                                                                                                          | / expandable)                                                                                                                                                                                           |                     |           |  |  |

| General-purpose re                 | gisters    | 8 bits $\times$ 16 $\times$ 8 banks                                                                                                                                                                                                                                            | 3                                                                                                                                                                                                       |                     |           |  |  |

| Number of basic ins                | structions | 115                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                         |                     |           |  |  |

| Instruction set                    |            | <ul><li>Bit manipulation</li><li>String</li></ul>                                                                                                                                                                                                                              | ion (16 bits $	imes$ 16 bits, 3<br>peration (16 bits $	imes$ 16                                                                                                                                         |                     |           |  |  |

| I/O lines                          | Input      | 14 (of which 8 are sh                                                                                                                                                                                                                                                          | nared with analog input                                                                                                                                                                                 | t)                  |           |  |  |

|                                    | I/O        | 49                                                                                                                                                                                                                                                                             | 31                                                                                                                                                                                                      | 49                  |           |  |  |

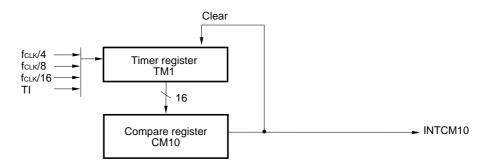

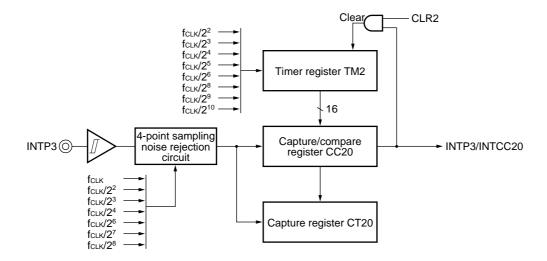

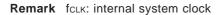

| Real-time pulse unit               |            | Mode 0, set-r<br>Mode 1, buffe<br>16-bit timer × 1<br>16-bit compare<br>16-bit timer × 1<br>16-bit capture re<br>16-bit capture re<br>16-bit timer × 1<br>16-bit capture re<br>16-bit capture re<br>16-bit capture re<br>16-bit capture re<br>16-bit compare                   | register $\times$ 4<br>at mode can be selecte<br>eset output: 6 channels<br>register $\times$ 1<br>egister $\times$ 1<br>ompare register $\times$ 1<br>egister $\times$ 2<br>ompare register $\times$ 1 | ls                  |           |  |  |

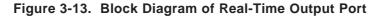

| Real-time output po                | ort        | Pulse outputs associated with real-time pulse unit: 4 lines                                                                                                                                                                                                                    |                                                                                                                                                                                                         |                     |           |  |  |

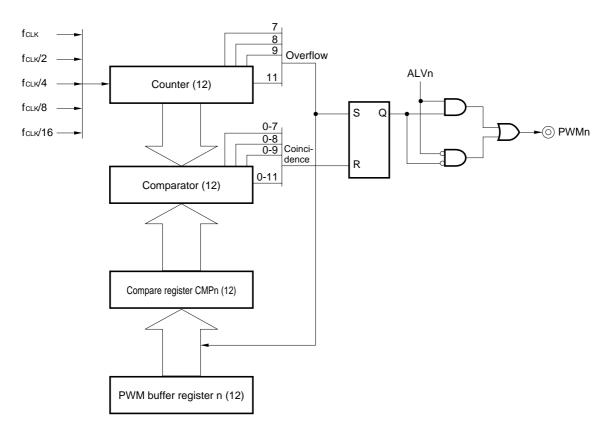

| PWM unit                           |            | 8-/9-/10-/12-bit resolution variable PWM output: 2 channels                                                                                                                                                                                                                    |                                                                                                                                                                                                         |                     |           |  |  |

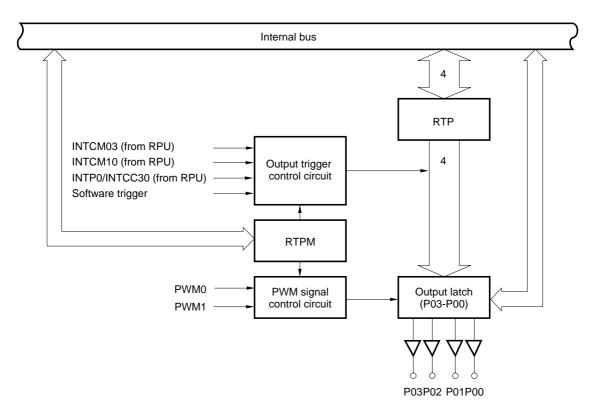

| A/D converter                      |            | 10-bit resolution, 8 channels                                                                                                                                                                                                                                                  |                                                                                                                                                                                                         |                     |           |  |  |

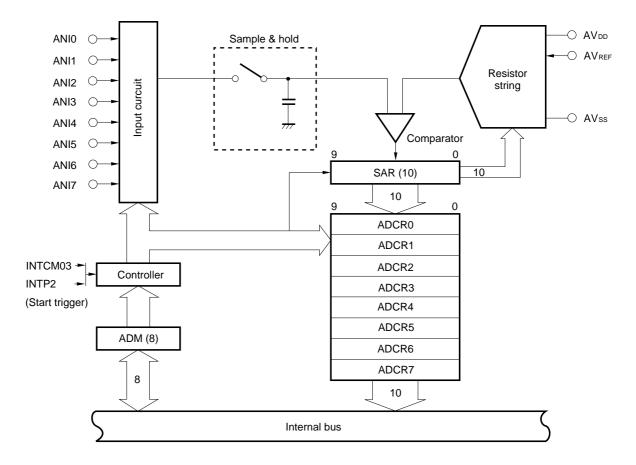

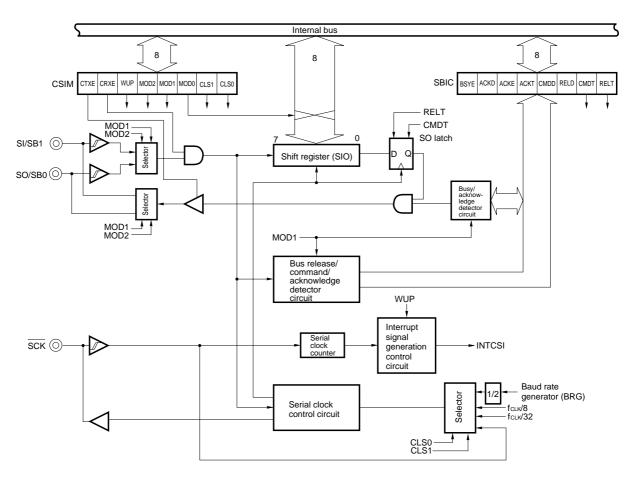

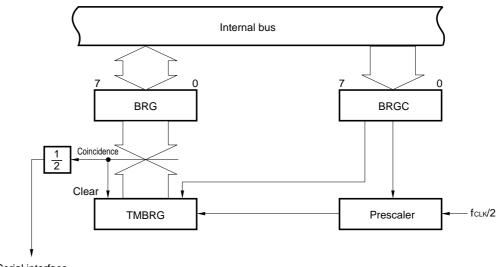

| Serial interface                   |            | Dedicated baud rate generator<br>UART (w/pin selection function): 1 channel<br>Clocked serial interface/SBI: 1 channel                                                                                                                                                         |                                                                                                                                                                                                         |                     |           |  |  |

| Interrupt function                 |            | <ul> <li>External: 6, internal: 14 (of which 2 are multiplexed with external)</li> <li>4 priority levels can be specified through software</li> <li>3 types of interrupt processing modes selectable<br/>(vectored interrupt, macro service, and context switching)</li> </ul> |                                                                                                                                                                                                         |                     |           |  |  |

| Package                            |            | 80-pin plastic QFP (1                                                                                                                                                                                                                                                          | 14 × 20 mm)                                                                                                                                                                                             |                     |           |  |  |

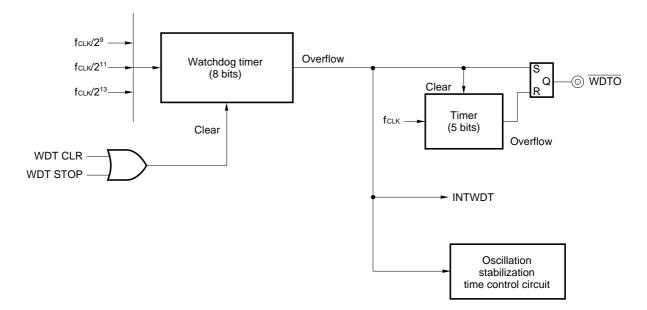

| Others                             |            | <ul><li>Watchdog timer</li><li>Standby function (</li></ul>                                                                                                                                                                                                                    | HALT and STOP mode                                                                                                                                                                                      | 25)                 |           |  |  |

#### DIFFERENCES BETWEEN $\mu$ PD78363A, 78365A, 78366A, AND 78368A

| Item                                   | t name | μPD78363A                                                                                                                                                      | μPD78366A                                                                | μPD78368A       | μPD78365A                                                                                                                                                      |  |  |

|----------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Internal ROM                           | ROM    | 24K bytes                                                                                                                                                      | 32K bytes                                                                | 48K bytes       | None                                                                                                                                                           |  |  |

| Internal ROM                           | RAM    | 786 bytes                                                                                                                                                      | 2K bytes                                                                 |                 |                                                                                                                                                                |  |  |

| Input                                  |        | 14 (of which 8                                                                                                                                                 | are multiplexed                                                          | with analog inp | ut)                                                                                                                                                            |  |  |

| I/O lines                              | I/O    | 49                                                                                                                                                             |                                                                          |                 | 31                                                                                                                                                             |  |  |

| Port 4 (P40-P47)                       |        | of 8 bits. In ex<br>mode, this por                                                                                                                             | nput or output n<br>aternal memory<br>t functions as m<br>ous (AD0-AD7). | expansion       | Always functions as multiplexed address/<br>data bus (AD0-AD7).                                                                                                |  |  |

| Port 5 (P50-P57)                       |        | Can be set in input or output mode in<br>1-bit units. In external memory expansion<br>mode, this port functions as address bus<br>(A8-A15).                    |                                                                          |                 | Always functions as address bus (A8-A15)                                                                                                                       |  |  |

| Port 9 (P90-P9:                        | 3)     | Can be set in input or output mode in<br>1-bit units. In external memory expansion<br>mode, P90 outputs RD strobe signal, and<br>P91 outputs WR strobe signal. |                                                                          |                 | P90 always functions as RD strobe signal<br>output pin, and P91 always functions as WR<br>strobe signal output pin. P92 and P93<br>function as I/O port lines. |  |  |

| Memory expansion<br>mode register (MM) |        | Sets port 4 in input or output mode in units<br>of 8 bits. In external memory expansion<br>mode, sets memory expansion width of ports<br>4 and 5.              |                                                                          |                 | Always fixed to external memory expansion mode.                                                                                                                |  |  |

| Port 5 mode<br>register (PM5)          |        | Sets port 5 in input or output mode in 1-bit units.                                                                                                            |                                                                          |                 | None                                                                                                                                                           |  |  |

| Setting of<br>MODE0, MODE1             |        | MODE0, -                                                                                                                                                       | nary operation mode:<br>DE0, 1 = LL                                      |                 | <ul> <li>Always set as follows:<br/>MODE0, 1 = HH</li> </ul>                                                                                                   |  |  |

$\mu$ PD78363A, 78365A, 78366A, 78368A

Remark The internal ROM and RAM capacities differ depending on the product.

#### CONTENTS

| 1.  | <b>PIN</b> | FUNCTIONS                                             | 10  |

|-----|------------|-------------------------------------------------------|-----|

|     | 1.1        | PORT PINS                                             |     |

|     | 1.2        | PINS OTHER THAN PORT PINS                             |     |

|     | 1.3        | PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS        | 13  |

| 2.  | CPU        | ARCHITECTURE                                          |     |

|     | 2.1        | MEMORY SPACE                                          | -   |

|     | 2.2        | DATA MEMORY ADDRESSING                                |     |

|     | 2.3        | PROCESSOR REGISTERS                                   | 20  |

|     |            | 2.3.1 Control Registers                               |     |

|     |            | 2.3.2 General-Purpose Registers                       |     |

|     |            | 2.3.3 Special Function Registers (SFR)                | .23 |

| 3.  | FUN        | CTIONAL BLOCKS                                        |     |

|     | 3.1        | EXECUTION UNIT (EXU)                                  |     |

|     | 3.2        | BUS CONTROL UNIT (BCU)                                | 29  |

|     | 3.3        | ROM/RAM                                               |     |

|     | 3.4        | PORT FUNCTIONS                                        |     |

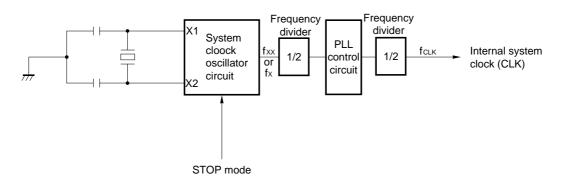

|     | 3.5        | CLOCK GENERATOR CIRCUIT                               | 32  |

|     | 3.6        | REAL-TIME PULSE UNIT (RPU)                            |     |

|     | 3.7        | REAL-TIME OUTPUT PORT (RTP)                           |     |

|     | 3.8        | A/D CONVERTER                                         |     |

|     | 3.9        | SERIAL INTERFACE                                      |     |

|     |            | PWM UNIT                                              |     |

|     | 3.11       | WATCHDOG TIMER (WDT)                                  | 47  |

| 4.  | INTE       | RRUPT FUNCTIONS                                       |     |

|     | 4.1        | OUTLINE                                               |     |

|     | 4.2        | MACRO SERVICE                                         | -   |

|     | 4.3        | CONTEXT SWITCHING                                     | 52  |

|     |            | 4.3.1 Context Switching Function by Interrupt Request |     |

|     |            | 4.3.2 Context Switching Function by BRKCS Instruction |     |

|     |            | 4.3.3 Restoration from Context Switching              | .53 |

| 5.  | EXT        | ERNAL DEVICE EXPANSION FUNCTION                       | 54  |

| 6.  | STA        | NDBY FUNCTIONS                                        | 55  |

| 7.  | RES        |                                                       | 56  |

|     | _          |                                                       |     |

| 8.  | INST       | RUCTION SET                                           | 57  |

| 9.  | EXA        | MPLE OF SYSTEM CONFIGURATION                          | 71  |

| 10. | ELE        | CTRICAL SPECIFICATIONS                                | 72  |

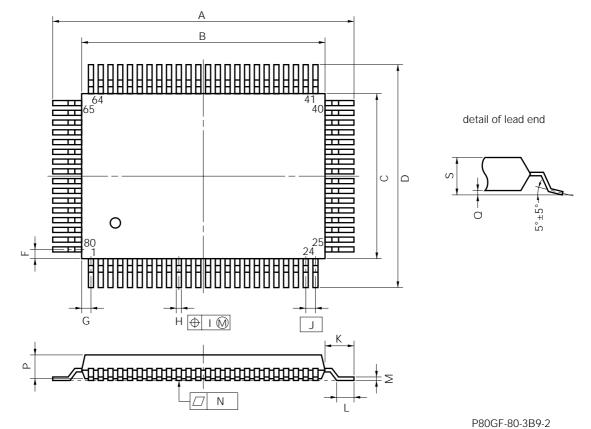

| 11. PACK | AGE DRAWING                                               | 83 |

|----------|-----------------------------------------------------------|----|

| 12. RECO | OMMENDED SOLDERING CONDITIONS                             | 84 |

| APPENDI  | X A. DIFFERENCES BETWEEN $\mu$ PD78366A AND $\mu$ PD78328 | 85 |

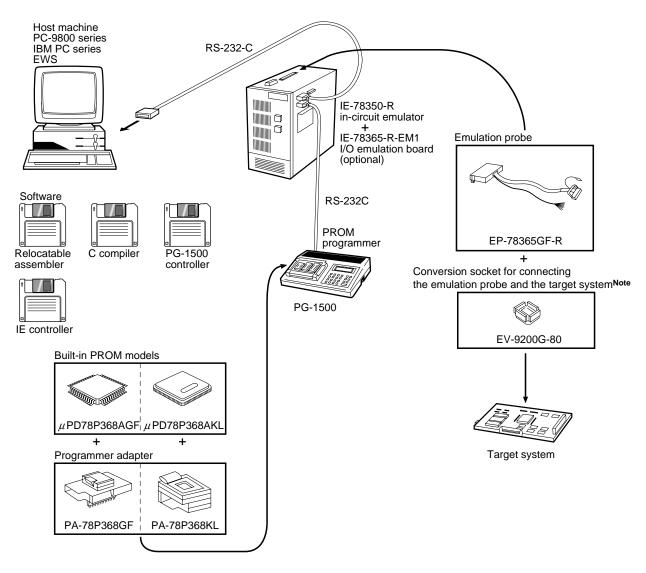

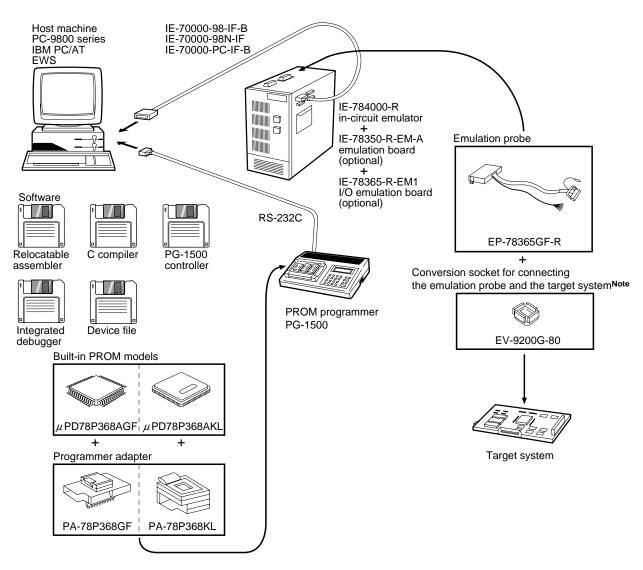

| APPENDI  | X B. TOOLS                                                | 86 |

| B.1 [    | DEVELOPMENT TOOLS                                         | 86 |

| B.2 E    | EMBEDDED SOFTWARE                                         | 91 |

|          |                                                           |    |

#### 1. PIN FUNCTIONS

#### 1.1 PORT PINS

| Pin name | I/O   | Function                                                                         | Shared by: |

|----------|-------|----------------------------------------------------------------------------------|------------|

| P00-P03  |       | Port 0.                                                                          | RTP0-RTP3  |

| P04      |       | 8-bit I/O port.                                                                  | PWM0       |

| P05      | I/O   | Can be set in input or output mode in 1-bit units.                               | TCUD/PWM1  |

| P06      |       |                                                                                  | TIUD/TO40  |

| P07      | _     |                                                                                  | TCLRUD     |

| P10-P17  | I/O   | Port 1.<br>8-bit I/O port.<br>Can be set in input or output mode in 1-bit units. | _          |

| P20      |       | Port 2.                                                                          | NMI        |

| P21      | -     | 6-bit input port.                                                                | INTP0      |

| P22      |       |                                                                                  | INTP1      |

| P23      | Input |                                                                                  | INTP2      |

| P24      |       |                                                                                  | INTP3/TI   |

| P25      |       |                                                                                  | INTP4      |

| P30      |       | Port 3.                                                                          | TxD0       |

| P31      | _     | 7-bit I/O port.<br>Can be set in input or output mode in 1-bit units.            | R×D0       |

| P32      | I/O   |                                                                                  | SO/SB0     |

| P33      |       |                                                                                  | SI/SB1     |

| P34      | -     |                                                                                  | SCK        |

| P35      | -     |                                                                                  | TxD1       |

| P36      | _     |                                                                                  | RxD1       |

| P40-P47  | I/O   | Port 4.<br>8-bit I/O Port.<br>Can be set in input or output mode in 8-bit units. | AD0-AD7    |

| P50-P57  | I/O   | Port 5.<br>8-bit I/O port.<br>Can be set in input or output mode in 1-bit units. | A8-A15     |

| P70-P77  | Input | Port 7.<br>8-bit input port                                                      | ANIO-ANI7  |

| P80-P85  | I/O   | Port 8.<br>6-bit I/O port.<br>Can be set in input or output mode in 1-bit units. | TO00-TO05  |

| P90      |       |                                                                                  | RD         |

| P91      | 1/2   | Port 9.                                                                          | WR         |

| P92      | - I/O | 4-bit I/O port.                                                                  | _          |

| P93      | 1     | Can be set in input or output mode in 1-bit units.                               | _          |

| Pin name  | I/O     | Function                                                                                                                           | Shared by: |

|-----------|---------|------------------------------------------------------------------------------------------------------------------------------------|------------|

| RTP0-RTP3 | Output  | Real-time output port that outputs pulses in synchronization with trigger signal from real-time pulse unit.                        | P00-P03    |

| NMI       |         | Non-maskable interrupt request input.                                                                                              | P20        |

| INTP0     |         | External interrupt request input.                                                                                                  | P21        |

| INTP1     | Input   |                                                                                                                                    | P22        |

| INTP2     | mput    |                                                                                                                                    | P23        |

| INTP3     |         |                                                                                                                                    | P24/TI     |

| INTP4     |         |                                                                                                                                    | P25        |

| TI        |         | External count clock input to timer 1.                                                                                             | P24/INTP3  |

| TCUD      | Input   | Count operation selection control signal input to up/down counter (timer 4).                                                       | P05/PWM1   |

| TIUD      |         | External count clock input to up/down counter (timer 4).                                                                           | P06/TO40   |

| TCLRUD    | 1       | Clear signal input to up/down counter (timer 4).                                                                                   | P07        |

| TO00-TO05 | Output  |                                                                                                                                    | P80-P85    |

| TO40      |         | Pulse output from real-time pulse unit.                                                                                            | P06/TIUD   |

| ANIO-ANI7 | Input   | Analog input to A/D converter.                                                                                                     | P70-P77    |

| TxD0      | Output  |                                                                                                                                    | P30        |

| TxD1      |         | Serial data output of asynchronous serial interface.                                                                               | P35        |

| R×D0      | Input   | Carial data input of asymphraneus asrial interface                                                                                 | P31        |

| RxD1      | Input   | Serial data input of asynchronous serial interface.                                                                                | P36        |

| SCK       | I/O     | Serial clock input/output of clocked serial interface.                                                                             | P34        |

| SI        | Input   | Serial data input of clocked serial interface in 3-line mode.                                                                      | P33/SB1    |

| SO        | Ouput   | Serial data output of clocked serial interface in 3-line mode.                                                                     | P32/SB0    |

| SB0       | 1/0     |                                                                                                                                    | P32/SO     |

| SB1       | I/O     | Serial data input/output of clocked serial interface in SBI mode.                                                                  | P33/SI     |

| PWM0      | Outrast |                                                                                                                                    | P04        |

| PWM1      | Output  | PWM signal output.                                                                                                                 | P05/TCUD   |

| WDTO      | Output  | Signal output indicating overflow of watchdog timer (generates non-maskable interrupt).                                            | _          |

| AD0-AD7   | 1/2     | Multiplexed address/data bus when memory is externally expanded.                                                                   | P40-P47    |

| A8-A15    | - I/O   | Address bus when memory is externally expanded.                                                                                    | P50-P57    |

| ASTB      |         | Outputs timing signal at which address information output from AD0-AD7 and A8-A15 pins to access external memory is to be latched. | _          |

| RD        | Output  | Read strobe signal output to external memory.                                                                                      | P90        |

| WR        | 1       | Write strobe signal output to external memory.                                                                                     | P91        |

#### 1.2 PINS OTHER THAN PORT PINS (1/2)

| Pin name | I/O   | Function                                                                                                               | Shared by: |

|----------|-------|------------------------------------------------------------------------------------------------------------------------|------------|

| MODE0    |       | Control signal input to set operation mode. With $\mu$ PD78363A, 78366A, and                                           |            |

| MODE1    | Input | 78368A MODE0 and MODE1 are usually connected to Vss. With $\mu$ PD78365A, MODE0 and MODE1 are always connected to Vdd. | _          |

| RESET    | Input | System reset input                                                                                                     | _          |

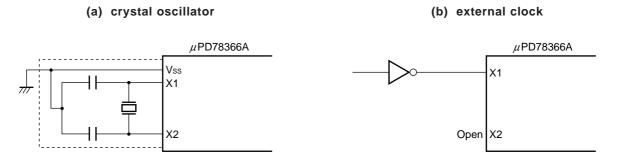

| X1       | Input | Crystal oscillator connecting pins for system clock. If a clock is externally                                          |            |

| X2       | _     | supplied, input it to pin X1. Leave pin X2 open.                                                                       | _          |

| AVREF    | Input | A/D converter reference voltage input.                                                                                 | _          |

| AVdd     | -     | A/D converter analog power supply.                                                                                     | _          |

| AVss     | -     | A/D converter GND.                                                                                                     | _          |

| Vdd      | _     | Positive power supply                                                                                                  | _          |

| Vss      | -     | GND                                                                                                                    | _          |

| IC       | -     | Internally connected. Connect this pin to Vss.                                                                         | _          |

#### 1.2 PINS OTHER THAN PORT PINS (2/2)

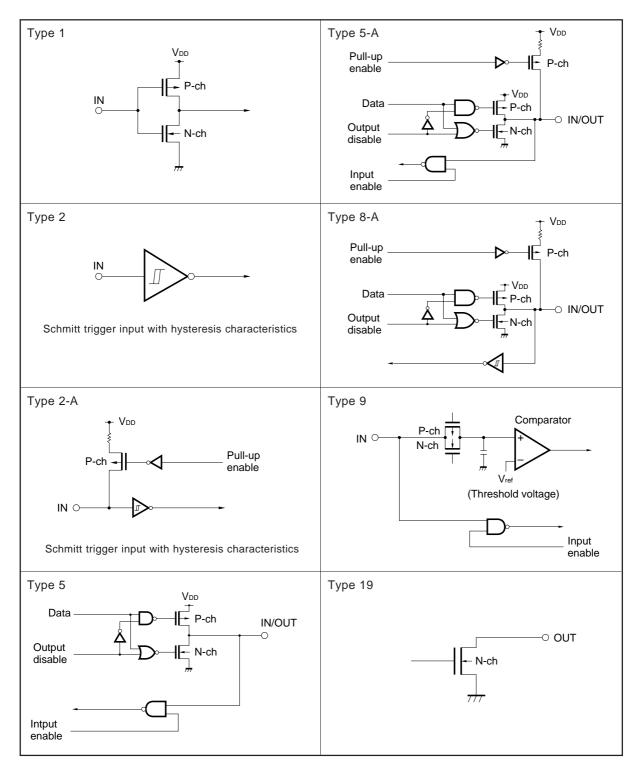

#### 1.3 PIN I/O CIRCUITS AND PROCESSING OF UNUSED PINS

Table 1-1 shows the I/O circuit types of the respective pins, and recommended connections of the unused pins. Figure 1-1 shows the circuits of the respective pins.

| Pin               | I/O circuit type | Recommended connections                                                                    |  |  |  |  |

|-------------------|------------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| P00/RTP0-P03/RTP3 |                  |                                                                                            |  |  |  |  |

| P04/PWM0          |                  |                                                                                            |  |  |  |  |

| P05/TCUD/PWM1     |                  | Input : Independently connect to VDD or VSS through resistor<br>Output : Leave unconnected |  |  |  |  |

| P06/TIUD/TO40     | 5-A              |                                                                                            |  |  |  |  |

| P07/TCLRUD        |                  |                                                                                            |  |  |  |  |

| P10-P17           |                  |                                                                                            |  |  |  |  |

| P20/NMI           | 2                |                                                                                            |  |  |  |  |

| P21/INTP0         |                  | _                                                                                          |  |  |  |  |

| P22/INTP1         |                  |                                                                                            |  |  |  |  |

| P23/INTP2         | 2-A              | Connect to Vss                                                                             |  |  |  |  |

| P24/INTP3/TI      |                  |                                                                                            |  |  |  |  |

| P25/INTP4         |                  |                                                                                            |  |  |  |  |

| P30/TxD0          | 5.0              |                                                                                            |  |  |  |  |

| P31/RxD0          | 5-A              |                                                                                            |  |  |  |  |

| P32/SO/SB0        |                  | _                                                                                          |  |  |  |  |

| P33/SI/SB1        | 8-A              | Input : Independently connect to VDD or VSS through resistor                               |  |  |  |  |

| P34/SCK           |                  | Output : Leave unconnected                                                                 |  |  |  |  |

| P35/TxD1          |                  |                                                                                            |  |  |  |  |

| P36/RxD1          | 5-A              |                                                                                            |  |  |  |  |

| P40/AD0-P47/AD7   | 5-A              |                                                                                            |  |  |  |  |

| P50/A8-P57/A15    |                  |                                                                                            |  |  |  |  |

| P70/ANI0-P77/ANI7 | 9                | Connect to Vss                                                                             |  |  |  |  |

| P80/TO00-P85/TO05 |                  |                                                                                            |  |  |  |  |

| P90/RD            | 5-A              |                                                                                            |  |  |  |  |

| P91/WR            | 077              | Input : Independently connect to VDD or Vss through resistor<br>Output : Leave unconnected |  |  |  |  |

| P92, P93          |                  |                                                                                            |  |  |  |  |

| ASTB              | 5                |                                                                                            |  |  |  |  |

| WDTO              | 19               | Connect to Vss                                                                             |  |  |  |  |

| MODE0, MODE1      | 1                | _                                                                                          |  |  |  |  |

| RESET             | 2                |                                                                                            |  |  |  |  |

| AVREF, AVSS       |                  | Connect to Vss                                                                             |  |  |  |  |

| AVdd              |                  | Connect to VDD                                                                             |  |  |  |  |

| IC                |                  | Connect to Vss                                                                             |  |  |  |  |

Table 1-1. Pin I/O Circuit Type and Recommended Connections of Unused Pins

Figure 1-1. Pin I/O Circuits

٠

#### 2. CPU ARCHITECTURE

#### 2.1 MEMORY SPACE

The  $\mu$ PD78366A can access a memory space of 64K bytes. Figures 2-1 through 2-3 show the memory map.

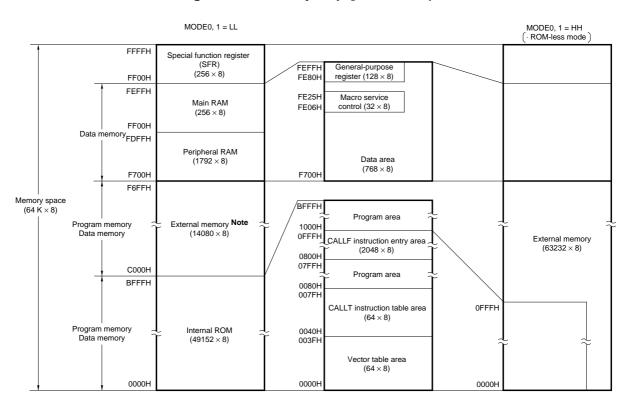

#### Figure 2-1. Memory Map (µPD78368A)

Note Accessed in external memory expansion mode.

Caution For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

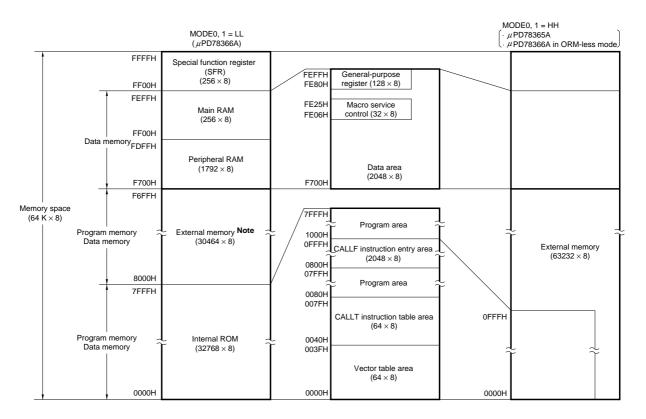

Figure 2-2. Memory Map (µPD78365A, 78366A)

Note Accessed in external memory expansion mode.

Caution For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

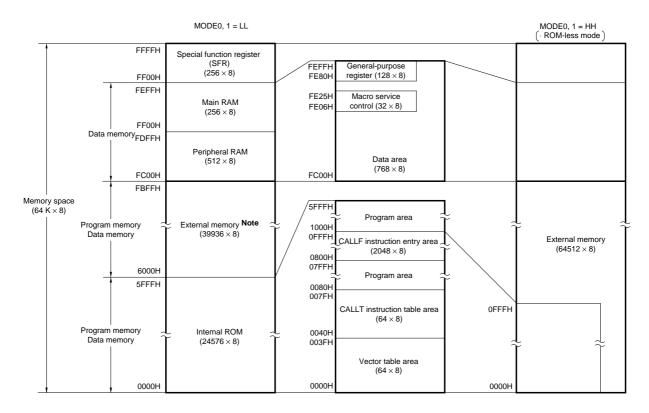

#### Figure 2-3. Memory Map (µPD78363A)

Note Accessed in external memory expansion mode.

Caution For word access (including stack operations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

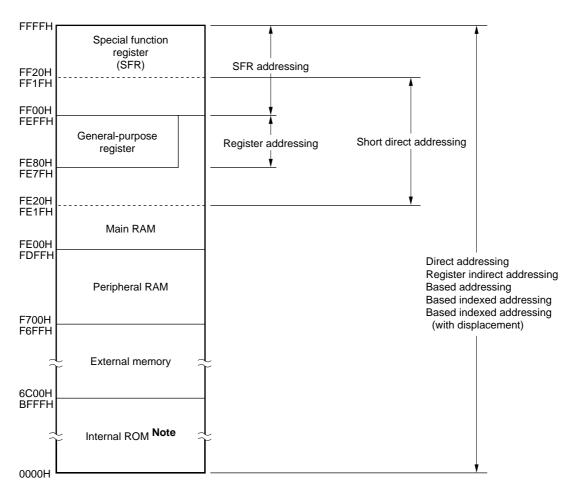

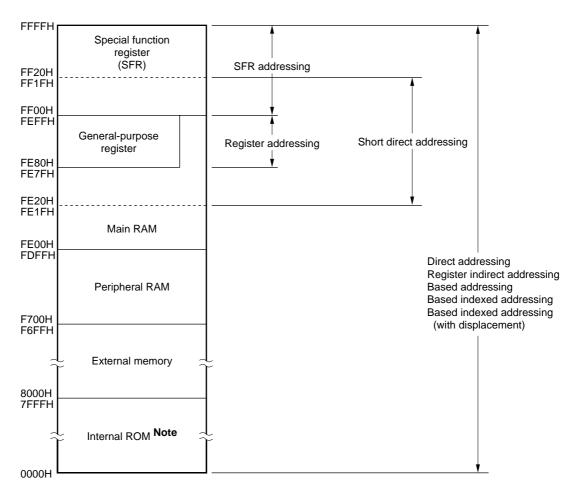

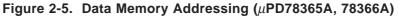

#### 2.2 DATA MEMORY ADDRESSING

The  $\mu$ PD78366A is provided with many addressing modes that improve the operability of the memory and can be used with high-level languages. Especially, an area of addresses F700H-FFFFH (In the  $\mu$ PD78363A, FC00H-FFFFH) to which the data memory is mapped can be addressed in a mode peculiar to the functions provided in this area, including special function registers (SFR) and general-purpose registers.

Figure 2-4. Data Memory Addressing (µPD78368A)

Note Is external memory in the ROMless mode.

Caution For word access (including stack oprations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

Caution For word access (including stack oprations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

Figure 2-6. Data Memory Addressing (µPD78363A)

## Caution For word access (including stack oprations) to the main RAM area (FE00H-FEFFH), the address that specifies the operand must be an even value.

#### 2.3 PROCESSOR REGISTERS

The  $\mu$ PD78366A is provided with the following three types of processor registers:

- Control registers

- General-purpose registers

- Special function registers (SFRs)

#### 2.3.1 Control Registers

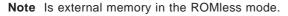

- (1) Program counter (PC)This is a 16-bit register that holds an address of the instruction to be executed next.

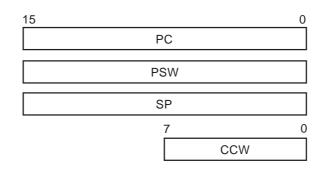

- (2) Program status word (PSW)This 16-bit register indicates the status of the CPU as a result of instruction execution.

- (3) Stack pointer (SP)This 16-bit register indicates the first address of the stack area (LIFO) of the memory.

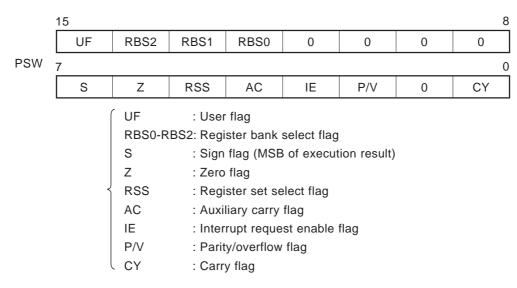

- (4) CPU control word (CCW)This 8-bit register is used to control the CPU.

Figure 2-7. Configuration of Control Registers

Figure 2-9. Configuration of CCW

#### 2.3.2 General-Purpose Registers

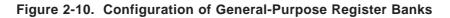

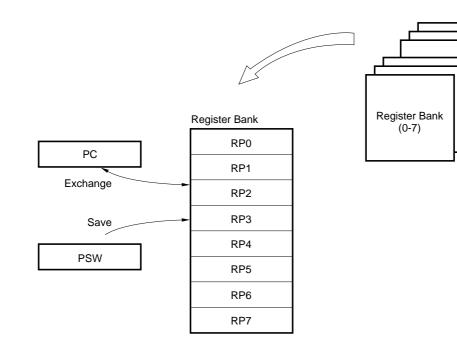

The  $\mu$ PD78366A is provided with eight banks of general-purpose registers with one bank consisting of 8 words  $\times$  16 bits. Figure 2-10 shows the configuration of the general-purpose register banks. The general-purpose registers are mapped to an area of addresses FE80H-FEFFH. Each of these registers can be used as an 8-bit register. In addition, two registers can be used as one 16-bit register pair (refer to **Figure 2-11**). These general-purpose registers facilitate complicated multitask processing.

Figure 2-11. Processing Bits of General-Purpose Registers

|       |       |            | 8-bit pr | ocessing |   | 16-b | it proces | ssing |

|-------|-------|------------|----------|----------|---|------|-----------|-------|

| FEFFH | RBNK0 |            | R15      | R14      |   | (FH) | RP7       | (EH)  |

|       | RBNK1 |            | R13      | R12      |   | (DH) | RP6       | (CH)  |

|       | RBNK2 |            | R11      | R10      |   | (BH) | RP5       | (AH)  |

|       | RBNK3 |            | R9       | R8       |   | (9H) | RP4       | (8H)  |

|       | RBNK4 |            | R7       | R6       |   | (7H) | RP3       | (6H)  |

|       | RBNK5 |            | R5       | R4       |   | (5H) | RP2       | (4H)  |

|       | RBNK6 |            | R3       | R2       |   | (3H) | RP1       | (2H)  |

| FE80H | RBNK7 |            | R1       | R0       |   | (1H) | RP0       | (0H)  |

|       |       | - <u> </u> | 7 0      | 7 C      | ) | 15   |           | 0     |

#### 2.3.3 Special Function Registers (SFR)

Special function registers (SFRs) are registers assigned special functions such as mode registers and control registers for internal peripheral hardware, and are mapped to a 256-byte address space at FF00H through FFFFH.

Table 2-1 lists the SFRs. The meanings of the symbols in this table are as follows:

- Symbol ..... Indicates the mnemonic symbol for an SFR.

- This mnemonic can be coded in the operand field of an instruction.

- R/W ..... Indicates whether the SFR can be read or written.

- R/W : Read/write

- R : Read only

- W : Write only

- Bit units for manipulation ..... Indicates bit units in which the SFR can be manipulated. The SFRs that can be manipulated in 16-bit units can be coded as an sfrp operand. Specify an even address for these SFRs.

- The SFRs that can be manipulated in 1-bit units can be coded as the operand of bit manipulation instructions.

- On reset ...... Indicates the status of the register at RESET input.

- Cautions 1. Do not access the addresses in the range FF00H through FFFFH to which no special function register is allocated. If these addresses are accessed, malfunctioning may occur.

- 2. Do not write data to the read-only registers. Otherwise, the internal circuit may not operate normally.

- 3. When using read data as byte data, process undefined bit(s) first.

- 4. TOUT and TXS are write-only registers. Do no read these registers.

- 5. Bits 0, 1, and 4 of SBIC are write-only bits. When these bits are read, they are always "0".

| Address | Special function register (SFR) | Symbol              | R/W      |       | it units f<br>anipulati | On reset |            |  |

|---------|---------------------------------|---------------------|----------|-------|-------------------------|----------|------------|--|

|         |                                 |                     |          | 1 bit | 8 bits                  | 16 bits  |            |  |

| FF00H   | Port 0                          | P0                  | D AA     | 0     | 0                       | -        |            |  |

| FF01H   | Port 1                          | P1                  | R/W      | 0     | 0                       | _        |            |  |

| FF02H   | Port 2                          | P2                  | R        | 0     | 0                       | _        |            |  |

| FF03H   | Port 3                          | P3                  |          | 0     | 0                       | _        |            |  |

| FF04H   | Port 4                          | P4Note              | R/W      | 0     | 0                       | _        |            |  |

| FF05H   | Port 5                          | P5Note              |          | 0     | 0                       | -        |            |  |

| FF07H   | Port 7                          | P7                  | R        | 0     | 0                       | -        |            |  |

| FF08H   | Port 8                          | P8                  |          | 0     | 0                       | _        |            |  |

| FF09H   | Port 9                          | P9                  |          | 0     | 0                       | _        |            |  |

| FF10H   |                                 | 01100               |          |       |                         |          |            |  |

| FF11H   | Compare register 00             | CM00                |          | -     | -                       | 0        |            |  |

| FF12H   |                                 |                     |          |       |                         |          | Undefined  |  |

| FF13H   | Compare register 01             | CM01                |          | -     | -                       | 0        | -          |  |

| FF14H   |                                 |                     | -        |       | -                       | 0        |            |  |

| FF15H   | Compare register 02             | CM02                |          | -     |                         |          |            |  |

| FF16H   |                                 | CM03                | R/W      |       |                         |          |            |  |

| FF17H   | Compare register 03             |                     |          | -     |                         |          |            |  |

| FF18H   |                                 | BFCM00              | -        |       |                         | _        |            |  |

| FF19H   | Buffer register CM00            |                     |          | -     | -                       | 0        |            |  |

| FF1AH   |                                 |                     |          |       |                         | _        |            |  |

| FF1BH   | Buffer register CM01            | BFCM01              | -        | -     | 0                       |          |            |  |

| FF1CH   |                                 |                     |          |       |                         |          | 1          |  |

| FF1DH   | Buffer register CM02            | BFCM02              |          | -     | -                       | 0        |            |  |

| FF1EH   |                                 |                     | _        |       |                         |          |            |  |

| FF1FH   | Timer register 0                | TM0                 | R        | -     | -                       | 0        | 0000H      |  |

| FF20H   | Port 0 mode register            | PM0                 |          | 0     | 0                       | _        |            |  |

| FF21H   | Port 1 mode register            | PM1                 |          | 0     | 0                       | _        | FFH        |  |

| FF23H   | Port 3 mode register            | PM3                 |          | 0     | 0                       | _        | ×111 1111B |  |

| FF25H   | Port 5 mode register            | PM5 <sup>Note</sup> | R/W      | 0     | 0                       | _        | FFH        |  |

| FF28H   | Port 8 mode register            | PM8                 |          | 0     | 0                       | _        | ××11 1111B |  |

| FF29H   | Port 9 mode register            | PM9                 | 1        | 0     | 0                       | _        | xxxx 1111B |  |

| FF2CH   |                                 |                     |          |       |                         |          |            |  |

| FF2DH   | Reload register                 | DTIME               |          | -     | -                       | 0        | Undefined  |  |

| FF2EH   | Timer unit mode register 0      | TUM0                | <b>_</b> | 0     | 0                       | -        | 0.011      |  |

| FF2FH   | Timer unit mode register 1      | TUM1                | R/W      | 0     | 0                       | -        | 00H        |  |

| FF30H   | Compare register 10             | 01440               | 1        |       |                         |          | llodeficed |  |

| FF31H   | Compare register 10             | CM10                |          | -     | -                       | 0        | Undefined  |  |

| FF32H   | Timor register 1                | TNAA                | P        |       |                         |          | 000011     |  |

| FF33H   | Timer register 1                | TM1                 | R        | -     | -                       | 0        | 0000H      |  |

Table 2-1. List of Special Function Registers (1/5)

**Note** Not provided for the  $\mu$ PD78365A.

| Address | Special function register (SFR)     | Symbol R/W    | R/W      | 1     | it units f<br>anipulati |         | On reset   |  |

|---------|-------------------------------------|---------------|----------|-------|-------------------------|---------|------------|--|

|         |                                     |               |          | 1 bit | 8 bits                  | 16 bits |            |  |

| FF34H   | Capture/compare register 20         | CC20          | R/W      | _     | _                       | 0       |            |  |

| FF35H   |                                     |               | 1\/ VV   |       |                         |         | Undefined  |  |

| FF36H   | Capture register 20                 | CT20          |          |       |                         | 0       | Undenned   |  |

| FF37H   |                                     | 0120          | R        |       |                         |         |            |  |

| FF38H   | - Timer register 2                  | TM2           | n        |       |                         | 0       | 0000H      |  |

| FF39H   |                                     | 1 1012        |          | _     | _                       |         | 000011     |  |

| FF3AH   | Duffer register CM02                | <b>BECM02</b> |          |       |                         |         | Underfined |  |

| FF3BH   | Buffer register CM03                | BFCM03        |          | _     | -                       | 0       | Undernned  |  |

| FF3CH   | External interrupt mode register 0  | INTMO         |          | 0     | 0                       | -       |            |  |

| FF3DH   | External interrupt mode register 1  | INTM1         |          | 0     | 0                       | -       | 00H        |  |

| FF40H   | Port 0 mode control register        | PMC0          |          | 0     | 0                       | _       |            |  |

| FF43H   | Port 3 mode control register        | PMC3          |          | 0     | 0                       | -       | ×000 0000B |  |

| FF44H   | Pull-up resistor option register L  | PUOL          | R/W      | 0     | 0                       | -       | 0011       |  |

| FF45H   | Pull-up resistor option register H  | PUOH          |          | 0     | 0                       | -       | 00H        |  |

| FF48H   | Port 8 mode control register        | PMC8          | -        | 0     | 0                       | -       | ××00 0000B |  |

| FF4EH   | Sampling control register 0         | SMPC0         | :0 0     |       | 0                       | -       | 0011       |  |

| FF4FH   | Sampling control register 1         | SMPC1         |          | 0     | 0                       | -       | 00H        |  |

| FF50H   |                                     |               |          |       |                         |         |            |  |

| FF51H   | Capture/compare register 30         | CC30          |          | -     | -                       | 0       |            |  |

| FF52H   |                                     |               |          |       |                         |         |            |  |

| FF53H   | - Capture register 30               | CT30          |          | _     | _                       | 0       | Undefined  |  |

| FF54H   |                                     | 0701          |          |       |                         |         |            |  |

| FF55H   | - Capture register 31               | CT31          | R        | -     | -                       | 0       |            |  |

| FF56H   |                                     |               |          |       |                         |         |            |  |

| FF57H   | - Timer register 3                  | TM3           |          | -     | -                       | 0       | 0000H      |  |

| FF58H   | 0                                   | 0.1.10        |          |       |                         |         |            |  |

| FF59H   | - Compare register 40               | CM40          | DAA      | -     | -                       | 0       |            |  |

| FF5AH   |                                     | 0.144         | R/W      |       |                         |         | Undefined  |  |

| FF5BH   | - Compare register 41               | CM41          |          | -     | -                       | 0       |            |  |

| FF5CH   | Timer register 4                    |               | <b>D</b> |       |                         |         | 000011     |  |

| FF5DH   | Timer register 4 TM4 R              |               | ĸ        | -     | -                       | 0       | 0000H      |  |

| FF5EH   | Timer control register 4            | TMC4          | R/W      | -     | 0                       | -       | 00H        |  |

| FF5FH   | Timer out register                  | TOUT          | W        | -     | 0                       | -       | ××01 0101B |  |

| FF60H   | Real-time output port register      | RTP           |          | 0     | 0                       | _       | Undefined  |  |

| FF61H   | Real-time output port mode register | RTPM          | 1        | 0     | 0                       | _       |            |  |

| FF62H   | Port read control register          | PRDC          | R/W      | 0     | 0                       | _       | 00H        |  |

| FF68H   | A/D converter mode register         | ADM           | 1        | 0     | 0                       | _       | 1          |  |

| Table 2-1. L | _ist of Special | <b>Function</b> F | Registers | (2/5) |

|--------------|-----------------|-------------------|-----------|-------|

|--------------|-----------------|-------------------|-----------|-------|

| Address | Special function register (SFR)               | Symbol | R/W                 | Bit units for manipulation |        | On reset |           |

|---------|-----------------------------------------------|--------|---------------------|----------------------------|--------|----------|-----------|

|         |                                               |        |                     | 1 bit                      | 8 bits | 16 bits  |           |

| FF70H   | Slave buffer register 0                       | SBUF0  |                     | 0                          | 0      | -        |           |

| FF71H   | Slave buffer register 1                       | SBUF1  |                     | 0                          | 0      | -        |           |

| FF72H   | Slave buffer register 2                       | SBUF2  |                     | 0                          | 0      | -        |           |

| FF73H   | Slave buffer register 3                       | SBUF3  |                     | 0                          | 0      | -        |           |

| FF74H   | Slave buffer register 4                       | SBUF4  |                     | 0                          | 0      | -        |           |

| FF75H   | Slave buffer register 5                       | SBUF5  |                     | 0                          | 0      | -        | Undefined |

| FF76H   | Master buffer register 0                      | MBUF0  |                     | 0                          | 0      | -        | Undenned  |

| FF77H   | Master buffer register 1                      | MBUF1  |                     | 0                          | 0      | -        |           |

| FF78H   | Master buffer register 2                      | MBUF2  | R/W                 | 0                          | 0      | -        |           |

| FF79H   | Master buffer register 3                      | MBUF3  | K/VV                | 0                          | 0      | -        |           |

| FF7AH   | Master buffer register 4                      | MBUF4  |                     | 0                          | 0      | -        |           |

| FF7BH   | Master buffer register 5                      | MBUF5  |                     | 0                          | 0      | -        |           |

| FF7CH   | Timer control register 0                      | TMC0   |                     | 0                          | 0      | -        |           |

| FF7DH   | Timer control register 1                      | TMC1   |                     | 0                          | 0      | -        |           |

| FF7EH   | Timer control register 2                      | TMC2   |                     | 0                          | 0      | -        | 00H       |

| FF7FH   | Timer control register 3                      | TMC3   |                     | 0                          | 0      | -        |           |

| FF80H   | Clocked serial interface mode register        | CSIM   |                     | 0                          | 0      | -        |           |

| FF82H   | Serial bus interface control register         | SBIC   | R/W <sup>Note</sup> | 0                          | 0      | -        |           |

| FF84H   | Baud rate generator control register          | BRGC   |                     | 0                          | 0      | -        |           |

| FF85H   | Baud rate generator compare register          | BRG    | DAA                 | -                          | 0      | -        | Undefined |

| FF86H   | Serial I/O shift register                     | SIO    | R/W                 | 0                          | 0      | -        | Undefined |

| FF88H   | Asynchronous serial interface mode register   | ASIM   |                     | 0                          | 0      | -        | 80H       |

| FF8AH   | Asynchronous serial interface status register | ASIS   | R                   | 0                          | 0      | -        | 00H       |

| FF8CH   | Serial receive buffer: UART                   | RXB    | rt                  | _                          | 0      | -        | Undefined |

| FF8EH   | Serial transfer shift register: UART          | TXS    | W                   | -                          | 0      | -        | Undenned  |

| FFA0H   | PWM control register 0                        | PWMC0  |                     | 0                          | 0      | -        | 00H       |

| FFA1H   | PWM control register 1                        | PWMC1  |                     | 0                          | 0      | -        | 001       |

| FFA2H   | PWM register 0L                               | PWM0L  | R/W                 | 0                          | 0      | -        |           |

| FFA2H   | PWM register 0                                | PWM0   |                     | _                          | _      | 0        | Undefined |

| FFA3H   |                                               |        |                     |                            |        |          |           |

Table 2-1. List of Special Function Registers (3/5)

Note Bits 7 and 5 : read/write Bits 6, 3, and 2 : read-only Bits 4, 1, and 0 : write-only

| Address | Special function register (SFR)   | Symbol                                  | R/W |       | it units f<br>anipulati |         | On reset   |

|---------|-----------------------------------|-----------------------------------------|-----|-------|-------------------------|---------|------------|

|         |                                   |                                         |     | 1 bit | 8 bits                  | 16 bits |            |

| FFA4H   | PWM register 1L                   | PWM1L                                   |     | 0     | 0                       | -       |            |

| FFA4H   |                                   | DIAMAA                                  | R/W |       |                         |         | Undefined  |

| FFA5H   | PWM register 1                    | PWM1                                    |     | _     | -                       | 0       |            |

| FFA8H   | In-service priority register      | ISPR                                    | R   | 0     | 0                       | -       | 00H        |

| FFAAH   | Interrupt mode control register   | IMC                                     |     | 0     | 0                       | -       | 80H        |

| FFACH   | Interrupt mask register 0L        | MKOL                                    |     | 0     | 0                       | -       | FFH        |

| FFACH   | Interrupt mask register 0         | МКО                                     | R/W |       |                         | 0       | FFFFH      |

| FFADH   |                                   | IVIKU                                   |     | _     | _                       |         | ггггп      |

| FFADH   | Interrupt mask register 0H        | МКОН                                    |     | 0     | 0                       | -       | FFH        |

| FFB0H   |                                   | ADCR0                                   |     |       |                         | 0       |            |

| FFB1H   | A/D conversion result register 0  | ADCRU                                   |     | _     | _                       |         |            |

| FFB1H   | A/D conversion result register 0H | ADCR0H                                  |     | _     | 0                       | -       |            |

| FFB2H   | A/D conversion requit register 1  |                                         |     |       |                         |         |            |

| FFB3H   | A/D conversion result register 1  | onversion result register 1 ADCR1       |     | _     | _                       | - 0     |            |

| FFB3H   | A/D conversion result register 1H | ADCR1H                                  |     | _     | 0                       | -       |            |

| FFB4H   | A/D conversion result register 2  | ADCR2                                   |     |       |                         | 0       |            |

| FFB5H   | A/D conversion result register 2  | ADORZ                                   |     |       | _                       |         |            |

| FFB5H   | A/D conversion result register 2H | ADCR2H                                  |     | _     | 0                       | -       |            |

| FFB6H   | A/D conversion result register 3  | ADCR3                                   |     |       |                         | 0       |            |

| FFB7H   |                                   | Aberto                                  | R   |       |                         |         | Undefined  |

| FFB7H   | A/D conversion result register 3H | ADCR3H                                  |     | _     | 0                       | -       | Undenned   |

| FFB8H   | A/D conversion result register 4  | ADCR4                                   | 24  | _     | _                       | 0       |            |

| FFB9H   |                                   |                                         |     |       |                         |         |            |

| FFB9H   | A/D conversion result register 4H | ADCR4H                                  |     | _     | 0                       | -       |            |

| FFBAH   | A/D conversion result register 5  | ADCR5                                   |     | _     | _                       | 0       |            |

| FFBBH   |                                   | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | _   |       |                         |         |            |

| FFBBH   | A/D conversion result register 5H | ADCR5H                                  | _   |       | 0                       |         |            |

| FFBCH   | A/D conversion result register 6  | ADCR6                                   |     | _     | _                       | 0       |            |

| FFBDH   |                                   | 1.0010                                  |     |       |                         |         |            |

| FFBDH   | A/D conversion result register 6H | ADCR6H                                  |     | _     | 0                       | -       |            |

| FFBEH   | A/D conversion result register 7  | ADCR7                                   |     | _     | _                       | 0       |            |

| FFBFH   |                                   |                                         |     |       |                         |         |            |

| FFBFH   | A/D conversion result register 7H | ADCR7H                                  |     | _     | 0                       | -       |            |

| FFC0H   | Standby control register          | STBC <sup>Note</sup>                    |     |       | 0                       | -       | 0000 ×000B |

| FFC1H   | CPU control word                  | CCW                                     | R/W | 0     | 0                       | -       | 00H        |

| FFC2H   | Watchdog timer mode register      | WDM <sup>Note</sup>                     |     | _     | 0                       | -       | 0011       |

Table 2-1. List of Special Function Registers (4/5)

**Note** Can be written when a special instruction is executed.

| Address | Special function register (SFR)            | Symbol | R/W   |       | it units f<br>anipulati | -       | On reset  |

|---------|--------------------------------------------|--------|-------|-------|-------------------------|---------|-----------|

|         |                                            |        |       | 1 bit | 8 bits                  | 16 bits |           |

| FFC4H   | Memory expansion mode register             | MM     |       | 0     | 0                       | -       | Note      |

| FFC6H   | Programmable wait control register         | PWC    |       |       |                         | 0       | COAAH     |

| FFC7H   |                                            | FVVC   |       | _     | _                       |         | CUAAN     |

| FFD0H   |                                            |        |       |       |                         |         |           |

|         | External SFR area                          | -      |       | 0     | 0                       | -       | Undefined |

| FFDFH   |                                            |        |       |       |                         |         |           |

| FFE0H   | Interrupt control register (INTOV3)        | OVIC3  |       | 0     | 0                       | -       |           |

| FFE1H   | Interrupt control register (INTP0/INTCC30) | PIC0   |       | 0     | 0                       | -       |           |

| FFE2H   | Interrupt control register (INTP1)         | PIC1   |       | 0     | 0                       | -       |           |

| FFE3H   | Interrupt control register (INTP2)         | PIC2   |       | 0     | 0                       | -       |           |

| FFE4H   | Interrupt control register (INTP3/INTCC20) | PIC3   | R/W   | 0     | 0                       | -       |           |

| FFE5H   | Interrupt control register (INTP4)         | PIC4   | K/ VV | 0     | 0                       | -       |           |

| FFE6H   | Interrupt control register (INTTM0)        | TMIC0  |       | 0     | 0                       | -       |           |

| FFE7H   | Interrupt control register (INTCM03)       | CMIC03 |       | 0     | 0                       | -       | 43H       |

| FFE8H   | Interrupt control register (INTCM10)       | CMIC10 |       | 0     | 0                       | -       | 43N       |

| FFE9H   | Interrupt control register (INTCM40)       | CMIC40 |       | 0     | 0                       | -       |           |

| FFEAH   | Interrupt control register (INTCM41)       | CMIC41 |       | 0     | 0                       | _       |           |

| FFEBH   | Interrupt control register (INTSER)        | SERIC  |       | 0     | 0                       | _       |           |

| FFECH   | Interrupt control register (INTSR)         | SRIC   |       | 0     | 0                       | _       |           |

| FFEDH   | Interrupt control register (INTST)         | STIC   |       | 0     | 0                       | _       |           |

| FFEEH   | Interrupt control register (INTCSI)        | CSIIC  |       | 0     | 0                       | -       |           |

| FFEFH   | Interrupt control register (INTAD)         | ADIC   |       | 0     | 0                       | -       |           |

| Table 2-1. | List of Special | Function | Registers (5/5) |

|------------|-----------------|----------|-----------------|

|------------|-----------------|----------|-----------------|

Note The value of the MW register at reset time differs depending on the product.

μPD78363A : 60H μPD78365A, 78366A : 20H μPD78368A : 00H

\*

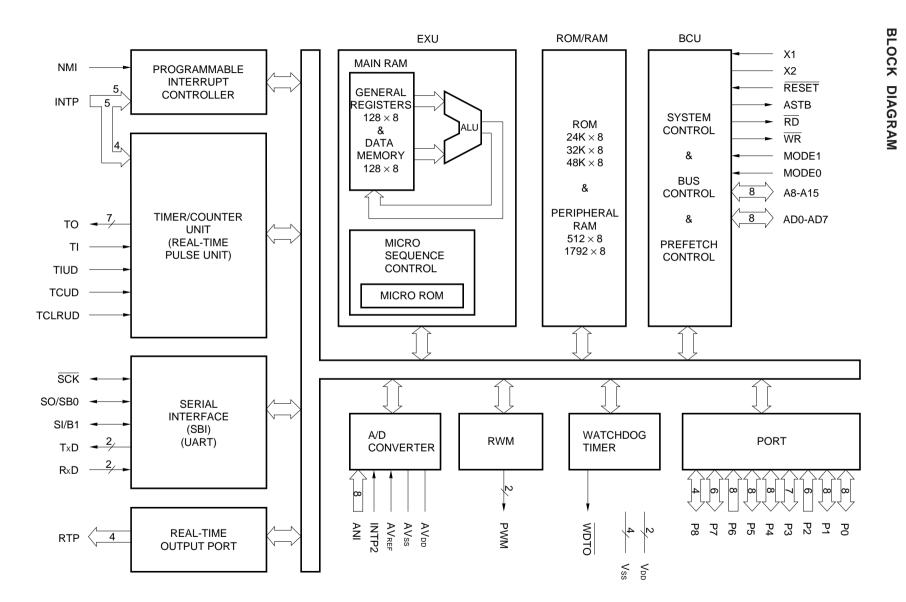

#### 3. FUNCTIONAL BLOCKS

#### 3.1 EXECUTION UNIT (EXU)

EXU controls address computation, arithmetic and logical operations, and data transfer through microprogram. EXU has an internal main RAM. This RAM can be accessed by instructions faster than the peripheral RAM.

#### 3.2 BUS CONTROL UNIT (BCU)

BCU starts necessary bus cycles according to the physical address obtained by the execution unit (EXU). If EXU does not request start of the bus cycle, an address is generated to prefetch an instruction. The prefetched op code is stored in an instruction queue.

#### 3.3 ROM/RAM

The internal ROM and RAM capacities differ depending on the product.

The  $\mu$ PD78363A has a 24-KB ROM and a 512-B peripheral RAM. The  $\mu$ PD78366A has a 32-KB ROM and a 1792-B peripheral RAM. The  $\mu$ PD78368A has a 48-KB ROM and a 1792-B peripheral RAM. The  $\mu$ PD78365A does not have a ROM and only has a 1792-B peripheral RAM.

Access to the ROM can be disabled by using the MODE0 and MODE1 pins, in which case an external memory of 64 KB can be accessed.

#### 3.4 PORT FUNCTIONS

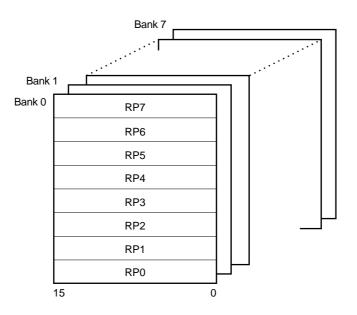

The  $\mu$ PD78366A is provided with the ports shown in Figure 3-1 for various control operations.

The functions of each port are listed in Table 3-1. These ports function not only as digital ports but also as input/output lines of the internal hardware.

Figure 3-1. Port Configuration

| Port   | Port function                                                      | Multiplexed function                                                                                                                           |

|--------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Port 0 | 8-bit I/O port. Can be set in input or output mode in 1-bit units. | In control mode, serves as real-time output port (RTP), or input operation control signal of real-time pulse unit (RPU) and output PWM signal. |

| Port 1 | 8-bit I/O port. Can be set in input or output mode in 1-bit units. | _                                                                                                                                              |

| Port 2 | 6-bit input port.                                                  | Inputs external interrupt and count pulse of real-time pulse<br>unit (RPU) (fixed to the control mode).                                        |

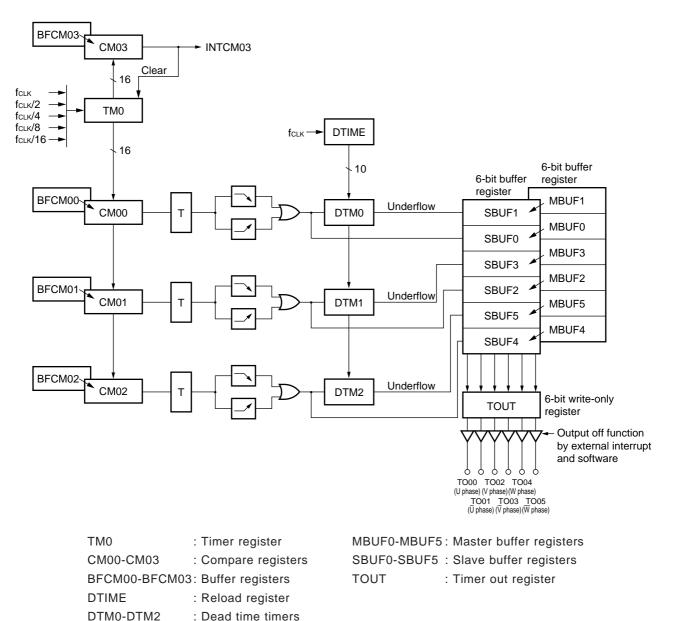

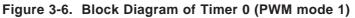

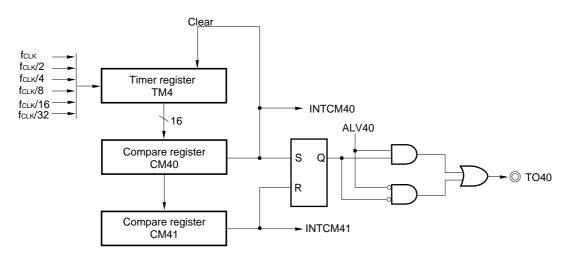

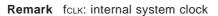

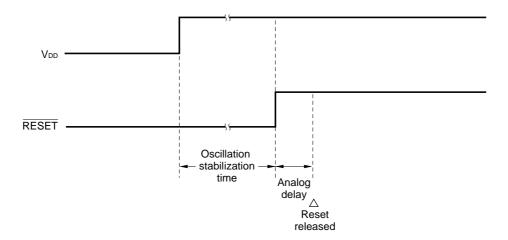

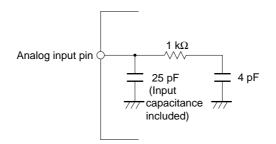

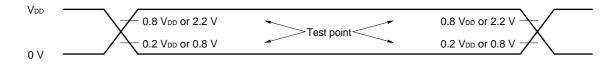

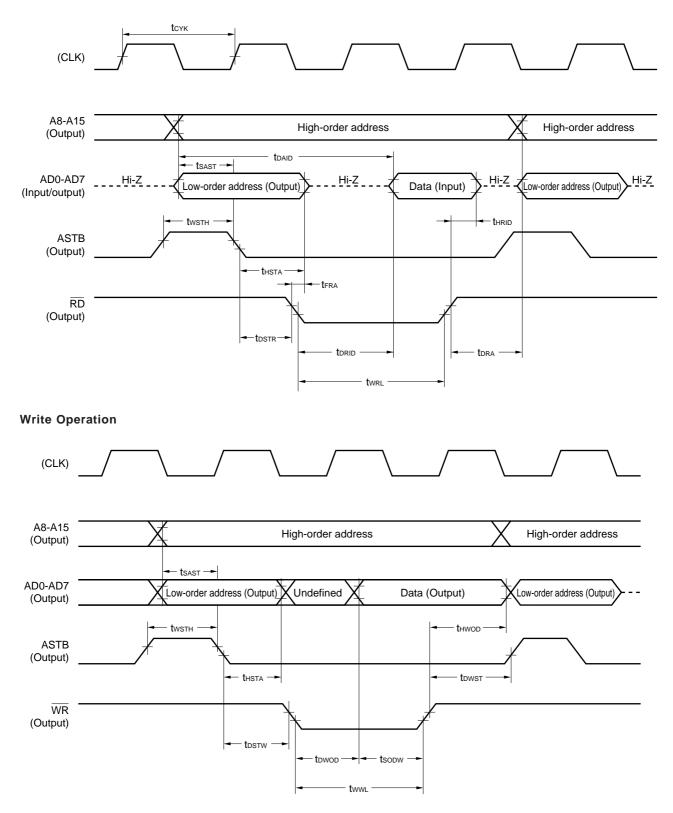

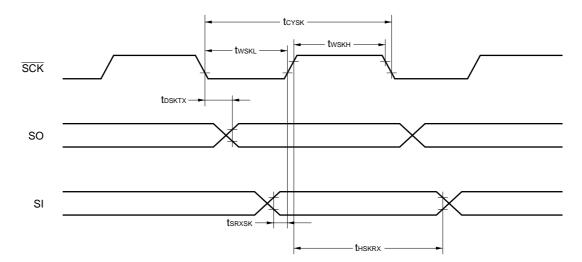

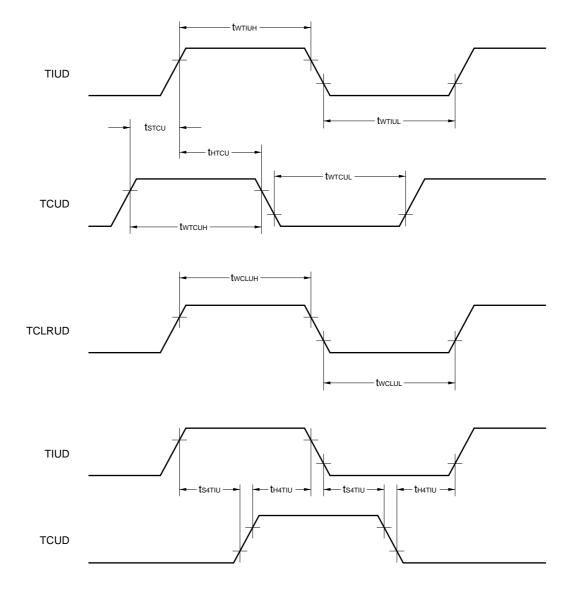

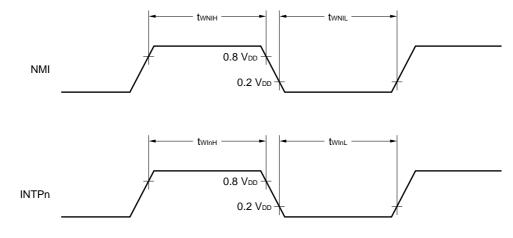

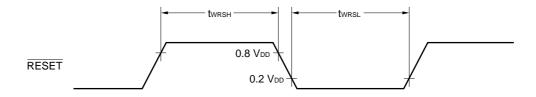

| Port 3 | 7-bit I/O port. Can be set in input or output in 1-bit units.      | In control mode, inputs/outputs signals of serial interfaces (UART, CSI).                                                                      |