# mos integrated circuit $\mu$ PD78F0034A, 78F0034AY

### 8-BIT SINGLE-CHIP MICROCONTROLLER

#### **DESCRIPTION**

The  $\mu$ PD78F0034A is a member of the  $\mu$ PD780034A Subseries in the 78K/0 Series, and is equivalent to the  $\mu$ PD780034A but with flash memory in place of internal ROM.

The  $\mu$ PD78F0034AY is a member of the  $\mu$ PD780034AY Subseries, featuring flash memory in place of the internal ROM of the  $\mu$ PD780034AY.

The  $\mu$ PD78F0034A incorporates flash memory, which can be programmed and erased while mounted on the board.

Detailed function descriptions are provided in the following user's manuals. Be sure to read them before designing.

$\mu$ PD780024A, 780034A, 780024AY, 780034AY Subseries User's Manual: U14046E 78K/0 Series Instruction User's Manual: U12326E

#### **FEATURES**

Pin-compatible with mask ROM versions (except VPP pin)

Flash memory: 32 KB<sup>Note</sup>

Internal high-speed RAM: 1,024 bytes<sup>Note</sup>

Supply voltage: VDD = 1.8 to 5.5 V

**Note** The flash memory and internal high-speed RAM capacities can be changed with the memory size switching register (IMS).

**Remark** For the differences between the flash memory and the mask ROM versions, refer to **4. DIFFERENCES BETWEEN**  $\mu$ **PD78F0034A, 78F0034AY, AND MASK ROM VERSIONS**.

#### ★ ORDERING INFORMATION

| Part Number             | Package                              | Internal ROM |

|-------------------------|--------------------------------------|--------------|

| $\mu$ PD78F0034ACW      | 64-pin plastic SDIP (19.05 mm (750)) | Flash memory |

| $\mu$ PD78F0034AGB-8EU  | 64-pin plastic LQFP (10 $\times$ 10) | Flash memory |

| $\mu$ PD78F0034AGC-8BS  | 64-pin plastic LQFP (14 $\times$ 14) | Flash memory |

| $\mu$ PD78F0034AGC-AB8  | 64-pin plastic QFP (14 $\times$ 14)  | Flash memory |

| $\mu$ PD78F0034AGK-9ET  | 64-pin plastic TQFP (12 $\times$ 12) | Flash memory |

| $\mu$ PD78F0034AYCW     | 64-pin plastic SDIP (19.05 mm (750)) | Flash memory |

| $\mu$ PD78F0034AYGB-8EU | 64-pin plastic LQFP (10 $\times$ 10) | Flash memory |

| $\mu$ PD78F0034AYGC-8BS | 64-pin plastic LQFP (14 × 14)        | Flash memory |

| $\mu$ PD78F0034AYGC-AB8 | 64-pin plastic QFP (14 $\times$ 14)  | Flash memory |

| $\mu$ PD78F0034AYGK-9ET | 64-pin plastic TQFP (12 $\times$ 12) | Flash memory |

The information in this document is subject to change without notice. Before using this document, please confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for availability and additional information.

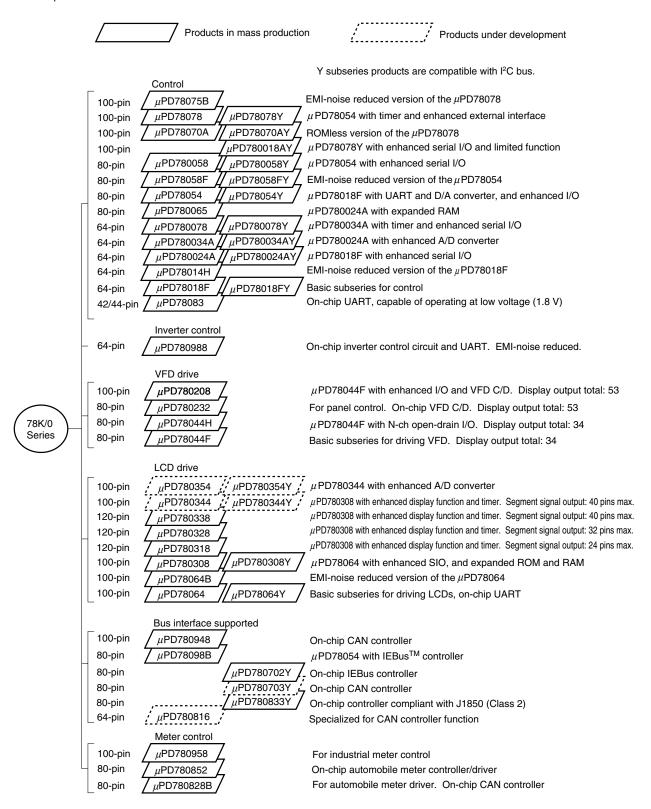

#### **★** 78K/0 SERIES LINEUP

The products in the 78K/0 Series are listed below. The names enclosed in boxes are subseries names.

**Remark** VFD (Vacuum Fluorescent Display) is referred to as FIP<sup>TM</sup> (Fluorescent Indicator Panel) in some documents, but the functions of the two are the same.

The major functional differences among the subseries are listed below.

# Non-Y subseries

|                  | Function       | ROM<br>Capacity |       | Tin    | ner   |      | 8-Bit | 10-Bit | 8-Bit | Serial Interface                | I/O | V <sub>DD</sub> | External  |

|------------------|----------------|-----------------|-------|--------|-------|------|-------|--------|-------|---------------------------------|-----|-----------------|-----------|

| Subseries        | Name           | (Bytes)         | 8-Bit | 16-Bit | Watch | WDT  | A/D   | A/D    | D/A   |                                 |     | Value           | Expansion |

| Control          | μPD78075B      | 32 K to 40 K    | 4 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      | 2 ch  | 3 ch (UART: 1 ch)               | 88  | 1.8 V           | √         |

|                  | μPD78078       | 48 K to 60 K    |       |        |       |      |       |        |       |                                 |     |                 |           |

|                  | μPD78070A      | _               |       |        |       |      |       |        |       |                                 | 61  | 2.7 V           |           |

|                  | $\mu$ PD780058 | 24 K to 60 K    | 2 ch  |        |       |      |       |        |       | 3 ch (time-division UART: 1 ch) | 68  | 1.8 V           |           |

|                  | $\mu$ PD78058F | 48 K to 60 K    |       |        |       |      |       |        |       | 3 ch (UART: 1 ch)               | 69  | 2.7 V           |           |

|                  | μPD78054       | 16 K to 60 K    |       |        |       |      |       |        |       |                                 |     | 2.0 V           |           |

|                  | μPD780065      | 40 K to 48 K    |       |        |       |      |       |        | -     | 4 ch (UART: 1 ch)               | 60  | 2.7 V           |           |

|                  | μPD780078      | 48 K to 60 K    |       | 2 ch   |       |      | _     | 8 ch   |       | 3 ch (UART: 2 ch)               | 52  | 1.8 V           |           |

|                  | μPD780034A     | 8 K to 32 K     |       | 1 ch   |       |      |       |        |       | 3 ch (UART: 1 ch)               | 51  |                 |           |

|                  | μPD780024A     |                 |       |        |       |      | 8 ch  | _      |       |                                 |     |                 |           |

|                  | μPD78014H      |                 |       |        |       |      |       |        |       | 2 ch                            | 53  |                 |           |

|                  | μPD78018F      | 8 K to 60 K     |       |        |       |      |       |        |       |                                 |     |                 |           |

|                  | μPD78083       | 8 K to 16 K     |       | _      | _     |      |       |        |       | 1 ch (UART: 1 ch)               | 33  |                 | _         |

| Inverter control | μPD780988      | 16 K to 60 K    | 3 ch  | Note   | ı     | 1 ch | _     | 8 ch   | _     | 3 ch (UART: 2 ch)               | 47  | 4.0 V           | √         |

| VFD              | μPD780208      | 32 K to 60 K    | 2 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      | _     | 2 ch                            | 74  | 2.7 V           | -         |

| drive            | μPD780232      | 16 K to 24 K    | 3 ch  | _      | _     |      | 4 ch  |        |       |                                 | 40  | 4.5 V           |           |

|                  | μPD78044H      | 32 K to 48 K    | 2 ch  | 1 ch   | 1 ch  |      | 8 ch  |        |       | 1 ch                            | 68  | 2.7 V           |           |

|                  | μPD78044F      | 16 K to 40 K    |       |        |       |      |       |        |       | 2 ch                            |     |                 |           |

| LCD              | μPD780354      | 24 K to 32 K    | 4 ch  | 1 ch   | 1 ch  | 1 ch | _     | 8 ch   | _     | 3 ch (UART: 1 ch)               | 66  | 1.8 V           | _         |

| drive            | μPD780344      |                 |       |        |       | ·    | 8 ch  | _      |       |                                 |     |                 |           |

|                  | μPD780338      | 48 K to 60 K    | 3 ch  | 2 ch   |       |      | _     | 10 ch  | 1 ch  | 2 ch (UART: 1 ch)               | 54  |                 |           |

|                  | μPD780328      |                 |       |        |       |      |       |        |       |                                 | 62  |                 |           |

|                  | μPD780318      |                 |       |        |       |      |       |        |       |                                 | 70  |                 |           |

|                  | μPD780308      | 48 K to 60 K    | 2 ch  | 1 ch   |       |      | 8 ch  | _      | _     | 3 ch (time-division UART: 1 ch) | 57  | 2.0 V           |           |

|                  | μPD78064B      | 32 K            |       |        |       |      |       |        |       | 2 ch (UART: 1 ch)               |     |                 |           |

|                  | μPD78064       | 16 K to 32 K    |       |        |       |      |       |        |       |                                 |     |                 |           |

| Bus              | μPD780948      | 60 K            | 2 ch  | 2 ch   | 1 ch  | 1 ch | 8 ch  | _      | _     | 3 ch (UART: 1 ch)               | 79  | 4.0 V           | √         |

| interface        | μPD78098B      | 40 K to 60 K    |       | 1 ch   |       |      |       |        | 2 ch  |                                 | 69  | 2.7 V           | _         |

| supported        | μPD780816      | 32 K to 60 K    |       | 2 ch   |       |      | 12 ch |        | _     | 2 ch (UART: 1 ch)               | 46  | 4.0 V           |           |

| Meter<br>control | μPD780958      | 48 K to 60 K    | 4 ch  | 2 ch   | _     | 1 ch | -     | _      | _     | 2 ch (UART: 1 ch)               | 69  | 2.2 V           | _         |

| Dash-            | μPD780852      | 32 K to 40 K    | 3 ch  | 1 ch   | 1 ch  | 1 ch | 5 ch  | -      | -     | 3 ch (UART: 1 ch)               | 56  | 4.0 V           | _         |

| board<br>control | μPD780828B     | 32 K to 60 K    |       |        |       |      |       |        |       |                                 | 59  |                 |           |

Note 16-bit timer: 2 channels 10-bit timer: 1 channel

# Y subseries

|           | Function    | ROM<br>Capacity |       | Tin    | ner   |      | 8-Bit | 10-Bit | 8-Bit | Serial Interface                                        | I/O | V <sub>DD</sub> | External  |

|-----------|-------------|-----------------|-------|--------|-------|------|-------|--------|-------|---------------------------------------------------------|-----|-----------------|-----------|

| Subseries | Name        | (Bytes)         | 8-Bit | 16-Bit | Watch | WDT  | A/D   | A/D    | D/A   |                                                         |     | Value           | Expansion |

| Control   | μPD78078Y   | 48 K to 60 K    | 4 ch  | 1 ch   | 1 ch  | 1 ch | 8 ch  | _      | 2 ch  | 3 ch (UART: 1 ch, I <sup>2</sup> C: 1 ch)               | 88  | 1.8 V           | <b>√</b>  |

|           | μPD78070AY  | -               |       |        |       |      |       |        |       |                                                         | 61  | 2.7 V           |           |

|           | μPD780018AY | 48 K to 60 K    |       |        |       |      |       |        | -     | 3 ch (I <sup>2</sup> C: 1 ch)                           | 88  |                 |           |

|           | μPD780058Y  | 24 K to 60 K    | 2 ch  |        |       |      |       |        | 2 ch  | 3 ch (time-division UART: 1 ch, I <sup>2</sup> C: 1 ch) | 68  | 1.8 V           |           |

|           | μPD78058FY  | 48 K to 60 K    |       |        |       |      |       |        |       | 3 ch (UART: 1 ch, I <sup>2</sup> C: 1 ch)               | 69  | 2.7 V           |           |

|           | μPD78054Y   | 16 K to 60 K    |       |        |       |      |       |        |       |                                                         |     | 2.0 V           |           |

|           | μPD780078Y  | 48 K to 60 K    |       | 2 ch   |       |      | _     | 8 ch   | _     | 4 ch (UART: 2 ch, I <sup>2</sup> C: 1 ch)               | 52  | 1.8 V           |           |

|           | μPD780034AY | 8 K to 32 K     |       | 1 ch   |       |      |       |        |       | 3 ch (UART: 1 ch, I <sup>2</sup> C: 1 ch)               | 51  |                 |           |

|           | μPD780024AY |                 |       |        |       |      | 8 ch  | _      |       |                                                         |     |                 |           |

|           | μPD78018FY  | 8 K to 60 K     |       |        |       |      |       |        |       | 2 ch (I <sup>2</sup> C: 1 ch)                           | 53  |                 |           |

| LCD       | μPD780354Y  | 24 K to 32 K    | 4 ch  | 1 ch   | 1 ch  | 1 ch | _     | 8 ch   | _     | 4 ch (UART: 1 ch,                                       | 66  | 1.8 V           | -         |

| drive     | μPD780344Y  |                 |       |        |       |      | 8 ch  | _      |       | I <sup>2</sup> C: 1 ch)                                 |     |                 |           |

|           | μPD780308Y  | 48 K to 60 K    | 2 ch  |        |       |      |       |        |       | 3 ch (time-division UART: 1 ch, I <sup>2</sup> C: 1 ch) | 57  | 2.0 V           |           |

|           | μPD78064Y   | 16 K to 32 K    |       |        |       |      |       |        |       | 2 ch (UART: 1 ch, I <sup>2</sup> C: 1 ch)               |     |                 |           |

| Bus       | μPD780701Y  | 60 K            | 3 ch  | 2 ch   | 1 ch  | 1 ch | 16 ch | _      | _     | 4 ch (UART: 1 ch, I <sup>2</sup> C: 1 ch)               | 67  | 3.5 V           |           |

|           | μPD780703Y  |                 |       |        |       |      |       |        |       |                                                         |     |                 |           |

| supported | μPD780833Y  |                 |       |        |       |      |       |        |       |                                                         | 65  | 4.5 V           |           |

**Remark** Functions other than the serial interface are common to both the Y and non-Y subseries.

4 Data Sheet U14040EJ4V0DS www.DataSheet4U.com

# **OVERVIEW OF FUNCTIONS**

| Item             | Part Number                     | μPD78F0034A μPD78F0034AY                                                                                                                                                                   |                                                                                                                           |  |  |  |  |  |

|------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Internal         | Flash memory                    | 32 KB <sup>Note</sup>                                                                                                                                                                      |                                                                                                                           |  |  |  |  |  |

| memory           | High-speed RAM                  | 1,024 bytes <sup>Note</sup>                                                                                                                                                                |                                                                                                                           |  |  |  |  |  |

| Memory space     |                                 | 64 KB                                                                                                                                                                                      |                                                                                                                           |  |  |  |  |  |

| General-purpose  | e registers                     | 8 bits × 32 registers (8 bits × 8 registers ×                                                                                                                                              | 4 banks)                                                                                                                  |  |  |  |  |  |

| Minimum instruc  | tion execution time             | On-chip minimum instruction execution tim                                                                                                                                                  | ne cycle variable function                                                                                                |  |  |  |  |  |

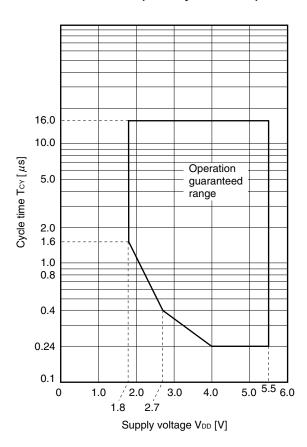

|                  | When main system clock selected | 0.24 μs/0.48 μs/0.95 μs/1.91 μs/3.81 μs ( (                                                                                                                                                |                                                                                                                           |  |  |  |  |  |

|                  | When subsystem clock selected   | 122 μs (@ 32.768 kHz operation)                                                                                                                                                            |                                                                                                                           |  |  |  |  |  |

| Instruction set  |                                 | <ul> <li>16-bit operation</li> <li>Multiply/divide (8 bits × 8 bits, 16 bits ÷ 8</li> <li>Bit manipulation (set, reset, test, Boolean</li> <li>BCD adjust, etc.</li> </ul>                 | ,                                                                                                                         |  |  |  |  |  |

| I/O ports        |                                 | Total:                                                                                                                                                                                     | 51                                                                                                                        |  |  |  |  |  |

|                  |                                 | CMOS input: CMOS I/O: N-ch open-drain I/O (5 V withstand voltage)                                                                                                                          | 8<br>39<br>ge): 4                                                                                                         |  |  |  |  |  |

| A/D converter    |                                 | <ul> <li>10-bit resolution × 8 channels</li> <li>Operable over a wide power supply voltage range: AV<sub>DD</sub> = 1.8 to 5.5 V</li> </ul>                                                |                                                                                                                           |  |  |  |  |  |

| Serial interface |                                 | UART mode: 1 channel     3-wire serial I/O mode: 2 channels                                                                                                                                | UART mode:  1 channel  3-wire serial I/O mode:  1 channel  1 <sup>2</sup> C bus mode  (multimaster supporting): 1 channel |  |  |  |  |  |

| Timers           |                                 | 16-bit timer/event counter: 1 channel     8-bit timer/event counter: 2 channels     Watch timer: 1 channel     Watchdog timer: 1 channel                                                   |                                                                                                                           |  |  |  |  |  |

| Timer outputs    |                                 | 3 (8-bit PWM output capable: 2)                                                                                                                                                            | •                                                                                                                         |  |  |  |  |  |

| Clock output     |                                 | 65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.10 MHz, 4.19 MHz, 8.38 MHz     (@ 8.38 MHz operation with main system clock)     32.768 kHz (@ 32.768 kHz operation with subsystem clock) |                                                                                                                           |  |  |  |  |  |

| Buzzer output    |                                 | 1.02 kHz, 2.05 kHz, 4.10 kHz, 8.19 kHz (@                                                                                                                                                  | 8.38 MHz operation with main system clock)                                                                                |  |  |  |  |  |

| Vectored interru | pt Maskable                     | Internal: 13, external: 5                                                                                                                                                                  |                                                                                                                           |  |  |  |  |  |

| sources          | Non-maskable                    | Internal: 1                                                                                                                                                                                |                                                                                                                           |  |  |  |  |  |

|                  | Software                        | 1                                                                                                                                                                                          |                                                                                                                           |  |  |  |  |  |

| Test inputs      |                                 | Internal: 1, external: 1                                                                                                                                                                   |                                                                                                                           |  |  |  |  |  |

| Supply voltage   |                                 | V <sub>DD</sub> = 1.8 to 5.5 V                                                                                                                                                             |                                                                                                                           |  |  |  |  |  |

| Operating ambie  | ent temperature                 | T <sub>A</sub> = -40 to +85°C                                                                                                                                                              |                                                                                                                           |  |  |  |  |  |

| Package          |                                 | 64-pin plastic SDIP (19.05 mm (750))     64-pin plastic LQFP (10 × 10)     64-pin plastic LQFP (14 × 14)     64-pin plastic QFP (14 × 14)     64-pin plastic TQFP (12 × 12)                |                                                                                                                           |  |  |  |  |  |

**Note** The capacities of the flash memory and the internal high-speed RAM can be changed with the memory size switching register (IMS).

# **CONTENTS**

| 1. | PIN CONFIGURATION (TOP VIEW)                                           | 7  |

|----|------------------------------------------------------------------------|----|

| 2. | BLOCK DIAGRAM                                                          | 10 |

| 3. | PIN FUNCTIONS                                                          | 11 |

|    | 3.1 Port Pins                                                          | 11 |

|    | 3.2 Non-Port Pins                                                      | 12 |

|    | 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins         | 14 |

| 4. | DIFFERENCES BETWEEN $\mu$ PD78F0034A, 78F0034AY, AND MASK ROM VERSIONS | 17 |

| 5. | MEMORY SIZE SWITCHING REGISTER (IMS)                                   | 19 |

| 6. | FLASH MEMORY PROGRAMMING                                               | 20 |

|    | 6.1 Selection of Communication Mode                                    | 20 |

|    | 6.2 Flash Memory Programming Functions                                 | 22 |

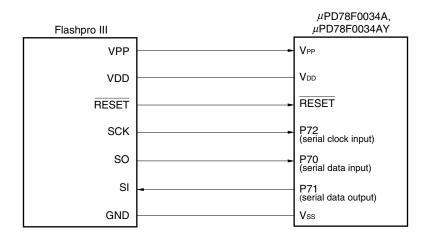

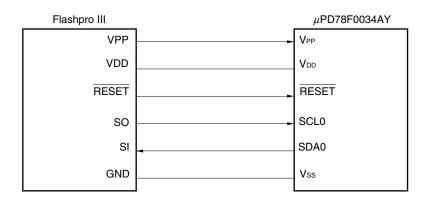

|    | 6.3 Connection of Flashpro III                                         | 22 |

| 7. | ELECTRICAL SPECIFICATIONS                                              | 24 |

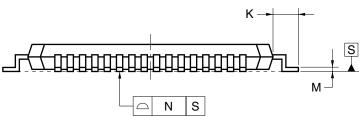

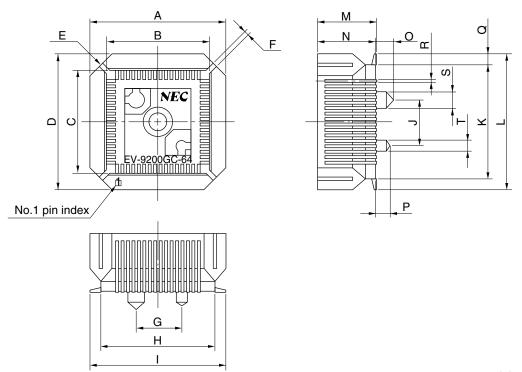

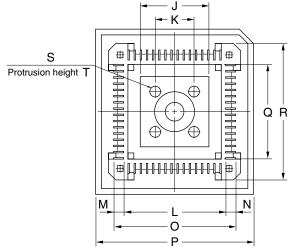

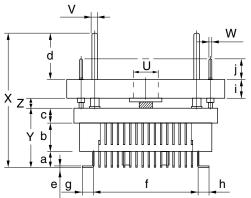

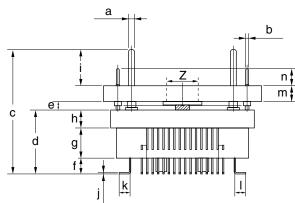

| 8. | PACKAGE DRAWINGS                                                       | 47 |

| 9. | RECOMMENDED SOLDERING CONDITIONS                                       | 52 |

| ΑP | PPENDIX A. DEVELOPMENT TOOLS                                           | 54 |

| ΛP | PRENDLY R. DELATED DOCUMENTS                                           | 61 |

www.DataSheet4U.com

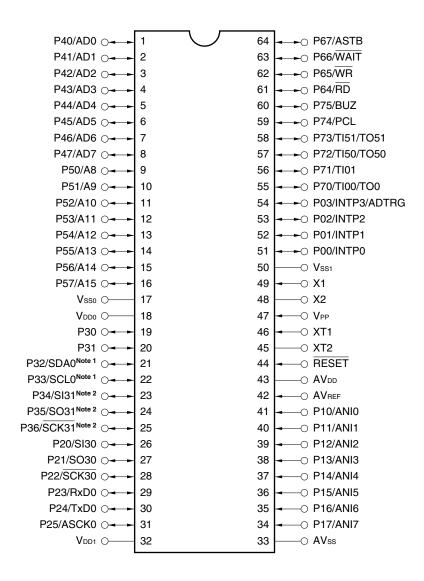

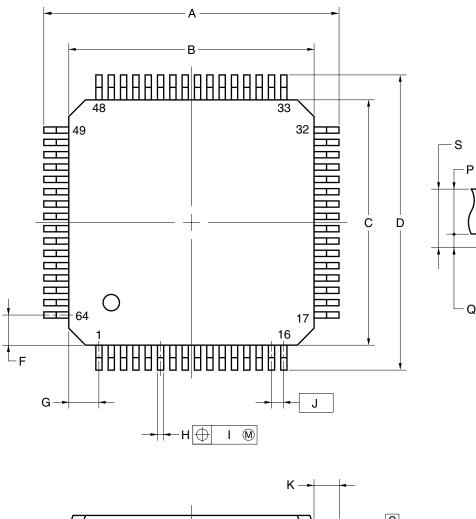

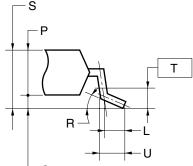

### 1. PIN CONFIGURATION (TOP VIEW)

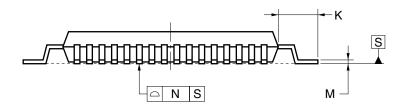

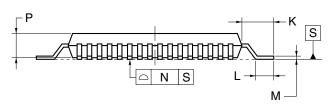

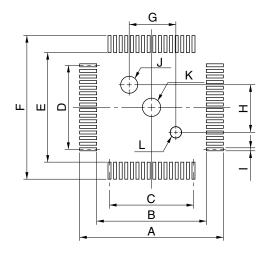

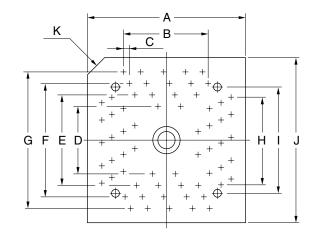

64-pin plastic SDIP (19.05 mm (750))

μPD78F0034ACW, 78F0034AYCW

- **Notes 1.** SDA0 and SCL0 are incorporated only in the  $\mu$ PD78F0034AY Subseries.

- **2.** SI31, SO31, and SCK31 are incorporated only in the  $\mu$ PD78F0034A Subseries.

- Cautions 1. Connect the VPP pin directly to Vsso or Vss1 in normal operation mode.

- 2. Connect the AVss pin to Vsso.

**Remark** When the μPD78F0034A and 78F0034AY are used in application fields that require reduction of the noise generated from inside the microcontroller, the implementation of noise reduction measures, such as supplying voltage to V<sub>DD0</sub> and V<sub>DD1</sub> individually and connecting V<sub>SS0</sub> and V<sub>SS1</sub> to different ground lines, is recommended.

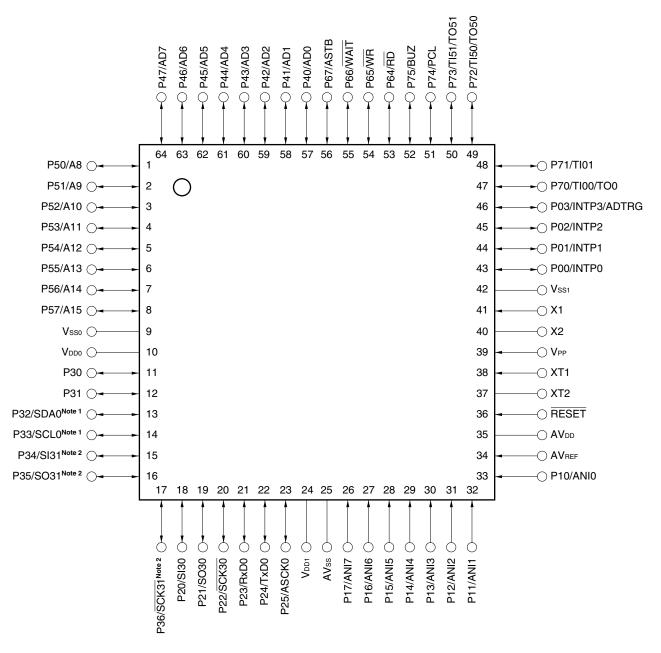

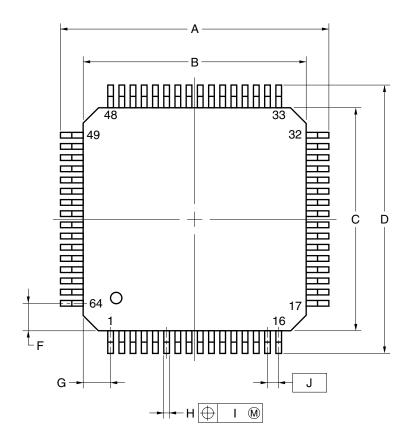

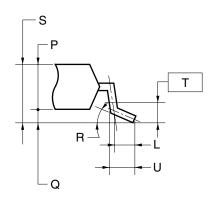

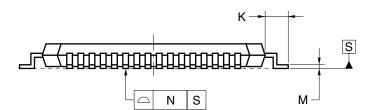

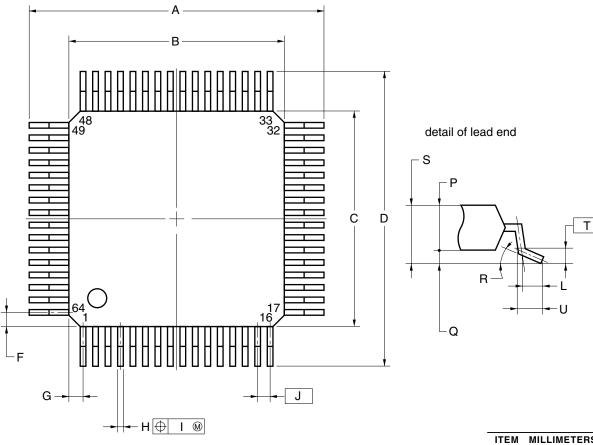

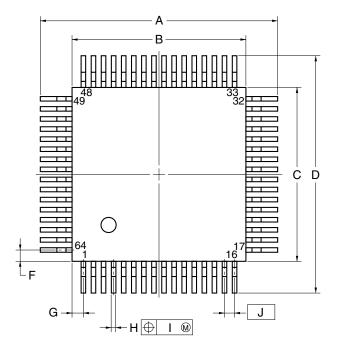

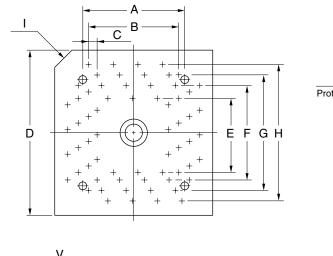

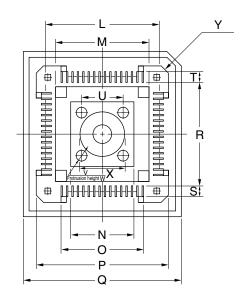

- 64-pin plastic LQFP ( $10 \times 10$ )  $\mu$ PD78F0034AGB-8EU, 78F0034AYGB-8EU

- 64-pin plastic LQFP (14  $\times$  14) μPD78F0034AGC-8BS, 78F0034AYGC-8BS

- 64-pin plastic QFP (14  $\times$  14)  $\mu$ PD78F0034AGC-AB8, 78F0034AYGC-AB8

- 64-pin plastic TQFP (12  $\times$  12)  $\mu$ PD78F0034AGK-9ET, 78F0034AYGK-9ET

- **Notes 1.** SDA0 and SCL0 are incorporated only in the  $\mu$ PD78F0034AY Subseries.

- 2. SI31, SO31, and  $\overline{SCK31}$  are incorporated only in the  $\mu$ PD78F0034A Subseries.

- Cautions 1. Connect the VPP pin directly to Vsso or Vss1 in normal operation mode.

- 2. Connect the AVss pin to Vsso.

- **Remark** When the  $\mu$ PD78F0034A and 78F0034AY are used in application fields that require reduction of the noise generated from inside the microcontroller, the implementation of noise reduction measures, such as supplying voltage to VDD0 and VDD1 individually and connecting Vss0 and Vss1 to different ground lines, is recommended.

P00 to P03:

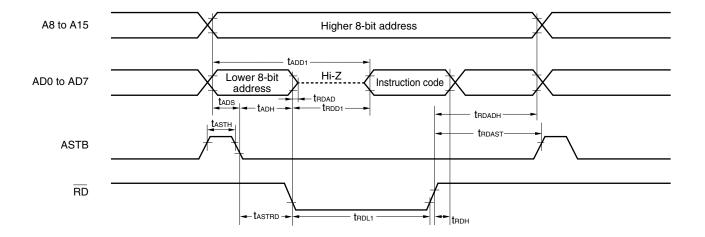

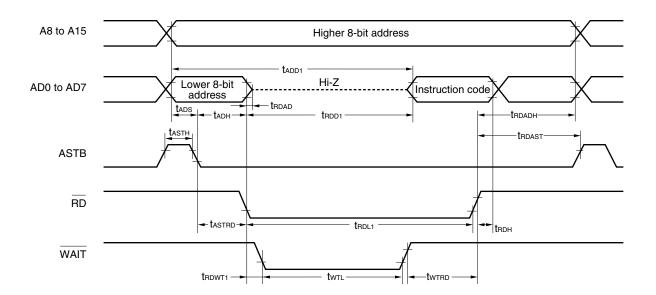

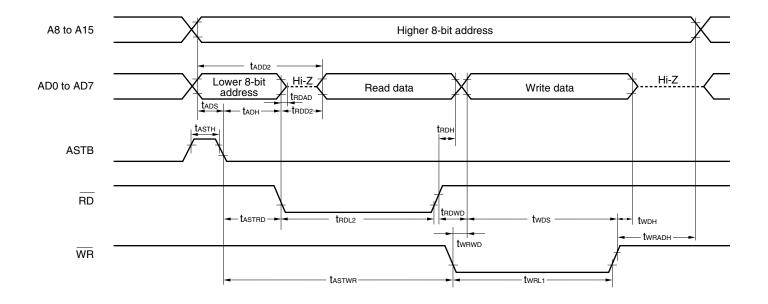

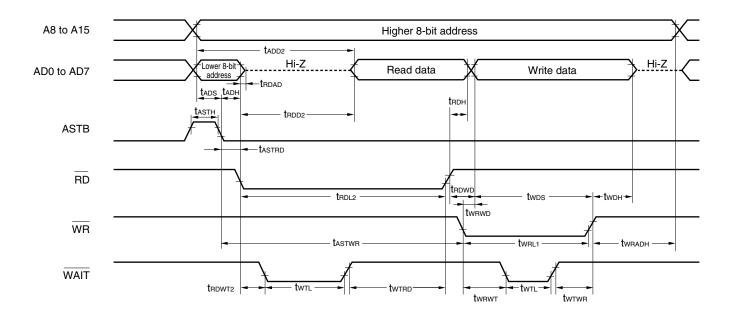

A8 to A15: Address bus P70 to P75: Port 7

AD0 to AD7: Address/data bus PCL: Programmable clock

ADTRG: RD: Read strobe AD trigger input ANI0 to ANI7: RESET: Reset

Analog input ASCK0: Asynchronous serial clock RxD0: Receive data

ASTB: Address strobe SCK30, SCK31, SCL0: Serial clock SDA0: AV<sub>DD</sub>: Analog power supply Serial data AVREF: Analog reference voltage SI30, SI31: Serial input

AVss: Analog ground SO30, SO31: Serial output BUZ: Buzzer clock TI00, TI01, TI50, TI51: Timer input INTP0 to INTP3: External interrupt input TO0, TO50, TO51: Timer output Port 0

P10 to P17: V<sub>DD0</sub>, V<sub>DD1</sub>: Port 1 Power supply Port 2 V<sub>PP</sub>: P20 to P25: Programming power supply

TxD0:

P30 to P36: Port 3 Vsso, Vss1: Ground WAIT: P40 to P47: Port 4 Wait

WR: P50 to P57: Port 5 Write strobe

X1, X2: P64 to P67: Port 6 Crystal (main system clock)

XT1, XT2: Crystal (subsystem clock)

Transmit data

#### www.bataoncct+o.com

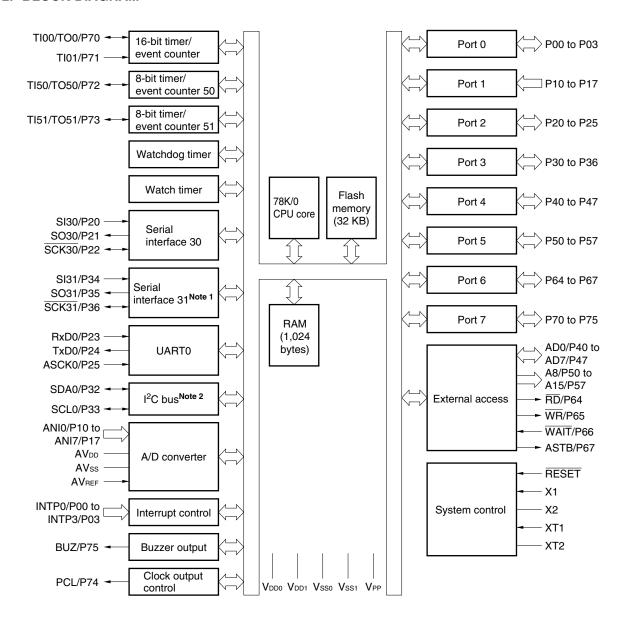

#### 2. BLOCK DIAGRAM

**Notes 1.** Incorporated only in the  $\mu$ PD78F0034A

2. Incorporated only in the  $\mu$ PD78F0034AY

# 3. PIN FUNCTIONS

# 3.1 Port Pins (1/2)

| Pin Name   | I/O   |                                                                                                                    | Function                           | After Reset | Alternate<br>Function  |

|------------|-------|--------------------------------------------------------------------------------------------------------------------|------------------------------------|-------------|------------------------|

| P00        | I/O   | Port 0                                                                                                             |                                    | Input       | INTP0                  |

| P01        |       | 4-bit I/O port.                                                                                                    |                                    | INTP1       |                        |

| P02        |       | Input/output can be specified  An on-chip pull-up resistor ca                                                      |                                    |             | INTP2                  |

| P03        |       | An on-chip pull-up resistor ca                                                                                     | n be specified by software.        |             | INTP3/ADTRG            |

| P10 to P17 | Input | Port 1 8-bit input-only port.                                                                                      |                                    | Input       | ANI0 to ANI7           |

| P20        | I/O   | Port 2                                                                                                             |                                    | Input       | SI30                   |

| P21        |       | 6-bit I/O port.                                                                                                    |                                    |             | SO30                   |

| P22        |       | Input/output can be specified                                                                                      |                                    |             | SCK30                  |

| P23        |       | An on-chip pull-up resistor ca                                                                                     | n be specified by software.        |             | RxD0                   |

| P24        |       |                                                                                                                    |                                    |             | TxD0                   |

| P25        |       |                                                                                                                    |                                    |             | ASCK0                  |

| P30        | I/O   | Port 3                                                                                                             | N-ch open-drain I/O port.          | Input       | -                      |

| P31        |       | 7-bit I/O port.                                                                                                    | LEDs can be driven directly.       |             |                        |

| P32        |       | Input/output can be specified                                                                                      |                                    |             | SDA0 <sup>Note 1</sup> |

| P33        |       | in 1-bit units.                                                                                                    |                                    |             | SCL0 <sup>Note 1</sup> |

| P34        |       |                                                                                                                    | An on-chip pull-up resistor can be |             | SI31 Note 2            |

| P35        |       |                                                                                                                    | specified by software.             |             | SO31 <sup>Note 2</sup> |

| P36        |       |                                                                                                                    |                                    |             | SCK31 Note 2           |

| P40 to P47 | I/O   | Port 4 8-bit I/O port. Input/output can be specified An on-chip pull-up resistor ca Interrupt request flag KRIF is |                                    | Input       | AD0 to AD7             |

| P50 to P57 | I/O   | Port 5 8-bit I/O port. LEDs can be driven directly. Input/output can be specified An on-chip pull-up resistor ca   |                                    | Input       | A8 to A15              |

| P64        | I/O   | Port 6                                                                                                             |                                    | Input       | RD                     |

| P65        |       | 4-bit I/O port.                                                                                                    |                                    |             | WR                     |

| P66        |       | Input/output can be specified An on-chip pull-up resistor ca                                                       |                                    |             | WAIT                   |

| P67        |       | An on-only pull-up resistor ca                                                                                     | ii be specified by software.       |             | ASTB                   |

**Notes 1.** SDA0 and SCL0 are incorporated only in the  $\mu$ PD78F0034AY Subseries.

2. SI31, SO31, and  $\overline{\text{SCK31}}$  are incorporated only in the  $\mu\text{PD78F0034A}$  Subseries.

3.1 Port Pins (2/2)

| Pin Name | I/O | Function                                                                                                 | After Reset | Alternate<br>Function |

|----------|-----|----------------------------------------------------------------------------------------------------------|-------------|-----------------------|

| P70      | I/O | Port 7                                                                                                   | Input       | TI00/TO0              |

| P71      |     | 6-bit I/O port.                                                                                          |             | TI01                  |

| P72      |     | Input/output can be specified in 1-bit units.  An on-chip pull-up resistor can be specified by software. |             | TI50/TO50             |

| P73      |     | All off-only pull-up resistor can be specified by software.                                              |             | TI51/TO51             |

| P74      |     |                                                                                                          |             | PCL                   |

| P75      |     |                                                                                                          |             | BUZ                   |

# 3.2 Non-Port Pins (1/2)

| Pin Name               | I/O    | Function                                                                                                                                                 | After Reset | Alternate<br>Function |

|------------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------|

| INTP0                  | Input  | External interrupt request input by which the valid edge (rising edge,                                                                                   | Input       | P00                   |

| INTP1                  |        | falling edge, or both rising and falling edges) can be specified.                                                                                        |             | P01                   |

| INTP2                  |        |                                                                                                                                                          |             | P02                   |

| INTP3                  |        |                                                                                                                                                          |             | P03/ADTRG             |

| SI30                   | Input  | Serial interface serial data input.                                                                                                                      | Input       | P20                   |

| SI31 Note 1            |        |                                                                                                                                                          |             | P34                   |

| SDA0 <sup>Note 2</sup> | I/O    | Serial interface serial data input/output                                                                                                                | Input       | P32                   |

| SO30                   | Output | Serial interface serial data output.                                                                                                                     | Input       | P21                   |

| SO31 <sup>Note 1</sup> |        |                                                                                                                                                          |             | P35                   |

| SCK30                  | I/O    | Serial interface serial clock input/output.                                                                                                              | Input       | P22                   |

| SCK31 Note 1           |        |                                                                                                                                                          |             | P36                   |

| SCL0 <sup>Note 2</sup> |        |                                                                                                                                                          |             | P33                   |

| RxD0                   | Input  | Serial data input for asynchronous serial interface.                                                                                                     | Input       | P23                   |

| TxD0                   | Output | Serial data output for asynchronous serial interface.                                                                                                    | Input       | P24                   |

| ASCK0                  | Input  | Serial clock input for asynchronous serial interface.                                                                                                    | Input       | P25                   |

| TI00                   | Input  | External count clock input to 16-bit timer/event counter 0.  Capture trigger signal input to capture register 01 (CR01) of 16-bit timer/event counter 0. | Input       | P70/TO0               |

| TI01                   |        | Capture trigger signal input to capture register 00 (CR00) of 16-bit timer/ event counter 0.                                                             |             | P71                   |

| TI50                   |        | External count clock input to 8-bit timer/event counter 50.                                                                                              |             | P72/TO50              |

| TI51                   |        | External count clock input to 8-bit timer/event counter 51.                                                                                              |             | P73/TO51              |

| TO0                    | Output | 16-bit timer/event counter 0 output.                                                                                                                     | Input       | P70/TI00              |

| TO50                   |        | 8-bit timer/event counter 50 output (shared with 8-bit PWM output).                                                                                      | Input       | P72/TI50              |

| TO51                   |        | 8-bit timer/event counter 51 output (shared with 8-bit PWM output).                                                                                      |             | P73/TI51              |

| PCL                    | Output | Clock output (for trimming of main system clock and subsystem clock).                                                                                    | Input       | P74                   |

| BUZ                    | Output | Buzzer output.                                                                                                                                           | Input       | P75                   |

| AD0 to AD7             | I/O    | Lower address/data bus for extending memory externally.                                                                                                  | Input       | P40 to P47            |

**Notes 1.** SI31, SO31, and  $\overline{\text{SCK31}}$  are incorporated only in the  $\mu$ PD78F0034A Subseries.

2. SDA0 and SCL0 are incorporated only in the  $\mu$ PD78F0034AY Subseries.

# 3.2 Non-Port Pins (2/2)

| Pin Name         | I/O    | Function                                                                                                      | After Reset | Alternate<br>Function |

|------------------|--------|---------------------------------------------------------------------------------------------------------------|-------------|-----------------------|

| A8 to A15        | Output | Higher address bus for extending memory externally.                                                           | Input       | P50 to P57            |

| RD               | Output | Strobe signal output for read operation of external memory.                                                   | Input       | P64                   |

| WR               |        | Strobe signal output for write operation of external memory.                                                  |             | P65                   |

| WAIT             | Input  | Inserting wait for accessing external memory.                                                                 | Input       | P66                   |

| ASTB             | Output | Strobe output which externally latches address information output to ports 4 and 5 to access external memory. | Input       | P67                   |

| ANI0 to ANI7     | Input  | A/D converter analog input.                                                                                   | Input       | P10 to P17            |

| ADTRG            | Input  | A/D converter trigger signal input.                                                                           | Input       | P03/INTP3             |

| AVREF            | Input  | A/D converter reference voltage input.                                                                        | _           | _                     |

| AVDD             | _      | A/D converter analog power supply.  Set the voltage equal to VDDD or VDD1.                                    | -           | _                     |

| AVss             | -      | A/D converter ground potential.  Set the voltage equal to Vsso or Vss1.                                       | _           | _                     |

| RESET            | Input  | System reset input.                                                                                           | _           | _                     |

| X1               | Input  | Connecting crystal resonator for main system clock oscillation.                                               | _           | _                     |

| X2               | -      |                                                                                                               | _           | _                     |

| XT1              | Input  | Connecting crystal resonator for subsystem clock oscillation.                                                 | -           | _                     |

| XT2              | _      |                                                                                                               | _           | _                     |

| V <sub>DD0</sub> | -      | Positive power supply voltage for ports.                                                                      | _           | _                     |

| Vsso             | -      | Ground potential of ports.                                                                                    | _           | _                     |

| V <sub>DD1</sub> | _      | Positive power supply (except ports).                                                                         | _           | -                     |

| V <sub>SS1</sub> | -      | Ground potential (except ports).                                                                              | _           | _                     |

| V <sub>PP</sub>  | -      | Applying high-voltage for program write/verify. Connect directly to Vsso or Vss1 in normal operation mode.    | _           | _                     |

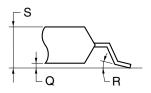

# 3.3 Pin I/O Circuits and Recommended Connection of Unused Pins

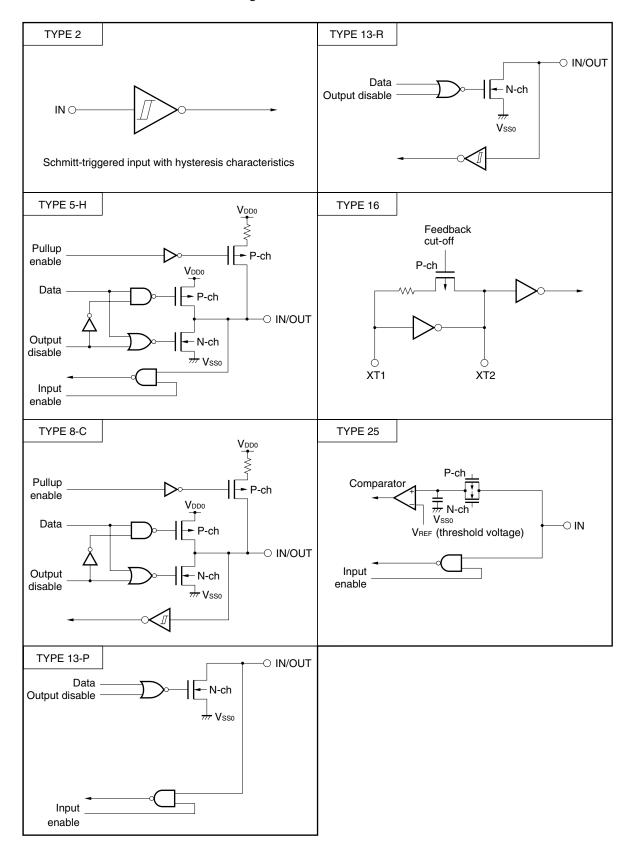

The input/output circuit type of each pin and recommended connection of unused pins are shown in Table 3-1. For the input/output configuration of each type, refer to Figure 3-1.

Table 3-1. Types of Pin I/O Circuits (1/2)

| Pin Name                   | I/O Circuit Type | I/O   | Recommended Connection of Unused Pins                                     |

|----------------------------|------------------|-------|---------------------------------------------------------------------------|

| P00/INTP0                  | 8-C              | I/O   | Input: Independently connect to V <sub>SS0</sub> via a resistor.          |

| P01/INTP1                  |                  |       | Output: Leave open.                                                       |

| P02/INTP2                  |                  |       |                                                                           |

| P03/INTP3/ADTRG            |                  |       |                                                                           |

| P10/ANI0 to P17/ANI7       | 25               | Input | Directly connect to VDD0 or VSS0.                                         |

| P20/SI30                   | 8-C              | I/O   | Input: Independently connect to VDD0 or VSS0 via a                        |

| P21/SO30                   | 5-H              |       | resistor.                                                                 |

| P22/SCK30                  | 8-C              |       | Output: Leave open.                                                       |

| P23/RxD0                   |                  |       |                                                                           |

| P24/TxD0                   | 5-H              |       |                                                                           |

| P25/ASCK0                  | 8-C              |       |                                                                           |

| P30, P31                   | 13-P             | I/O   | Input: Independently connect to VDDO via a resistor.                      |

| P32/SDA0 <sup>Note 1</sup> | 13-R             |       | Output: Leave open.                                                       |

| P33/SCL0 <sup>Note 1</sup> |                  |       |                                                                           |

| P34/SI31Note 2             | 8-C              |       | Input: Independently connect to VDD0 or VSS0 via a                        |

| P35/SO31 <sup>Note 2</sup> | 5-H              |       | resistor.                                                                 |

| P36/SCK31Note 2            | 8-C              |       | Output: Leave open.                                                       |

| P40/AD0 to P47/AD7         | 5-H              | I/O   | Input: Independently connect to VDDO via a resistor.  Output: Leave open. |

| P50/A8 to P57/A15          | 5-H              | I/O   | Input: Independently connect to VDD0 or VSS0 via a                        |

| P64/RD                     |                  | I/O   | resistor.                                                                 |

| P65/WR                     |                  |       | Output: Leave open.                                                       |

| P66/WAIT                   |                  |       |                                                                           |

| P67/ASTB                   |                  |       |                                                                           |

| P70/TI00/TO0               | 8-C              |       |                                                                           |

| P71/TI01                   |                  |       |                                                                           |

| P72/TI50/TO50              |                  |       |                                                                           |

| P73/TI51/TO51              |                  |       |                                                                           |

| P74/PCL                    | 5-H              |       |                                                                           |

| P75/BUZ                    |                  |       |                                                                           |

**Notes 1.** SDA0 and SCL0 are incorporated only in the  $\mu$ PD78F0034AY Subseries.

2. SI31, SO31, and  $\overline{\text{SCK31}}$  are incorporated only in the  $\mu\text{PD78F0034A}$  Subseries.

www.DataSheet4U.com

# Table 3-1. Types of Pin I/O Circuits (2/2)

| Pin Name        | I/O Circuit Type | I/O   | Recommended Connection of Unused Pins |

|-----------------|------------------|-------|---------------------------------------|

| RESET           | 2                | Input | -                                     |

| XT1             | 16               |       | Directly connect to VDD0.             |

| XT2             |                  | _     | Leave open.                           |

| AVDD            | -                |       | Directly connect to VDD0 or VDD1.     |

| AVREF           |                  |       | Directly connect to Vsso or Vss1.     |

| AVss            |                  |       |                                       |

| V <sub>PP</sub> |                  |       | Directly connect to Vsso or Vss1.     |

Figure 3-1. Pin I/O Circuits

#### ♦ 4. DIFFERENCES BETWEEN μPD78F0034A, 78F0034AY, AND MASK ROM VERSIONS

The  $\mu$ PD78F0034A and 78F0034AY are products provided with a flash memory which enables writing, erasing, and rewriting of programs with device mounted on the target system.

The functions of the  $\mu$ PD78F0034A (except the functions specified for flash memory) can be made the same as those of the mask ROM versions by setting the memory size switching register (IMS).

Tables 4-1 and 4-2 show the differences between the  $\mu$ PD78F0034A, 78F0034AY and the mask ROM versions.

Table 4-1. Differences Between  $\mu$ PD78F0034A and Mask ROM Versions

| Item                                                                      | μPD78F0034A                                                                                                                                                                              | Mask ROM Versions                                                                                                                                                             |                                                                                                      |  |  |

|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|

|                                                                           |                                                                                                                                                                                          | μPD780034A Subseries                                                                                                                                                          | μPD780024A Subseries <sup>Note</sup>                                                                 |  |  |

| Internal ROM structure                                                    | Flash memory                                                                                                                                                                             | Mask ROM                                                                                                                                                                      |                                                                                                      |  |  |

| Internal ROM capacity                                                     | 32 KB                                                                                                                                                                                    | μPD780031A: 8 KB<br>μPD780032A: 16 KB<br>μPD780033A: 24 KB<br>μPD780034A: 32 KB                                                                                               | μPD780021A: 8 KB<br>μPD780022A: 16 KB<br>μPD780023A: 24 KB<br>μPD780024A: 32 KB                      |  |  |

| Internal high-speed RAM capacity                                          | 1,024 bytes                                                                                                                                                                              | μPD780031A: 512 bytes<br>μPD780032A: 512 bytes<br>μPD780033A: 1,024 bytes<br>μPD780034A: 1,024 bytes                                                                          | μPD780021A: 512 bytes<br>μPD780022A: 512 bytes<br>μPD780023A: 1,024 bytes<br>μPD780024A: 1,024 bytes |  |  |

| Minimum instruction execution time                                        | Minimum instruction execution                                                                                                                                                            | on time variable function inco                                                                                                                                                | rporated                                                                                             |  |  |

| When main system clock is selected                                        | 0.24 $\mu$ s/0.48 $\mu$ s/0.95 $\mu$ s/<br>1.91 $\mu$ s/3.81 $\mu$ s<br>(operation at 8.38 MHz,<br>V <sub>DD</sub> = 4.0 to 5.5 V)                                                       | 0.166 $\mu$ s/0.333 $\mu$ s/0.666 $\mu$ s/1.33 $\mu$ s/2.66 $\mu$ s (operation at 12 MHz, V <sub>DD</sub> = 4.5 to 5.5 V)                                                     |                                                                                                      |  |  |

| When subsystem clock is selected                                          | 122 μs (32.768 kHz)                                                                                                                                                                      |                                                                                                                                                                               |                                                                                                      |  |  |

| Clock output                                                              | 65.5 kHz, 131 kHz, 262 kHz, 524 kHz, 1.05 MHz, 2.10 MHz, 4.19 MHz, 8.38 MHz (operation at 8.38 MHz with main system clock)     32.768 kHz (operation at 32.768 kHz with subsystem clock) | 93.75 kHz, 187.5 kHz, 375 kHz, 750 kHz, 1.25 MHz, 3 MHz, 6 MHz, 12 MHz (operation at 12 MHz with main system clock) 32.768 kHz (operation at 32.768 kHz with subsystem clock) |                                                                                                      |  |  |

| Buzzer output                                                             | 1.02 kHz, 2.5 kHz,<br>4.10 kHz, 8.19 kHz<br>(operation at 8.38 MHz<br>with main system clock)                                                                                            | 1.46 kHz, 2.93 kHz, 5.86 kHz, 11.7 kHz (operation at 12 MHz with main system clock)                                                                                           |                                                                                                      |  |  |

| A/D converter resolution                                                  | 10 bits                                                                                                                                                                                  |                                                                                                                                                                               | 8 bits                                                                                               |  |  |

| Mask option specification of on-chip pull-up resistor for pins P30 to P33 | Not available                                                                                                                                                                            | Available                                                                                                                                                                     |                                                                                                      |  |  |

| IC pin                                                                    | Not provided                                                                                                                                                                             | Provided                                                                                                                                                                      |                                                                                                      |  |  |

| V <sub>PP</sub> pin                                                       | Provided                                                                                                                                                                                 | Not provided                                                                                                                                                                  |                                                                                                      |  |  |

| Electrical specifications, recommended soldering conditions               | Refer to the data sheet of ir                                                                                                                                                            | individual products.                                                                                                                                                          |                                                                                                      |  |  |

**Note** The  $\mu$ PD78F0034A can be used as the flash memory version of the  $\mu$ PD780024A Subseries.

Caution There are differences in noise immunity and noise radiation between the flash memory and mask ROM versions. When pre-producing an application set with the flash memory version and then mass producing it with the mask ROM version, be sure to conduct sufficient evaluations on the commercial samples (CS) (not engineering samples (ES)) of the mask ROM versions.

www.DataSneet4U.com

Table 4-2. Differences Between  $\mu$ PD78F0034AY and Mask ROM Versions

| Item                                                                       | μPD78F0034AY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mask ROM                                                                                                                                                                                              | M Versions                                                                                               |  |  |  |

|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

|                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | μPD780034AY Subseries                                                                                                                                                                                 | μPD780024AY Subseries <sup>Note</sup>                                                                    |  |  |  |

| Internal ROM structure                                                     | Flash memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Mask ROM                                                                                                                                                                                              |                                                                                                          |  |  |  |

| Internal ROM capacity                                                      | 32 KB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | μPD780031AY: 8 KB       μPD780021AY: 8 KB         μPD780032AY: 16 KB       μPD780022AY: 16 KB         μPD780033AY: 24 KB       μPD780023AY: 24 KB         μPD780034AY: 32 KB       μPD780024AY: 32 KB |                                                                                                          |  |  |  |

| Internal high-speed RAM capacity                                           | 1,024 bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $\mu$ PD780031AY: 512 bytes $\mu$ PD780032AY: 512 bytes $\mu$ PD780033AY: 1,024 bytes $\mu$ PD780034AY: 1,024 bytes                                                                                   | μPD780021AY: 512 bytes<br>μPD780022AY: 512 bytes<br>μPD780023AY: 1,024 bytes<br>μPD780024AY: 1,024 bytes |  |  |  |

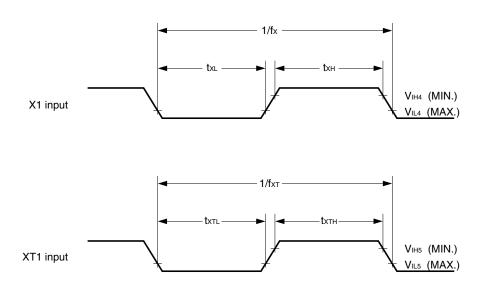

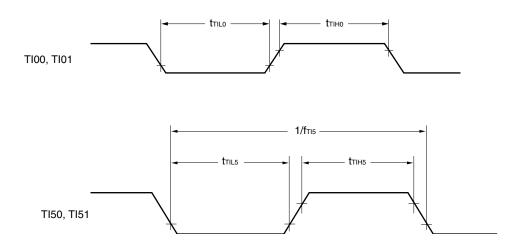

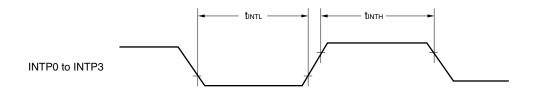

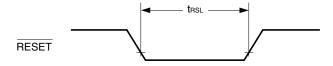

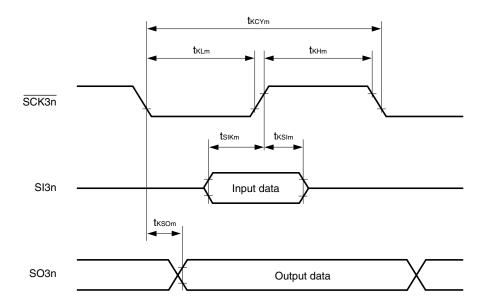

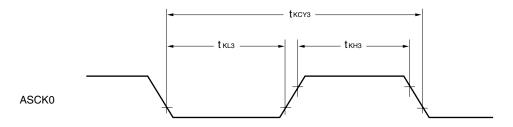

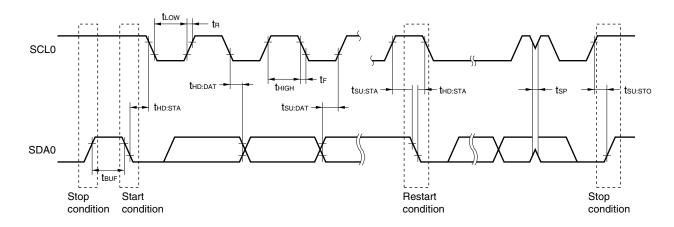

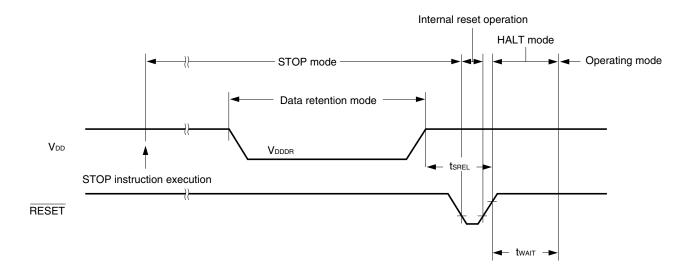

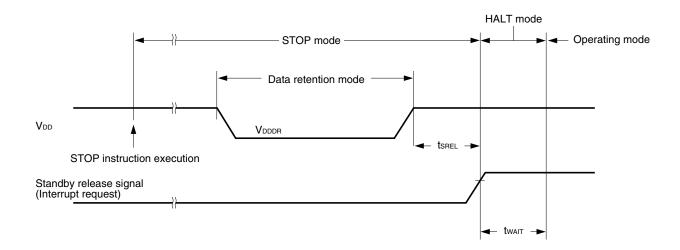

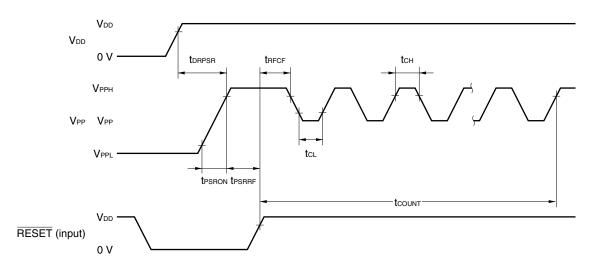

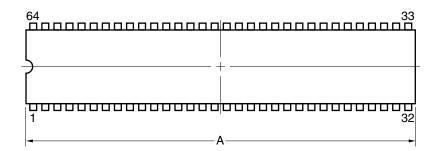

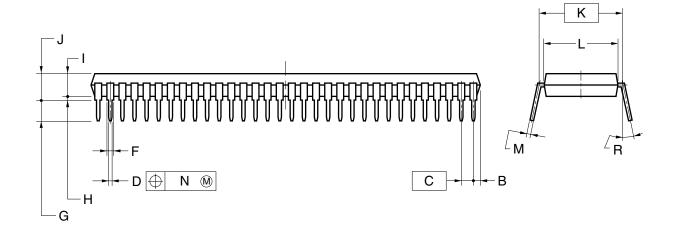

| Minimum instruction execution time                                         | Minimum instruction execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | on time variable function inco                                                                                                                                                                        | rporated                                                                                                 |  |  |  |