# **General Description**

DA9155M offers a small solution that can be easily added on to existing main charger circuits and solves the heat dissipation problem created when the rapid charging feature is adopted. DA9155M is compatible to all rapid charging technologies using high voltage input.

DA9155M features a Buck converter capable of 2.5 A constant output current and regulates the output current with ±5 % accuracy for single cell Li-lon batteries. Current sensing is performed with a fully integrated circuit.

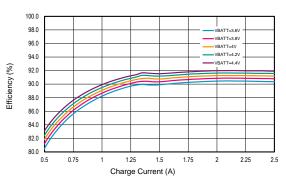

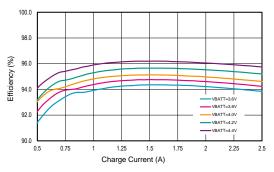

The peak efficiency of the Buck converter is 92 %.

# **Key Features**

- Input voltage 4.3 V to 13.5 V

- Input voltage monitoring

- Buck converter with output current regulation

- □ Output current 2.5 A

- □ ±5 % current regulation accuracy

- □ Selectable switching frequency

- Fault detection (V<sub>IN</sub> and V<sub>BAT</sub> monitoring)

- Safety timer

- Junction temperature monitoring

- -40 °C to +85 °C temperature range

- WLCSP, 0.4 mm pitch

# **Applications**

- Companion charger in smartphone and tablet platforms

- Companion charger for all single cell Li-lon battery powered devices

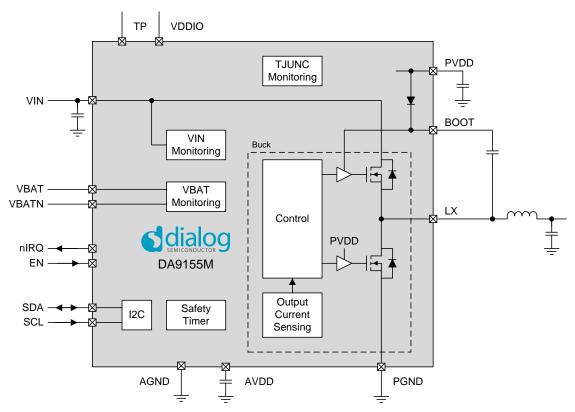

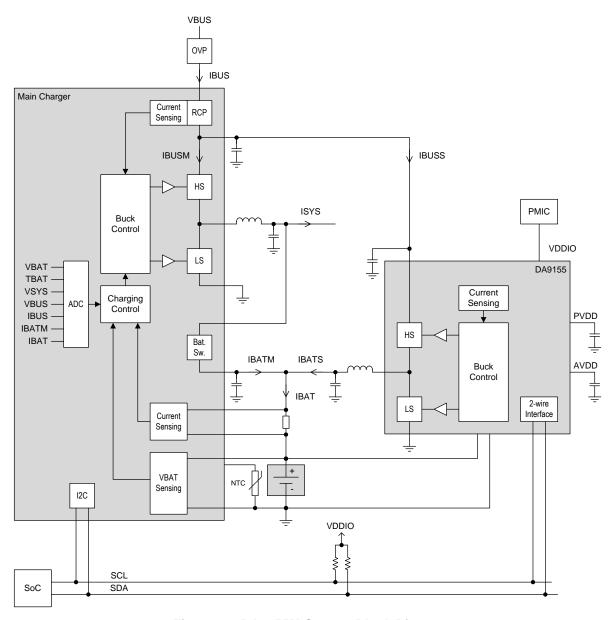

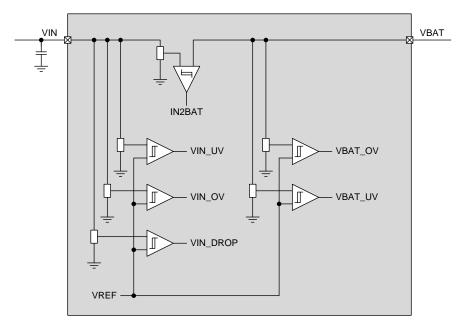

# 1 Block Diagram

Figure 1: DA9155M Block Diagram.

# 2 Revision History

| Revision | Date         | Changes                                                                                                                                                                                                                                                                                                                                     |

|----------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1      | 04-May-2017  | Document formatting changes                                                                                                                                                                                                                                                                                                                 |

| 3.06     | 21-Dec-2016  | Added thermal resistance to Recommended Operating Conditions Additional description in TIMER_B register definition table Additional description in Pin list for AVDD and PVDD Changes to Description                                                                                                                                        |

| 3.05     | 22-July-2016 | Updated first page                                                                                                                                                                                                                                                                                                                          |

| 3.04     | 10-May-2016  | Added max value of $V_{IN\_OVLO}$ Updated max value of $V_{IN\_UVLO}$ Updated typ value of $L_{ESR}$ Added min value in Output current range Added min and max values of $I_{LIM}$ Updated test condition for $V_{BAT\_OV}$ Updated test condition for $I_{Q\_DIS\_VIN}$ Updated description of Bit $E\_RDY$ in $EVENT\_B$ (0x004) register |

| 3.03     | 24-Mar-2016  | Update Specs for I <sub>Q_NO_PWR_VBAT</sub> and removed V <sub>OH</sub>                                                                                                                                                                                                                                                                     |

| 3.02     | 01-Mar-2016  | Updated Specs for V <sub>IN2BAT</sub> , V <sub>IN2BAT_HYST</sub> , V <sub>IN_DROP_HYST</sub> , V <sub>IN_DROP_ACC</sub> , V <sub>BAT_UV_ACC</sub> , V <sub>BAT_OV_ACC</sub>                                                                                                                                                                 |

| 3.01     | 15-Jan-2016  | Update Figure 2 for LF35                                                                                                                                                                                                                                                                                                                    |

| 3.00     | 09-Nov-2015  | Final Datasheet Release                                                                                                                                                                                                                                                                                                                     |

# **3 Ordering Information**

The order number consists of the part number followed by a suffix indicating the packing method. For details, please consult the customer portal on the Dialog website or your local sales representative.

**Table 1: Ordering Information**

| Part number   | Package   | Package description    |

|---------------|-----------|------------------------|

| DA9155M-xxU72 | 30 WL-CSP | Tape and Reel, 4500pcs |

### **Contents**

| Ge | neral l | Descripti  | on                                                  | 1  |

|----|---------|------------|-----------------------------------------------------|----|

| Ke | y Feat  | ures       |                                                     | 1  |

| Аp | plicati | ons        |                                                     | 1  |

| 1  | Block   | k Diagran  | n                                                   | 2  |

| 2  | Revis   | sion Histo | ory                                                 | 3  |

| 3  |         |            | rmation                                             |    |

|    |         | _          |                                                     |    |

|    |         |            |                                                     |    |

| 4  |         |            |                                                     |    |

| 5  |         |            | imum Ratings                                        |    |

| 6  |         |            | d Operating Conditions                              |    |

| 7  | Elect   |            | racteristics                                        |    |

|    | 7.1     | •          | O                                                   |    |

|    | 7.2     |            | itoring                                             |    |

|    | 7.3     |            | onverter                                            |    |

|    | 7.4     |            | nterface                                            |    |

|    | 7.5     | -          | ature Supervision                                   |    |

|    | 7.6     | 2,         | nitoring                                            |    |

| _  | 7.7     |            | Consumption                                         |    |

| 8  | ٠.      |            | cteristics                                          |    |

| 9  | •       |            | Diagram                                             |    |

|    | 9.1     |            | arger                                               |    |

|    | 9.2     |            | harger                                              |    |

| 10 |         |            | scription                                           |    |

|    | 10.1    |            | Signals                                             |    |

|    |         | 10.1.1     | EN                                                  |    |

|    | 40.0    | 10.1.2     | nIRQ                                                |    |

|    | 10.2    |            | nterface                                            |    |

|    |         | 10.2.1     | Register Map Paging  Details of the 2-Wire Protocol |    |

|    | 10.3    |            | nverter                                             |    |

|    | 10.3    |            | imer                                                |    |

|    | _       | -          | itoring                                             |    |

|    |         |            | nitoring                                            |    |

|    | 10.7    |            | Temperature Supervision                             |    |

|    |         |            | lodes                                               |    |

|    |         | 10.8.1     | No-Power                                            | 23 |

|    |         | 10.8.2     | Reset                                               | 23 |

|    |         | 10.8.3     | Disabled                                            | 24 |

|    |         | 10.8.4     | Active                                              | 24 |

| 11 | Regis   | ster Map.  |                                                     | 25 |

|    | 11.1    | Overviev   | w25                                                 |    |

|    | 11.2    | Register   | Descriptions                                        | 26 |

|    | 11.3    | Page 0     | 26                                                  |    |

|    |         |            |                                                     |    |

**Datasheet**

04-May-2017

|    |       | 11.3.1    | Page Control             | . 26 |

|----|-------|-----------|--------------------------|------|

|    |       | 11.3.2    | Status and Events        |      |

|    |       | 11.3.3    | VIN and VBAT Monitoring  | . 27 |

|    |       | 11.3.4    | Configuration            | . 28 |

|    |       | 11.3.5    | Safety Timer             |      |

|    |       | 11.3.6    | Buck Control             | . 29 |

|    |       | 11.3.7    | Interface                | . 30 |

|    |       | 11.3.8    | Configuration            | . 30 |

|    | 11.4  | Page 1    | 31                       |      |

|    |       | 11.4.1    | Page Control             | . 31 |

|    | 11.5  | Page 2    | 31                       |      |

|    |       | 11.5.1    | Page Control             | . 31 |

|    | 11.6  | Page 3    | 31                       |      |

|    |       | 11.6.1    | Page Control             | . 31 |

|    | 11.7  | Page 4    | 32                       |      |

|    |       | 11.7.1    | Page Control             | . 32 |

|    | 11.8  | Page 5    | 32                       |      |

|    |       | 11.8.1    | Page Control             | . 32 |

|    | 11.9  | Page 6    | 32                       |      |

|    |       | 11.9.1    | Page Control             | . 32 |

|    |       | 11.9.2    | Trimming and Engineering | . 33 |

| 12 | Appli | cation In | formation                | . 34 |

|    |       |           | /out                     |      |

|    |       | -         | ent Selection            |      |

|    |       | 12.2.1    | Capacitors               | . 34 |

|    |       | 12.2.2    | Inductor                 | . 35 |

|    |       |           |                          |      |

# 4 Pin List

Table 2: DA9155M Pin Description

| Pin                                     | Name  | Туре | Description                                          |

|-----------------------------------------|-------|------|------------------------------------------------------|

| C1                                      | VDDIO | PS   | IO supply                                            |

| B2, B3,<br>B4, C2,<br>C3, D1,<br>D2, D3 | AGND  | GND  | Analog ground                                        |

| A2                                      | AVDD  | AIO  | Internal supply, typical 4 V                         |

| А3                                      | PVDD  | AIO  | Internal supply, typical 4 V                         |

| E2                                      | SDA   | DIO  | Data signal of the 2-wire interface (GPIO)           |

| E1                                      | SCL   | DI   | Clock signal of the 2-wire interface (GPIO)          |

| E4                                      | EN    | DI   | Control signal for the output current/voltage (GPIO) |

| E3                                      | nIRQ  | DO   | Interrupt signal to host processor (GPIO)            |

| A5, A6                                  | VIN   | PS   | Input supply                                         |

| B5, B6,<br>C5, C6,<br>D5, D6            | VLX   | АО   | Switching node of Buck                               |

| A4                                      | воот  | AIO  | Supply of the high-side driver                       |

| B1                                      | VBAT  | Al   | Battery voltage sense, positive terminal             |

| A1                                      | VBATN | Al   | Battery voltage sense, negative terminal             |

| E5, E6                                  | PGND  | GND  | Power grounds of the Buck, digital ground            |

| C4, D4                                  | NC    |      | Not connected. Short to ground.                      |

# **Table 3: Pin Type Definitions**

| Pin type | Description          | Pin type | Description           |

|----------|----------------------|----------|-----------------------|

| DI       | Digital Input        | Al       | Analogue Input        |

| DO       | Digital Output       | AO       | Analogue Output       |

| DIO      | Digital Input/Output | AIO      | Analogue Input/Output |

| PS       | Power Supply         | GND      | Ground connection     |

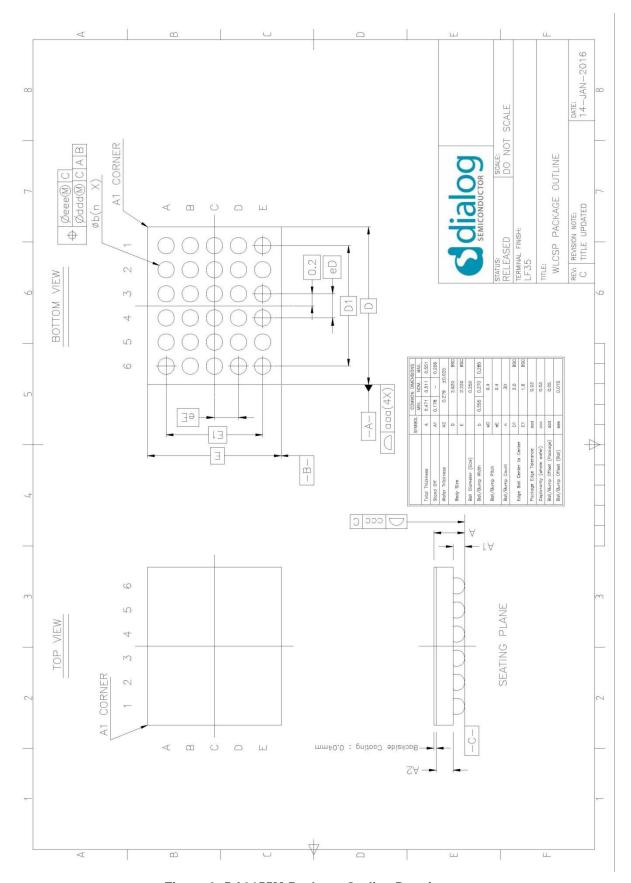

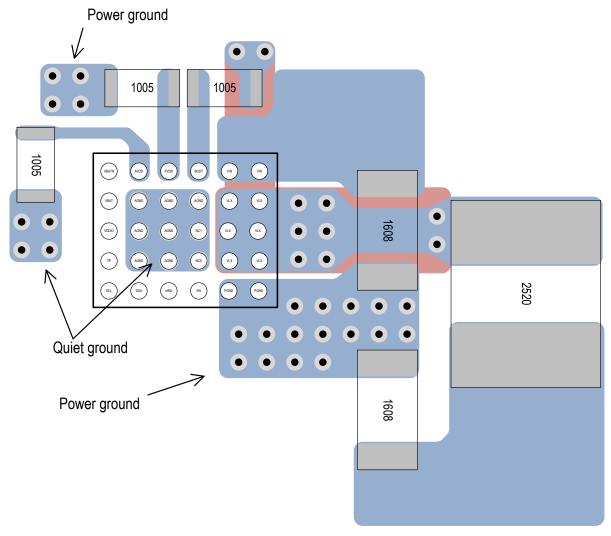

Figure 2: DA9155M Package Outline Drawing

### 5 Absolute Maximum Ratings

Table 4 lists the absolute maximum ratings of the device. Stressing the device beyond these ratings may cause permanent damage to the device. Functionality of the device is only guaranteed in conditions listed in sections 6 and 7. Operating the device in conditions exceeding those listed in sections 6 and 7, but still complying with the absolute maximum ratings listed in Table 4, for extended periods of time may affect device reliability.

**Table 4: Absolute Maximum Ratings**

| Parameter                             | Symbol              | Note                                                       | Min  | Max     | Unit |

|---------------------------------------|---------------------|------------------------------------------------------------|------|---------|------|

| Storage temperature                   |                     |                                                            | -60  | +150    | °C   |

| Operating temperature                 | T <sub>A</sub>      |                                                            | -40  | +85     | °C   |

| Terminal voltage (referenced to PGND, | VIN                 | The device is not operational above V <sub>IN_OVLO</sub> . | -0.3 | 20      | V    |

| unless otherwise noted)               | VLX                 |                                                            | -0.3 | VIN     | ٧    |

|                                       | BOOT                |                                                            | -0.3 | VLX+5.5 | ٧    |

|                                       | VBATP               | Referenced to VBATN                                        | -0.3 | 6       | ٧    |

|                                       | All other terminals | Referenced to AGND                                         | -0.3 | 5.5     | V    |

| ESD tolerance                         |                     | НВМ                                                        |      | 2       | kV   |

# **6** Recommended Operating Conditions

**Table 5: Recommended Operating Conditions**

| Parameter                                       | Symbol          | Min | Max   | Unit |

|-------------------------------------------------|-----------------|-----|-------|------|

| Operating temperature                           | T <sub>A</sub>  | -40 | +85   | °C   |

| Supply voltage                                  | V <sub>IN</sub> | 4.3 | 13.5  | V    |

| Supply voltage IO                               | $V_{DDIO}$      | 1.5 | 3.6   | V    |

| Thermal resistance (junction to ambient) Note 1 | θЈΑ             |     | 37.42 | °C/W |

Note 1 Multilayer JEDEC standard, still air, ambient temperature 27 °C, simulated value

#### 7 Electrical Characteristics

#### 7.1 Digital I/O

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85  $^{\circ}$ C,  $V_{IN}$  = 4.3 to 13.5 V,  $V_{BAT}$  = 2.6 to 4.4 V

Table 6: Digital I/O

| Parameter                           | Symbol          | Test conditions | Min            | Тур | Max            | Unit |

|-------------------------------------|-----------------|-----------------|----------------|-----|----------------|------|

| Input high voltage (EN, SCL, SDA)   | V <sub>IH</sub> |                 | 0.7 ×<br>VDDIO |     |                | V    |

| Input low voltage<br>(EN, SCL, SDA) | V <sub>IL</sub> |                 |                |     | 0.3 ×<br>VDDIO | V    |

| Output low voltage (nIRQ, SDA)      | V <sub>OL</sub> |                 |                |     | 0.3            | V    |

| Input capacitance (SCL, SDA)        | C <sub>IN</sub> |                 |                |     | 10             | pF   |

### 7.2 V<sub>IN</sub> Monitoring

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85  $^{\circ}$ C,  $V_{IN}$  = 4.3 to 13.5 V,  $V_{BAT}$  = 2.6 to 4.4 V

Table 7: V<sub>IN</sub> Monitoring

| Parameter                                      | Symbol                    | Test conditions                                       | Min   | Тур  | Max   | Unit |

|------------------------------------------------|---------------------------|-------------------------------------------------------|-------|------|-------|------|

| V <sub>IN</sub> to V <sub>BAT</sub> threshold  | V <sub>IN2BAT</sub>       | Falling threshold                                     | 225   | 275  | 330   | mV   |

| V <sub>IN</sub> to V <sub>BAT</sub> hysteresis | V <sub>IN2BAT_HYST</sub>  |                                                       |       | 130  |       | mV   |

| V <sub>IN</sub> overvoltage threshold          | V <sub>IN_OVLO</sub>      | Rising threshold,<br>pulse width greater<br>than 3 µs | 13.5  |      | 15    | V    |

| V <sub>IN</sub> overvoltage<br>hysteresis      | VIN_OVLO_HYST             |                                                       |       | 2%   |       |      |

| V <sub>IN</sub> undervoltage threshold         | V <sub>IN_UVLO</sub>      | Falling threshold                                     | 4.085 | 4.3  | 4.5   | V    |

| V <sub>IN</sub> undervoltage<br>hysteresis     | V <sub>IN_UVLO_HYST</sub> |                                                       |       | 2%   |       |      |

| V <sub>IN</sub> drop<br>threshold range        | V <sub>IN_DROP</sub>      | Falling threshold. V <sub>IN_DROP</sub> =0x3B         |       | 12   |       | V    |

|                                                |                           | Falling threshold.  VIN_DROP=0x37                     |       | 11.6 |       | V    |

|                                                |                           | Falling threshold. V <sub>IN_DROP</sub> =0x23         |       | 8.6  |       | V    |

|                                                |                           | Falling threshold V <sub>IN_DROP</sub> =0x00          |       | 4.3  |       | V    |

| V <sub>IN</sub> drop hysteresis                | V <sub>IN_DROP_HYST</sub> |                                                       |       | 1.5% |       |      |

| V <sub>IN</sub> drop accuracy                  | V <sub>IN_DROP_ACC</sub>  | Vin_drop <= 5.4V                                      | -1.6% |      | +1.6% |      |

|                                                |                           | Vin_drop > 5.4V                                       | -1.9% |      | +1.9% |      |

#### 7.3 Buck Converter

**Table 8: External Components**

| Parameter            | Symbol            | Test conditions | Min | Тур  | Max | Unit |

|----------------------|-------------------|-----------------|-----|------|-----|------|

| Input capacitor      | C <sub>IN</sub>   |                 |     | 10   |     | μF   |

| Output capacitor     | Соит              | Nominal         | 10  | 22   |     | μF   |

| Output capacitor ESR | C <sub>ESR</sub>  |                 |     | 3    |     | mΩ   |

| Inductor value       | L <sub>BUCK</sub> |                 |     | 0.47 |     | μH   |

| Inductor resistance  | L <sub>ESR</sub>  |                 |     | 24   |     | mΩ   |

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85  $^{\circ}$ C,  $V_{IN}$  = 4.3 to 13.5 V,  $V_{BAT}$  = 2.6 to 4.4 V

**Table 9: Buck Converter**

| Parameter                          | Symbol               | Test conditions                                                                                                                          | Min  | Тур  | Max  | Unit |

|------------------------------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Input voltage range                | V <sub>IN</sub>      | V <sub>IN</sub> has to be above V <sub>BAT</sub> (Section 7.2)                                                                           | 4.3  |      | 13.5 | V    |

| Output current range               |                      |                                                                                                                                          | 400  |      | 2500 | mA   |

| Output current                     | Іоит                 | BUCK_IOUT = 0x32                                                                                                                         |      | 750  |      | mA   |

|                                    |                      | BUCK_IOUT = 0x7D                                                                                                                         |      | 1500 |      | mA   |

|                                    |                      | BUCK_IOUT = 0xE1                                                                                                                         |      | 2500 |      | mA   |

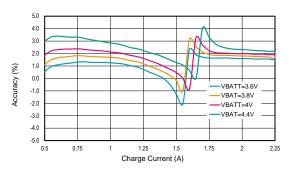

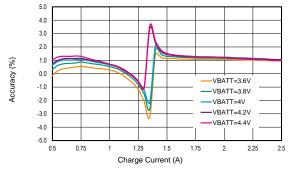

| Output current regulation accuracy | I <sub>OUT_ACC</sub> | $I_{OUT} = 2.5 \text{ A},$<br>D \le 80%,<br>V <sub>IN</sub> = 5V to 12V,<br>T <sub>A</sub> = 0 to 85 °C (Note 2)                         | -5%  |      | +5%  |      |

|                                    |                      | $1.5 \text{ A} \le I_{OUT} < 2.5 \text{ A},$<br>$D \le 80\%,$<br>$V_{IN} = 5V \text{ to } 12V,$<br>$T_A = 25 ^{\circ}\text{C (Note 2)}$  | -5%  |      | +5%  |      |

|                                    |                      | $500 \text{ mA} \le I_{OUT} < 1.5 \text{ A},$<br>$D \le 80\%,$<br>$V_{IN} = 5V \text{ to } 12V,$<br>$T_A = 25 ^{\circ}\text{C (Note 2)}$ | -10% |      | +10% |      |

| Efficiency                         | η                    | $V_{IN} = 5 V$ $V_{BAT} = 4.4 V$ $I_{OUT} = 2.5 A$                                                                                       |      | 96%  |      |      |

|                                    |                      | $V_{IN} = 9 V$ $V_{BAT} = 4.4 V$ $I_{OUT} = 2.5 A$                                                                                       |      | 92%  |      |      |

|                                    |                      | V <sub>IN</sub> = 12 V<br>V <sub>BAT</sub> = 4.4 V<br>I <sub>OUT</sub> = 2.5 A                                                           |      | 90%  |      |      |

| Switching frequency                | f                    | OSC_TUNE = 0x0<br>BUCK_FSW = 0x0 (Note 3)                                                                                                |      | 1.2  |      | MHz  |

|                                    |                      | OSC_TUNE = 0x0<br>BUCK_FSW = 0x2 (Note 3)                                                                                                |      | 1.5  |      | MHz  |

|                                    |                      | OSC_TUNE = 0x0<br>BUCK_FSW = 0x3 (Note 3)                                                                                                |      | 1    |      | MHz  |

| Duty cycle                         | D                    | VIN ≥ 5 V, f=1.5 MHz                                                                                                                     | 15%  |      | 85%  |      |

|                                    |                      | Switching frequency is stepwise reduced above 85% duty cycle                                                                             |      |      | 95%  |      |

| Minimum off-time                   | t <sub>MIN_OFF</sub> |                                                                                                                                          |      | 100  |      | ns   |

| High-side R <sub>DSON</sub>        | R <sub>DSON-HS</sub> | Including pin and routing                                                                                                                |      | 25   |      | mΩ   |

| Low-side R <sub>DSON</sub>         | R <sub>DSON-LS</sub> | Including pin and routing                                                                                                                |      | 25   |      | mΩ   |

| Peak current limit                 | I <sub>LIM</sub>     | BUCK_ILIM = 0x19                                                                                                                         | 4400 | 5500 | 6600 | mA   |

|                                    |                      | BUCK_ILIM = 0x14                                                                                                                         | 4000 | 5000 | 6000 | mA   |

|                                    |                      | BUCK_ILIM = 0x0                                                                                                                          | 2050 | 3000 | 3820 | mA   |

Note 2 Accuracy may decrease by 5% at D > 80%

Note 3 1 MHz is recommended for  $V_{IN} \le 6.5 \text{ V}$  and 1.5 MHz for  $V_{IN} > 6.5 \text{ V}$

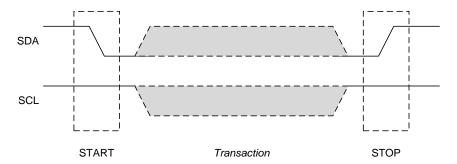

#### 7.4 2-Wire Interface

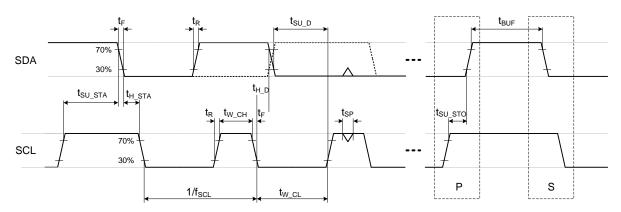

Figure 3: 2-Wire Interface Timing

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85  $^{o}C$ ,  $V_{IN}$  = 4.3 to 13.5 V,  $V_{BAT}$  = 2.6 to 4.4 V

Table 10: 2-Wire Interface

| Parameter                                  | Symbol              | Test conditions                                   | Min  | Тур | Max  | Unit |

|--------------------------------------------|---------------------|---------------------------------------------------|------|-----|------|------|

| Spike suppression (SCL,                    | t <sub>SP</sub>     | Fast/fast+ mode                                   | 0    |     | 50   | ns   |

| SDA)                                       |                     | High speed mode                                   | 0    |     | 10   | ns   |

| Bus free time from STOP to START condition | t <sub>BUF</sub>    |                                                   | 0.5  |     |      | μs   |

| Bus line capacitive load                   |                     |                                                   |      |     | 150  | pF   |

| Standard/Fast/Fast+ mod                    | le                  |                                                   |      |     |      |      |

| SCL clock frequency                        | f <sub>SCL</sub>    | Note 4                                            | 0    |     | 1000 | kHz  |

| Start condition setup time                 | tsu_sta             |                                                   | 0.26 |     |      | us   |

| Start condition hold time                  | t <sub>H_STA</sub>  |                                                   | 0.26 |     |      | us   |

| SCL low time                               | t <sub>W_CL</sub>   |                                                   | 0.5  |     |      | us   |

| SCL high time                              | t <sub>W_CH</sub>   |                                                   | 0.26 |     |      | us   |

| 2-wire SCL and SDA rise time               | t <sub>R</sub>      |                                                   |      |     | 1000 | ns   |

| 2-wire SCL and SDA fall time               | t <sub>R</sub>      |                                                   |      |     | 300  | ns   |

| Data setup time                            | t <sub>SU_D</sub>   |                                                   | 50   |     |      | ns   |

| Data hold-time                             | t <sub>H_D</sub>    |                                                   | 0    |     |      | ns   |

| Stop condition setup time                  | t <sub>SU_STO</sub> |                                                   | 0.26 |     |      | us   |

| High speed mode                            |                     |                                                   |      |     |      |      |

| SCL clock frequency                        | f <sub>SCL</sub>    | Requires<br>V <sub>DDIO</sub> ≥ 1.8 V<br>(Note 4) | 0    |     | 3400 | kHz  |

| Start condition setup time                 | t <sub>SU_STA</sub> |                                                   | 160  |     |      | ns   |

Datasheet Revision 3.1 04-May-2017

| Start condition hold time         | t <sub>H_STA</sub>  | 160 |     | ns |

|-----------------------------------|---------------------|-----|-----|----|

| SCL low time                      | t <sub>SCL_LO</sub> | 160 |     | ns |

| SCL high time                     | t <sub>SCL_HI</sub> | 60  |     | ns |

| 2-wire SCL and SDA rise/fall time | t <sub>R</sub>      |     | 160 | ns |

| Data setup time                   | t <sub>SU_D</sub>   | 10  |     | ns |

| Data hold-time                    | t <sub>H_D</sub>    | 0   |     | ns |

| Stop condition setup time         | tsu_sto             | 160 |     | ns |

Note 4 Minimum clock frequency is 10 kHz if 2W\_TO is enabled

### 7.5 Temperature Supervision

Unless otherwise noted, the following is valid for  $V_{IN}$  = 4.3 to 13.5 V,  $V_{BAT}$  = 2.6 to 4.4 V

**Table 11: Temperature Supervision**

| Parameter                      | Symbol                 | Test conditions                    | Min | Тур | Max | Unit |

|--------------------------------|------------------------|------------------------------------|-----|-----|-----|------|

| POR temperature threshold      | T <sub>JUNC_POR</sub>  |                                    |     | 150 |     | °C   |

| Critical temperature threshold | T <sub>JUNC_CRIT</sub> |                                    |     | 140 |     | °C   |

| Warning temperature threshold  | T <sub>JUNC_WARN</sub> | Rising threshold<br>TJUNC_WARN=0xB |     | 125 |     | °C   |

|                                |                        | Rising threshold<br>TJUNC_WARN=0x0 |     | 70  |     | °C   |

### 7.6 V<sub>BAT</sub> Monitoring

Unless otherwise noted, the following is valid for TA = -40 to +85  $^{\circ}$ C

Table 12: V<sub>BAT</sub> Monitoring

| Parameter                    | Symbol                   | Test conditions                   | Min   | Тур  | Max   | Unit |

|------------------------------|--------------------------|-----------------------------------|-------|------|-------|------|

| Overvoltage threshold        | V <sub>BAT_OV</sub>      | Rising threshold, VBAT_OV = 0x3C  |       | 5.1  |       | V    |

|                              |                          | Rising threshold, VBAT_OV = 0x20  |       | 4.4  |       | V    |

|                              |                          | Rising threshold, VBAT_OV = 0x00  |       | 3.6  |       | V    |

| Undervoltage threshold       | V <sub>BAT_UV</sub>      | Falling threshold, VBAT_UV = 0x32 |       | 3.25 |       | V    |

|                              |                          | Falling threshold, VBAT_UV = 0x18 |       | 2.6  |       | V    |

|                              |                          | Falling threshold, VBAT_UV = 0x0  |       | 2.0  |       | V    |

| VBAT monitoring hysteresis   | V <sub>BAT_MON_HYS</sub> |                                   |       | 1.5% |       |      |

| V <sub>BAT_UV</sub> accuracy | V <sub>BAT_UV_ACC</sub>  |                                   | -3%   |      | +3%   |      |

| V <sub>BAT_OV</sub> accuracy | V <sub>BAT_OV_ACC</sub>  |                                   | -1.6% |      | +1.6% |      |

Datasheet Revision 3.1 04-May-2017

### 7.7 Current Consumption

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85  $^{\circ}C$

### **Table 13:Current Consumption**

| Parameter               | Symbol                      | Conditions                                                      | Min | Тур | Max | Unit |

|-------------------------|-----------------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| Current (no-power mode) | I <sub>Q_NO_PWR_</sub> VBAT | V <sub>BAT</sub> = 3.6 V                                        | 1   | 5   | 12  | μΑ   |

| Current (disabled mode) | I <sub>Q_DIS_VIN</sub>      | $V_{IN} = 5 \text{ V}, V_{BAT} = 2.6 \text{ to } 4.4 \text{ V}$ | 100 | 250 | 400 | μΑ   |

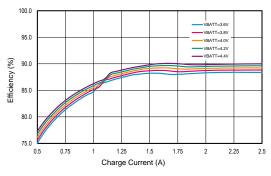

# **8 Typical Characteristics**

Figure 4: Efficiency V<sub>IN</sub> = 12 V

Figure 5: Efficiency V<sub>IN</sub> = 9 V

Figure 6: Efficiency  $V_{IN} = 5 \text{ V}$

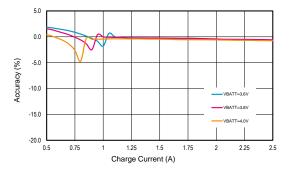

Figure 7: Accuracy V<sub>IN</sub> = 12 V

Figure 8: Accuracy V<sub>IN</sub> = 9 V

Figure 9: Accuracy  $V_{IN} = 5 \text{ V}$

# 9 System Block Diagram

A block diagram of a typical application is illustrated in Figure 10.

Figure 10: DA9155M System Block Diagram

#### 9.1 Main Charger

The main charger is a fully featured charger that can operate as a stand-alone device. It is also designed to support an external slave charger. The main charger is responsible for the following functions:

- Charging control (pre-charge, CC, CV, JEITA)

- Battery detection

- Battery activation

- Battery pre-charge

- CV-phase

- IBUS sensing (IBUSM + IBUSS)

- Reverse-current protection

- IBATM regulation

- IBAT sensing (IBATM + IBATS)

- Battery isolation

- TBAT monitoring

- VBAT sensing

#### 9.2 Slave Charger

The slave charger provides a regulated current (IBATS) and it is enabled only in the CC-phase of charging. The slave charger does not feature a VBAT regulation loop, and therefore, does not operate during CV-phase of charging. It is controlled by the application processor. The slave charger is responsible for the following functions:

- IBATS regulation

- Hazard detection (VBAT over- and undervoltage)

For more details about the slave charger operation and the system integration, please refer to the application note.

# 10 Functional Description

#### 10.1 Control Signals

#### 10.1.1 EN

The EN pin controls the BUCK\_EN register. A rising edge sets the register and a falling edge clears it. The rising edge of the EN pin has to occur when DA9155M is in the disabled mode. The application processor can start the Buck by asserting the EN pin or by setting the BUCK\_EN bit through the 2-wire interface.

The level of the EN pin can be read from S\_EN\_PIN register.

A fault condition in the system (VIN\_DROP, VIN\_OV, VIN\_UV, VBAT\_OV, VBAT\_UV, VIO\_UV, TJUNC\_CRIT) de-asserts BUCK\_EN and triggers a transition to the disabled mode. If a rising edge of the EN pin occurs while the fault condition remains, the Buck is not enabled and an event indicating a blocked enable is triggered (E\_EN\_BLOCK). Re-enabling the Buck after a fault condition requires that status and event bits are cleared.

The EN pin can be shorted to ground when not used.

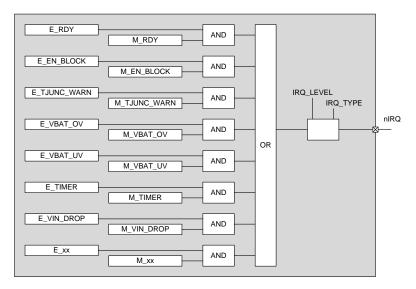

#### 10.1.2 nIRQ

nIRQ is a level sensitive interrupt signal. It can be configured either as a push-pull or as an open drain output (IRQ\_TYPE), and the polarity can be selected (IRQ\_LEVEL). The structure of the interrupt logic is depicted in Figure 11.

nIRQ is asserted when an un-masked event is asserted. The nIRQ will not be released until all event registers have been cleared. New events that occur during reading an event register will be held until the event register has been cleared, ensuring that the host processor does not miss them.

Figure 11: DA9155M Interrupt Logic

#### 10.2 2-Wire Interface

The 2-wire interface provides access to control and status registers. The interface supports operations compatible to standard, fast, fast-plus and high speed mode of the I<sup>2</sup>C bus specification Rev. 3.

Communication on the 2-wire bus is always between two devices, one acting as the master and the other as the slave. The DA9155M will only operate as a slave.

SCL carries the 2-wire clock and SDA carries the bi-directional data. The 2-wire interface is opendrain supporting multiple devices on a single line. The bus lines have to be pulled high by external pull-up resistors (2 –20 k $\Omega$ ). These are often shared between multiple devices connected to the interface. The attached devices only drive the bus lines low by connecting them to ground. As a result, two devices cannot conflict if they drive the bus simultaneously. In standard/fast mode the highest frequency of the bus is 400 kHz. The exact frequency can be determined by the application and it does not have any relation to the DA9155M internal clock signals. DA9155M will follow the host clock speed within the described limitations and does not initiate any clock arbitration or slow down. An automatic interface reset can be triggered in case the clock signal ceases to toggle for >35 ms (controlled in 2W\_TO).

Bus clear, if the SDA is stuck, is achieved after receiving 9 clock pulses. Operation in high speed mode at 3.4 MHz requires a minimum interface supply voltage of 1.8 V and a mode change in order to enable spike suppression and slope control characteristics compatible to the I<sup>2</sup>C specification. The high speed mode can be enabled on a transfer-by-transfer basis by sending the master code (0000 1XXX) at the beginning of the transfer. The DA9155M does not make a use of clock stretching and delivers read data without additional delay up to 3.4 MHz.

Alternatively the interface can be configured to use high speed mode continuously via PM\_IF\_HSM, so that the master code is not required at the beginning of every transfer. This reduces communication overhead on the bus, but limits the attachable bus slaves to compatible devices.

#### 10.2.1 Register Map Paging

The 2-wire interface has direct access to two pages of the register map (up to 256 addresses). The register at address zero on each page is used as a page control register (the LSB of the PAGE register is ignored). Writing to the page control register changes the active page for all subsequent read/write operations unless an automatic return to page 0 was selected by asserting the REVERT register.

Alternatively, DA9155M offers a way to access register pages which avoids changing the active page via the PAGE register. DA9155M can respond to multiple consecutive slave addresses and update the PAGE register automatically based on the slave address. For example, when IF\_BASE\_ADDR = 0x58, the PAGE register responds to the slave address as follows:

Slave address =  $0x58 \Rightarrow PAGE = 0x00$

Slave address =  $0x59 \Rightarrow PAGE = 0x02$

Slave address = 0x5A ⇒ PAGE = 0x04

Slave address =  $0x5B \Rightarrow PAGE = 0x06$

The consecutive addresses are obtained by replacing the two LSB in IF\_BASE\_ADDR with "00", "01", "10", or "11". This feature can be enabled in the I2C\_EXTEND\_EN register.

#### 10.2.2 Details of the 2-Wire Protocol

All data is transmitted across the 2-wire bus in 8-bit groups. To send a bit the SDA line is driven at the intended state while the SCL is low. Once the SDA has settled, the SCL line is brought high and then low. This pulse on SCL clocks the SDA bit into the receiver's shift register.

A two-byte serial protocol is used containing one address byte and one data byte. Data and address transfer is transmitted MSB first for both read and write operations. All transmission begins with the START condition from the master during which the bus is in IDLE state (the bus is free). It is initiated by a high-to-low transition on the SDA line while the SCL is in the high state. A STOP condition is indicated by a low-to-high transition on the SDA line while the SCL is in the high state. The START and STOP conditions are illustrated in Figure 12.

Figure 12: Timing of the START and STOP Conditions

The 2-wire bus will be monitored by DA9155M for a valid slave address whenever the interface is enabled. It responds immediately when it receives its own slave address. This is acknowledged by pulling the SDA line low during the following clock cycle (white blocks marked with 'A' in the following figures).

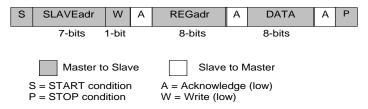

The protocol for a register write from master to slave consists of a START condition, a slave address, a read/write-bit, 8-bit address, 8-bit data, and a STOP condition. DA9155M responds to all bytes with an ACK. A register write operation is illustrated in Figure 13.

Figure 13: Byte Write Operation

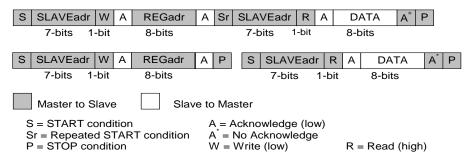

When the host reads data from a register it first has to write-access DA9155M the target register address and then read-access DA9155M with a repeated START or alternatively a second START condition. After receiving the data, the host sends NACK and terminates the transmission with a STOP condition. This is illustrated in Figure 14.

Figure 14: Examples of Byte Read Operations

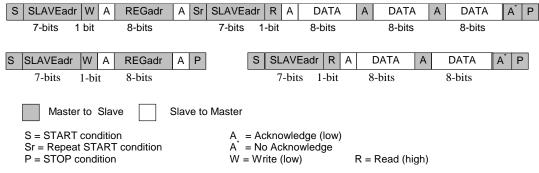

Consecutive (page) read-out mode is initiated from the master by sending an ACK instead of NACK after receiving a byte, see Figure 15. The 2-wire control block then increments the address pointer to the next register address and sends the data to the master. This enables an unlimited read of data bytes until the master sends a NACK directly after receiving the data, followed by a subsequent STOP condition. If a non-existent 2-wire address is read out then the DA9155M will return code zero.

Figure 15: 2-Wire Page Read

The slave address after the Repeated START condition must be the same as the previous slave address.

Consecutive (page) write mode is supported if the master sends several data bytes following a slave register address. The 2-wire control block then increments the address pointer to the next 2-wire address, stores the received data, and sends an ACK until the master sends a STOP condition. The page write mode is illustrated in Figure 16.

Figure 16: 2-Wire Page Write

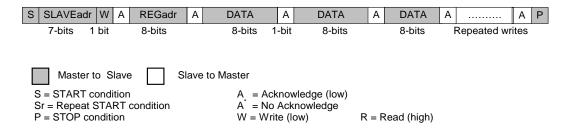

Via control WRITE\_MODE, a repeated write mode can be enabled. In this mode, the master can execute back-to-back write operations to non-consecutive addresses. This is achieved by transmitting register address and data pairs. The data will be stored in the address specified by the preceding byte. The repeated write mode is illustrated in Figure 17.

| S SLAVEadr W A      | REGadr    | A DATA         | А         | REGadr       | А     | DATA        | Α |             | Α     | Р |

|---------------------|-----------|----------------|-----------|--------------|-------|-------------|---|-------------|-------|---|

| 7-bits 1 bit        | 8-bits    | 8-bits         | 1-bit     | 8-bits       | ,     | 8-bits      |   | Repeated wi | rites |   |

|                     |           |                |           |              |       |             |   |             |       |   |

|                     |           |                |           |              |       |             |   |             |       |   |

| Master to Slav      | e SI      | lave to Master |           |              |       |             |   |             |       |   |

| S = START condition | Ì         | A =            | Acknow    | vledge (low) |       |             |   |             |       |   |

| Sr = Repeat START   | condition | A =            | No Ack    | nowledge     |       |             |   |             |       |   |

| P = STOP condition  |           | W = Y          | Write (le | ow)          | R = F | Read (high) |   |             |       |   |

Figure 17: 2-Wire Repeated Write

If a new START or STOP condition occurs within a message, the bus will return to IDLE-mode.

#### 10.3 Buck Converter

DA9155M features a Buck converter that provides up to 2.5 A of regulated output current, with  $I_{\text{OUT\_ACC}}$  regulation accuracy.

The output current of the Buck can be selected from a control register (BUCK\_IOUT). In order to limit inrush current from the power supply, the Buck converter features a soft-start function. Whenever the Buck is enabled or the output current is changed, the output current is ramped to the target value by running through the BUCK\_IOUT steps at a rate defined by the START\_SLEW and DEF\_SLEW\_RATE registers. As the names imply, START\_SLEW is used when the Buck is enabled and DEF\_SLEW\_RATE is used when disabling the Buck or changing between IOUT settings. The slew rate timings are summarized in Table 14.

**Table 14: Slew Rate Timings with Different Register Settings**

| SLEW[2:0] | Time per IOUT Step [μs] | Ramp Rate<br>[mA/µs] | Ramp Time 250 mA to 2.5 A [µs] |

|-----------|-------------------------|----------------------|--------------------------------|

| 0x5       | 10.67                   | 0.938                | 2400                           |

| 0x6       | 21.30                   | 0.469                | 4800                           |

| 0x7       | 42.70                   | 0.234                | 9600                           |

The Buck features a programmable peak current limit (BUCK\_ILIM), which protects the pass devices and the inductor. Hitting the limit triggers an E\_BUCK\_ILIM event. During normal operation the E\_BUCK\_ILIM event should not occur. However, the event can be used as an indication of abnormal system behaviour.

The Buck is enabled either by writing directly to a control register BUCK\_EN or asserting the EN input. The soft-start feature described above is effective when the Buck is enabled or disabled.

The switching frequency is chosen high enough to allow the use of a small 0.47 µH inductor. Furthermore, the switching frequency can be adjusted with the BUCK\_FSW and OSC\_FRQ registers in order to avoid interference to/from the main charger. The Buck also features an automatic

frequency fold back mode, where the switching frequency is stepwise reduced until a required duty cycle can be achieved. Without the frequency fold back the duty cycle is limited by the Buck's minimum off-time.

It is recommended to configure the switching frequency to 1 MHz when operating with 5 V V<sub>IN</sub>.

#### 10.4 Safety Timer

DA9155M features a safety timer that is intended to disable the Buck converter in the event of system malfunction during charging.

Whenever the Buck is enabled, either through the EN pin or from a register, the safety timer is loaded with a pre-programmed value (TIMER\_LOAD) and it starts decrementing. In normal operation the application processor should periodically re-initialize the safety timer by writing a new value to the TIMER\_LOAD register. The value of the counter can be read from the TIMER\_COUNT register. However, if the timer reaches zero an event is asserted, and the Buck is automatically disabled. The BUCK\_EN register is cleared and the Buck is stopped by ramping down the output current at a rate defined in SLEW\_RATE. Resuming normal operation requires that the event is cleared.

#### 10.5 V<sub>IN</sub> Monitoring

$V_{IN}$  is monitored to detect a power supply insertion, and to ensure that  $V_{IN}$  is within an acceptable voltage range. The monitoring is illustrated in Figure 18.

When  $V_{\text{IN}}$  is below the VIN2BAT threshold DA9155M stays in the no-power mode. When  $V_{\text{IN}}$  rises above the VIN2BAT threshold, DA9155M moves to the reset mode where the internal supply and reference are enabled.

Figure 18: V<sub>IN</sub> Monitoring of DA9155M

In reset, disabled, and active mode,  $V_{\text{IN}}$  is monitored against over- and undervoltage. If over- or undervoltage is detected, an event is triggered (E\_VIN\_OV, E\_VIN\_UV), the BUCK\_EN register is cleared, and DA9155M moves to disabled mode. Re-enabling the Buck requires that the status and event bits are cleared.

During charging  $V_{\text{IN}}$  is monitored for weak charger or high impedance USB cable detection. If  $V_{\text{IN}}$  drops below the threshold  $V_{\text{IN}\_DROP}$ , an event is triggered (E\_VIN\_DROP) and the Buck is automatically disabled. The BUCK\_EN register is cleared and the Buck is stopped by ramping down the output current at a rate defined in DEF\_SLEW\_RATE. The Buck does not start automatically when the  $V_{\text{IN}}$  rises above the threshold. Resuming normal operation requires that the status and event bits are cleared. This feature is targeted for use cases where the  $V_{\text{IN}}$  is above the standard

$V_{BUS}$ , in which case the undervoltage lockout is too low to detect a weak supply. By default,  $V_{IN\_DROP}$  is set to the same voltage as the  $V_{IN\_UVLO}$ , which effectively disables the  $V_{IN\_DROP}$ .

The status of the  $V_{IN}$  monitoring comparators can be read out from the status registers (S\_VIN\_UV, S\_VIN\_OV, S\_VIN\_DROP).

#### 10.6 V<sub>BAT</sub> Monitoring

The V<sub>BAT</sub> monitoring is illustrated in Figure 18. The slave charger has to monitor the battery voltage in case of fault conditions during charging, meaning that battery over- and undervoltage have to be detected.

DA9155M features two factory programmable settings for handling the monitoring:

- An overvoltage or undervoltage event triggers an event (E\_VBAT\_OV, E\_VBAT\_UV) and the BUCK\_EN register is de-asserted. Resuming normal operation requires that V<sub>BAT</sub> is within normal range and the events are cleared. The supervision of the battery voltage V<sub>BAT</sub> is done by comparators.

- 2. An overvoltage or undervoltage event does not disable the Buck converter. Only the status registers are updated (default).

The V<sub>BAT</sub> monitoring status comparators can always be read out from the status registers (S\_VBAT\_UV, S\_VBAT\_OV).

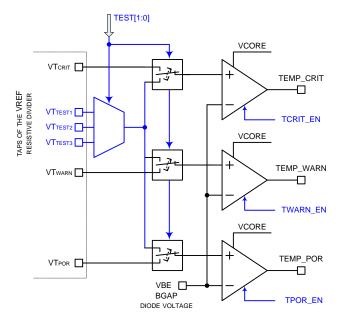

#### 10.7 Junction Temperature Supervision

To protect DA9155M from damage due to excessive power dissipation the junction temperature is monitored continuously. The monitoring is split into three temperature ranges  $T_{JUNC\_WARN}$  (125 °C),  $T_{JUNC\_CRIT}$  (140 °C), and  $T_{JUNC\_POR}$  (150 °C).

If the junction temperature rises above the first threshold (TJUNC\_WARN), the event E\_TJUNC\_WARN is asserted. If the event is not masked, this will fire an interrupt. This first level of temperature supervision is intended for non-invasive temperature control, where the necessary measures for cooling the system down are left to the host software. The status of the  $T_{\text{JUNC}\_WARN}$  comparator can be read from S\_TJUNC\_WARN. The interrupt is only generated when the temperature crosses the threshold from low to high. After the interrupt, the application processor can read out the comparator status to detect when the temperature drops below the threshold.

If the junction temperature continues to rise and crosses the second threshold ( $T_{JUNC\_CRIT}$ ), an event is fired (E\_TJUNC\_CRIT), the BUCK\_EN is de-asserted, and DA9155M moves to the disabled mode. Resuming normal operation requires that  $T_{JUNC}$  drops below  $T_{JUNC\_CRIT}$  and the event is cleared.

There is also a third temperature threshold ( $T_{JUNC\_POR}$ ) which causes DA9155M to enter the reset mode. DA9155M stays in the reset mode as long as the junction temperature is above  $T_{JUNC\_CRIT}$ .

Figure 19: Junction Temperature Monitoring of DA9155M

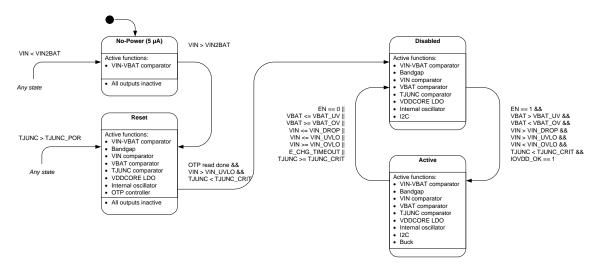

#### 10.8 Power Modes

The power modes of DA9155M are illustrated in Figure 20.

Figure 20: Power Modes of DA9155M.

**Note 1** The conditions for state transitions follow the C-language syntax.

#### 10.8.1 No-Power

The no-power mode is the initial state of DA9155M. Only the  $V_{IN}$ - $V_{BAT}$  comparator is active in this state. When  $V_{IN}$  rises above  $V_{BAT}$ , DA9155M enters the reset mode. All IOs are in their inactive state. The no-power mode is entered whenever  $V_{IN}$  drops below  $V_{BAT}$ .

#### 10.8.2 Reset

DA9155M enters the reset mode when a power supply is attached and  $V_{IN}$  rises above  $V_{BAT}$ . In the reset mode, DA9155M will enable the internal reference, the internal supply, execute the reset sequence, and read the OTP. Once the OTP is read and all the  $V_{IN}$  conditions are met, DA9155M moves automatically to the disabled mode.

Datasheet Revision 3.1 04-May-2017

The junction temperature monitoring is also enabled in the reset mode. If a junction over-temperature is detected during operation (TJUNC ≥ TJUNC\_POR), DA9155M moves back to the reset mode.

#### 10.8.3 Disabled

In the disabled mode DA9155M is fully functional but the Buck has not been enabled. An event is fired when entering the disabled mode to notify the application processor that the slave charger is ready for operation. If a fault condition exists ( $T_{JUNC}$ ,  $V_{BAT}$ , or  $V_{IN}$ ), the enable signal is blocked, DA9155M stays in the disabled mode, and an event is triggered.

DA9155M moves to the active mode when the Buck is enabled either by asserting the EN signal or by setting the BUCK\_EN register.

#### 10.8.4 Active

In the active mode DA9155M is fully functional and the Buck is running.

DA9155M moves back to the disabled mode if the Buck is disabled, the safety timer expires, or if there is a fault condition ( $T_{JUNC}$ ,  $V_{BAT}$ , or  $V_{IN}$ ).

# 11 Register Map

# 11.1 Overview

| Addr       | Register        | 7              | 6          | 5             | 4            | 3            | 2             | 1            | 0            |

|------------|-----------------|----------------|------------|---------------|--------------|--------------|---------------|--------------|--------------|

| Page Con   | itrol           |                |            |               |              |              |               |              |              |

| 0x000      | PAGE_CTRL_0     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Status An  | d Events        |                |            |               |              |              |               |              |              |

| 0x001      | STATUS_A        | S_EN_BLOCK     | S_VIN_OV   | S_VIN_DROP    | S_VIN_UV     | S_VBAT_OV    | S_VBAT_UV     | S_TJUNC_CRIT | S_TJUNC_WARN |

| 0x002      | STATUS_B        |                |            |               |              |              | S_BUCK_ILIM   | S_EN_PIN     | MODE         |

| 0x003      | EVENT_A         | E_EN_BLOCK     | E_VIN_OV   | E_VIN_DROP    | E_VIN_UV     | E_VBAT_OV    | E_VBAT_UV     | E_TJUNC_CRIT | E_TJUNC_WARN |

| 0x004      | EVENT_B         |                |            |               | E_TJUNC_POR  | E_VDDIO_UV   | E_TIMER       | E_BUCK_ILIM  | E_RDY        |

| 0x005      | IRQ_MASK_A      | M_EN_BLOCK     | M_VIN_OV   | M_VIN_DROP    | M_VIN_UV     | M_VBAT_OV    | M_VBAT_UV     | M_TJUNC_CRIT | M_TJUNC_WARN |

| 0x006      | IRQ_MASK_B      |                |            |               | M_TJUNC_POR  | M_VDDIO_UV   | M_TIMER       | M_BUCK_ILIM  | M_RDY        |

| VIN And \  | /BAT Monitoring |                |            |               |              |              |               |              |              |

| 0x007      | CONTROL_A       | VIN_DROP       |            |               |              |              |               |              |              |

| 0x008      | CONTROL_B       |                |            | VBAT_UV       |              |              |               |              |              |

| 0x009      | CONTROL_C       |                |            | VBAT_OV       |              |              |               |              |              |

| Configura  | tion            |                |            |               |              |              |               |              |              |

| 0x00A      | CONTROL_D       |                | START_SLEW |               |              |              | DEF_SLEW_RATE |              |              |

| 0x00B      | CONTROL_E       |                |            |               | TIMER_DIS    | TJUNC_WARN   |               |              |              |

| Safety Tin | ner             |                |            |               |              |              |               |              |              |

| 0x00C      | TIMER_A         | TIMER_COUNT    |            |               |              |              |               |              |              |

| 0x00D      | TIMER_B         | TIMER_LOAD     |            |               |              |              |               |              |              |

| Buck Con   | trol            |                |            |               |              |              |               |              |              |

| 0x00E      | BUCK_CTRL       |                |            |               |              |              |               |              | BUCK_EN      |

| 0x00F      | BUCK_ILIM       |                |            |               | BUCK_ILIM    |              |               |              |              |

| 0x010      | BUCK_IOUT       | BUCK_IOUT      |            |               |              |              |               |              |              |

| Interface  |                 |                |            |               |              |              |               |              |              |

| 0x011      | INTERFACE       | IF_BASE_ADDR   |            |               | 1            |              |               |              |              |

| 0x012      | CONFIG_A        | VDDIO_CONF     |            | I2C_EXTEND_EN | 2W_TO        | 2W_IF_HSM    |               | IRQ_LEVEL    | IRQ_TYPE     |

| Configura  | tion            | •              |            |               |              |              |               | 1            |              |

| 0x013      | CONFIG_B        | OSC_FRQ        |            |               |              |              |               | BUCK_FSW     |              |

| Page Con   | trol            | •              |            |               |              |              |               |              |              |

| 0x080      | PAGE_CTRL_1     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Page Con   | trol            | •              |            | Ī             |              |              |               |              |              |

| 0x100      | PAGE_CTRL_2     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Page Con   | trol            | T              |            | 1             |              |              |               |              |              |

| 0x180      | PAGE_CTRL_3     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Page Con   |                 | T              |            | 1             |              |              |               |              |              |

| 0x200      | PAGE_CTRL_4     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Page Con   | trol            | ı              |            | 1             |              |              |               |              |              |

| 0x280      | PAGE_CTRL_5     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Page Con   |                 | ı              |            |               |              |              |               |              |              |

| 0x300      | PAGE_CTRL_6     | REVERT         | WRITE_MODE | PAGE          |              |              |               |              |              |

| Trimming   | and Engineering | 1              |            |               | 1            |              |               |              |              |

| 0x319      | ANA_ENG_OTP_    | ENG_VDDIO_UV_D |            | ENG_TJUNC_CRI | ENG_VBAT_OV_ | ENG_VBAT_UV_ |               | ENG_VIN_DROP |              |

| 5,010      | 9               | IS             |            | T_DIS         | DIS          | DIS          |               | _DIS         |              |

# 11.2 Register Descriptions

# 11.3 Page 0

# 11.3.1 Page Control

#### **PAGE\_CTRL\_0 (0x000)**

| Field      | Slice | Description                                                                                                                                                              |

|------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REVERT     | 7:7   | PAGE maintains its value until re-written     PAGE reverts to 0 after one access                                                                                         |

| WRITE_MODE | 6:6   | Behavior upon sequential write accesses over the 2-wire interface  0: Write data to consecutive addresses  1: Write data to arbitrary addresses using address-data pairs |

| PAGE       | 5:0   | Top 6 bits of the register address.                                                                                                                                      |

#### 11.3.2 Status and Events

### STATUS\_A (0x001)

| Field        | Slice | Description                                                       |

|--------------|-------|-------------------------------------------------------------------|

| S_EN_BLOCK   | 7:7   | A status bit in STATUS_A is blocking the buck from being enabled. |

| S_VIN_OV     | 6:6   | VIN overvoltage comparator status                                 |

| S_VIN_DROP   | 5:5   | VIN DROP comparator status                                        |

| S_VIN_UV     | 4:4   | VIN undervoltage comparator status                                |

| S_VBAT_OV    | 3:3   | VBAT overvoltage comparator status                                |

| S_VBAT_UV    | 2:2   | VBAT undervoltage comparator status.                              |

| S_TJUNC_CRIT | 1:1   | TJUNC CRIT comparator status                                      |

| S_TJUNC_WARN | 0:0   | TJUNC_WARN comparator status                                      |

### STATUS\_B (0x002)

| Field       | Slice | Description                                        |

|-------------|-------|----------------------------------------------------|

| Reserved    | 8:3   |                                                    |

| S_BUCK_ILIM | 2:2   | Status (debounced) of the peak current comparator. |

| S_EN_PIN    | 1:1   | Status of the EN pin.                              |

| MODE        | 0:0   | DA9155M mode: disabled (0) or active (1).          |

### **EVENT\_A (0x003)**

| Field      | Slice | Description                                                                                           |

|------------|-------|-------------------------------------------------------------------------------------------------------|

| E_EN_BLOCK | 7:7   | An enable signal was blocked. The reason for the blocking can be read out from the STATUS_A register. |

| E_VIN_OV   | 6:6   | VIN exceeded the VIN_OVLO threshold.                                                                  |

| E_VIN_DROP | 5:5   | VIN dropped below the VIN_DROP threshold.                                                             |

| E_VIN_UV   | 4:4   | VIN dropped below the VIN_UVLO threshold.                                                             |

| E_VBAT_OV  | 3:3   | The battery voltage exceeded the VBAT_OV threshold.                                                   |

| E_VBAT_UV  | 2:2   | The battery voltage dropped below the VBAT_UV threshold.                                              |

| E_TJUNC_CRIT | 1:1 | The junction temperature exceeded the TJUNC_CRIT threshold.                                              |

|--------------|-----|----------------------------------------------------------------------------------------------------------|

| E_TJUNC_WARN | 0:0 | Junction temperature crossed the TJUNC_WARN threshold. Only a low-to-high transition triggers the event. |

#### **EVENT\_B (0x004)**

| Field       | Slice | Description                                                                                                                                                                        |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved    | 7:5   |                                                                                                                                                                                    |

| E_TJUNC_POR | 4:4   | The junction temperature crossed the TJUNC_POR threshold and caused an entry to the reset mode. This bit is only reset upon a transition from the no-power mode to the reset mode. |

| E_VDDIO_UV  | 3:3   | VDDIO dropped below a threshold. This event causes the I2C interface to be reset.                                                                                                  |

| E_TIMER     | 2:2   | The safety timer expired.                                                                                                                                                          |

| E_BUCK_ILIM | 1:1   | The peak output current exceeded the limit BUCK_ILIM.                                                                                                                              |

| E_RDY       | 0:0   | DA9155M moved to the disabled mode. The event is not generated if VDDIO is below the monitoring threshold (VDDIO_CONF).                                                            |

### IRQ\_MASK\_A (0x005)

| Field        | Slice | Description               |

|--------------|-------|---------------------------|

| M_EN_BLOCK   | 7:7   | Mask bit for E_EN_BLOCK   |

| M_VIN_OV     | 6:6   | Mask bit for E_VIN_OV     |

| M_VIN_DROP   | 5:5   | Mask bit for E_VIN_DROP   |

| M_VIN_UV     | 4:4   | Mask bit for E_VIN_UV     |

| M_VBAT_OV    | 3:3   | Mask bit for E_VBAT_OV    |

| M_VBAT_UV    | 2:2   | Mask bit for E_VBAT_UB    |

| M_TJUNC_CRIT | 1:1   | Mask bit for E_TJUNC_CRIT |

| M_TJUNC_WARN | 0:0   | Mask bit for E_TJUNC_WARN |

### IRQ\_MASK\_B (0x006)

| Field       | Slice | Description              |

|-------------|-------|--------------------------|

| Reserved    | 7:5   |                          |

| M_TJUNC_POR | 4:4   | Mask bit for E_TJUNC_POR |

| M_VDDIO_UV  | 3:3   | Mask bit for E_VDDIO_UV  |

| M_TIMER     | 2:2   | Mask bit for E_TIMER     |

| M_BUCK_ILIM | 1:1   | Mask bit for E_BUCK_ILIM |

| M_RDY       | 0:0   | Mask bit for E_RDY       |

# 11.3.3 VIN and VBAT Monitoring

### CONTROL\_A (0x007)

| Field    | Slice | Description                                                    |

|----------|-------|----------------------------------------------------------------|

| VIN_DROP | 7:0   | VIN drop threshold.<br>N=0x0,0x1,,0xE: VIN_DROP=4.3+(N×0.05) V |

| N=0x32,0x33,,0x3B: VIN_DROP=11.0+((N-0x31)x0.1) V The maximum value is 12.0 V (0x3B). Any value greater than the maximum will be stored in the register but limited to the maximum at the output. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N=0x28,0x29,,0x31: VIN_DROP=9.0+((N-0x27)x0.2) V                                                                                                                                                  |

| N=0x1E,0x1F,,0x27: VIN_DROP=8.0+((N-0x1D)x0.1) V                                                                                                                                                  |

| N=0xF,0x10,,0x1D: VIN_DROP=5.0+((N-0xE)×0.2) V                                                                                                                                                    |

### CONTROL\_B (0x008)

| Field    | Slice | Description                                 |

|----------|-------|---------------------------------------------|

| Reserved | 7:6   |                                             |

| VBAT_UV  | 5:0   | VBAT undervoltage. VBAT_UV=2.0+(Nx0.025) V. |

# CONTROL\_C (0x009)

| Field    | Slice | Description                                |

|----------|-------|--------------------------------------------|

| Reserved | 7:6   |                                            |

| VBAT_OV  | 5:0   | VBAT overvoltage. VBAT_OV=3.6+(Nx0.025) V. |

# 11.3.4 Configuration

# CONTROL\_D (0x00A)

| Field         | Slice | Description                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved      | 7:7   |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| START_SLEW    | 6:4   | Slew rate control for the buck start. The enumeration is the same as DEF_SLEW_RATE                                                                                                                                                                                                                                                                                                                                                             |

| Reserved      | 3:3   |                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| DEF_SLEW_RATE | 2:0   | Slew rate control for the output current changes. Each output current step (10 mA) is delayed with T_STEP=OSC/(2^N1), where OSC is the high frequency oscillator (6 MHz default). The minimum value for N is 5 (101). The effective slew rate is then given by the current change (I_DELTA), the number of steps required for the change (I_DELTA/10 mA), and the time spend in each step (T_STEP): SLEW_RATE=I_DELTA/((I_DELTA/10 mA)xT_STEP) |

### CONTROL\_E (0x00B)

| Field      | Slice | Description                                                                     |

|------------|-------|---------------------------------------------------------------------------------|

| Reserved   | 7:5   |                                                                                 |

| TIMER_DIS  | 4:4   | Disables the safety timer.  1 = Safety timer disabled  0 = safety timer enabled |

| TJUNC_WARN | 3:0   | Junction temperature warning threshold. TJUNC_WARN=70+(Nx5) °C                  |

© 2017 Dialog Semiconductor

# 2.5 A Companion Charger for Rapid Charging

### 11.3.5 Safety Timer

### TIMER\_A (0x00C)

| Field       | Slice | Description                                                                                                                                                |

|-------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMER_COUNT | 7:0   | Countdown value of the safety timer. Decremented at 1 s intervals. Reading the register gives the current timer value. Writing the register has no affect. |

### TIMER\_B (0x00D)

| Field      | Slice | Description                                                                                                                                                                                                                                                                                         |

|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMER_LOAD | 7:0   | Safety timer pre-load and re-load. Writing the register when the buck is not enabled sets the pre-load value. The pre-load value is automatically loaded in to TIMER_COUNT the next time the buck is enabled. Writing the register during buck operation loads the written value in to TIMER_COUNT. |

|            |       | TIMER_LOAD provides the time in seconds.                                                                                                                                                                                                                                                            |

|            |       | The minimum value is 0 s (0x00). The maximum value is 255 s (0xFF). The default is set to the maximum time (0xFF).                                                                                                                                                                                  |

#### 11.3.6 Buck Control

#### BUCK\_CTRL (0x00E)

| Field    | Slice | Description                                                                                             |

|----------|-------|---------------------------------------------------------------------------------------------------------|

| Reserved | 7:1   |                                                                                                         |

| BUCK_EN  | 0:0   | Buck enable. The register is also set at the rising edge of the EN pin and cleared at the falling edge. |

### BUCK\_ILIM (0x00F)

| Field     | Slice | Description                                                                                                                                                                                 |

|-----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved  | 7:5   |                                                                                                                                                                                             |

| BUCK_ILIM | 4:0   | Peak current limit. BUCK_ILIM=(3000+N×100) mA The maximum value is 5.5 A (0x19). Any value greater than the maximum will be stored in the register but limited to the maximum at the output |

# BUCK\_IOUT (0x010)