# **General Description**

DA9213, DA9214, and DA9215 are PMUs optimized for the supply of CPUs, GPUs, and DDR memory rails in smartphones, tablets and other portable applications. The fast transient response (10 A/µs) and load regulation are optimized for the latest generation of multi core application processors.

DA9213 operates as a single four-phase buck converter delivering up to 20 A output current.

DA9214 integrates two dual-phase buck converters, capable of delivering 2 x10 A output current.

DA9215 integrates a three-phase buck converter capable of delivering 15 A and a single-phase buck converter delivering 5 A output current.

Each buck regulates a programmable output voltage in the range 0.3 to 1.57 V. With an external resistor divider the output voltage can be set to any voltage between 1.57 V and 4.3 V The input voltage range of 2.8 to 5.5 V makes it suited for a wide variety of low voltage systems, including all Li-lon battery powered applications.

To guarantee the highest accuracy and to support multiple PCB routing scenarios without loss of performance, a remote sensing capability is implemented in DA9213, DA9214, and DA9215.

The power devices are fully integrated, so no external FETs or Schottky diodes are needed.

A programmable soft start-up can be enabled, which limits the inrush current from the input node and secures a slope controlled activation of the rail.

The Dynamic Voltage Control (DVC) supports adaptive adjustment of the supply voltage depending on the processor load, either via direct register writes through the communication interface (I<sup>2</sup>C or SPI compatible) or via an input pin.

DA9213, DA9214, and DA9215 feature integrated over-temperature and over-current protection for increased system reliability without the need for external sensing components. The safety feature set is completed by a VDDIO under voltage lockout.

The configurable I<sup>2</sup>C address selection via GPI allows multiple instances of DA9213, DA9214, and DA9215 or both to be placed in the application sharing the same communication interface with different addresses.

# **Key Features**

- 2.8 V to 5.5 V input voltage

- 0.3 V to 1.57 V output voltage

- 1.57 to 4.3 V with resistor divider

- 20 A DA9213

- 2 x 10 A DA9214

- 1 x 15 A + 1x 5 A DA9215

- 3 MHz nominal switching frequency (allows use of low profile [1 mm] inductors)

- ±1 % accuracy (static)

- ±3 % accuracy (dynamic)

- Dynamic Voltage Control (DVC)

- Automatic phase shedding

- Integrated power switches

- Remote sensing at point of load

- I<sup>2</sup>C/SPI compatible interface

- Adjustable soft start

- -40 to +85 °C temperature range

- Package 66 WL-CSP 0.4 mm pitch

# **Applications**

- TV/media players

- Smartphones

- Tablet PCs

- Ultrabooks

- Mobile computing

# **System Diagrams**

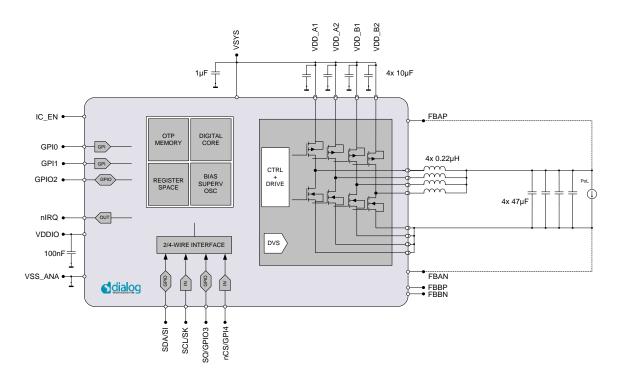

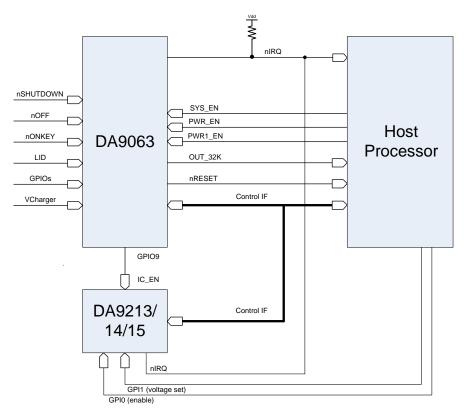

Figure 1: DA9213, DA9214, and DA9215 System Diagram

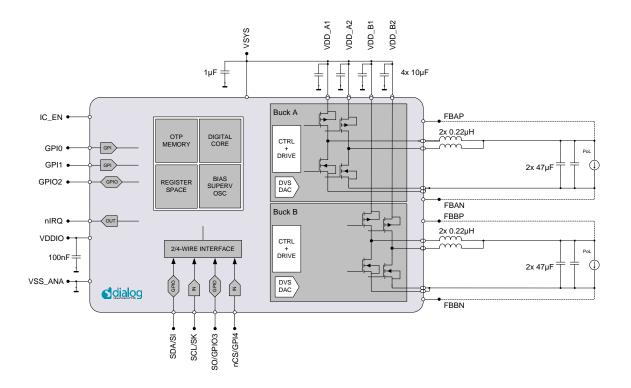

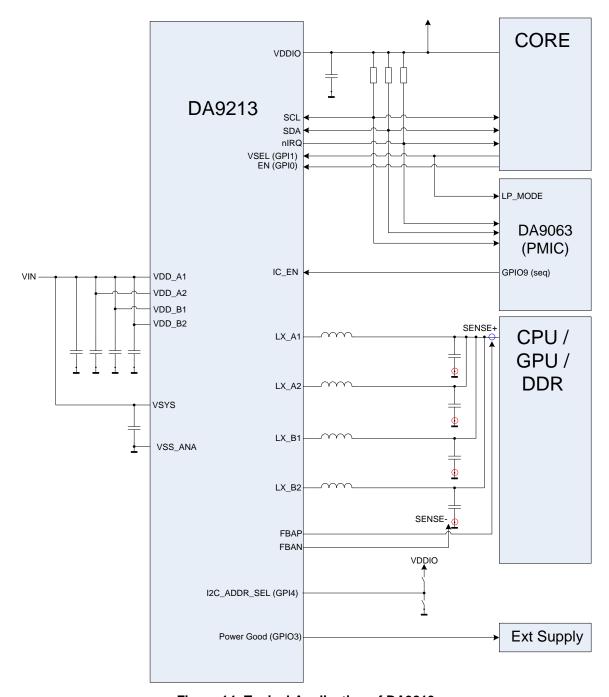

Figure 2: DA9214 System Diagram

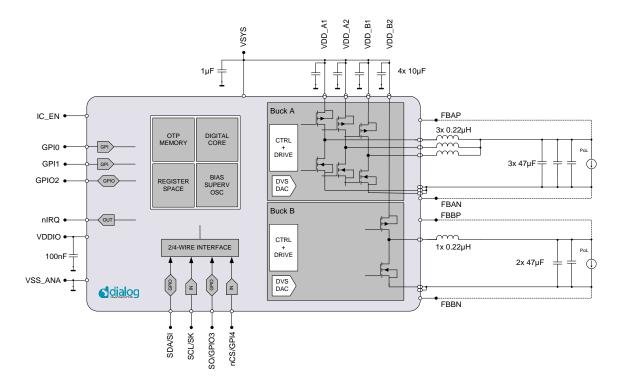

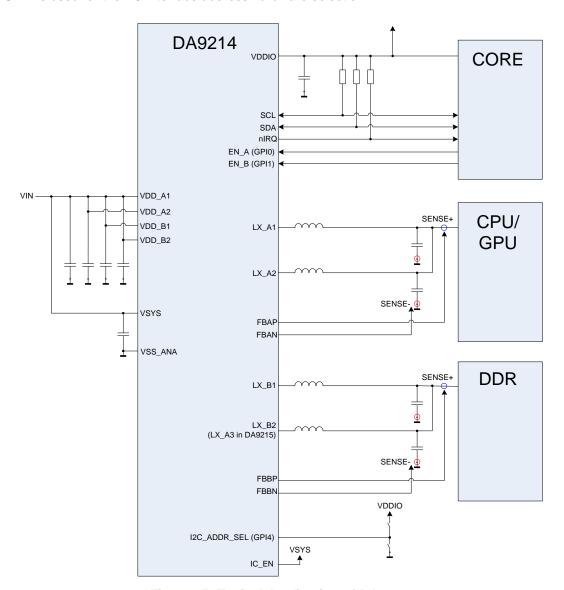

Figure 3: DA9215 System Diagram

## **Contents**

| Ge       | eneral | Descript  | tion                                       | 1  |

|----------|--------|-----------|--------------------------------------------|----|

| Ke       | y Fea  | tures     |                                            | 1  |

| Αp       | plicat | ions      |                                            | 2  |

| Sy       | stem   | Diagram   | ıs                                         | 2  |

| Co       | ontent | s         |                                            | 4  |

|          |        |           |                                            |    |

| •        |        |           |                                            |    |

| . ս<br>1 |        |           | efinitions                                 |    |

| -        |        |           | elilitions                                 |    |

| 2        |        |           |                                            |    |

| 3        |        |           | ximum Ratings                              |    |

| 4        |        |           | ed Operating Conditions                    |    |

| 5        |        |           | aracteristics                              |    |

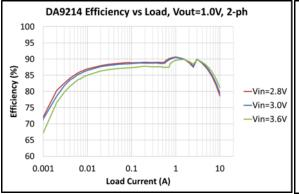

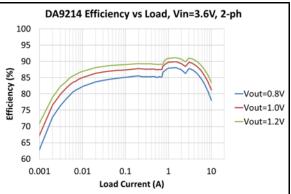

| 6        | Effic  | iency Me  | easurements                                | 19 |

| 7        | Fund   | tional D  | escription                                 | 20 |

|          | 7.1    | DC_DC     | Buck Converter                             | 23 |

|          |        | 7.1.1     | Switching Frequency                        | 24 |

|          |        | 7.1.2     | Operation Modes and Phase Selection        | 24 |

|          |        | 7.1.3     | Output Voltage Selection                   | 24 |

|          |        | 7.1.4     | Soft Start-Up                              | 25 |

|          |        | 7.1.5     | Current Limit                              | 25 |

|          |        | 7.1.6     | Variable VOUT above 1.57 V                 | 26 |

|          | 7.2    | Ports D   | Description                                | 27 |

|          |        | 7.2.1     | VDDIO                                      | 27 |

|          |        | 7.2.2     | IC_EN                                      | 27 |

|          |        | 7.2.3     | nIRQ                                       | 27 |

|          |        | 7.2.4     | GPIO Extender                              | 28 |

|          | 7.3    | Operati   | ing Modes                                  | 30 |

|          |        | 7.3.1     | ON Mode                                    | 30 |

|          |        | 7.3.2     | OFF Mode                                   | 30 |

|          | 7.4    | Control   | Interfaces                                 | 30 |

|          |        | 7.4.1     | 4-WIRE Communication                       | 30 |

|          |        | 7.4.2     | 2-WIRE Communication                       | 35 |

|          |        | 7.4.3     | Details of the 2-WIRE Control Bus Protocol | 36 |

|          | 7.5    | Internal  | I Temperature Supervision                  | 39 |

| 8        | Regi   | ster Defi | initions                                   | 40 |

|          | 8.1    | Registe   | er Map                                     | 40 |

|          |        | 8.1.1     | Register Page Control                      | 42 |

|          |        | 8.1.2     | Register Page 0                            | 42 |

|          |        |           | 8.1.2.1 System Control and Event           | 42 |

|          |        |           |                                            |    |

|     |             | 8.1.2.2         | GPIO Control                                            | 44       |

|-----|-------------|-----------------|---------------------------------------------------------|----------|

|     |             | 8.1.2.3         | Regulators Control                                      | 46       |

|     | 8.1.3       | Register Pa     | age 1                                                   |          |

|     |             | 8.1.3.1         | Regulators Settings                                     |          |

|     | 8.1.4       |                 | age 2                                                   |          |

|     | 0.1.4       | 8.1.4.1         | Interface and OTP Settings (shared with DA9063)         |          |

|     |             | _               | ,                                                       |          |

|     |             | 8.1.4.2         | OTP Fusing Registers                                    |          |

|     |             | 8.1.4.3         | Application Configuration Settings                      |          |

| 9   | Application | າ Information   |                                                         | 58       |

|     | 9.1 Capa    | citor Selection |                                                         | 58       |

|     | 9.2 Induc   | ctor Selection  |                                                         | 59       |

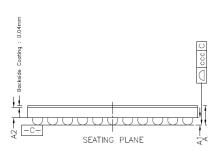

| 10  | Package In  | formation       |                                                         | 60       |

|     | _           |                 |                                                         |          |

|     |             | •               |                                                         |          |

| 11  | Ordering I  | nformation      |                                                         | 61       |

|     |             |                 |                                                         |          |

|     |             |                 |                                                         |          |

| Fi  | gures       |                 |                                                         |          |

|     |             | 10 510011       | I DAGGE C D'                                            | _        |

|     |             |                 | d DA9215 System Diagramram                              |          |

|     |             |                 | ram                                                     |          |

|     |             |                 |                                                         |          |

|     |             |                 |                                                         |          |

|     |             |                 |                                                         |          |

|     |             |                 | 0 to 10 A                                               |          |

|     |             |                 | 0 to 10 A<br>0 to 20 A (Linear)                         |          |

|     |             |                 | , 0 to 20 A (Linear)                                    |          |

|     |             |                 | , 0 to 20 A                                             |          |

|     |             |                 | Modes                                                   |          |

|     |             |                 | /14/15 with DA9063 and the Host Processor               |          |

|     |             |                 | of DA9213                                               |          |

|     |             |                 | of DA9214                                               |          |

|     |             |                 | of the Buck's Output Voltage m VOUT to FBAN             |          |

|     |             |                 | peration (example paths)                                |          |

|     |             |                 | E and 2-WIRE Power Manager Bus                          |          |

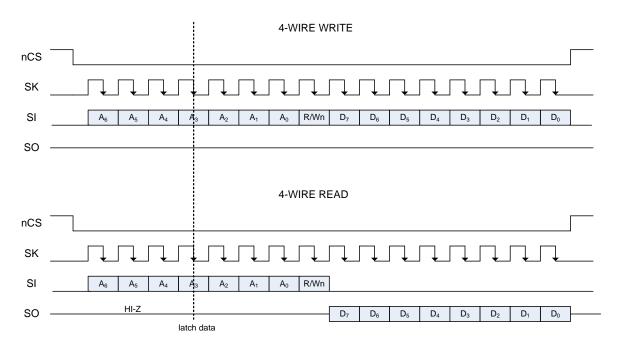

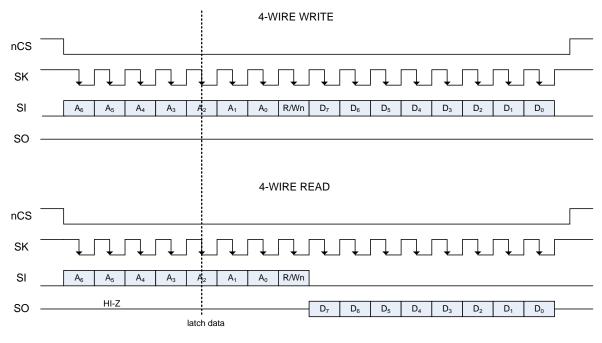

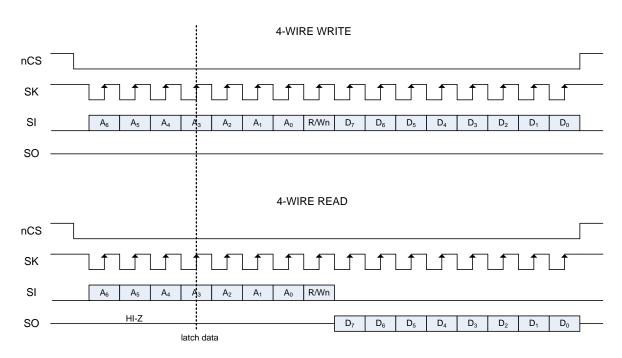

| Fig | ure 20: 4-W | RE Host Write a | and Read Timing (nCS_POL = '0', CPOL = '0', CPHA = '0') | 32       |

| Fig | ure 21: 4-W | RE Host Write a | and Read Timing (nCS_POL= '0', CPOL = '0', CPHA = '1')  | 33       |

|     |             |                 | and Read Timing (nCS_POL = '0', CPOL = '1', CPHA = '0') |          |

|     |             |                 | and Read Timing (nCS_POL = '0', CPOL = '1', CPHA = '1') |          |

|     |             |                 | TART and STOP Condition                                 |          |

| rig | ure 25: 2-W | RE Byte Write ( | SDA Line)<br>E Byte Read (SDA Line)                     | ر3<br>حو |

|     |             |                 | E Byte Read (SDA Line)                                  |          |

|     |             |                 | (SDA Line)                                              |          |

|     |             |                 | /rite (SDA Line)                                        |          |

|     |             |                 | SSP Package Outline Drawing                             |          |

**Datasheet**

# DA9213, DA9214, and DA9215

# Multi-Phase 5A/Phase DC-DC Buck Converter

## **Tables**

| Table 1: Pin Description                           | 9  |

|----------------------------------------------------|----|

| Table 2: Pin Type Definition                       | 10 |

| Table 3: Absolute Maximum Ratings                  | 11 |

| Table 4: Recommended Operating Conditions (Note 1) | 11 |

| Table 5: Buck Converters Characteristics           |    |

| Table 6: IC Performance and Supervision            | 15 |

| Table 7: Digital I/O Characteristics               |    |

| Table 8: 2-WIRE Control Bus Characteristics        |    |

| Table 9: 4-WIRE Control Bus Characteristics        | 18 |

| Table 10: 4-WIRE Clock Configurations              |    |

| Table 11: 4-WIRE Interface Summary                 |    |

| Table 12: Over-Temperature Thresholds              | 39 |

| Table 13: Register Map                             | 41 |

| Table 14: Recommended Capacitor Types              | 58 |

| Table 15: Recommended Inductor Types               | 59 |

| Table 16: Ordering Information                     | 61 |

## 1 Terms and Definitions

AP Application Processor

CPU Central Processing Unit

DDR Double Data Rate (type of SDRAM memory for PCs)

DVC Dynamic Voltage Control GPU Graphic Processing Unit

IC Integrated Circuit

OTP One Time Programmable memory

PCB Printed Circuit Board

PMIC Power Management Integrated Circuit

POL Point Of Load

SDRAM Synchronous Dynamic Random Access Memory

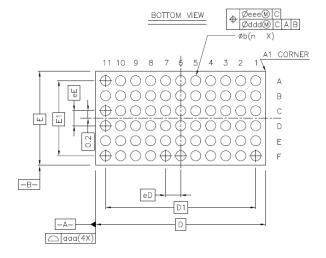

## 2 Pinout

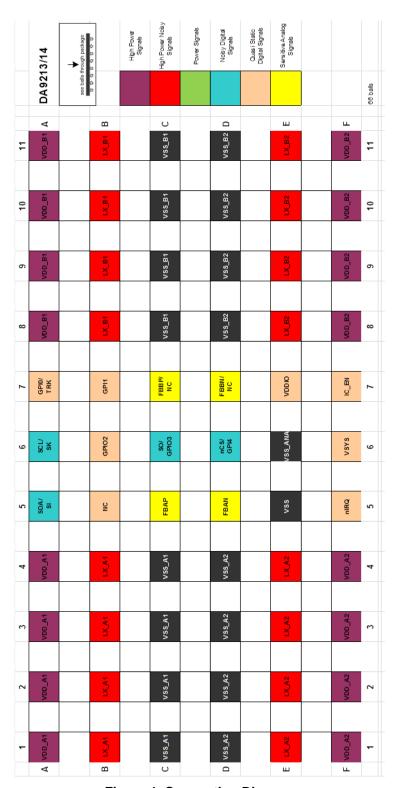

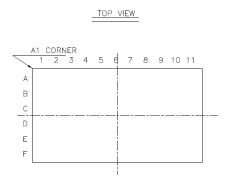

Figure 4: Connection Diagram

**Table 1: Pin Description**

| Pin Name         | Signal<br>Name | Second<br>Function | Type (Table 2) | Description                                                                             |

|------------------|----------------|--------------------|----------------|-----------------------------------------------------------------------------------------|

| B1, B2, B3, B4   | LX_A1          |                    | AO             | Switching node for Buck A phase 1                                                       |

| E1, E2, E3, E4   | LX_A2          |                    | AO             | Switching node for Buck A phase 2                                                       |

| B8, B9, B10, B11 | LX_B1          |                    | AO             | Switching node for Buck B phase 1                                                       |

| E8, E9, E10, E11 | LX_B2          |                    | AO             | Switching node for Buck B phase 2                                                       |

| A1, A2, A3, A4   | VDD_A1         |                    | PS             | Supply voltage for Buck A phase 1 To be connected to VSYS                               |

| F1, F2, F3, F4   | VDD_A2         |                    | PS             | Supply voltage for Buck A phase 2 To be connected to VSYS                               |

| A8, A9, A10, A11 | VDD_B1         |                    | PS             | Supply voltage for Buck B phase 1 To be connected to VSYS                               |

| F8, F9, F10, F11 | VDD_B2         |                    | PS             | Supply voltage for Buck B phase 2 To be connected to VSYS                               |

| F7               | IC_EN          |                    | DI             | Integrated Circuit (IC) Enable Signal                                                   |

| F5               | nIRQ           |                    | DO             | Interrupt line towards the host                                                         |

| E7               | VDDIO          |                    | PS             | I/O Voltage Rail                                                                        |

| C5               | FBAP           |                    | Al             | Positive sense node for the Buck A                                                      |

| D5               | FBAN           |                    | Al             | Negative sense node for the Buck A                                                      |

| C7               | FBBP           |                    | AI             | Positive sense node for the Buck B for DA9214 and DA9215                                |

|                  | NC             |                    | AO             | Do not connect for DA9213                                                               |

| D7               | FBBN           |                    | Al             | Negative sense node for the Buck B for DA9214 and DA9215                                |

|                  | NC             |                    | AO             | Do not connect for DA9213                                                               |

| A7               | GPI0           | TRK                | DI/AI          | General purpose input, input track                                                      |

| B7               | GPI1           |                    | DI             | General purpose input                                                                   |

| B6               | GPIO2          |                    | DIO            | General purpose input/output                                                            |

| A5               | SDA            | SI                 | DIO            | 2-WIRE data, 4-WIRE data input/output                                                   |

| A6               | SCL            | SK                 | DI             | 2-WIRE clock, 4-WIRE clock                                                              |

| D6               | nCS            | GPI4               | DI             | 4-WIRE chip select, general purpose input                                               |

| C6               | SO             | GPIO3              | DIO            | 4-WIRE data output, general purpose input/output                                        |

| B5               | NC             |                    | АО             | Do not connect and leave floating. This pin is used for the supply of internal circuits |

| F6               | VSYS           |                    | PS             | Supply for IC and input for voltage supervision                                         |

| E5               | VSS            |                    | VSS            |                                                                                         |

| E6               | VSS_ANA        |                    | VSS            |                                                                                         |

# **DA9213, DA9214, and DA9215**

## Multi-Phase 5A/Phase DC-DC Buck Converter

| Pin Name                                                                       | Signal<br>Name                        | Second<br>Function | Type<br>(Table 2) | Description      |

|--------------------------------------------------------------------------------|---------------------------------------|--------------------|-------------------|------------------|

| C1, C2, C3, C4,<br>D1, D2, D3, D4,<br>C8, C9, C10,<br>C11,<br>D8, D9, D10, D11 | VSS_A1,<br>VSS_A2<br>VSS_B1<br>VSS_B2 |                    | VSS               | Connect together |

# **Table 2: Pin Type Definition**

| Pin Type | Description          | Pin Type | Description           |

|----------|----------------------|----------|-----------------------|

| DI       | Digital Input        | Al       | Analogue Input        |

| DO       | Digital Output       | AO       | Analogue Output       |

| DIO      | Digital Input/Output | AIO      | Analogue Input/Output |

| PS       | Power Supply         | VSS      | Ground                |

# 3 Absolute Maximum Ratings

**Table 3: Absolute Maximum Ratings**

| Symbol               | Parameter                                 | Conditions (Note 1)                                       | Min  | Тур  | Max                      | Unit |

|----------------------|-------------------------------------------|-----------------------------------------------------------|------|------|--------------------------|------|

| T <sub>STG</sub>     | Storage temperature                       |                                                           | -65  |      | +150                     | °C   |

| T <sub>A_LIM</sub>   | Limiting ambient temperature              |                                                           | -40  |      | +85                      | °C   |

| $V_{DD\_LIM}$        | Limiting supply voltage                   |                                                           | -0.3 |      | 5.5                      | V    |

| V <sub>PIN</sub>     | Limiting voltage at all pins except above |                                                           | -0.3 |      | $V_{DD} + 0.3$ (max 5.5) | V    |

| P <sub>TOT</sub>     | Total power dissipation<br>Note 2         | Derating factor above<br>T <sub>A</sub> = 70 °C: 37 mW/°C | 2035 | 2590 |                          | mW   |

| V <sub>ESD_HBM</sub> | Electrostatic discharge voltage           | Human Body Model                                          |      |      | 2                        | kV   |

Note 1 Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, so functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 2** Obtained from simulation on a 2S2P 4L JEDEC Board (EIA/JESD51-2). Influenced by PCB technology and layout.

# 4 Recommended Operating Conditions

Table 4: Recommended Operating Conditions (Note 1)

| Parameter  | Description                 | Conditions | Min | Тур | Max           | Unit |

|------------|-----------------------------|------------|-----|-----|---------------|------|

| $V_{DD}$   | Supply voltage              |            | 2.8 |     | 5.5           | V    |

| $V_{DDIO}$ | Input/output supply voltage |            | 1.2 |     | 3.6<br>Note 2 |      |

**Note 1** Within the specified limits, a lifetime of 10 years is guaranteed.

Note 2 V<sub>DDIO</sub> is not allowed to be higher than V<sub>DD.</sub>

## 5 Electrical Characteristics

Unless otherwise noted, the following is valid for  $T_A$  = -40 to +85 °C,  $V_{DD}$  = 2.8 V to 5.5 V,  $C_{OUT}$  = 47  $\mu F$  per phase, local sensing.

**Table 5: Buck Converters Characteristics**

| Parameter             | Description                              | Conditions                                                                                                 | Min          | Тур  | Max          | Unit |

|-----------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------|------|--------------|------|

| External Co           | emponent Electrical Condition            | ons                                                                                                        |              |      |              |      |

| Соит                  | Output capacitance (per phase)           | Including voltage and temperature coefficient                                                              | 23           | 47   | 62           | μF   |

| ESR <sub>COUT</sub>   | Equivalent series resistance (per phase) | f > 100 kHz                                                                                                |              |      | 10           | mΩ   |

| L <sub>PHASE</sub>    | Inductance (per phase)                   | Including current and temperature dependence                                                               | 0.11         | 0.22 | 0.29         | μΗ   |

| DCR <sub>LPHASE</sub> | Inductor resistance                      |                                                                                                            |              |      | 100          | mΩ   |

| Electrical C          | haracteristics                           |                                                                                                            |              |      |              |      |

| $V_{DD}$              | Supply voltage                           | VDD_x = VSYS                                                                                               | 2.8          |      | 5.5          | V    |

| V <sub>BUCK</sub>     | Buck output voltage<br>Note 1            | I <sub>O</sub> = 0 to I <sub>O_MAX</sub>                                                                   | 0.3          |      | 1.57         | V    |

|                       | Output voltage accuracy<br>PWM mode      | Incl. static line/load reg<br>and voltage ripple<br>V <sub>BUCK</sub> ≥ 1 V                                | -2.0         |      | +2.0         | %    |

|                       |                                          | Incl. static line/load reg<br>and voltage ripple<br>V <sub>BUCK</sub> < 1 V                                |              | ±20  |              | mV   |

| Voacc                 |                                          | $V_{BUCK} = 1 V$ $V_{DD} = 3.8 V$ no load                                                                  | -1.0         |      | +1.0         | %    |

|                       |                                          | $V_{BUCK} = 1 \text{ V}$ $V_{DD} = 3.8 \text{ V}$ no load $T_{A} = 27 ^{\circ}\text{C}$                    | -0.5         |      | +0.5         | %    |

|                       |                                          | DA9213<br>$I_O = 0$ to 5 A, $t_R = 500$ ns<br>PWM 4-phase<br>$V_{BUCK} \ge 1$ V<br>$V_{BUCK} < 1$ V        | -2<br>-20 mV |      | +2<br>+20 mV | %    |

| $V_{TR\_LOAD}$        | Load regulation transient voltage Note 2 | DA9213 $I_{O} = 0 \text{ to 5 A, } t_{R} = 500 \text{ ns}$ auto mode, ph shedding $V_{BUCK} = 1 \text{ V}$ | -3.5         |      | +3.5         | %    |

|                       |                                          | DA9214<br>$I_0 = 0$ to 5 A, $t_R = 500$ ns<br>PWM 2-phase<br>$V_{BUCK} = 1$ V                              |              | ±3.5 |              | %    |

| Parameter             | Description                                         | Conditions                                                                             | Min  | Тур          | Max  | Unit |

|-----------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------|------|--------------|------|------|

|                       |                                                     | DA9215 Buck A $I_0$ = 0 to 5 A, $t_R$ = 500 ns PWM 3-phase VBUCK = 1 V                 |      | ±2.5         |      | %    |

|                       |                                                     | DA9215 Buck B $I_O=0$ to 2.5 A, $t_R=200$ ns PWM, 2 x 47 $\mu$ F $V_{BUCK}=1$ V        |      | ±2.5         |      | %    |

| V <sub>TR_LINE</sub>  | Line regulation transient voltage                   | $V_{DD} = 3.0 \text{ to } 3.6 \text{ V}$ $dt = 10  \mu\text{s}$ $I_{O} = I_{O(MAX)}/2$ |      | 15           |      | mV   |

| I <sub>O_MAX</sub>    | Maximum output current                              | Per phase                                                                              | 5000 |              |      | mA   |

| I <sub>LIM_MIN</sub>  | Minimum current limit per phase (programmable)      | BUCKA_ILIM = 0000<br>BUCKB_ILIM = 0000<br>Note 3                                       | -20% | 4000         | 20%  | mA   |

| I <sub>LIM_MAX</sub>  | Maximum current limit per phase (programmable)      | BUCKA_ILIM = 1111<br>BUCKB_ILIM = 1111<br>Note 3                                       | -20% | 7000         | 20%  | mA   |

| I <sub>Q_PWM</sub>    | Quiescent current at synchronous rectification mode | Per phase<br>No load<br>V <sub>DD</sub> = 3.7 V                                        |      | 17           |      | mA   |

| f <sub>SW</sub>       | Switching frequency                                 |                                                                                        |      | 3            |      | MHz  |

| tstup                 | Start-up time                                       | BUCKA_UP_CTRL = 011<br>BUCKB_UP_CTRL = 011                                             |      | 50<br>Note 4 |      | μs   |

| R <sub>O_PD</sub>     | Output pull-down resistance                         | For each phase at the LX node at 0.5 V, (see BUCKx_PD_DIS)                             |      | 150          | 200  | Ω    |

| R <sub>ON_PMOS</sub>  | PMOS on-resistance                                  | incl. pin and routing $V_{DD} = 3.7 \text{ V}$ per phase                               |      | 26           |      | mΩ   |

| R <sub>ON_NMOS</sub>  | NMOS on-resistance                                  | incl. pin and routing $V_{DD} = 3.7 \text{ V}$ per phase                               |      | 18           |      | mΩ   |

| PFM Mode              |                                                     |                                                                                        |      |              |      |      |

| V <sub>BUCK_PFM</sub> | Buck output voltage in PFM                          | $I_O = 0$ mA to $I_{O\_MAX}$                                                           | 0.3  |              | 1.57 | V    |

| I <sub>Q_PFM_A2</sub> | DA9214 quiescent current<br>Buck A enabled          | No switching V <sub>DD</sub> = 3.7 V Note 5                                            |      | 58           |      | μA   |

# DA9213, DA9214, and DA9215

### Multi-Phase 5A/Phase DC-DC Buck Converter

| Parameter   | Description                                            | Conditions                                      | Min | Тур | Max | Unit |

|-------------|--------------------------------------------------------|-------------------------------------------------|-----|-----|-----|------|

| IQ_PFM_A4   | DA9213 quiescent current<br>Buck enabled               | No switching $V_{DD} = 3.7 \text{ V}$<br>Note 5 |     | 72  |     | μA   |

| IQ_PFM_A2B2 | DA9214 quiescent current Buck A enabled Buck B enabled | No switching $V_{DD} = 3.7 \text{ V}$ Note 5    |     | 106 |     | μA   |

| IQ_PFM_A3B1 | DA9215 quiescent current Buck A enabled Buck B enabled | No switching $V_{DD} = 3.7 \text{ V}$ Note 5    |     | 130 |     | μA   |

- Note 1 Programmable in 10 mV increments.

- **Note 2** Additional to the dc accuracy. The value is intended to be measured directly at C<sub>OUT(EXT)</sub>. In case of remote sensing, parasitics of PCB and external components may affect this value.

- Note 3 On-time > 50 ns.

- Note 4 Time from beginning to end of the voltage ramp. Additional 10 μs typical delay, plus internal sync to the enable port.

- **Note 5** For the total quiescent current of the IC, the I<sub>DD\_ON</sub> should be added.

**Table 6: IC Performance and Supervision**

| Parameter               | Description                                           | Conditions                                    | Min  | Тур  | Max  | Unit |

|-------------------------|-------------------------------------------------------|-----------------------------------------------|------|------|------|------|

| I <sub>DD_OFF</sub>     | Off state supply current                              | IC_EN = 0<br>T <sub>A</sub> = 27 °C           |      | 0.1  | 1    | μΑ   |

| I <sub>DD_ON</sub>      | On state supply current                               | IC_EN = 1 Buck A/B off T <sub>A</sub> = 27 °C |      | 14   |      | μА   |

| V <sub>TH_PG</sub>      | Power good threshold voltage                          | referred to V <sub>BUCK</sub>                 |      | -50  |      | mV   |

| V <sub>HYS_PG</sub>     | Power good hysteresis voltage                         |                                               |      | 50   |      | mV   |

| V <sub>TH_UVLO_V</sub>  | Under voltage lockout threshold at V <sub>DD</sub>    |                                               |      | 2.0  |      | V    |

| V <sub>TH_UVLO_IO</sub> | Under voltage lockout threshold at V <sub>DDIO</sub>  |                                               | 1.35 | 1.45 | 1.55 | V    |

| V <sub>HYS_UVLO_I</sub> | Under voltage lockout hysteresis at V <sub>DDIO</sub> |                                               |      | 70   |      | mV   |

| T <sub>TH_WARN</sub>    | Thermal warning threshold temperature                 |                                               | 110  | 125  | 140  | °C   |

| T <sub>TH_CRIT</sub>    | Thermal critical threshold temperature                |                                               | 125  | 140  | 155  | °C   |

| T <sub>TH_POR</sub>     | Thermal power on reset threshold temperature          |                                               | 135  | 150  | 165  | °C   |

| fosc                    | Internal oscillator frequency                         |                                               | -7%  | 6.0  | +7%  | MHz  |

# Table 7: Digital I/O Characteristics

$T_A = -40 \text{ to } +85 \text{ }^{\circ}\text{C}$

| Parameter             | Description                                                    | Conditions                                          | Min                             | Тур | Max                             | Unit     |

|-----------------------|----------------------------------------------------------------|-----------------------------------------------------|---------------------------------|-----|---------------------------------|----------|

| V <sub>IH_EN</sub>    | HIGH level input voltage                                       | At pin IC_EN                                        | 1.1                             |     |                                 | V        |

| V <sub>IL_EN</sub>    | LOW level input voltage                                        | At pin IC_EN                                        |                                 |     | 0.35                            | ٧        |

| t <sub>EN</sub>       | Enable time                                                    | I/F operating                                       |                                 | 750 |                                 | μs       |

| R <sub>O_PU_GPO</sub> | Pull up resistor at GPO                                        | $V_{DDIO} = 1.8 \text{ V}$ $V_{GPO} = 0 \text{ V}$  |                                 | 100 |                                 | kΩ       |

| R <sub>I_PD_GPI</sub> | Pull down resistor at GPI                                      | $V_{DDIO} = 1.8 \text{ V}$ $V_{GPO} = 0 \text{ V}$  |                                 | 150 |                                 | kΩ       |

| V <sub>IH</sub>       | GPI0-4, SCL, SDA,<br>(2-WIRE mode)<br>HIGH level input voltage | V <sub>LDOCORE</sub> mode<br>V <sub>DDIO</sub> mode | 1.75<br>0.7 * V <sub>DDIO</sub> |     |                                 | <b>V</b> |

| VıL                   | GPI0-4, SCL, SDA,<br>(2-WIRE mode)<br>LOW level input voltage  | V <sub>LDOCORE</sub> mode<br>V <sub>DDIO</sub> mode |                                 |     | 0.75<br>0.3 * V <sub>DDIO</sub> | V        |

| Parameter              | Description                                                                                   | Conditions                                                                     | Min                              | Тур | Max                   | Unit |

|------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|----------------------------------|-----|-----------------------|------|

| V <sub>IH_4</sub> wire | SK, nCS, SI<br>(4-WIRE Mode)<br>HIGH level input voltage                                      |                                                                                | 0.7* V <sub>DDIO</sub>           |     |                       | V    |

| V <sub>IL_4</sub> WIRE | SK, nCS, SI<br>(4-WIRE Mode)<br>LOW level input voltage                                       |                                                                                |                                  |     | 0.3*V <sub>DDIO</sub> | V    |

| V <sub>OH</sub>        | GPO2-3, SO (4-WIRE mode) HIGH level output voltage                                            | push-pull mode<br>at 1 mA<br>V <sub>DDIO</sub> ≥ 1.5 V                         | 0.8*V <sub>DDIO</sub>            |     |                       | V    |

| V <sub>OL1</sub>       | GPO2-3, SDA (2-WIRE mode) SO (4-WIRE mode) LOW level output voltage at I <sub>OL</sub> = 1 mA |                                                                                |                                  |     | 0.3                   | V    |

| V <sub>OL3</sub>       | SDA (2-WIRE Mode) LOW level output voltage at I <sub>OL</sub> = 3 mA                          |                                                                                |                                  |     | 0.24                  | V    |

| V <sub>OL20</sub>      | SDA (2-WIRE Mode) LOW level output voltage at I <sub>OL</sub> = 20 mA                         |                                                                                |                                  |     | 0.4                   | V    |

| C <sub>IN</sub>        | CLK, SDA<br>(2-WIRE Mode)<br>input capacitance                                                |                                                                                |                                  | 2.5 | 10                    | pF   |

| t <sub>SP</sub>        | CLK, SDA (2-WIRE Mode) spike suppression pulse width                                          | Fast/Fast+ mode<br>High Speed mode                                             | 0                                |     | 50<br>10              | ns   |

| t <sub>fDA</sub>       | Fall time of SDA signal (2-WIRE Mode)                                                         | Fast at $C_B < 550$ pF<br>HS at $10 < C_B < 100$<br>pF<br>HS at $C_B < 400$ pF | 20+0.1C <sub>B</sub><br>10<br>20 |     | 120<br>80<br>160      | ns   |

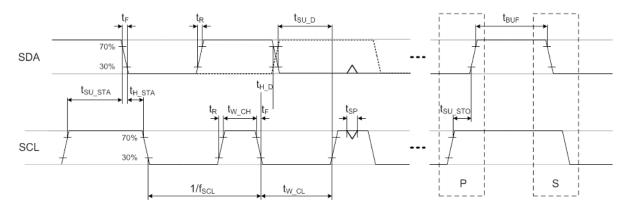

### **Table 8: 2-WIRE Control Bus Characteristics**

$T_A = -40 \text{ to } +85 \, {}^{\circ}\text{C}$

| Parameter           | Description                                | Conditions | Min         | Тур | Max  | Unit |  |

|---------------------|--------------------------------------------|------------|-------------|-----|------|------|--|

| t <sub>BUF</sub>    | Bus free time from STOP to START condition |            | 0.5         |     |      | μs   |  |

| Св                  | Bus line capacitive load                   |            |             |     | 150  | pF   |  |

| Standard/Fa         | Standard/Fast/Fast+ Mode                   |            |             |     |      |      |  |

| f <sub>SCL</sub>    | Clock frequency                            | At pin SCL | 0<br>Note 1 |     | 1000 | kHz  |  |

| t <sub>SU_STA</sub> | START condition set-up time                |            | 0.26        |     |      | μs   |  |

| t <sub>H_STA</sub>  | START condition hold time                  |            | 0.26        |     |      | μs   |  |

Datasheet Revision 2.2 23-Oct-2017

| Parameter             | Description                 | Conditions                             | Min         | Тур | Max  | Unit |

|-----------------------|-----------------------------|----------------------------------------|-------------|-----|------|------|

| t <sub>W_CL</sub>     | Clock LOW duration          |                                        | 0.5         |     |      | μs   |

| t <sub>W_CH</sub>     | Clock HIGH duration         |                                        | 0.26        |     |      | μs   |

| t <sub>R</sub>        | Rise time                   | Input requirement. At pin CLK and DATA |             |     | 1000 | ns   |

| t <sub>F</sub>        | Fall time                   | Input requirement. At pin CLK and DATA |             |     | 300  | ns   |

| t <sub>SU_D</sub>     | Data set-up time            |                                        | 50          |     |      | ns   |

| t <sub>H_D</sub>      | Data hold time              |                                        | 0           |     |      | ns   |

| High Speed            | Mode                        |                                        |             |     |      |      |

| f <sub>SCL_HS</sub>   | Clock frequency             | At pin SCL                             | 0<br>Note 1 |     | 3400 | kHz  |

| tsu_sta_hs            | START condition set-up time |                                        | 160         |     |      | ns   |

| t <sub>H_STA_HS</sub> | START condition hold time   |                                        | 160         |     |      | ns   |

| t <sub>W_CL_HS</sub>  | Clock LOW duration          |                                        | 160         |     |      | ns   |

| t <sub>W_CH_HS</sub>  | Clock HIGH duration         |                                        | 60          |     |      | ns   |

| t <sub>R_HS</sub>     | Rise time                   | Input requirement. At pin CLK and DATA |             |     | 160  | ns   |

| t <sub>F_HS</sub>     | Fall time                   | Input requirement. At pin CLK and DATA |             |     | 160  | ns   |

| t <sub>SU_D_HS</sub>  | Data set-up time            |                                        | 10          |     |      | ns   |

| t <sub>H_D_HS</sub>   | Data hold time              |                                        | 0           |     |      | ns   |

| tsu_sto_нs            | STOP condition set-up time  |                                        | 160         |     |      | ns   |

Note 1 Minimum clock frequency is 10 kHz if 2WIRE\_TO is enabled

Figure 5: 2-WIRE Bus Timing

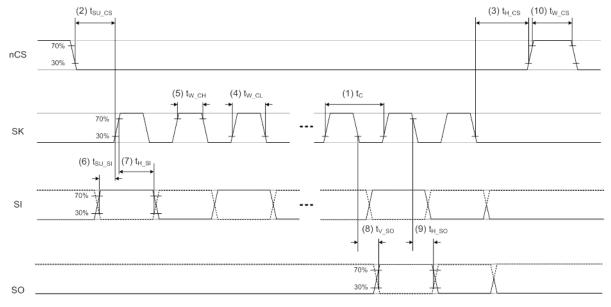

#### **Table 9: 4-WIRE Control Bus Characteristics**

$T_A = -40 \text{ to } +85 \, {}^{\circ}\text{C}$

| Parameter          | Description               | Conditions                         | Min                  | Тур | Max | Unit |

|--------------------|---------------------------|------------------------------------|----------------------|-----|-----|------|

| Св                 | Bus line capacitive load  |                                    |                      |     | 100 | pF   |

| t <sub>C</sub>     | Cycle time                | 1                                  | 70                   |     |     | ns   |

| t <sub>SU_CS</sub> | Chip select setup time    | 2, from CS active to first SK edge | 20                   |     |     | ns   |

| t <sub>H_CS</sub>  | Chip select hold time     | 3, from last SK edge to CS idle    | 20                   |     |     | ns   |

| t <sub>W_CL</sub>  | Clock LOW duration        | 4                                  | 0.4 x t <sub>C</sub> |     |     | ns   |

| t <sub>W_CH</sub>  | Clock HIGH duration       | 5                                  | 0.4 x t <sub>C</sub> |     |     | ns   |

| t <sub>SU_SI</sub> | Data input setup time     | 6                                  | 10                   |     |     | ns   |

| t <sub>H_SI</sub>  | Data input hold time      | 7                                  | 10                   |     |     | ns   |

| t <sub>V_SO</sub>  | Data output valid time    | 8                                  |                      |     | 22  | ns   |

| t <sub>H_SO</sub>  | Data output hold time     | 9                                  | 6                    |     |     | ns   |

| t <sub>W_CS</sub>  | Chip select HIGH duration | 10                                 | 20                   |     |     | ns   |

Figure 6: 4-WIRE Bus Timing

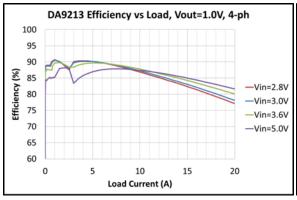

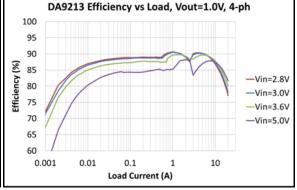

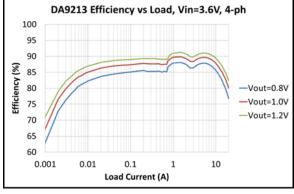

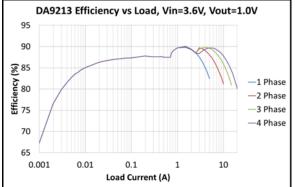

# **6 Efficiency Measurements**

Note: Phase shedding is enabled in each plot.

Figure 7: 2 Phase Auto-Mode, 0 to 10 A

Figure 8: 2 Phase Auto-Mode, 0 to 10 A

Figure 9: 4 Phase Auto-Mode, 0 to 20 A (Linear)

Figure 10: 4 Phase Auto-Mode, 0 to 20 A (Logarithmic)

Figure 11: 4 Phase Auto-Mode, 0 to 20 A

Figure 12: 1, 2, 3, and 4 Phase Modes

Datasheet Revision 2.2 23-Oct-2017

## **7 Functional Description**

Flexible configurability and the availability of different control schemes make both DA9213, DA9214, and DA9215 the ideal single/dual buck companion ICs to expand the existing capabilities of a master PMIC.

Due to the advanced compatibility between both DA9213, DA9214, and DA9215 and the DA9063, they offer several advantages when they are operated together. These advantages include:

- DA9213, DA9214, and DA9215 can be enabled and controlled by DA9063 during the power up sequence, thanks to DA9063's dedicated output signals during power up, and compatible input controls in both DA9213, DA9214, and DA9215.

- DA9213, DA9214, and DA9215 can be used in a completely transparent way for the host processor and can share the same Control Interface (same SPI chip select or I<sup>2</sup>C address), thanks to the compatible registers map. DA9213, DA9214, and DA9215 have a dedicated register space for configuration and control which doesn't conflict with DA9063.

- DA9213, DA9214, and DA9215 support a power good configurable port for enhanced communication to the host processor and improved power up sequencing.

- DA9213, DA9214, and DA9215 can both share the same interrupt line with DA9063.

In addition, the 2-WIRE / 4-WIRE interfaces allow DA9213, DA9214, and DA9215 to fit many standard PMU parts and power applications.

Figure 13: Interface of DA9213/14/15 with DA9063 and the Host Processor

As shown in Figure 13, a typical application case includes a host processor, a Main PMIC (for example, DA9063) and DA9213 or DA9214 used as companion IC for the high power core supply.

The easiest way of controlling DA9213, DA9214, and DA9215 is through the Control Interface. The master initiating the communication must always be the host processor that reads and writes to the

main PMIC, and to the DA9213, DA9214, and DA9215 registers. To poll the status of DA9213 or DA9214, the host processor must access the dedicated register area through the Control Interface. DA9213, DA9214, and DA9215 can be additionally controlled by means of hardware inputs.

Figure 14: Typical Application of DA9213

Figure 14 shows a typical use case of DA9213 for the supply of CPU, GPU, or DDR rails. The IC is enabled and disabled by the main PMIC via IC\_EN port as part of its sequencer. Once the IC is enabled, the CORE application processor enables the buck converter with the EN1 signal and manages the output voltage selection with the VSEL signal.

The VSEL signal can be shared between the main PMIC and the DA9213. Three GPI/GPIOs embedded in DA9213 are used in this case:

- GPIO2 signals the insertion of an external charger in the application (through interrupt to the host processor)

- GPIO3 indicates a power good condition, either to proceed with the power up sequence or to enable an external supply connected to the port

- GPI4 is used for the I<sup>2</sup>C interface address hardware selection

Figure 15: Typical Application of DA9214

Figure 15 shows a typical use case of DA9214 for the simultaneous supply of a CPU and a GPU rail. The IC is always enabled because IC\_EN is shorted to the battery voltage. The CORE application processor enables and disables the CPU/GPU and the DDR individually via dedicated ports on DA9214.

### 7.1 DC DC Buck Converter

DA9213 is a four phase 20 A high efficiency synchronous step down DVC regulator, operating at a high frequency of typically 3 MHz. It supplies an output voltage of typically 1.0 V for a CPU rail, configurable in the range 0.3 to 1.57 V, with high accuracy in steps of 10 mV.

DA9214 contains two buck converters, Buck A and Buck B, each capable of delivering 10 A.

DA9215 contains also two buck converters, Buck A capable of 15 A and Buck B capable of 5 A.

To improve the accuracy of the delivered voltage, each buck converter is able to support a differential sensing of the configured voltage directly at the point of load via dedicated positive and negative sense pins.

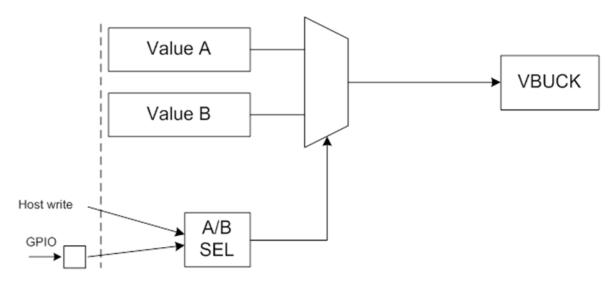

Both Buck A and Buck B have two voltage registers each. One defines the normal output voltage, while the other offers an alternative retention voltage. In this way different application power modes can easily be supported. The voltage selection can be operated either via GPI or via control interface to guarantee the maximum flexibility according to the specific host processor status in the application.

When a buck is enabled, its output voltage is monitored and a power good signal indicates that the buck output voltage has reached a level higher than the  $V_{TH(PG)}$  threshold. The power good is lost when the voltage drops below  $V_{TH(PG)}$  -  $V_{HYS(PG)}$ , which is the level at which the signal is de-asserted. The power good signaling should not be used in conjunction with fast start up rates, configured in BUCKx\_UP\_CTRL register fields and can be individually masked during DVC transitions using the PGA\_DVC\_MASK and PGB\_DVC\_MASK bits. For each of the buck converters the status of the power good indicator can be read back via  $I^2$ C from the PWRGOOD\_A and PWRGOOD\_B status bits. It can be also individually assigned to either GPIO2 or GPIO3 using BUCKA\_PG\_SEL and BUCKB\_PG\_SEL. For correct functionality, the GPIO ports need to be configured as output. An  $I^2$ C write in GPIOx\_MODE can overwrite the internal configuration so that a new update will be automatically done only when the internal power good indicator changes status.

The buck converters are capable of supporting DVC transitions that occur:

- When the active and selected A-voltage or B-voltage is updated to a new target value.

- When the voltage selection is changed from the A-voltage to the B-voltage (or B-voltage to the A voltage) using VBUCKA SEL and VBUCKB SEL.

The DVC controller operates in Pulse Width Modulation (PWM) mode with synchronous rectification. When the host processor changes the output voltage, the voltage transition of each buck converter can be individually signaled with a READY signal routed to either GPIO2 or GPIO3. The port has to be configured as GPO and selected for the functionality via READYA\_CONF or READYB\_CONF. In contrast to the power good signal, the READY only informs the host processor about the completion of the digital DVC ramp without confirming that the target voltage has actually been reached.

The slew rate of the DVC transition is individually programmed for each buck converter at 10 mV per (4, 2, 1, or 0.5 µs) via control bit SLEW\_RATE\_A and SLEW\_RATE\_B.

The typical supply current is in the order of 8 mA per phase (quiescent current and charge/discharge current) and drops to  $<1~\mu$ A when the buck is turned off.

When the buck is disabled, a pull down resistor (typically 150  $\Omega$ ) for each phase is activated depending of the value stored in register bits BUCKA\_PD\_DIS and BUCKB\_PD\_DIS. Phases disabled using PHASE\_SEL\_A and PHASE\_SEL\_B will not have any pull down. The pull down resistor is always disabled at all phases when DA9213, DA9214, and DA9215 are OFF.

### 7.1.1 Switching Frequency

The switching frequency is chosen to be high enough to allow the use of a small 0.22  $\mu$ H inductor (see a complete list of coils in the Application Information, Section 9). The buck switching frequency can be tuned using register bit OSC\_TUNE. The internal 6 MHz oscillator frequency is tuned in steps of 180 kHz. This impacts the buck converter frequency in steps of 90 kHz and helps to mitigate possible disturbances to other HF systems in the application.

### 7.1.2 Operation Modes and Phase Selection

The buck converters can operate in synchronous PWM mode and PFM mode. The operating mode is selected using register bits BUCKA\_MODE and BUCKB\_MODE.

An automatic phase shedding can be enabled for each buck converter in PWM mode via PH\_SH\_EN\_A, PH\_SH\_EN\_B, thereby automatically reducing or increasing the number of active phases depending on the output load current. For DA9214 the phase shedding will automatically change between 1-phase and 2-phase operation at a typical current of 2.0 A. For DA9213 the phase shedding will automatically change between 1-phase and 4-phase operation at a typical current of 2.5 A. The PHASE\_SEL\_A and PHASE\_SEL\_B register fields limit the maximum number of active phases under any conditions.

If the automatic operation mode is selected on BUCKA\_MODE or BUCKB\_MODE, the buck converters will automatically change between synchronous PWM mode and PFM depending on the load current. This improves the efficiency of the converters across the whole range of output load currents.

### 7.1.3 Output Voltage Selection

The switching converter can be configured using either a 2-WIRE or a 4-WIRE interface. For security reasons, the re-programming of registers that can cause damage when wrongly programmed (for example, the voltage settings) can be disabled by asserting the control V\_LOCK. When V\_LOCK is asserted, reprogramming the registers 0xD0 to 0x14F from control interfaces is disabled.

For each buck converter two output voltages can be pre-configured inside registers VBUCKA\_A and VBUCKB\_A, and registers VBUCKA\_B and VBUCKB\_B. The output voltage can be selected by either toggling register bits VBUCKA\_SEL and VBUCKB\_SEL or by re-programming the selected voltage control register. Both changes will result into ramped voltage transitions, during which the READY signal is asserted. After being enabled, the buck converter will by default use the register settings in VBUCKA\_A and VBUCKB\_A unless the output voltage selection is configured via the GPI port.

If "00" has been selected in BUCKA\_MODE or BUCKB\_MODE, A-/B- voltage selection registers VBUCKx\_x control the operation of the PWM and PFM modes.

Regardless of the values programmed in the VBUCKx\_A and VBUCKx\_B registers, the registers VBUCKA\_MAX, VBUCKB\_MAX will individually limit the output voltage that can be set for each of the buck converters.

The buck converter provides an optional hardware enable/disable via selectable GPI, and configured via control register bits BUCKA\_GPI and BUCKB\_GPI. A change of the output voltage from the state of a GPI is enabled via control register bits VBUCKA\_GPI and VBUCKB\_GPI. After detecting a rising or falling edge at the related GPIs, DA9213, DA9214, and DA9215 will configure the buck converters according to their status.

In addition to selecting between the A/B voltages, a track mode can be activated for Buck A to set the output voltage. In the DA9213, the track mode is applied to the 4-phase buck converter. This feature can be enabled on GPI0 via GPI0\_PIN. The output voltage will be configured to follow the value applied at a selected GPI pin. The voltage applied at GPI0 must be in the same range as the nominal

output voltage selectable for the buck rail (see VBUCKA\_A and VBUCKA\_B registers). In Track Mode, only single ended remote sensing is possible.

In Track Mode, the content of the VBUCKA\_SEL bit is ignored, as well as VBUCKA\_A and VBUCKA\_B bits. They will become active again once the voltage track mode is disabled. The GPI0 does not generate any event in this case.

Figure 16: Concept of Control of the Buck's Output Voltage

#### 7.1.4 Soft Start-Up

To limit in-rush current from VSYS, the buck converters can perform a soft start after being enabled. The start-up behavior is a compromise between acceptable inrush current from the battery and turn on time. In DA9213, DA9214, and DA9215, different ramp times can be individually configured for each buck converter on register BUCKA\_UP\_CTRL and BUCKB\_UP\_CTRL. Rates higher than 20 mV/µs may produce overshoot during the start-up phase, so they should be considered carefully.

A ramped power down can be selected on register bits BUCKA\_DOWN\_CTRL and BUCKB\_DOWN\_CTRL. When no ramp is selected, the output node will be discharged only by the pull down resistor, if enabled via BUCKA\_PD\_DIS and BUCKB\_PD\_DIS.

#### 7.1.5 Current Limit

The integrated current limit is meant to protect DA9213, DA9214, and DA9215's power stages and the external coil from excessive current. The bucks' current limit should be configured to be at least 40 % higher than the required maximum continuous output current.

When reaching the current limit, each buck converter generates an event and an interrupt to the host processor unless the interrupt has been masked using the OCx\_MASK controls. These OCA\_MASK and OCB\_MASK control bits can be used to mask the generation of over current events during DVC transitions. An extra masking time as defined in OCx\_MASK will be automatically added to the DVC interval after the DVC has finished in order to ensure that the possible high current levels needed for DVC do not influence the event generation.

#### 7.1.6 Variable VOUT above 1.57 V

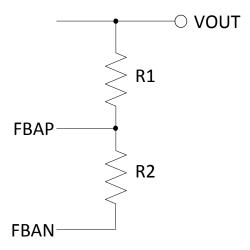

The whole product family is also available with an adjustable output voltage up to 4.3V. A resistive divider from VOUT to FBAN (or FBBN) can be used to set the output voltage higher than 1.57 V, see Figure 17. The specific variant DA921\_S is optimized for variable output voltage and the VREF on FBAN (or FBBN) is set to 1.2 V.

The value of the output voltage  $V_{OUT}$  is set by the selection of the resistive divider shown in equation 1. The total resistance of the divider resistors (R1+R2) should be less than 40 k $\Omega$ .

$$VOUT = \left(1 + \frac{R1}{R2}\right) \cdot VREF$$

#### **Equation 1**

Figure 17: Resistive Divider from VOUT to FBAN

For example, to program the output voltage VOUT to 1.8 V, suggest 10 k $\Omega$  on R1 and 20 k $\Omega$  on R2.

Note 1 The resistors need to be properly selected since the output voltage accuracy will be directly affected by any errors on the resistors. The voltage across FBAP and FBAN (VREF) is guaranteed, but not the output voltage accuracy.

### **CAUTION**

The followings are important notes that need to be considered before using resistive divider on DA9213, DA9214, and DA9215:

- Please contact your region's Dialog representative when adopting the resistive divider technique. Dialog

need to prepare a special OTP because incorrect OTP settings may result in a different output voltage than

expected.

- The voltage difference between input voltage and output voltage needs to be: above 1.2 V, VIN-VOUT > 1.2 V.

- 3. The total resistance (R1+R2) is less than 40 k $\Omega$ .

- 4. It is recommended that the device is operated in PWM mode only.

## 7.2 Ports Description

This section describes the functionality of each input / output port.

#### 7.2.1 **VDDIO**

VDDIO is an independent IO supply rail input to DA9213, DA9214, and DA9215 that can be assigned to the power manager interface and to the GPIOs (see control PM\_IF\_V and GPI\_V). The rail assignment determines the IO voltage levels and logical thresholds (see also the Digital I/O Characteristics in Table 7).

An integrated under voltage lockout circuit for the VDDIO prevents internal errors by disabling the I<sup>2</sup>C communication when the voltage drops below V<sub>ULO\_IO</sub>. In that case the buck converters are also disabled and cannot be re-enabled (even via input port) until the VDDIO under voltage condition has been resolved. At the exit of the VDDIO under voltage condition an event E\_UVLO\_IO is generated and the nIRQ line is driven active if the event is not masked.

The VDDIO under voltage circuit monitors voltages relative to a nominal voltage of 1.8V. If a different rail voltage is being used, the under-voltage circuit can be disabled via UVLO\_IO\_DIS.

Note that the maximum speed at 4-WIRE interface is only available if the selected supply rail is greater than 1.6 V.

### 7.2.2 IC\_EN

IC\_EN is a general enable signal for DA9213, DA9214, and DA9215, turning on and off the internal circuitry (for example, the reference, the digital core, etc.). Correct control of this port has a direct impact on the quiescent current of the whole application. A low level of IC\_EN allows the device to reach the minimum quiescent current. The voltage at this pin is continuously sensed by a dedicated analogue circuit.

The host processor will be allowed to start the communication with DA9213, DA9214, and DA9215 through the Control Interface and, for example to turn on the buck converters, a delay time of t<sub>EN</sub> after assertion of the IC\_EN pin. If the bucks are enabled via OTP (see BUCKA\_EN and BUCKB\_EN controls), they will start up automatically after assertion of IC\_EN.

The IC\_EN activation threshold is defined with a built in hysteresis to avoid glitching transitions that take place with unstable rising or falling edges.

#### 7.2.3 nIRQ

The nIRQ port indicates that an interrupt causing event has occurred and that the event/status information is available in the related registers. The nIRQ is an output signal that can either be push pull or open drain (selected via IRQ\_TYPE). If an active high IRQ signal is required, it can be achieved by asserting control IRQ\_LEVEL (recommended for push-pull mode).

Examples of this type of information can be critical temperature and voltage, fault conditions, status changes at GPI ports, and so forth. The event registers hold information about the events that have occurred. Events are triggered by a status change at the monitored signals. When an event bit is set, the nIRQ signal is asserted unless this interrupt is masked by a bit in the IRQ mask register. The nIRQ will not be released until all event registers with asserted bits have been read and cleared. New events that occur during reading an event register are held until the event register has been cleared, ensuring that the host processor does not miss them.

#### 7.2.4 **GPIO Extender**

DA9213, DA9214, and DA9215 include a GPIO extender that offers up to five 5 V-tolerant general purpose input/output ports. Each port is controlled via registers from the host processor.

The GPIO3 and GPI4 ports are pin-shared with the 4-WIRE Control Interface. For instance, if GPIO3\_PIN = 01, GPI4\_PIN = 01 (Interface selected), the GPIO3 and GPI4 ports will be exclusively dedicated to output and chip select signaling for 4-WIRE purposes. If the alternative function is selected, all GPIOs configuration as per registers 0x58 to 0x5A and 0x145 will be ignored.

GPIs are supplied from the internal rail VDDCORE or VDDIO (selected via GPI\_V) and can be configured to be active high or active low (selected via GPIOx\_TYPE). The input signals can be debounced or directly change the state of the assigned status register GPIx to high or low, according to the setting of GPIOx\_MODE. The debouncing time is configurable via control DEBOUNCE (10 ms default).

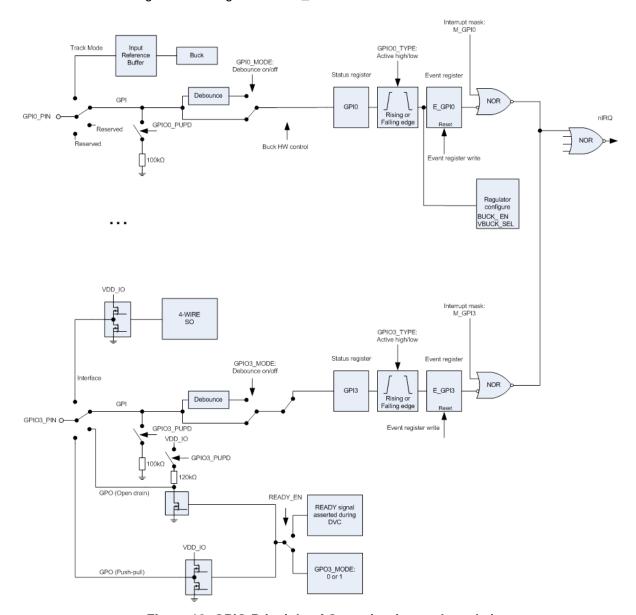

Whenever the status has changed to its configured active state (edge sensitive), the assigned event register is set and the nIRQ signal is asserted (unless this nIRQ is masked, see also Figure 18).

Whenever DA9213, DA9214, and DA9215 is enabled and enters ON mode (also when enabled changing the setting of GPIOx\_PIN) the GPI status bits are initiated towards their configured passive state. This ensures that already active signals are detected, and that they create an event immediately after the GPI comparators are enabled.

The buck enable signal (BUCKx\_EN) can be controlled directly via a GPI, if so configured in the BUCKA\_GPI and BUCKB\_GPI registers. If it is required that GPI ports do not generate an event when configured for the HW control of the switching regulator, the relative mask bit should be set.

GPIs can alternatively be selected to toggle the VBUCKA\_SEL and VBUCKB\_SEL from rising and falling edges at these inputs. Apart from changing the regulator output voltage this also provides hardware control of the regulator mode (normal/low power mode) from the settings of BUCKA\_SL\_A, BUCKA\_SL\_B, BUCKB\_SL\_A, and BUCKB\_SL\_B (enabled if BUCKA\_MODE or BUCKB\_MODE = '00').

All GPI ports have the additional option of activating a 100 k $\Omega$  pull-down resistor via GPIOx\_PUPD, which ensures a well-defined level in case the input is not actively driven.

If enabled via ADDR\_SEL\_CONF, the I<sup>2</sup>C address selection can be assigned to a specific GPI. An active voltage level at the selected GPI configures the slave address of DA9213, DA9214, and DA9215 to IF\_BASE\_ADDR1 while a passive voltage level configures the slave address to IF\_BASE\_ADDR2. If no GPI is selected then the IF\_BASE\_ADDR1 is automatically used.

If defined as an output, GPIOs can be configured to be open-drain or push-pull. If configured as push pull, the supply rail is VDDIO. By disabling the internal 120 k $\Omega$  pull-up resistor in open-drain mode, the GPO can also be supplied from an external rail. The output state will be assigned as configured by the GPIO register bit GPIOx\_MODE.

A specific power good port for each of the buck converters can be configured via BUCKA\_PG\_SEL and BUCKB\_PG\_SEL. The respective port must be configured as GPO for correct operation. If assigned to the same GPO, it is necessary that the power good indicators for Buck A and Buck B are both active (supply voltages in range) to assert the overall power good. The signal will be released as soon as one of the single power good signals is not active (that is, at least one supply is out of range).

The power good signaling should not be used in conjunction with fast start up rates, configured in BUCKx\_UP\_CTRL register fields.

Once enabled via RELOAD\_FUNC\_EN the GPIO0 can be used as input port to operate a partial OTP download. When the input level is changed to active, the registers 0x5D, 0x5E, 0xD1 to 0xDA are updated to their OTP default. This allows a complete buck re-configuration that resets all the changes done to those registers previously (soft reset). If the buck should be kept on during the soft

reset, the OTP values for the enable bits should be asserted because they are also part of the reload.

Whenever the GPIO unit is off (POR or OFF Mode) all ports are configured as open drain active high (pass device switched off, high impedance state). When leaving POR the pull-up or pull-down resistors will be configured from register GPIOx\_PUPD.

Figure 18: GPIO Principle of Operation (example paths)

## 7.3 Operating Modes

#### **7.3.1 ON Mode**

DA9213, DA9214, and DA9215 are in ON Mode when the IC\_EN port is higher than EN\_ON and the supply voltage is higher than  $V_{TH(UVLO)(VDD)}$ . Once enabled, the host processor can start the communication with DA9213, DA9214, and DA9215 via Control Interface after the  $t_{EN}$  delay needed for internal circuit start up.

If BUCKA\_EN or BUCKB\_EN is asserted when DA9213, DA9214, and DA9215 is in ON Mode the power up of the related buck converter is initiated. If the bucks are controlled via GPI, the level of the controlling ports is checked when entering ON mode, so that an active level will immediately have effect on the buck. If BUCKA\_EN or BUCKB\_EN are not asserted and all controlling GPI ports are inactive, the buck converter will stay off with the output pull down resistor enabled/disabled according to the setting of BUCKA\_PD\_DIS and BUCKB\_PD\_DIS.

#### **7.3.2 OFF Mode**

DA9213, DA9214, and DA9215 are in OFF Mode when the IC\_EN port is lower than EN\_OFF. In OFF Mode, the bucks are always disabled and the output pull down resistors are disabled independently of BUCKA\_PD\_DIS and BUCKB\_PD\_DIS. All I/O ports of DA9213, DA9214, and DA9215 are configured as high impedance.

#### 7.4 Control Interfaces

All the features of DA9213, DA9214, and DA9215 can be controlled by SW through a serial control interfaces. The communication is selectable to be either a 2-WIRE (I<sup>2</sup>C compliant) or a 4-WIRE connection (SPI compliant) via control IF\_TYPE, which will be selected during the initial OTP read. If 4-WIRE is selected, the GPIO3 and GPI4 are automatically configured as interface pins. Data is shifted into or out of DA9213, DA9214, and DA9215 under the control of the host processor, which also provides the serial clock. In a normal application case the interface is only configured once from OTP values, which are loaded during the initial start-up of DA9213, DA9214, and DA9215.

DA9213, DA9214, and DA9215 reacts only on read/write commands where the transmitted register address (using the actual page bits as a MSB address range extensions) is within 0x50 to 0x67, 0xD0 to DF, 0x140 to 0x14F and (read only) 0x200 to 0x27F. Host access to registers outside these ranges will be ignored. This means there will be no acknowledge after receiving the register address in 2-WIRE Mode, and SO stays HI-Z in 4-WIRE Mode. During debug and production modes write access is available to page 4 (0x200 to 0x27F). DA9213, DA9214, and DA9215 will react only on write commands where the transmitted register address is 0x00, 0x80, 0x100 to0x106. The host processor must read the content of those registers before writing, thereby changing only the bit fields that are not marked as reserved (the content of the read back comes from the compatible PMIC, for example DA9063).

If the STAND\_ALONE bit is asserted (OTP bit), DA9213, DA9214, and DA9215 will also react to read commands.

#### 7.4.1 4-WIRE Communication

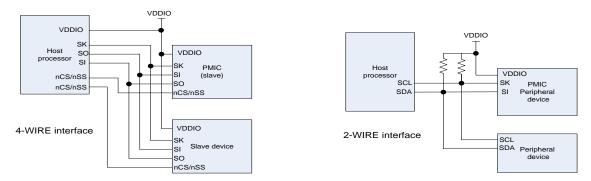

In 4-WIRE Mode the interface uses a chip-select line (nCS/nSS), a clock line (SK), data input (SI) and data output line (SO).

The DA9213, DA9214, and DA9215 register map is split into four pages that each contain up to 128 registers. The register at address zero on each page is used as a page control register. The default active page after turn on includes registers 0x50 to 0x6F. Writing to the page control register changes the active page for all subsequent read/write operations unless an automatic return to page 0 was selected by asserting bit REVERT. Unless the REVERT bit was asserted after modifying the

active page, it is recommended to read back the page control register to ensure that future data exchange is accessing the intended registers.

All registers outside the DA9213, DA9214, and DA9215 range are write only, that is, the DA9213, DA9214, and DA9215 will not answer to a read command and the data bus is tristate (they are implicitly directed to DA9063). In particular the information contained in registers 0x105 and 0x106 is used by DA9213, DA9214, and DA9215 to configure the control interface. They must be the same as the main PMIC (DA9063), so that a write to those registers configures both the main PMIC and DA9213, DA9214, and DA9215 at the same time. The default OTP settings also need to be identical for a correct operation of the system.

The 4-WIRE interface features a half-duplex operation, that is, data can be transmitted and received within a single 16-bit frame at enhanced clock speed (up to 14 MHz). It operates at the clock frequencies provided by the host.

Figure 19: Schematic of 4-WIRE and 2-WIRE Power Manager Bus

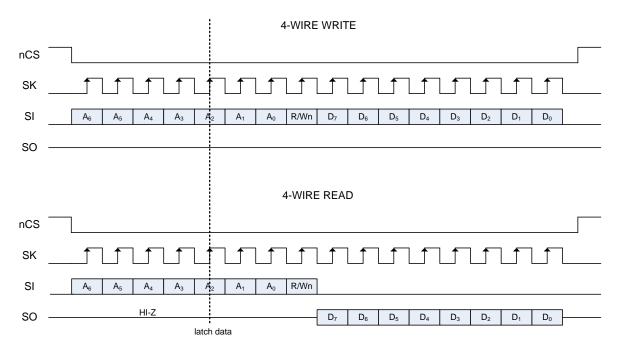

A transmission begins when initiated by the host. Reading and writing is accomplished by the use of an 8-bit command, which is sent by the host prior to the exchanged 8-bit data. The byte from the host begins shifting in on the SI pin under the control of the serial clock SK provided from the host. The first seven bits specify the register address (0x01 to 0x07) that will be written or read by the host. The register address is automatically decoded after receiving the seventh address bit. The command word ends with an R/W bit, which together with the control bit R/W\_POL specifies the direction of the following data exchange. During register writing the host continues sending out data during the following eight SK clocks. For reading, the host stops transmitting and the 8-bit register is clocked out of DA9213, DA9214, and DA9215 during the consecutive eight SK clocks of the frame. Address and data are transmitted with MSB first. The polarity (active state) of nCS is defined by control bit nCS\_POL. nCS resets the interface when inactive and it has to be released between successive cycles.

The SO output from DA9213, DA9214, and DA9215 is normally in high-impedance state and active only during the second half of read cycles. A pull-up or pull-down resistor may be needed at the SO line if a floating logic signal can cause unintended current consumption inside other circuits.

Table 10: 4-WIRE Clock Configurations

| CPHA Clock<br>Polarity | CPOL Clock<br>Phase | Output Data is Updated at SK<br>Edge | Input Data is Registered at SK<br>Edge |

|------------------------|---------------------|--------------------------------------|----------------------------------------|

| 0 (idle low)           | 0                   | Falling                              | Rising                                 |

| 0 (idle low)           | 1                   | Rising                               | Falling                                |

| 1 (idle high)          | 0                   | Rising                               | Falling                                |

| 1 (idle high)          | 1                   | Falling                              | Rising                                 |

Datasheet Revision 2.2 23-Oct-2017

DA9213, DA9214, and DA9215's 4-WIRE interface offers two further configuration bits. Clock polarity (CPOL) and clock phase (CPHA) define when the interface will latch the serial data bits. CPOL determines whether SK idles high (CPOL = 1) or low (CPOL = 0). CPHA determines on which SK edge data is shifted in and out. With CPOL = 0 and CPHA = 0, DA9213, DA9214, and DA9215 latch data on the SK rising edge. If the CPHA is set to 1 the data is latched on the SK falling edge. CPOL and CPHA states allow four different combinations of clock polarity and phase. Each setting is incompatible with the other three. The host and DA9213, DA9214, and DA9215 must be set to the same CPOL and CPHA states to communicate with each other.

Figure 20: 4-WIRE Host Write and Read Timing (nCS\_POL = '0', CPOL = '0', CPHA = '0')

Figure 21: 4-WIRE Host Write and Read Timing (nCS\_POL= '0', CPOL = '0', CPHA = '1')

Figure 22: 4-WIRE Host Write and Read Timing (nCS\_POL = '0', CPOL = '1', CPHA = '0')

Figure 23: 4-WIRE Host Write and Read Timing (nCS\_POL = '0', CPOL = '1', CPHA = '1')

**Table 11: 4-WIRE Interface Summary**

| Parameters     |                           |                                             |  |  |  |

|----------------|---------------------------|---------------------------------------------|--|--|--|

|                | nCS                       | Chip select                                 |  |  |  |

| Signal lines   | SI Serial input data      | Master out Slave in                         |  |  |  |

| Signal lines   | SO Serial output data     | Master in Slave out                         |  |  |  |

|                | SK                        | Transmission clock                          |  |  |  |

| Interface      | Push-pull with tristate   |                                             |  |  |  |

| Supply voltage | Selected from VDDIO       | 1.6 V to 3.3 V                              |  |  |  |

| Data rate      | Effective read/write data | Up to 7 Mbps                                |  |  |  |

| Transmission   | Half-duplex               | MSB first                                   |  |  |  |

| Hansinission   | 16-bit cycles             | 7-bit address, 1-bit read/write, 8-bit data |  |  |  |

|                | CPOL                      | Clock polarity                              |  |  |  |

| Configuration  | СРНА                      | Clock phase                                 |  |  |  |

|                | nCS_POL                   | nCS is active low/high                      |  |  |  |

Note 1 Reading the same register at high clock rates directly after writing it does not guarantee a correct value. It is recommended to keep a delay of one frame until re-accessing a register that has just been written (for example, by writing/reading another register address in-between).

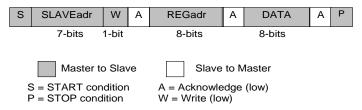

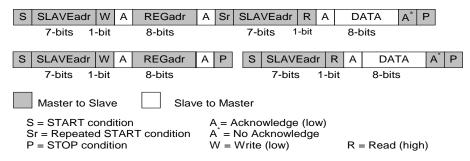

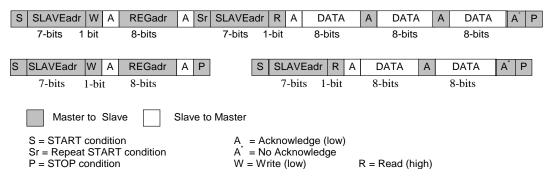

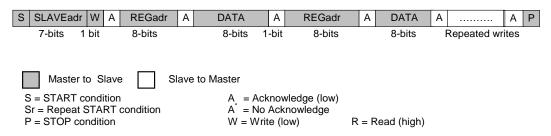

### 7.4.2 2-WIRE Communication

The IF\_TYPE bit in the INTERFACE2 register can be used to configure the DA9213, DA9214, and DA9215 control interface as a 2-WIRE serial data interface. In this case the GPIO3 and GPI4 are free for regular input/output functions. DA9213, DA9214, and DA9215 has a configurable device write address (default: 0xD0) and a configurable device read address (default: 0xD1). See control IF\_BASE\_ADDR1 for details of configurable addresses. The ADDR\_SEL\_CONF bit is used to configure the device address as IF\_BASE\_ADDR1 or IF\_BASE\_ADDR2 depending on the voltage level applied at a configurable GPI port (see Section 7.2.4).