## **General Description**

DA9313 is a high-voltage power converter with a maximum output current of 10 A, suitable for applications supplied from a dual (2S) Li-ion or Li-polymer stacked cell battery pack, or any input voltage between 5 V and 10.5 V. The converter operates with efficiency during conversion of up to 98 %. Master/slave operation is offered, where a pair of devices can combine to double the peak output current to 20 A.

Low profile external components and a minimum PCB footprint allow small circuit implementation in compact applications. The pass devices are fully integrated therefore no external FETs are needed.

DA9313 utilizes a programmable soft start to limit the inrush current from the input node and secure a slope controlled activation of the rails. It also implements integrated over-temperature and over-current protection for increased system reliability without the need for external sensing components.

Enable, low power mode entry and exit, and power good signals are available at configurable ports flexibly supporting different applications and power-up or power-down scenarios.

## **Key Features**

- 2S to 1S power voltage converter

- 5 V to 10.5 V input voltage (2S Li-ion stacked battery pack)

- 10 A total output current (standalone)

- 20 A total output current (master/slave)

- 1.0 mm max external components height

- Integrated power switches

- I<sup>2</sup>C compatible interface

- $V_{OUT} = \frac{1}{2} V_{IN}$

- High and flat efficiency, up to 98 %

- Typical 55 µA quiescent current (standalone)

- □ Typical 70 µA total quiescent current in master/slave configuration

- Package 43 WLCSP (RouteEasy<sup>™</sup> equivalent to 0.65 mm pitch)

# **Applications**

- Ultrabooks™

- Notebook computers

- Chromebooks<sup>™</sup>

- Tablets

- Smartphone direct charging

- DSLR and mirrorless cameras

- Camcorders

- Power banks

- 2S battery applications

# Contents

| Ge  | neral l    | Descript           | ion                                            | 1  |

|-----|------------|--------------------|------------------------------------------------|----|

| Ke  | y Feat     | ures               |                                                | 1  |

| Аp  | plicati    | ions               |                                                | 1  |

| Со  | ntents     | S                  |                                                | 2  |

| Fig | ures       |                    |                                                | 3  |

| Tal | oles       |                    |                                                | 4  |

| 1   | Term       | s and De           | efinitions                                     | 5  |

| 2   |            |                    |                                                |    |

| 3   |            |                    | ock Diagrams                                   |    |

| 4   |            |                    | Ook Diagrams                                   |    |

| -   |            |                    | kimum Ratings                                  |    |

| 5   |            |                    | <del>-</del>                                   |    |

| 6   |            |                    | ed Operating Conditions                        |    |

| 7   |            |                    | aracteristics                                  | _  |

|     | 7.1        |                    | On-Reset, Reference Generation and Supervision |    |

|     | 7.2        |                    | Oscillator                                     |    |

|     | 7.3        |                    | /oltage Converter                              |    |

|     | 7.4<br>7.5 |                    |                                                |    |

|     | 7.5<br>7.6 |                    | O Characteristics                              |    |

| 0   | _          | ŭ                  | us                                             |    |

| 8   |            |                    |                                                |    |

| 9   |            |                    | acteristics                                    |    |

|     | 9.1<br>9.2 |                    | one OperationSlave Operation                   |    |

| 40  |            |                    | •                                              |    |

| 10  |            |                    | escription                                     | 22 |

|     | 10.1       | Start Up<br>10.1.1 | Standalone Operation                           | າາ |

|     |            | 10.1.1             | Master/Slave Operation                         |    |

|     | 10.2       |                    | e Functions                                    |    |

|     | 10.2       | 10.2.1             | GPIOs                                          |    |

|     |            | 10.2.2             | nONKEY                                         |    |

|     | 10.3       | Power \            | /oltage Converter                              | 27 |

|     |            | 10.3.1             | PVC Output Voltage                             |    |

|     |            | 10.3.2             | PVC Start-Up                                   | 27 |

|     |            | 10.3.3             | PVC Operating Modes                            | 28 |

|     |            | 10.3.4             | PVC Power Down                                 | 29 |

|     |            | 10.3.5             | PVC Current Limit                              | 29 |

| 11  | Opera      | ating Mo           | des                                            | 30 |

|     | 11.1       | OFF Mo             | ode (HARDRESET)                                | 31 |

|     | 11.2       | POWER              | R_DOWN Mode                                    | 31 |

|     |            |                    | Mode                                           |    |

|     |            |                    | Mode                                           |    |

|     | 11.5       | FAULT              | RECOVERY Mode                                  | 32 |

|                                        |                                                                              | 11.5.1                                                                                                                                                                                        | Input Under-Voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 32                   |

|----------------------------------------|------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

|                                        |                                                                              | 11.5.2                                                                                                                                                                                        | Over-Temperature                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 33                   |

|                                        |                                                                              | 11.5.3                                                                                                                                                                                        | PVC Current Limit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 33                   |

|                                        |                                                                              | 11.5.4                                                                                                                                                                                        | PVC Start-Up Failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 33                   |

|                                        | 11.6                                                                         | VCORE                                                                                                                                                                                         | Voltage Regulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

|                                        |                                                                              |                                                                                                                                                                                               | Generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|                                        | 11.8                                                                         |                                                                                                                                                                                               | Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                      |

|                                        |                                                                              | 11.8.1                                                                                                                                                                                        | Internal Temperature Supervision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                      |

| 40                                     | Comt                                                                         |                                                                                                                                                                                               | ace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                      |

| 12                                     |                                                                              |                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

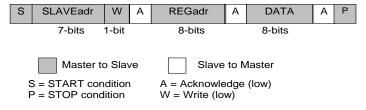

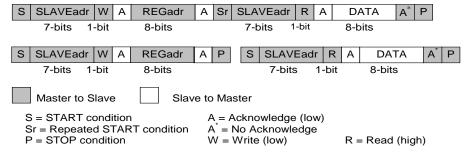

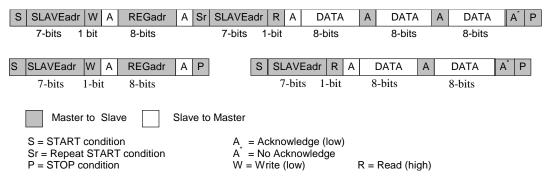

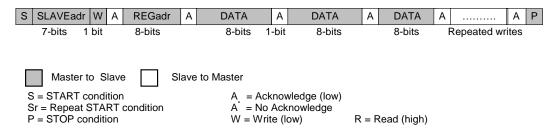

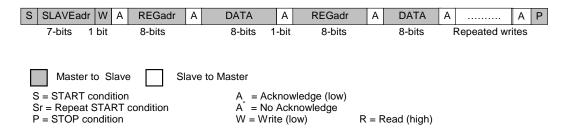

|                                        |                                                                              |                                                                                                                                                                                               | nmunication                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                      |

|                                        |                                                                              |                                                                                                                                                                                               | trol Bus Protocol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 13                                     | Regis                                                                        | ster Defi                                                                                                                                                                                     | nitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38                   |

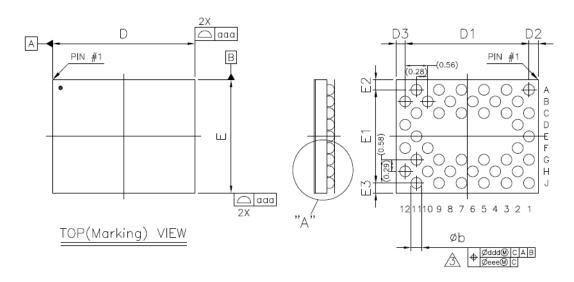

| 14                                     | Pack                                                                         | age Info                                                                                                                                                                                      | rmation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 50                   |

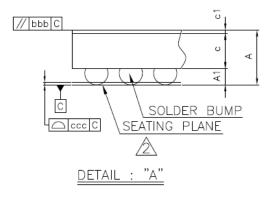

|                                        | 14.1                                                                         | Package                                                                                                                                                                                       | e Outline                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 50                   |

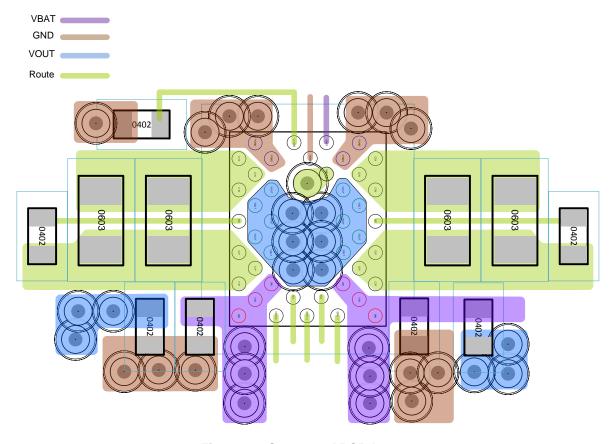

|                                        | 14.2                                                                         | Sugges                                                                                                                                                                                        | ted PCB Layout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 51                   |

|                                        |                                                                              |                                                                                                                                                                                               | asyTM Technology Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

| 15                                     |                                                                              |                                                                                                                                                                                               | of the formation in the |                      |

| 13                                     |                                                                              |                                                                                                                                                                                               | nended Capacitors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

|                                        |                                                                              |                                                                                                                                                                                               | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| 16                                     | Orde                                                                         | ring Info                                                                                                                                                                                     | rmation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52                   |

| Re                                     | vision                                                                       | History                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 53                   |

| Fig                                    | gure                                                                         | S                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                      |

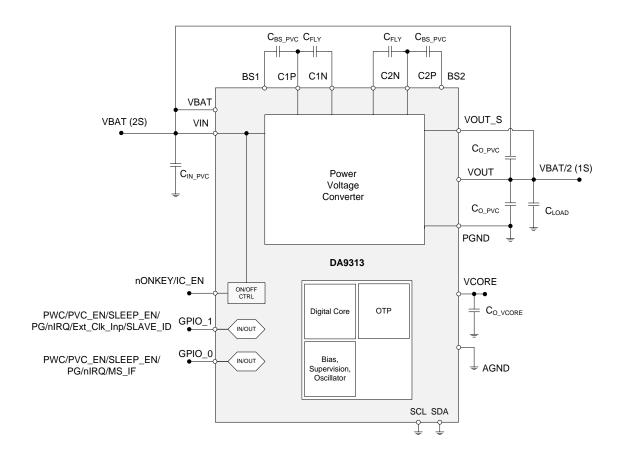

|                                        |                                                                              |                                                                                                                                                                                               | al Block Diagram Standalone (I <sup>2</sup> C Not Connected)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

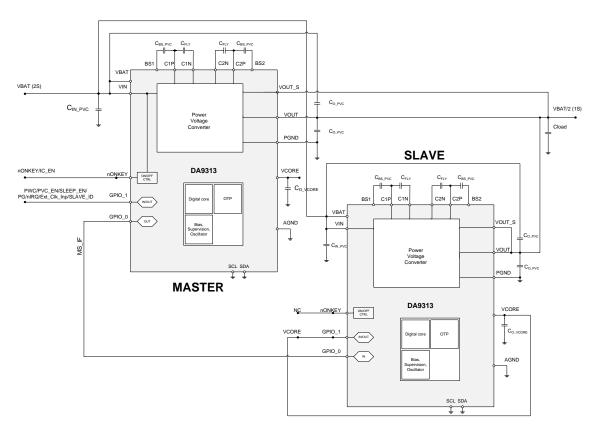

| Fig                                    | ure 2:                                                                       | Function                                                                                                                                                                                      | al Block Diagram Master/Slave Operation (I <sup>2</sup> C Not Connected)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                    |

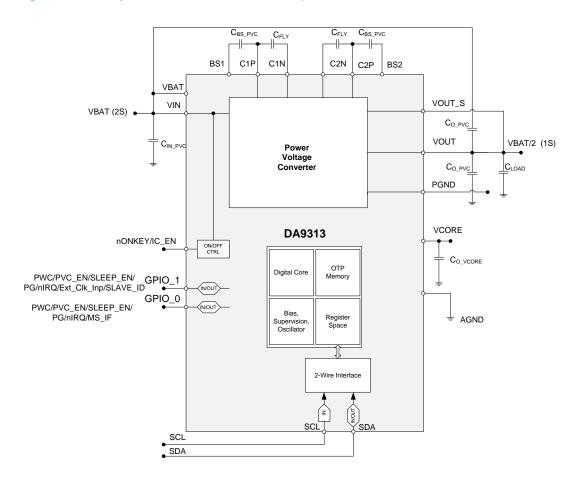

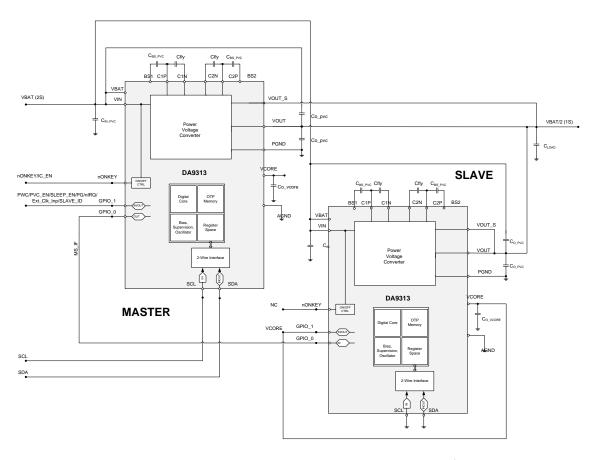

|                                        |                                                                              |                                                                                                                                                                                               | al Block Diagram Standalone (I <sup>2</sup> C Connected)al Block Diagram Master/Slave Operation (I <sup>2</sup> C Connected)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                      |

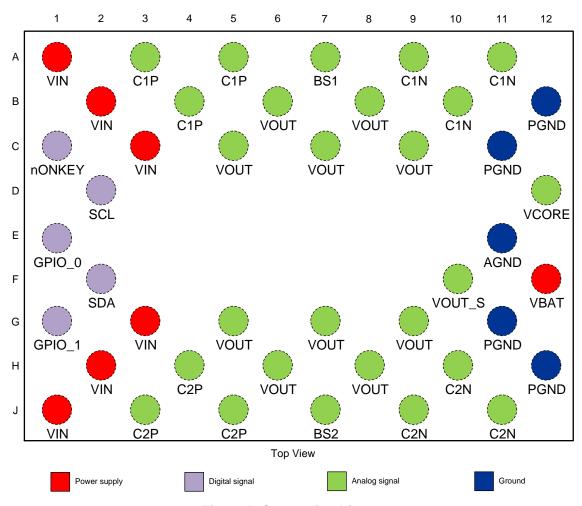

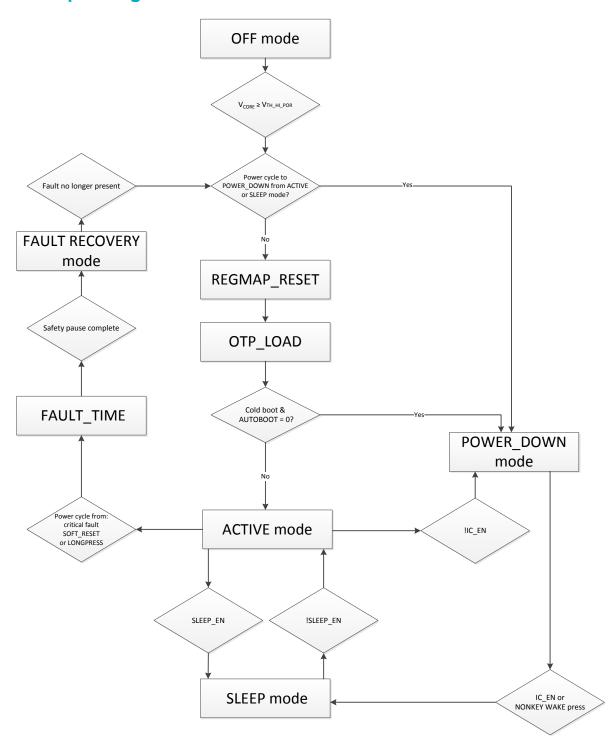

|                                        |                                                                              |                                                                                                                                                                                               | ion Diagramion Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

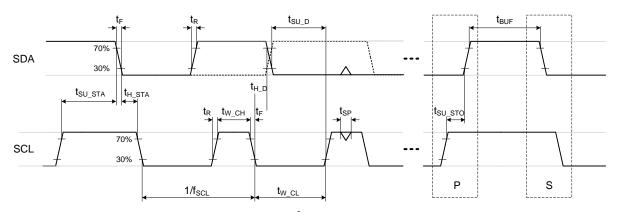

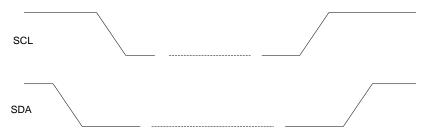

|                                        |                                                                              |                                                                                                                                                                                               | Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                      |

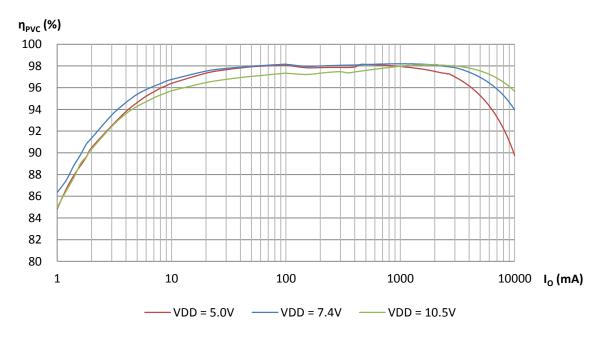

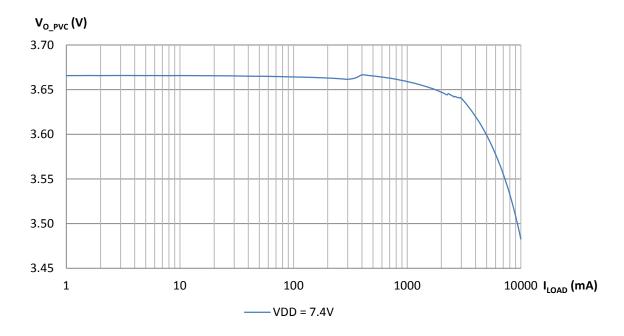

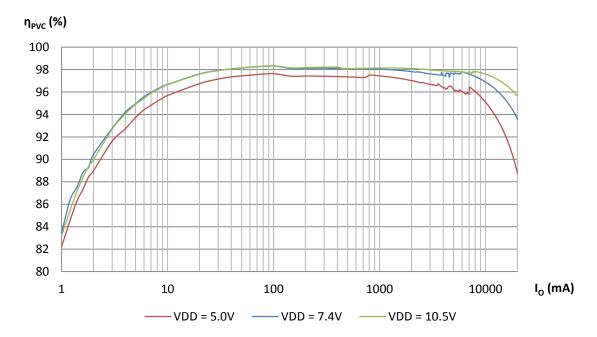

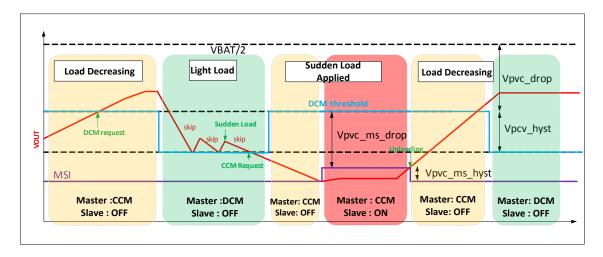

| Fig                                    | ure 7:                                                                       | DA9313                                                                                                                                                                                        | Efficiency Automatic Mode Standalone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 19                   |

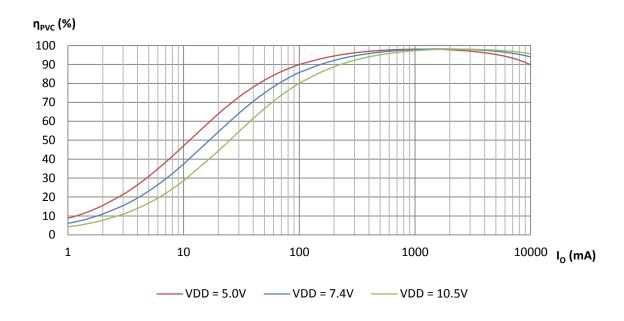

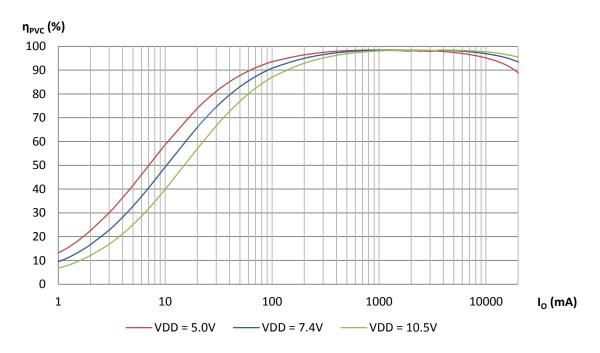

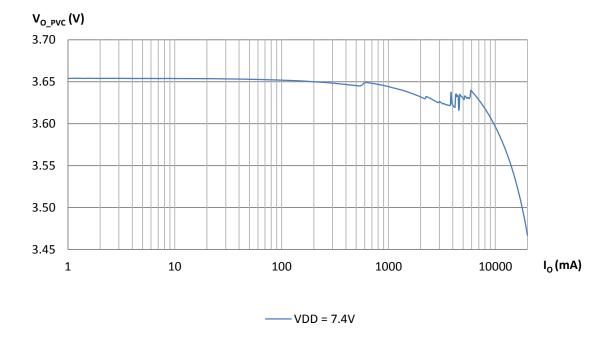

|                                        |                                                                              |                                                                                                                                                                                               | Efficiency Fixed Frequency Mode Standalone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                   |