**DAC1282, DAC1282A**

SBAS490B - DECEMBER 2011 - REVISED MAY 2015

# DAC1282 Low Distortion Digital-to-Analog Converter for Seismic

### **Features**

- Single-Chip Test Signal Generator

- **Buffered Voltage Output**

- High Performance:

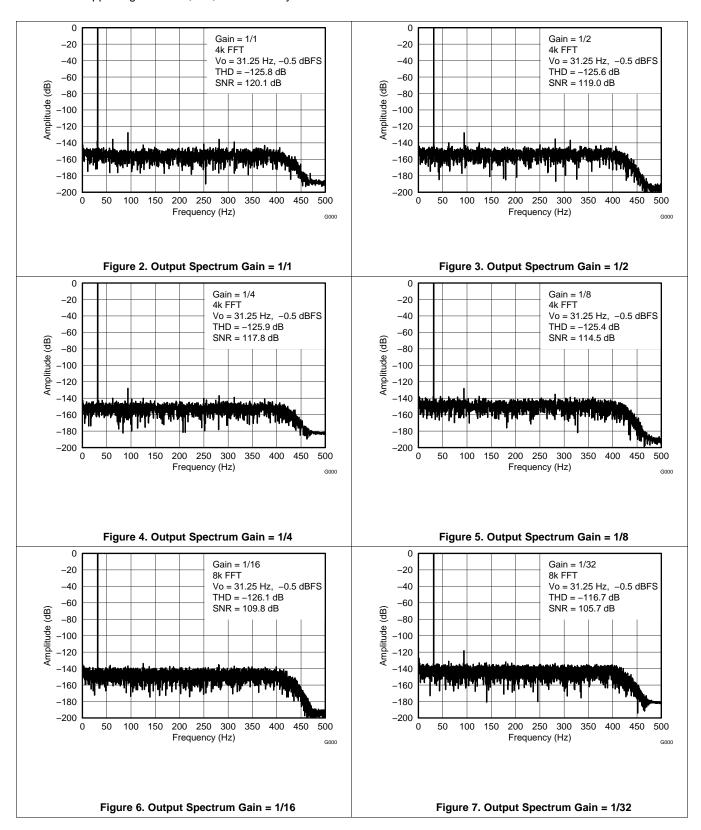

- THD: -125 dB (G = 1/1 to 1/8)

- SNR: 120 dB (413 Hz BW, G = 1/1)

- Analog and Digital Gain Control

- Output Frequency: 0.488 Hz to 250 Hz

- Sine, Pulse, and DC Modes

- Digital Data Input Mode

- Low On-Resistance Signal Switch

- Sync Input

- Power-Down Mode

- Analog Supply: 5 V or ±2.5 V

- Digital Supply: 1.8 V to 3.3 V

- Power: 38 mW

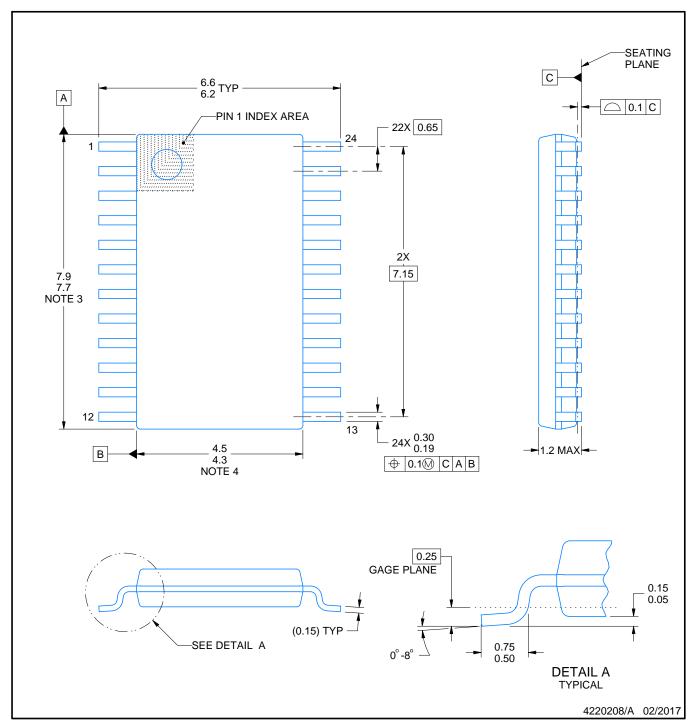

- Package: TSSOP-24

- Operating Range: -50°C to +125°C

# **Applications**

- **Energy Exploration**

- Seismic Monitoring Systems

- **High-Accuracy Instrumentation**

# 3 Description

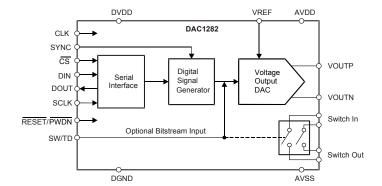

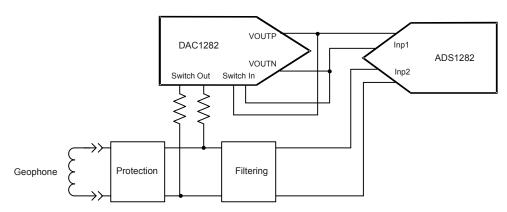

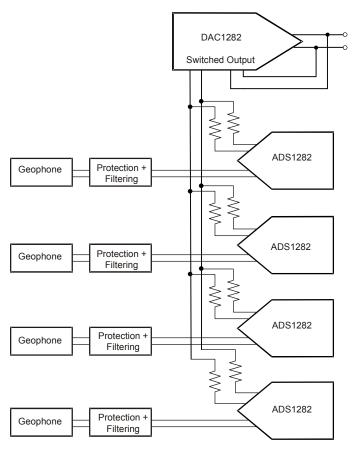

The DAC1282 is a fully-integrated digital-to-analog converter (DAC) providing low distortion, digital synthesized voltage output suitable for testing of seismic equipment. The DAC1282 achieves very high performance in a small package with low power. Together, with the high-performance ADS1281 and ADS1282 analog-to-digital converters (ADCs), these devices create a measurement system that meets the exacting demands of seismic data acquisition equipment.

The DAC1282 integrates a digital signal generator, a DAC, and an output amplifier providing sine wave, dc, and pulse output voltages.

The output frequency is programmable from 0.5 Hz to 250 Hz and the magnitude is scaled by both analog and digital control. The analog gain is adjustable in 6dB steps and the digital gain in 0.5-dB steps. The analog gain settings match those of the ADS1282 for testing at all gains with high resolution.

The DAC1282 also provides pulse outputs. The pulse amplitude is user-programmed and then selected by the pin for precise timing. Custom output signals can be generated by applying an external bitstream pattern.

A signal switch can be used to connect the DAC output to sensors for THD and impulse testing. The switch timing is controlled by pin and by command.

A SYNC pin synchronizes the DAC output to the analog-to-digital converter (ADC) sample interval. A power-down input disables the device, reducing power consumption to microwatts.

| T-1 |     | _£ | Co           | 1-  | 1-   |

|-----|-----|----|--------------|-----|------|

| ıaı | nie | OΤ | ı.n          | nte | nte  |

| ıuı | JIC | vı | $\mathbf{v}$ |     | 1113 |

| 1 | Features 1                                                        | 8.1 Overview 14                         |

|---|-------------------------------------------------------------------|-----------------------------------------|

| 2 | Applications 1                                                    | 8.2 Feature Description                 |

| 3 | Description 1                                                     | 8.3 Device Functional Modes30           |

| 4 | Revision History2                                                 | 8.4 Programming                         |

| 5 | Device Comparison                                                 | 8.5 Register Map                        |

| 6 | Pin Configuration and Functions                                   | 9 Application and Implementation 36     |

|   | _                                                                 | 9.1 Application Information             |

| 7 | Specifications                                                    | 9.2 Typical Applications                |

|   | 7.1 Absolute Maximum Ratings                                      | 10 Device and Documentation Support 39  |

|   | 7.2 ESD Ratings                                                   | 10.1 Community Resources                |

|   | 7.3 Thermal Information                                           | 10.2 Trademarks                         |

|   | 7.4 Electrical Characteristics                                    | 10.3 Electrostatic Discharge Caution    |

|   | 7.5 Timing Requirements: Serial Peripheral Interface (SPI) Timing | 10.4 Glossary                           |

|   | 7.6 Typical Characteristics 9                                     | 11 Mechanical, Packaging, and Orderable |

| 8 | Detailed Description 14                                           | Information 39                          |

|   | •                                                                 |                                         |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Cha | inges from Revision A (September 2012) to Revision B        | Page |

|-----|-------------------------------------------------------------|------|

| • / | Added ADS1282A device to data sheet                         | 1    |

| Cha | anges from Original (December 2011) to Revision A           | Page |

| • ( | Updated Figure 16                                           | 10   |

| • / | Added last paragraph to Signal Output section               | 16   |

| • ( | Changed t <sub>CSHD</sub> minimum specification in Table 11 | 25   |

| • ( | Changed min, max, and unit columns in Table 12              | 26   |

# 5 Device Comparison

| DEVICE  | DESCRIPTION                  |

|---------|------------------------------|

| ADS1281 | High-resolution ADC          |

| ADS1282 | High-resolution ADC with PGA |

| REF5050 | Low-drift 5 V reference      |

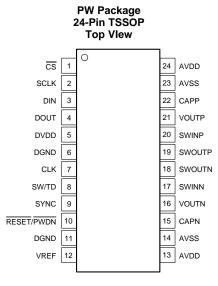

# 6 Pin Configuration and Functions

# **Pin Functions**

| NAME         NO.           AVDD         13, 24         Analog supply         Analog positive power supply, reference ground           AVSS         14         Analog supply         Analog negative power supply, reference ground           AVSS         23         Analog supply         Analog negative power supply, reference ground           CAPN         15         Analog         External capacitor connected to VOUTN           CAPP         22         Analog         External capacitor connected to VOUTP           CS         1         Digital input         Serial port chip select           CLK         7         Digital input         Master clock 4.096 MHz           DGND         6         Ground         Key digital ground           DGND         11         Ground         Digital ground           DOUT         4         Digital input         Serial port data input           DOUT         4         Digital output         Serial port data output           DVDD         5         Digital supply         Digital power supply: 1.65 V to 3.6 V           RESET/PWDN         10         Digital input         Reset/power-down input           SCLK         2         Digital input         Switch positive lock           SW/TD         8 | PIN        |        | FUNCTION       | DECODINE                                       |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------|----------------|------------------------------------------------|--|

| AVSS 14 Analog supply Analog negative power supply, reference ground  AVSS 23 Analog supply Analog negative power supply  CAPN 15 Analog External capacitor connected to VOUTN  CAPP 22 Analog External capacitor connected to VOUTP  CS 1 Digital input Serial port chip select  CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DIN 3 Digital input Serial port data input  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Serial port shift clock  SW/TD 8 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTN 18 Analog I/O Switch negative output  SYNC 9 Digital input Negative output  Negative voltage output  Negative voltage output  Negative voltage output  Negative voltage output  Positive voltage output                                                                                                                                                                                                                                                                            | NAME       | NO.    | FUNCTION       | DESCRIPTION                                    |  |

| AVSS 23 Analog supply Analog negative power supply  CAPN 15 Analog External capacitor connected to VOUTN  CAPP 22 Analog External capacitor connected to VOUTP  Test 1 Digital input Serial port chip select  CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DGND 11 Ground Digital input Serial port data input  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Serial port shift clock  SW/TD 8 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTN 18 Analog I/O Switch positive output  SYNC 9 Digital input Negative voltage output  Negative voltage output  Positive voltage output  Positive voltage output  Positive voltage output                                                                                                                                                                                                                                                                                                                                                        | AVDD       | 13, 24 | Analog supply  | Analog positive power supply                   |  |

| CAPN 15 Analog External capacitor connected to VOUTN  CAPP 22 Analog External capacitor connected to VOUTP  CS 1 Digital input Serial port chip select  CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DGND 11 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Serial port as a control input or bitstream input  SWIND 8 Digital input Serial port shift clock  SWITD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Negative voltage output  Negative voltage output  Negative voltage output  Negative voltage output  VOUTN 16 Analog output Positive voltage output  Positive voltage output                                                                                                                                                                                                                                                                                                                                                          | AVSS       | 14     | Analog supply  | Analog negative power supply, reference ground |  |

| CAPP 22 Analog External capacitor connected to VOUTP  CS 1 Digital input Serial port chip select  CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DGND 11 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Serial port shift clock  SW/TD 8 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTN 18 Analog I/O Switch positive output  SYNC 9 Digital input Negative voltage output  VOUTN 16 Analog output Positive voltage output  Positive voltage output  VOUTP 21 Analog output Positive voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                     | AVSS       | 23     | Analog supply  | Analog negative power supply                   |  |

| CS 1 Digital input Serial port chip select  CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DGND 11 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Negative voltage output  Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CAPN       | 15     | Analog         | External capacitor connected to VOUTN          |  |

| CLK 7 Digital input Master clock 4.096 MHz  DGND 6 Ground Key digital ground  DGND 11 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWOUTN 18 Analog I/O Switch positive input  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  Negative voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CAPP       | 22     | Analog         | External capacitor connected to VOUTP          |  |

| DGND 6 Ground Key digital ground  DGND 111 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output  Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | CS         | 1      | Digital input  | Serial port chip select                        |  |

| DGND 11 Ground Digital ground  DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch positive output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output  Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CLK        | 7      | Digital input  | Master clock 4.096 MHz                         |  |

| DIN 3 Digital input Serial port data input  DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch positive output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DGND       | 6      | Ground         | Key digital ground                             |  |

| DOUT 4 Digital output Serial port data output  DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DGND       | 11     | Ground         | Digital ground                                 |  |

| DVDD 5 Digital supply Digital power supply: 1.65 V to 3.6 V  RESET/PWDN 10 Digital input Reset/power-down input  SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | DIN        | 3      | Digital input  | Serial port data input                         |  |

| RESET/PWDN   10   Digital input   Reset/power-down input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DOUT       | 4      | Digital output | Serial port data output                        |  |

| SCLK 2 Digital input Serial port shift clock  SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | DVDD       | 5      | Digital supply | Digital power supply: 1.65 V to 3.6 V          |  |

| SW/TD 8 Digital input Switch control input or bitstream input  SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RESET/PWDN | 10     | Digital input  | Reset/power-down input                         |  |

| SWINN 17 Analog I/O Switch negative input  SWINP 20 Analog I/O Switch positive input  SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SCLK       | 2      | Digital input  | Serial port shift clock                        |  |

| SWINP 20 Analog I/O Switch positive input SWOUTN 18 Analog I/O Switch negative output SWOUTP 19 Analog I/O Switch positive output SYNC 9 Digital input Synchronize input VOUTN 16 Analog output Negative voltage output VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SW/TD      | 8      | Digital input  | Switch control input or bitstream input        |  |

| SWOUTN 18 Analog I/O Switch negative output  SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | SWINN      | 17     | Analog I/O     | Switch negative input                          |  |

| SWOUTP 19 Analog I/O Switch positive output  SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SWINP      | 20     | Analog I/O     | Switch positive input                          |  |

| SYNC 9 Digital input Synchronize input  VOUTN 16 Analog output Negative voltage output  VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SWOUTN     | 18     | Analog I/O     | Switch negative output                         |  |

| VOUTN 16 Analog output Negative voltage output VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SWOUTP     | 19     | Analog I/O     | Switch positive output                         |  |

| VOUTP 21 Analog output Positive voltage output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SYNC       | 9      | Digital input  | Synchronize input                              |  |

| 110111111111111111111111111111111111111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VOUTN      | 16     | Analog output  | Negative voltage output                        |  |

| VREF 12 Analog input Reference voltage input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VOUTP      | 21     | Analog output  | Positive voltage output                        |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | VREF       | 12     | Analog input   | Reference voltage input                        |  |

# 7 Specifications

# 7.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                                       | MIN        | MAX        | UNIT |

|---------------------------------------|------------|------------|------|

| AVDD to AVSS                          | -0.3       | +5.5       | V    |

| AVSS to DGND                          | -2.8       | +0.3       | V    |

| DVDD to DGND                          | -0.3       | +3.6       | V    |

| Input current continuous              | -10        | +10        | mA   |

| Analog input/output voltage           | AVSS - 0.3 | AVDD + 0.3 | V    |

| Switch current                        | -60        | +60        | mA   |

| Digital input voltage to DGND         | -0.3       | DVDD + 0.3 | V    |

| Operating temperature range           | -50        | +125       | °C   |

| Storage temperature, T <sub>stg</sub> | -60        | +150       | °C   |

<sup>(1)</sup> Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

# 7.2 ESD Ratings

|                    |               |                                                                     | VALUE | UNIT |

|--------------------|---------------|---------------------------------------------------------------------|-------|------|

| \/                 | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 7.3 Thermal Information

|                      | THERMAL METRIC <sup>(1)</sup>                |         | LINUT |

|----------------------|----------------------------------------------|---------|-------|

|                      | THERMAL METRIC                               | 24 PINS | UNIT  |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 78.3    |       |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 12.1    |       |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 33.8    | °C/W  |

| $\Psi_{JT}$          | Junction-to-top characterization parameter   | 0.3     | *C/VV |

| ΨЈВ                  | Junction-to-board characterization parameter | 33.5    |       |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A     |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 7.4 Electrical Characteristics

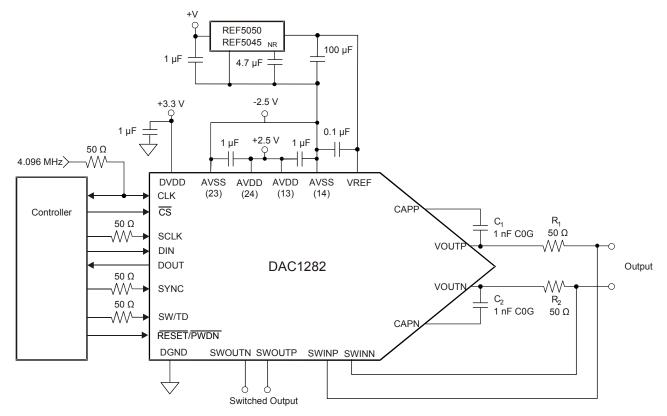

Minimum and maximum specifications are at  $T_A = -40$ °C to +85°C. Typical specifications are at  $T_A = +25$ °C, AVDD = +2.5 V, AVSS = -2.5 V,  $f_{CLK} = 4.096$  MHz,  $V_{REF} = 5$  V, and DVDD = 3.3 V (unless otherwise noted). Refer to Figure 50. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

|                   | PARAMETER                                |                  | TEST CONDITIONS        | MIN       | TYP                        | MAX                                    | UNIT                      |

|-------------------|------------------------------------------|------------------|------------------------|-----------|----------------------------|----------------------------------------|---------------------------|

| ANALO             | G OUTPUT (VOUTP, VOUTN)                  |                  |                        |           |                            | I                                      |                           |

|                   | Full-scale output voltage <sup>(1)</sup> |                  | Gain = 1/1 to 1/64     | ±         | V <sub>REF</sub> /2 × gain |                                        | V                         |

|                   | Output common-mode voltage               | e <sup>(2)</sup> |                        |           | -0.1                       |                                        | V                         |

|                   | Differential output impedance            | ,                |                        |           | 1.6                        |                                        | Ω                         |

| C <sub>LOAD</sub> | Capacitive load                          |                  |                        |           |                            | 2                                      | nF                        |

| R <sub>LOAD</sub> | Resistive load                           |                  |                        | 100       |                            |                                        | Ω                         |

|                   | Output current limit (3)                 |                  |                        |           | ±60                        |                                        | mA                        |

|                   |                                          |                  | T <sub>A</sub> = +25°C |           | 2                          |                                        |                           |

|                   | High-Z output leakage                    |                  | T <sub>A</sub> = +85°C |           | 50                         |                                        | nA                        |

| DC PER            | FORMANCE (Excluding Pulse Mode)          |                  |                        |           |                            |                                        |                           |

|                   | Gain error                               |                  | Gain = 1/1             |           | ±0.1%                      | ±0.75%                                 |                           |

|                   | Gain match                               |                  | Relative to gain = 1/1 |           | ±0.05%                     | ±0.5%                                  |                           |

|                   | Gain drift                               |                  |                        |           | 2                          |                                        | ppm/°C                    |

|                   | Offset                                   |                  | Gain = 1/1 to 1/64     |           | ±(7/gain) + 50             | ±(75/gain) +<br>300                    | ppm<br>FSR <sup>(4)</sup> |

|                   | Offset drift                             |                  |                        |           | 1.5                        |                                        | ppm<br>FSR/°C             |

| AC PER            | FORMANCE                                 |                  |                        |           |                            | <u>,</u>                               |                           |

|                   | ERFORMANCE                               |                  | Gain = 1/1             |           | -125                       | -118                                   | dB                        |

|                   |                                          |                  | Gain = 1/2, 1/4, 1/8   |           | -125                       |                                        | dB                        |

|                   |                                          | DAC1282          | Gain = 1/16            |           | -123                       |                                        | dB                        |

| THD               | Total harmonic distortion (5)            |                  | Gain = 1/32            |           | -115                       |                                        | dB                        |

|                   |                                          |                  | Gain = 1/64            |           | -111                       |                                        | dB                        |

|                   |                                          | DAC1282A         | Gain = 1/1             |           | -118                       | -106                                   | dB                        |

|                   |                                          | DAC1282A         | Gain = 1/4, 1/16       |           | -118                       | ±0.75%<br>±0.5%<br>±(75/gain) +<br>300 | dB                        |

|                   |                                          |                  | Gain = 1/1             | 116       | 120                        |                                        | dB                        |

|                   |                                          |                  | Gain = 1/2             |           | 119                        |                                        | dB                        |

|                   |                                          |                  | Gain = 1/4             |           | 117                        |                                        | dB                        |

| SNR               | Signal-to-noise ratio (6)                |                  | Gain = 1/8             |           | 114                        |                                        | dB                        |

|                   |                                          |                  | Gain = 1/16            |           | 110                        |                                        | dB                        |

|                   |                                          |                  | Gain = 1/32            |           | 106                        |                                        | dB                        |

|                   |                                          |                  | Gain = 1/64            |           | 100                        |                                        | dB                        |

|                   | Output frequency                         |                  |                        | 0.4883    |                            | 250                                    | Hz                        |

|                   | Digital gain                             |                  | 0.5-dB steps           | Full mute |                            | 0                                      | dB                        |

| PSR               | Downer ownels rejection                  | AVDD, AVSS       | 60 Hz ac gain 4/9      |           | 85                         |                                        | dB                        |

| PSK               | Power-supply rejection                   | DVDD             | 60-Hz ac, gain = 1/8   |           | 120                        |                                        | dB                        |

- (1) Full-scale differential output voltage:  $V_{OUT} = (VOUTP VOUTN) = \pm V_{REF}/2 \times Gain$ . Gain is the DAC analog gain.

- (2) Output common-mode voltage scales with analog supply voltage: V<sub>COM</sub> = 0.48 × (AVDD AVSS) + AVSS.

- (3) Sink or source current limit of VOUTP and VOUTN.

- (4) FSR full-scale range = V<sub>REF</sub> × gain.

- (5) THD = total harmonic distortion. THD is measured by the ADS1282, and is the sum of first nine harmonics using complementing gain. f<sub>OUT</sub> = 31.25 Hz, V<sub>OUT</sub> 0.5 dBFS, no load.

- (6) SNR = signal-to-noise ratio. SNR is measured by the ADS1282 over a 413-Hz bandwidth using complementing gain. f<sub>OUT</sub> = 31.25 Hz and V<sub>OUT</sub> 0.5 dBFS.

# **Electrical Characteristics (continued)**

Minimum and maximum specifications are at  $T_A = -40$ °C to +85°C. Typical specifications are at  $T_A = +25$ °C, AVDD = +2.5 V, AVSS = -2.5 V,  $f_{CLK}$  = 4.096 MHz,  $V_{REF}$  = 5 V, and DVDD = 3.3 V (unless otherwise noted). Refer to Figure 50. DAC1282A supports gains =  $\frac{1}{4}$   $\frac{1}{4}$  and  $\frac{1}{4}$  and

| PARAMETER                                         | TEST CONDITIONS                                       | MIN        | TYP                  | MAX         | UNIT              |

|---------------------------------------------------|-------------------------------------------------------|------------|----------------------|-------------|-------------------|

| PULSE MODE                                        |                                                       |            |                      | <u> </u>    |                   |

| Output levels                                     | 31 steps, approximate 3 dB per step                   | ±0.0195    |                      | ±2.5        | V                 |

| Gain error                                        |                                                       |            | ±0.1%                | ±0.75%      |                   |

| Gain drift                                        |                                                       |            | 3                    |             | ppm/°C            |

| Offset                                            |                                                       |            | ±0.5                 | ±3          | mV                |

| Offset drift                                      |                                                       |            | 3                    |             | μV/°C             |

| Output noise <sup>(7)</sup>                       |                                                       |            | 1.5                  |             | $\mu V_{RMS}$     |

| Slew rate                                         |                                                       |            | 5                    |             | V/µs              |

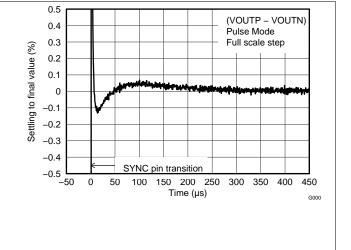

| Settling time                                     | 0.1% final value                                      |            | 25                   |             | μs                |

| DC MODE                                           | ,                                                     |            |                      | -           |                   |

| Resolution                                        |                                                       |            | 24                   |             | Bits              |

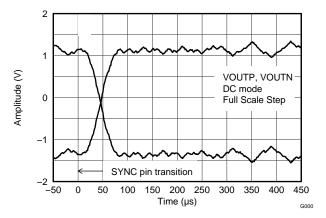

| Step response                                     |                                                       |            | 100                  |             | μs                |

|                                                   | Gain = 1/1                                            |            | 1.3                  |             | $\mu V_{RMS}$     |

|                                                   | Gain = 1/2                                            |            | 1.4                  |             | $\mu V_{RMS}$     |

|                                                   | Gain = 1/4                                            |            | 1.8                  |             | $\mu V_{RMS}$     |

| DC noise <sup>(8)</sup>                           | Gain = 1/8                                            |            | 2.7                  |             | $\mu V_{RMS}$     |

|                                                   | Gain = 1/16                                           |            | 4.7                  |             | μV <sub>RMS</sub> |

|                                                   | Gain = 1/32                                           |            | 8.5                  |             | μV <sub>RMS</sub> |

|                                                   | Gain = 1/64                                           |            | 16                   |             | $\mu V_{RMS}$     |

| DIGITAL DATA MODE                                 |                                                       |            |                      | 1           |                   |

| Data clock rate                                   |                                                       |            | f <sub>CLK</sub> /16 |             | Hz                |

| Ones-density full-scale modulation                | +FS and -FS, respectively                             | 25%        | -                    | 75%         |                   |

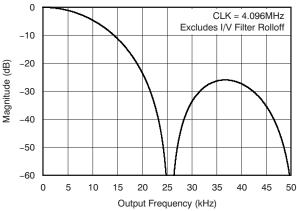

| Signal bandwidth                                  | -3 dB                                                 |            | 8.2                  |             | kHz               |

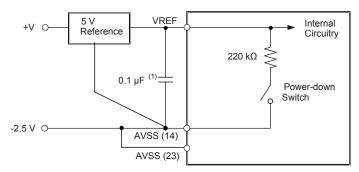

| REFERENCE VOLTAGE INPUT (V <sub>REF</sub> )       |                                                       |            |                      | 1           |                   |

| Reference voltage, V <sub>REF</sub> = VREF – AVSS |                                                       | 2.4        | 5                    | AVDD + 0.25 | V                 |

|                                                   | Operating                                             |            | 220                  |             | kΩ                |

| Reference input impedance                         | Power-down                                            |            | 10                   |             | ΜΩ                |

| SIGNAL SWITCH                                     |                                                       |            |                      | 1           |                   |

| Signal range                                      |                                                       | AVSS       |                      | AVDD        | V                 |

| Current                                           | Continuous                                            |            |                      | ±50         | mA                |

| Differential on-resistance                        | V <sub>SWIN</sub> , V <sub>SWOUT</sub> = 0 V          |            | 2.8                  |             | Ω                 |

| Differential on-resistance flatness               | V <sub>SWIN</sub> , V <sub>SWOUT</sub> = AVDD to AVSS |            | 0.7                  |             | Ω                 |

| On-resistance match between outputs               | V <sub>SWIN</sub> , V <sub>SWOUT</sub> = 0 V          |            | 0.04                 |             | Ω                 |

|                                                   | T <sub>A</sub> = +25°C                                |            | ±0.1                 |             |                   |

| Off-leakage current <sup>(9)</sup>                | T <sub>A</sub> = +85°C                                |            | ±5                   |             | nA                |

| Off-isolation <sup>(10)</sup>                     |                                                       |            | 120                  |             | dB                |

| DIGITAL INPUT/OUTPUT (DVDD = 1.65 V to 3.6 V)     |                                                       |            |                      |             |                   |

| V <sub>OH</sub>                                   | I <sub>OH</sub> = 1 mA                                | 0.8 × DVDD |                      |             | V                 |

| V <sub>OL</sub>                                   | I <sub>OL</sub> = 1 mA                                |            |                      | 0.2 × DVDD  | V                 |

| V <sub>IH</sub>                                   | 3.                                                    | 0.8 × DVDD |                      | DVDD        | V                 |

| V <sub>IL</sub>                                   |                                                       | DGND       |                      | 0.2 × DVDD  | V                 |

| Input hysteresis                                  |                                                       |            | 0.5                  | 2           | V                 |

| Input leakage                                     |                                                       |            |                      | ±10         | μA                |

|                                                   |                                                       | 1          | 4.096                | 4.225       | MHz               |

$V_{OUT} = 0$  V. Pulse mode output noise is measured by the ADS1282, over a 413-Hz bandwidth using ADC gain = 1.  $V_{OUT} = 0$  V. DC noise is measured by the ADS1282, over a 413-Hz bandwidth using complementing gain. DC noise is referred to a 1.77-V full-scale ADC output. Divide output-referred noise by the ADC gain to yield input-referred noise. Switch input or output voltage = AVDD – 0.5 V to AVSS + 0.5 V.

<sup>(10)</sup> f = 31.25 Hz, 1.77  $V_{RMS}$ . Switch output loaded 2 x 10  $k\Omega$  to mid-supply range.

# **Electrical Characteristics (continued)**

Minimum and maximum specifications are at  $T_A = -40$ °C to +85°C. Typical specifications are at  $T_A = +25$ °C, AVDD = +2.5 V, AVSS = -2.5 V,  $f_{CLK}$  = 4.096 MHz,  $V_{REF}$  = 5 V, and DVDD = 3.3 V (unless otherwise noted). Refer to Figure 50. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

| PARAMETER                   | TEST CONDITIONS                    | MIN         | TYP | MAX         | UNIT               |

|-----------------------------|------------------------------------|-------------|-----|-------------|--------------------|

| POWER SUPPLY                |                                    |             |     |             |                    |

| AVSS                        |                                    | -2.6        |     | 0           | V                  |

| AVDD                        |                                    | AVSS + 4.75 |     | AVSS + 5.25 | V                  |

| DVDD                        |                                    | 1.65        |     | 3.6         | V                  |

|                             | Gain = 1/1, V <sub>OUT</sub> = 0 V |             | 7.4 | 8.5         | mA <sup>(11)</sup> |

| AVDD, AVSS current          | Pulse mode, V <sub>OUT</sub> = 0 V |             | 7   |             | mA                 |

|                             | Shutdown                           |             | 1   | 10          | μΑ                 |

| DVDD                        | Operating                          |             | 180 | 300         | μΑ                 |

| DVDD current                | Shutdown <sup>(12)</sup>           |             | 1   | 10          | μΑ                 |

| Dawe                        | Operating                          |             | 38  | 44          | mW                 |

| Power                       | Shutdown <sup>(12)</sup>           |             | 10  | 85          | μW                 |

| TEMPERATURE RANGE           |                                    |             |     | ·           |                    |

| Specified temperature range |                                    | -40         |     | +85         | °C                 |

| Operating temperature range |                                    | -50         |     | +125        | °C                 |

| Storage temperature range   |                                    | -65         |     | +150        | °C                 |

<sup>(11)</sup> Analog supply current scales with gain as follows:

$I_{AVDD}$  and  $I_{AVSS} = 0.016 \times V_{REF} \times (44 \times Gain + 1) + 3.8$  (mA). (12) Digital inputs stopped and maintained at  $V_{IH}$  or  $V_{IL}$  level.

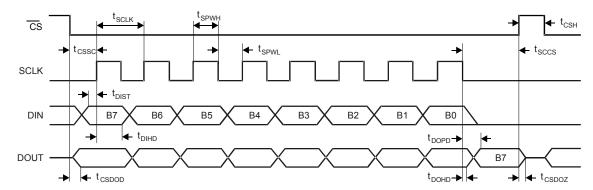

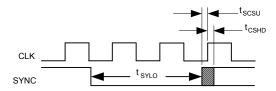

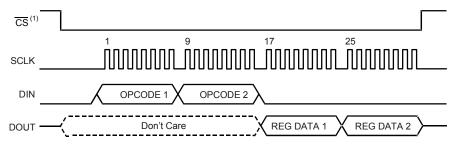

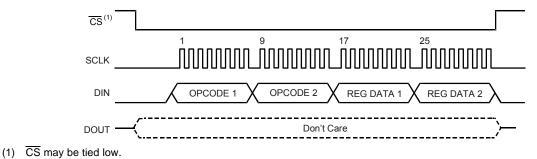

# 7.5 Timing Requirements: Serial Peripheral Interface (SPI) Timing

At  $T_A = -40$ °C to +85°C and DVDD = 1.65 V to 3.6 V, unless otherwise noted.

|                    |                                                              | MIN N | АХ              | UNIT             |

|--------------------|--------------------------------------------------------------|-------|-----------------|------------------|

| tcssc              | CS low to first SCLK: setup time <sup>(1)</sup>              | 30    |                 | ns               |

| t <sub>SCLK</sub>  | SCLK period                                                  | 120   |                 | ns               |

| t <sub>SPWH</sub>  | SCLK pulse width: high                                       | 50    |                 | ns               |

|                    | SCLK pulse width: low <sup>(2)</sup>                         | 50    |                 | ns               |

| t <sub>SPWL</sub>  | SCLK pulse width: low (-)                                    |       | 2 <sup>18</sup> | t <sub>CLK</sub> |

| t <sub>DIST</sub>  | Valid DIN to SCLK high: setup time                           | 40    |                 | ns               |

| t <sub>DIHD</sub>  | Valid DIN to SCLK high: hold time                            | 20    |                 | ns               |

| t <sub>DOPD</sub>  | SCLK low to valid new DOUT: propagation delay <sup>(3)</sup> |       | 40              | ns               |

| t <sub>DOHD</sub>  | SCLK low to DOUT invalid: hold time                          |       | 0               | ns               |

| t <sub>CSDOD</sub> | CS low to DOUT driven: propagation delay <sup>(3)</sup>      |       | 40              | ns               |

| t <sub>CSDOZ</sub> | CS high to DOUT Hi-Z: propagation delay                      |       | 20              | ns               |

| t <sub>CSH</sub>   | CS high pulse                                                | 50    |                 | ns               |

| t <sub>SCCS</sub>  | Last SCLK falling edge to CS high                            | 0     |                 | ns               |

- $\overline{\text{CS}}$  can be tied low. Holding SCLK low longer than 2<sup>18</sup> f<sub>CLK</sub> cycles resets the SPI interface. DOUT load = 20 pF || 100 k $\Omega$  to DGND.

Figure 1. Serial Interface Timing

# 7.6 Typical Characteristics

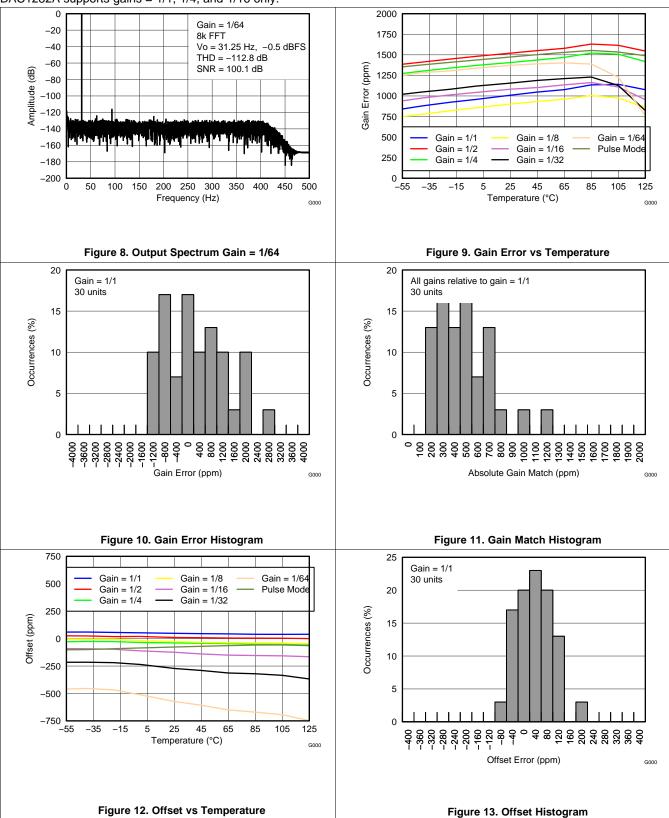

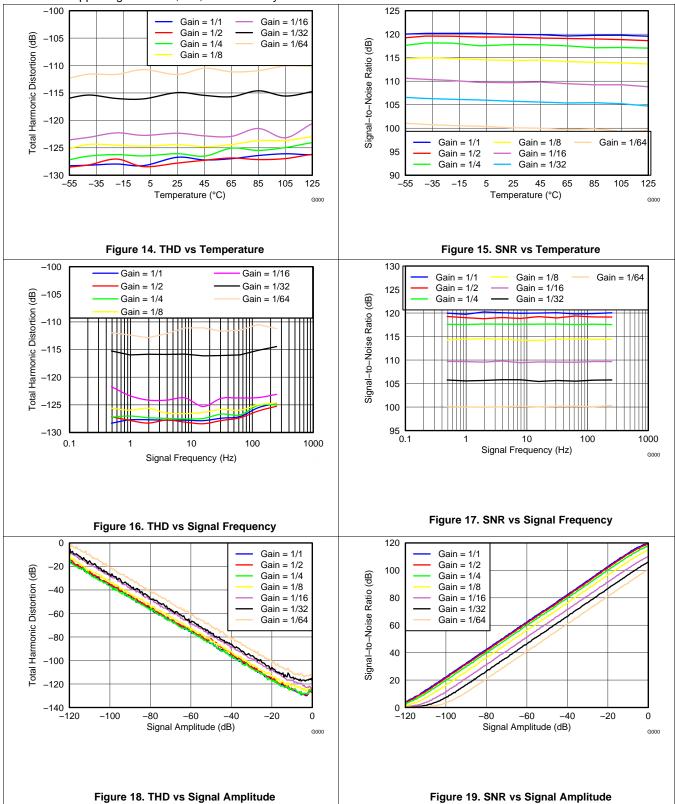

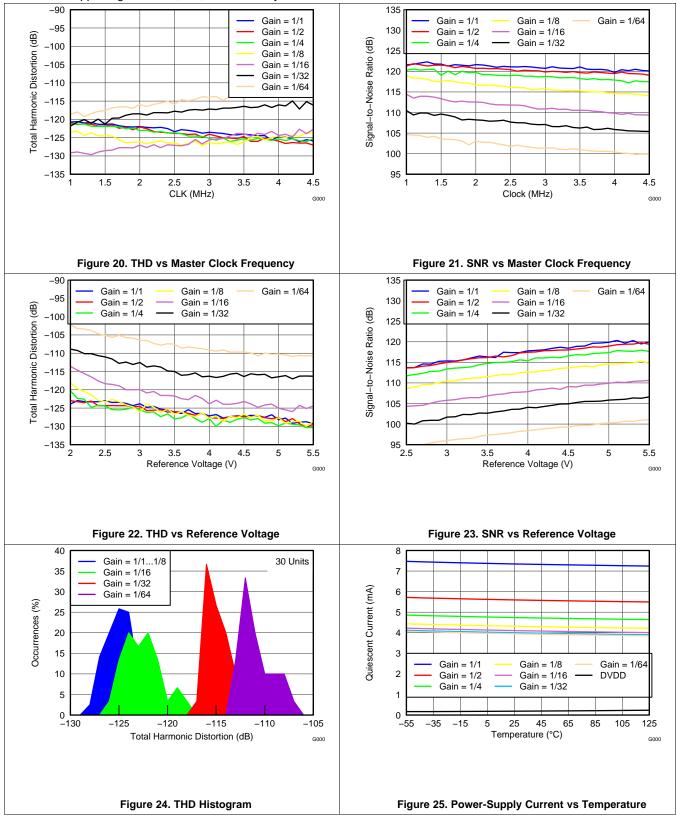

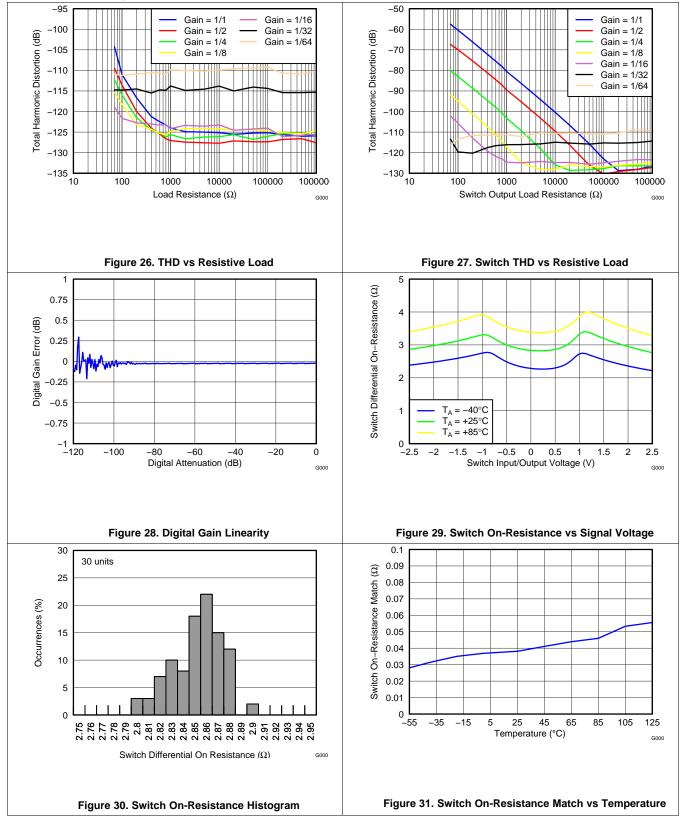

At  $T_A$  = +25°C, AVDD = +2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK}$  = 4.096 MHz, and  $V_{REF}$  = 5 V, unless otherwise noted. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

At  $T_A$  = +25°C, AVDD = +2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK}$  = 4.096 MHz, and  $V_{REF}$  = 5 V, unless otherwise noted. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

Submit Documentation Feedback

Copyright © 2011–2015, Texas Instruments Incorporated

At  $T_A$  = +25°C, AVDD = +2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK}$  = 4.096 MHz, and  $V_{REF}$  = 5 V, unless otherwise noted. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

At  $T_A$  = +25°C, AVDD = +2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK}$  = 4.096 MHz, and  $V_{REF}$  = 5 V, unless otherwise noted. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

Submit Documentation Feedback

Copyright © 2011–2015, Texas Instruments Incorporated

At  $T_A$  = +25°C, AVDD = +2.5 V, AVSS = -2.5 V, DVDD = 3.3 V,  $f_{CLK}$  = 4.096 MHz, and  $V_{REF}$  = 5 V, unless otherwise noted. DAC1282A supports gains = 1/1, 1/4, and 1/16 only.

# 8 Detailed Description

#### 8.1 Overview

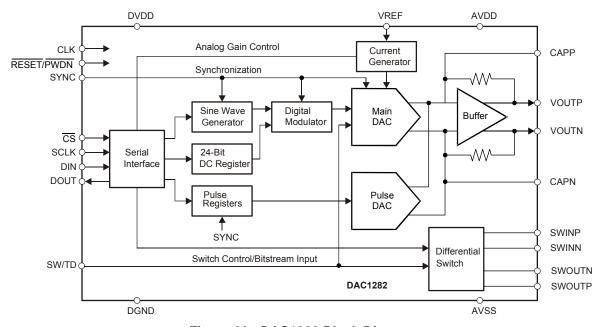

The DAC1282 is a single-chip, digital-to-analog converter (DAC) that self-generates low-distortion sine-wave and pulse-output signals for the demanding testing requirements of seismic recording equipment. Figure 32 shows the block diagram of the DAC1282.

The DAC1282A device is functionally equivalent to the DAC1282, except that the DAC1282A supports PGA gains of 1/1, 1/4, and 1/16 only. The DAC1282A also relaxes the THD specification of these gains. See the *Electrical Characteristics* section for more details.

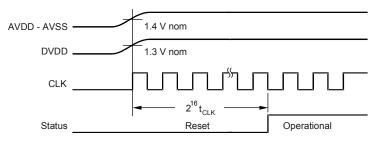

The DAC1282 requires two supply voltages: analog and digital. The analog supply can be single 5 V or bipolar ±2.5 V. The digital supply range is 1.65 V to 3.6V. The output signal common-mode voltage is regulated to 100 mV below the midpoint of the analog power-supply voltage. An internal power-on reset (POR) circuit resets the DAC on power-up.

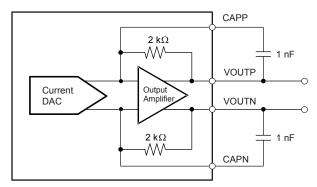

An SPI<sup>TM</sup>-compatible serial interface is used to access the DAC1282 registers for device configuration and control. The configuration registers can be read back by clocking the data out on the DOUT pin. The DAC1282 voltage output is fully differential and is taken out on the VOUTP/VOUTN pins. The CAPP/CAPN pins connect to external filter capacitors to reduce the output noise.

The reference input voltage sets the DAC1282 full-scale output. The DAC reference voltage is applied between the VREF and AVSS pins. The DAC is optimized to operate with a 5-V reference. The sine-wave generator is programmable by registers to set the sine frequency and amplitude. The frequency range is programmable from 0.4883 Hz to 250 Hz. The output level is controlled by both analog gain (in 6-dB steps), and digital gain (in 0.5-dB steps).

Figure 32. DAC1282 Block Diagram

The digital modulator takes the output from the sine-wave generator or the 24-bit dc register to generate the ones-density bitstream. The bitstream drives the main DAC. Optionally, ones-density data can be input to drive the DAC directly, bypasses the digital signal generator. The main DAC develops a differential output current that is converted to a differential output voltage by an internal current-to-voltage (I/V) amplifier. The output range is set by analog gain that scales the DAC current generator. The output amplifier provides current limit protection.

The dc mode is programmed by a 24-bit register and is used to provide a dc output. The dc mode also has programmable ranges controlled by the analog gain control.

## **Overview (continued)**

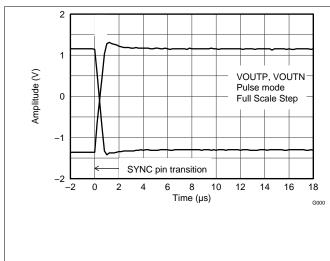

In Pulse mode, a fast-response, 5-bit pulse DAC is used to provide 31 preset dc levels. The levels span over the available output ranges. The pulse DAC is optimized to provide fast response with short output rise times. The pulse DAC is triggered by the SYNC pin for precision control of the pulse time.

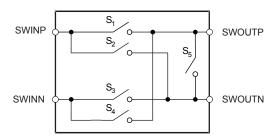

The DAC1282 includes a low distortion differential output switch. The output switch can connect the DAC1282 output to sensors for THD and impulse testing. The switch is controlled by either pin or command, thus allowing precise switch timing.

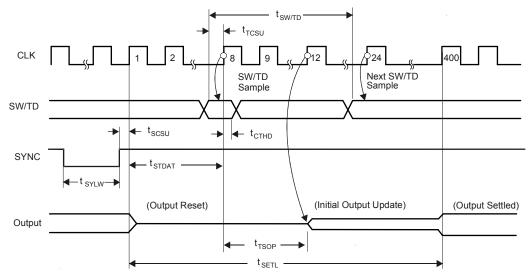

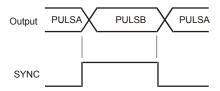

The SYNC input synchronizes the output signal to a known time reference. In sine mode, SYNC resets the sine wave to the zero crossing. In Pulse mode, SYNC selects one of two user-programmed dc levels.

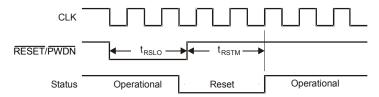

The RESET/PWDN pin powers down the device when low. When RESET/PWDN is released high, the DAC1282 is reset.

The SW/TD input is dual function. In digital data mode, the pin is the ones-density data input. In the other modes, SW/TD controls the opening/closing of the switch.

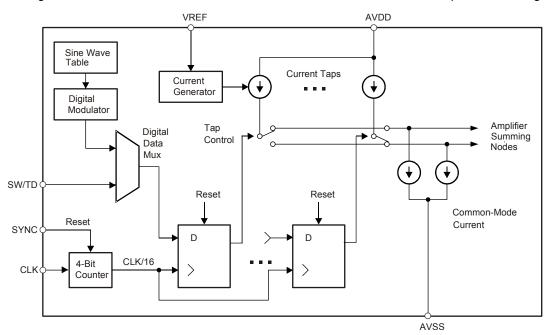

Figure 33 shows the main details of the main DAC. The main DAC provides the digital-to-analog conversion by filtering the ones-density digital data. In operation, the current generator establishes the range current that is mirrored to a multi-tap, current-steering filter stage. The current generator is controlled by the analog gain control register that scales the weight of the tap currents to one of seven ranges (0 dB to –36 dB).

The current-steering stage switches the tap currents to the positive or negative current summing nodes, as the digital input is sampled. A higher ones-density directs an increasing average current to one node than the other, thus increasing the differential current. The differential current is converted to differential voltage by the internal I/V converter stage. The common-mode current sources balance the current at the amplifier summing node.

Figure 33. Main DAC Block Diagram

### 8.2 Feature Description

# 8.2.1 Signal Output (VOUTP, VOUTN)

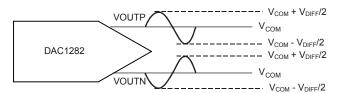

As shown in Figure 34, the DAC provides a differential voltage ( $V_{DIFF} = VOUTP - VOUTN$ ) on pins VOUTP and VOUTN. The output common-mode voltage ( $V_{COM}$ ) is regulated to 100 mV below the midpoint of the analog supply (AVDD – AVSS).

Each signal output swings above and below the common-mode voltage. Best performance is realized when the DAC output is used differentially. In power-down mode, the outputs enter a high-impedance, 3-state mode.

NOTE:  $V_{DIFF} = VOUTP - VOUTN = \pm 2.5 \text{ V} \times \text{Gain} (V_{REF} = 5 \text{ V}).$  $V_{COM} = -0.1 \text{ V} (\pm 2.5 \text{-V supplies}) \text{ or } 2.4 \text{ V} (5 \text{-V supply}).$

Figure 34. DAC Output Signal

The DAC output buffer is rated to drive up to a 2-nF capacitive load (maximum) and a  $100-\Omega$  resistive load (minimum). However, degradation of THD performance results in resistive loads less than 1 k $\Omega$ , as shown in Figure 26

The internal digital modulator generates the signal to drive the DAC. The modulator shapes the in-band noise to high frequency and the frequency-shaped noise is present on the DAC output. However, the high frequency DAC output noise is rejected by the digital filter of the ADC and does not affect system performance.

The DAC sampling update noise is also present on the signal output. The sampling noise does not affect the ADC performance, but when testing the ADC near full-scale input, the noise can cause false indication of the ADC modulator overrange detection. The ADS1282 overrange output signal indication should be ignored when testing at or below the ADC full-scale input.

# **Feature Description (continued)**

#### 8.2.2 DAC Modes

The DAC1282 has four operational modes of: sine, dc, pulse, and external digital data input. These modes are programmed by the MODE[1:0] bits in the GANMOD register, as shown in Table 1.

**Table 1. DAC Modes**

| MODE[1:0] BITS | DAC MODE     |

|----------------|--------------|

| 00             | Sine         |

| 01             | DC           |

| 10             | Digital data |

| 11             | Pulse        |

#### 8.2.2.1 Sine Mode

In sine mode, the DAC1282 provides a sine-wave output. An internal signal generator develops the sine-wave signal. The M[3:0], N[7:0], and FREQ register bits program the output frequency. The frequency range is programmable from 0.4883 Hz to 250 Hz, as shown in Equation 1.

Output Frequency (Hz)

$$^{(1)} = \frac{250}{2^{FREQ}} \times \frac{M[3:0] + 1}{N[7:0] + 1}$$

where:

$M[3:0] \le N[7:0]$

Table 2 lists values of registers M and N for selected output frequencies.

**Table 2. Register Output Frequencies**

| SIGNAL FREQUENCY (Hz) <sup>(1)</sup> | M[3:0] REGISTER BITS | N[7:0] REGISTER BITS | FREQ BIT |

|--------------------------------------|----------------------|----------------------|----------|

| 0.48828125                           | 0000                 | 1111 1111            | 1        |

| 0.9765625                            | 0000                 | 1111 1111            | 0        |

| 1.953125                             | 0000                 | 0111 1111            | 0        |

| 3.90625                              | 0000                 | 0011 1111            | 0        |

| 7.8125                               | 0000                 | 0001 1111            | 0        |

| 15.625                               | 0000                 | 0000 1111            | 0        |

| 31.25                                | 0000                 | 0000 0111            | 0        |

| 50                                   | 0000                 | 0000 0100            | 0        |

| 55                                   | 1010                 | 0011 0001            | 0        |

| 60                                   | 0101                 | 0001 1000            | 0        |

| 62.5                                 | 0000                 | 0000 0011            | 0        |

| 100                                  | 1001                 | 0001 1000            | 0        |

| 125                                  | 0000                 | 0000 0001            | 0        |

| 250                                  | 0000                 | 0000 0000            | 0        |

<sup>(1)</sup>  $f_{CLK} = 4.096MHz$ . The signal frequency scales with  $f_{CLK}$ .

When the M or N registers are updated, the sine wave resets to the zero-crossing point. The sine wave can also be reset to the zero-crossing point by taking the SYNC pin high; see the SYNC section.

The amplitude of the sine-wave output is determined by analog and digital gains. The analog gain increments are 6 dB, from 0 dB to -36 dB, and are programmed by the GAIN[2:0] register bits. Table 3 lists the analog gains.

**Table 3. Analog Gain**

| ANALOG GAIN (V/V) <sup>(1)</sup> | ANALOG GAIN (dB) <sup>(2)</sup> | DIFFERENTIAL RANGE (V) <sup>(3)</sup> | GAIN[2:0] REGISTER BITS |

|----------------------------------|---------------------------------|---------------------------------------|-------------------------|

| 1/1                              | 0                               | ±2.5                                  | 000                     |

| 1/2                              | -6                              | ±1.25                                 | 001                     |

| 1/4                              | -12                             | ±0.625                                | 010                     |

| 1/8                              | -18                             | ±0.312                                | 011                     |

| 1/16                             | -24                             | ±0.156                                | 100                     |

| 1/32                             | -30                             | ±0.078                                | 101                     |

| 1/64                             | -36                             | ±0.039                                | 110                     |

- (1) The DAC1282A supports analog gains of 1/1, 1/4, and 1/16 only.

- Relative to 1.77  $V_{RMS}$  full-scale.  $V_{REF} = 5 V$ , digital gain = 0 dB.

- (3)

The digital gain resolution is in 0.5-dB increments, from 0 dB to full mute and is programmed by the SINEG[7:0] register bits. Table 4 lists the digital gain setting. Equation 2 is the amplitude setting in sine mode.

Sine Amplitude (dB) = Analog Gain (dB) + Digital Gain (dB)

(2)

Best SNR, for a given signal level, is achieved by reducing the analog gain while maximizing the digital gain.

Table 4. Sine Mode Digital Gain