# **DAPDNA-2**

# **Dynamically Reconfigurable Processor**

ww.DataSheet4U.com

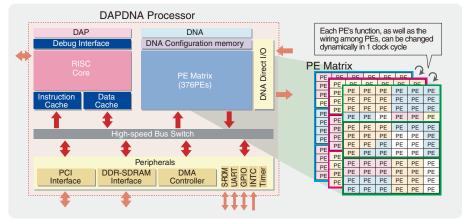

# DAPDNA<sup>®</sup> Architecture

The **DAPDNA Dynamically Reconfigurable Processor** is configurable during run-time to instantly (in one clock) provide the optimal hardware circuitry for application in demand.

The DAPDNA has a dual-core architecture, comprised of a RISC core (the DAP) and a dynamically reconfigurable matrix (the DNA).

This platform provides the processing performance of hardware with the flexibility of software.

### **DAP (Digital Application Processor)**

- High-performance RISC processor

- Controls the dynamic reconfiguration of the DNA

#### **DNA (Distributed Network Architecture)**

- Dynamically reconfigurable

- Two-dimensional array of 376 Processing Elements (PEs)

- Allows arbitrary configuration of the degree of parallelism and pipeline depth

Fig.1 DAPDNA Architecture

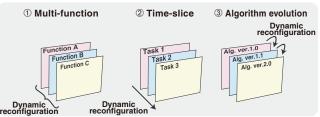

# Dynamic Reconfiguration

The DAPDNA-2's dynamic reconfiguration enables three beneficial usage models.

Fig.2 Dynamic Reconfiguration usage

#### ① Multi-function

- Function can be selected and executed according to changes in operating conditions (e.g.different encoding methods in incoming data)

- 2 Time-slice

- Algorithms can be partitioned in time

- As soon as one processing task is completed, the hardware immediately moves on to the next task

#### **3 Algorithm evolution**

As algorithm evolves with time (as in the case of virus definition for firewall), change is incorporated dynamically into hardware

# DNA Direct I/O

The DAPDNA-2 has six channels of DNA Direct I/O,which provides the interface for transfering data directly onto or out of the PE Matrix.

Each channel of DNA Direct I/O is 32-bit wide and operates at the maximum DAPDNA-2 system clock frequency of 166 MHz, reaching 32 Gbps. The DNA Direct I/O can operate synchronously on the system clock, or can be controlled by an external clock at a different frequency.

Multiple DAPDNA-2 processors can be connected through the DNA Direct I/O and integrated into a single system at 16 Gbps throughput.

The DNA Direct I/O can be also used to communicate directly with external devices, bringing data in for processing on the PE Matrix, bypassing the Bus Switch and memory interface.

# Guaranteed Clock Speed

The DAPDNA-2's unique architecture guarantees clock speed regardless of resource usage. Simulation result matches hardware performance accurately, eliminating the time-consuming process of design iteration. This feature reduces the system development time considerably.

# Large On-chip RAM

Large on-chip memory reduces the need to access off-chip memory, a process which often becomes a performance bottleneck. This feature allows the PE Matrix to provide the maximum possible parallel processing performance.

· IPFlex, DAPDNA and Software to Siliconre registered trademarks of IPFlex Inc. in Japan.

IPFlex Inc. Sun Felista Meguro 6F, 2-27-1, kamiosaki, Shinagawa-ku, Tokyo, 141-0021, Japan FLEX: Tel. +81-3-5436-3633 Fax +81-3-5436-3862 http://www.ipflex.com/

# FUJITSU MICROELECTRONICS LIMITED

North and South America FUJITSU MICROELECTRONICS AMERICA, INC. 1250 E. Arques Avenue, M/S 333 Sunnyvale, CA 94085-5401, U.S.A. Tel: +1-408-737-5600 Fax: +1-408-737-5999 http://www.fma.fujitsu.com/

#### Asia Pacific

FUJITSU MICROELECTRONICS ASIA PTE LTD. 151 Lorong Chuan, #05-08 New Tech Park Singapore 556741 Tel:+65-6281-0770 Fax:+65-6281-0220 http://www.fujitsu.com/sg/services/micro/semiconductor/ Europe FUJITSU MICROELECTRONICS EUROPE GmbH Pittlerstrasse 47, 63225 Langen, Germany Tel: +49-6103-690-0 Fax: +49-6103-690-122

http://emea.fujitsu.com/microelectronics/

FUJITSU MICROELECTRONICS SHANGHAI CO., LTD. Rm. 3102, Bund Center, No.222 Yan An Road (E), Shanghai 200002, China Tel : +86-21-6335-1560 Fax : +86-21-6335-1605 http://cn.fujitsu.com/fmc

# **DAPDNA-2** Processing Elements (PEs)

| PE    | Quantity | Function                                                                                    |

|-------|----------|---------------------------------------------------------------------------------------------|

| EXE   | 168      | 32-bit, 2 input 1 output execution<br>Includes 56 multipliers (16-bit input, 32-bit output) |

| RAM   | 32       | Internal memory, 16KB each, total 512KB                                                     |

| DLE   | 136      | 32-bit, 2 input 2 output delay<br>Configurable delay length                                 |

| CxE   | 24       | Address generation<br>Generic counter                                                       |

| LDx   | 8        | Data input into DNA                                                                         |

| STx   | 8        | Data output from DNA                                                                        |

| Total | 376      |                                                                                             |

#### **DAPDNA-2 Specification**

| DAP                    |                          | 32-bit RISC processor                                                                                                                                                       |

|------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                        |                          | 8 KB instruction cache, 8 KB data cache                                                                                                                                     |

| DNA                    |                          | Two-dimensional array of dynamically reconfigurable PEs (376PEs)                                                                                                            |

|                        | Number of configurations | Four banks (one foreground bank, three background banks,<br>Background banks can be loaded from external memory for<br>unlimited number of configurations to be used.)      |

| External<br>interfaces | DNA Direct I/O           | 166 MHz maximum (can be synchronized to external dock)<br>32-bit width<br>6 I/O channels : up to 32 Gbps bandwidth<br>(Can be used to connect multiple DAPDNA-2 processors) |

|                        | DDR-SDRAM                | 166 MHz, 64 bit DDR-SDRAM interface<br>Supports up to 512 MB                                                                                                                |

|                        | PCI                      | 33 MHz, 32-bit PCI interface (3.3 V tolerant)                                                                                                                               |

|                        | ROM                      | SPI serial ROM interface for boot or program storage                                                                                                                        |

|                        | External interrupts      | 8                                                                                                                                                                           |

|                        | Others                   | 2 UART channels<br>16 GPIO channels<br>1 synchronous serial (master) channel                                                                                                |

| Operating frequency    |                          | 166MHz                                                                                                                                                                      |

| Power supply           |                          | 2.5 V (I/O)<br>1.2 V (core)                                                                                                                                                 |

| Package                |                          | 1156-pin FC-BGA                                                                                                                                                             |

Shinjuku Dai-Ichi Seimei Bldg. 7-1, Nishishinjuku 2-chome, Shinjuku-ku, Tokyo 163-0722, Japan Tel: +81-3-5322-3329 Fax: +81-3-5322-3387 Tokyo 163-0722, Japan http://jp.fujitsu.com/fml/en/

> FUJITSU MICROELECTRONICS KOREA LID. 206 KOSMO TOWER, 1002 Daechi-Dong, Kangnam-Gu,Seoul 135-280 Korea Tel: +82-2-3484-7100 Fax: +82-2-3484-7111 http://www.fmk.fujitsu.com/

FUJITSU MICROELECTRONICS PACIFIC ASIA LTD. 10/F., World Commerce Centre, 11 Canton Road Tsimshatsui, Kowloon Hong Kong http://cn.fujitsu.com/fmc/tw

Specifications are subject to change without notice. For further information please contact each office.

#### All Rights Reserved.

All Rights Reserved. The contents of this document are subject to change without notice. Customers are advised to consult with sales representatives before ordering. The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of FULITSU MICROELECTRONICS device; FULITSU MICROELECTRONICS does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. FUJITSU MICROELECTRONICS assumes no liability for any damages whatsoever arising out of the use of the information. Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of FUJITSU MICROELECTRONICS or any third party or does FUJITSU MICROELECTRONICS warrant non-infringement of any third-party's intellectual property right or other right by using such information, contained herein. The products described in this document, to designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial setability. Please note that FUJITSU MICROELECTRONICS will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the

Please note that FUUITSU MICHOELECTRUMICS will not be have against you and/or any tank party or any tany tank party or a

©2005-2008 FUJITSU MICROELECTRONICS LIMITED Printed in Japan AD06-00015-3Ea June 2005 Edited: Strategic Business Development Dept.