# **DFPSQRT**

# Floating Point Pipelined Square Root Unit ver 2.90

# OVERVIEW

The DFPSQRT uses the **pipelined** mathematics algorithm to compute square root function. The input number format is according to IEEE-754 standard. DFPSQRT supports single precision real numbers. SQRT operation can be pipelined up to 9 levels. Input data are fed every clock cycle. The first result appears after 9 clock periods latency and next results are available **each clock** cycle. Precision and accuracy are parameterized.

### APPLICATION

- Math coprocessors

- DSP algorithms

- Embedded arithmetic coprocessor

- Data processing & control

# **KEY FEATURES**

- Full IEEE-754 compliance

- Single precision real format support

- Simple interface

- No programming required

- 9 levels pipelining

- 24-bit accuracy, 6 fractional decimal digits

- Results available at every clock

- Fully configurable

All trademarks mentioned in this document are trademarks of their respective owners.

Fully synthesizable, static synchronous design with no internal tri-states

## DELIVERABLES

- Source code:

- ♦ VHDL Source Code or/and

- ♦ VERILOG Source Code or/and

- ♦ Encrypted, or plain text EDIF netlist

- VHDL & VERILOG test bench environment

- Active-HDL automatic simulation macros

- ModelSim automatic simulation macros

- NCSim automatic simulation macros

- Tests with reference responses

- Technical documentation

- Installation notesHDL core specification

- ♦ Datasheet

- Synthesis scripts

- Example application

- Technical support

- ◊ IP Core implementation support

- 3 months maintenance

- Delivery the IP Core updates, minor and major versions changes

- Delivery the documentation updates

- Phone & email support

### LICENSING

Comprehensible and clearly defined licensing methods without royalty fees make using of IP Core easy and simply.

<u>Single Design</u> license allows using IP Core in single FPGA bitstream and ASIC implemen-

http://www.DigitalCoreDesign.com http://www.dcd.pl tation. It also permits FPGA prototyping before ASIC production.

<u>Unlimited Designs</u> license allows using IP Core in unlimited number of FPGA bitstreams and ASIC implementations.

In all cases number of IP Core instantiations within a design, and number of manufactured chips are unlimited. There is no time of use limitations.

- Single Design license for

- VHDL, Verilog source code called <u>HDL</u>

Source

- <sup>⊱om</sup>Encrypted, or plain text EDIF called <u>Netlist</u>

- Unlimited Designs license for

- o HDL Source

- Netlist

- Upgrade from

- Netlist to HDL Source

- Single Design to Unlimited Designs

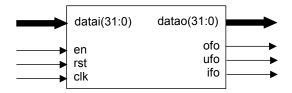

# SYMBOL

# PINS DESCRIPTION

| PIN         | TYPE   | DESCRIPTION         |  |  |

|-------------|--------|---------------------|--|--|

| clk         | Input  | Global system clock |  |  |

| rst         | Input  | Global system reset |  |  |

| en          | Input  | Enable computing    |  |  |

| datai[31:0] | Input  | Data bus input      |  |  |

| datao[31:0] | Output | Data bus output     |  |  |

| ofo         | Output | Overflow flag       |  |  |

| ufo         | Output | Underflow flag      |  |  |

| ifo         | Output | Invalid result flag |  |  |

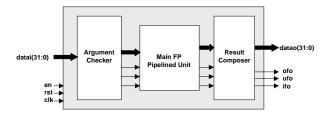

# **BLOCK DIAGRAM**

Arguments Checker - performs input data analyze against IEEE-754 number standard compliance. The appropriate numbers and information about the input data classes are given as the results to Main FP Pipelined Unit.

**Main FP Pipelined Unit** - performs floating point square root function. Gives the complex information about the results to Result Composer module.

**Result Composer** - performs result rounding function, data alignment to IEEE-754 standard, and the final flags setting.

# PERFORMANCE

The following table gives a survey about the Core area and performance in the ALTERA® devices after Place & Route:

| Device     | Speed grade | Logic Cells | F <sub>max</sub> |

|------------|-------------|-------------|------------------|

| FLEX10KE   | -1          | 1000        | 48 MHz           |

| ACEX1K     | -1          | 1000        | 48 MHz           |

| APEX20K    | -1          | 970         | 50 MHz           |

| APEX20KE   | -1          | 970         | 53 MHz           |

| APEX20KC   | -7          | 970         | 62 MHz           |

| APEX-II    | -7          | 970         | 83 MHz           |

| MERCURY    | -5          | 975         | 99 MHz           |

| STRATIX    | -5          | 725         | 96 MHz           |

| CYCLONE    | -6          | 725         | 94 MHz           |

| STRATIX-II | -3          | 890         | 131 MHz          |

| CYCLONE-II | -6          | 730         | 99 MHz           |

Core performance in ALTERA® devices

# CONTACTS

For any modification or special request please contact to Digital Core Design or local distributors.

# **Headquarters:**

Wroclawska 94

41-902 Bytom, POLAND

e-mail: info@dcd.pl

tel. : +48 32 282 82 66 fax : +48 32 282 74 37

#### **Distributors:**

Please check http://www.dcd.pl/apartn.php