**DLPR910**

DLPS065C - SEPTEMBER 2015-REVISED DECEMBER 2019

# **DLPR910 Configuration PROM**

#### **Features**

- Pre-Programmed Xilinx® PROM Configures the **DLPC910 DMD Digital Controller**

- I/O Pins Compatible With 1.8 V to 3.3 V

- 1.8 V Core Supply Voltage

- -40°C to 85°C Operating Temperature Range

# **Applications**

- Lithography

- Direct Imaging

- Flat Panel Display

- Printed Circuit Board Manufacturing

- Industrial

- 3D Printing

- 3D Scanners for Machine Vision

- **Quality Control**

- Displays

- 3D Imaging

- Intelligent and Adaptive Lighting

- Augmented Reality and Information Overlay

# Description

The DLPR910 device is a programmed PROM used to properly configure the DLPC910 Controller to operate four different digital micromirror device (DMD) options: the DLP9000X, the DLP9000XUV, and the DLP6500 family (S600 and Type A packages). The firmware in this device enables the DLPC910 Controller to provide system throughput rates up to 61 Gigabits per second (Gbps) for the DLP9000X and DLP9000XUV, and up to 24 Gbps for the DLP6500 family, with the options for random row addressing and Load4 capabilities.

For complete electrical and mechanical specifications of the DLPR910, see the XCF16P specification listed in Related Documentation.

### Device Information<sup>(1)</sup>

| PART<br>NUMBER PACKAGE |            | BODY SIZE (NOM)             |  |  |  |

|------------------------|------------|-----------------------------|--|--|--|

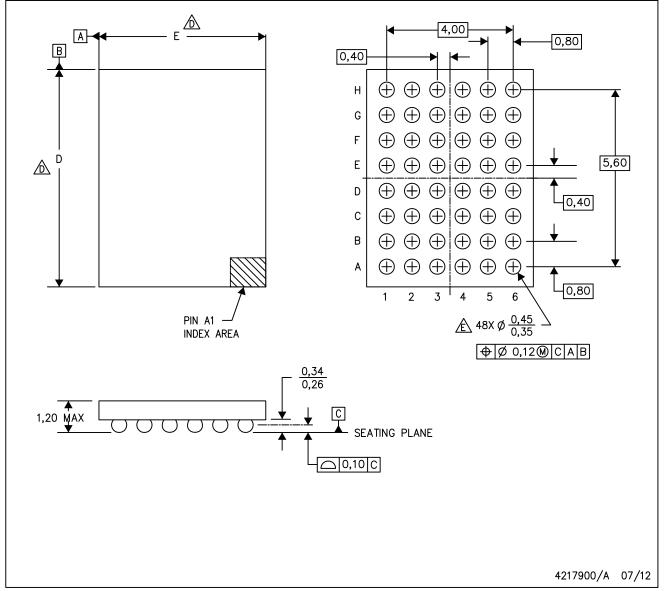

| DLPR910                | DSBGA (48) | 8.00 mm × 9.00 mm × 1.20 mm |  |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

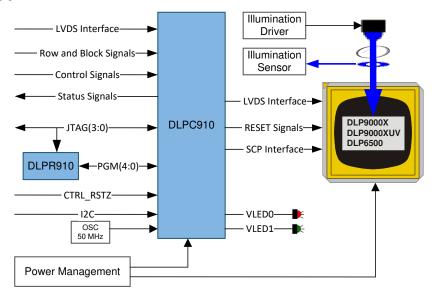

# Simplified Application

Page

# **Table of Contents**

| 1 | Features 1                                         | 8.3 Feature Description                 |

|---|----------------------------------------------------|-----------------------------------------|

| 2 | Applications 1                                     | 8.4 Device Functional Modes             |

| 3 | Description 1                                      | 9 Application and Implementation 10     |

| 4 | Simplified Application 1                           | 9.1 Application Information 10          |

| 5 | Revision History2                                  | 9.2 Typical Application                 |

| 6 | Pin Configuration and Functions 3                  | 10 Power Supply Recommendations 1       |

| 7 | Specifications5                                    | 11 Layout 1                             |

| • | 7.1 Absolute Maximum Ratings5                      | 11.1 Layout Guidelines1                 |

|   | 7.2 ESD Ratings                                    | 12 Device and Documentation Support 12  |

|   | 7.3 Recommended Operating Conditions               | 12.1 Device Support                     |

|   | 7.4 Thermal Information                            | 12.2 Documentation Support              |

|   | 7.5 Electrical Characteristics5                    | 12.3 Community Resources 13             |

|   | 7.6 Supply Voltage Requirements for Power-On Reset | 12.4 Trademarks 13                      |

|   | and Power-Down6                                    | 12.5 Electrostatic Discharge Caution    |

|   | 7.7 Timing Requirements 6                          | 12.6 Glossary1                          |

| 8 | Detailed Description7                              | 13 Mechanical, Packaging, and Orderable |

|   | 8.1 Overview 7                                     | Information 13                          |

|   | 8.2 Functional Block Diagram 7                     | 13.1 Package Option Addendum 14         |

|   |                                                    |                                         |

# **5 Revision History**

Changes from Original (September 2015) to Revision A

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Updated device from Product Preview to Production Data                                                    | 1      |

|-----------------------------------------------------------------------------------------------------------|--------|

| Changes from Revision A (October 2015) to Revision B                                                      | Page   |

| Updated <i>Description</i> to include additional supported DMD                                            | 1      |

| Update document to include additional supported DMD in <i>Detailed Description</i>                        | 7      |

| Added typical application schematic for newly supported DMD in <i>Typical Application</i>                 | 10     |

| Updated                                                                                                   | 12     |

| Added MSL Peak Temp to Packaging Information                                                              | 14     |

| Changes from Revision B (November 2016) to Revision C     Changed "three" to "four different DMD options" | Page 1 |

| Added DLP9000XUV                                                                                          |        |

| Updated SBD for DLP9000XUV, fixed LVDS.                                                                   |        |

| Updated Xilinx reference doc to revision v2.19 from v2.18                                                 |        |

| Added DLP9000XUV                                                                                          |        |

| 7,0000 521 00007,0 7                                                                                      | 6      |

| Added DLP9000XUV                                                                                          | 6<br>7 |

|                                                                                                           |        |

| Added DLP9000XUV                                                                                          |        |

| Added DLP9000XUV      Added DLP9000XUV to caption of Typical Application Schematic                        |        |

Submit Documentation Feedback

Copyright © 2015–2019, Texas Instruments Incorporated

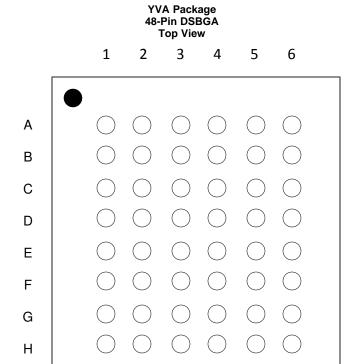

# 6 Pin Configuration and Functions

**Table 1. Pin Functions**

| P                  | PIN | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

|--------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME               | NO. | IIFE                | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| GND                | A1  | G                   | Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| GND                | A2  | G                   | Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| OE/RESET           | А3  | I/O                 | Output Enable/RESET (Open-Drain I/O). When Low, this input holds the address counter reset and the DATA and CLKOUT outputs are placed in a high-impedance state. This is a bidirectional open-drain pin that is held Low while the PROM completes the internal power-on reset sequence. Polarity is not programmable. Pin must be pulled High using an external 4.7-kΩ pull-up to V <sub>CCO</sub> . |  |  |  |

| DNC                | A4  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| D6                 | A5  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| D7                 | A6  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| V <sub>CCINT</sub> | B1  | Р                   | Positive 1.8-V supply voltage for internal logic.                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| V <sub>CCO</sub>   | B2  | Р                   | Positive 3.3-V and 1.8-V supply voltage connected to the output voltage drivers and internal buffers.                                                                                                                                                                                                                                                                                                |  |  |  |

| CLK                | В3  | I                   | Configuration clock input. Each rising edge on the CLK input increments the internal address counter. Pin must be pulled High and Low using an external 100- $\Omega$ pull-up to $V_{CCO}$ and an external 100- $\Omega$ pull-down to Ground. Place resistors close to pin.                                                                                                                          |  |  |  |

| CE                 | B4  | I                   | Chip Enable Input. When $\overline{\text{CE}}$ is High, the device is put into low-power standby mode, the address counter is reset, and the DATA and CLKOUT outputs are placed in a high impedance state.                                                                                                                                                                                           |  |  |  |

| D5                 | B5  |                     | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| GND                | B6  | G                   | Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| BUSY               | C1  |                     | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| CLKOUT             | C2  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

(1) P = Power, G = Ground, I = Input, O = Output

# **Table 1. Pin Functions (continued)**

|                    | PIN |                     |                                                                                                                                                                                                                                                                                                                  |  |  |  |

|--------------------|-----|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME               | NO. | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                      |  |  |  |

| DNC                | C3  |                     | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | C3  |                     | Do Not Connect. Leave unconnected.  Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                           |  |  |  |

| D4                 | C5  | _                   | Do Not Connect. Leave unconnected.  Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                           |  |  |  |

|                    | C5  | _                   | Positive 3.3-V and 1.8-V supply voltage connected to the output voltage drivers and                                                                                                                                                                                                                              |  |  |  |

| V <sub>CCO</sub>   | C6  | Р                   | internal buffers.                                                                                                                                                                                                                                                                                                |  |  |  |

| CF                 | D1  | 1                   | Configuration pin. The $\overline{\text{CF}}$ pin must be pulled High using an external 4.7-k $\Omega$ pull-up to $V_{\text{CCO}}$ . Selects serial mode configuration.                                                                                                                                          |  |  |  |

| CEO                | D2  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | D3  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | D4  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| D3                 | D5  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| V <sub>CCO</sub>   | D6  | Р                   | Positive 3.3-V and 1.8-V supply voltage connected to the output voltage drivers and internal buffers.                                                                                                                                                                                                            |  |  |  |

| V <sub>CCINT</sub> | E1  | Р                   | Positive 1.8-V supply voltage for internal logic.                                                                                                                                                                                                                                                                |  |  |  |

| TMS                | E2  | I                   | JTAG Mode Select Input. TMS has an internal 50-k $\Omega$ resistive pull-up to V <sub>CCJ</sub> .                                                                                                                                                                                                                |  |  |  |

| DNC                | E3  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | E4  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| D2                 | E5  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| TDO                | E6  | 0                   | JTAG Serial Data Output. TDO has an internal 50-kΩ resistive pull-up to V <sub>CCJ</sub> .                                                                                                                                                                                                                       |  |  |  |

| GND                | F1  | G                   | Ground                                                                                                                                                                                                                                                                                                           |  |  |  |

| DNC                | F2  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | F3  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| DNC                | F4  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| GND                | F5  | G                   | Ground                                                                                                                                                                                                                                                                                                           |  |  |  |

| GND                | F6  | G                   | Ground                                                                                                                                                                                                                                                                                                           |  |  |  |

| TDI                | G1  | I                   | JTAG Serial Data Input. TDI has an internal 50k-Ω resistive pull-up to V <sub>CCJ</sub> .                                                                                                                                                                                                                        |  |  |  |

| DNC                | G2  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| REV_SEL0           | G3  | I                   | Revision Select [1:0] Inputs. When the EN_EXT_SEL is Low, the Revision Select pins                                                                                                                                                                                                                               |  |  |  |

| REV_SEL1           | G4  | I                   | are used to select the design revision to be enabled. The Revision Select [1:0] inputs have an internal $50\text{-}k\Omega$ resistive pull-up to $V_{\text{CCO}}$ . The REV_SEL0 pin must be pulled Low using an external $10\text{-}k\Omega$ pull-down to Ground. The REV_SEL1 pin must be connected to Ground. |  |  |  |

| V <sub>cco</sub>   | G5  | Р                   | Positive 3.3-V and 1.8-V supply voltage connected to the output voltage drivers and internal buffers.                                                                                                                                                                                                            |  |  |  |

| V <sub>CCINT</sub> | G6  | Р                   | Positive 1.8-V supply voltage for internal logic.                                                                                                                                                                                                                                                                |  |  |  |

| GND                | H1  | G                   | Ground                                                                                                                                                                                                                                                                                                           |  |  |  |

| ACC1               | H2  | Р                   | Positive 3.3-V JTAG I/O supply voltage connected to the TDO output voltage driver and TCK, TMS and TDI input buffers.                                                                                                                                                                                            |  |  |  |

| тск                | H3  | I                   | JTAG Clock Input. This pin is the JTAG test clock. It sequences the TAP controller and all the JTAG test and programming electronics.                                                                                                                                                                            |  |  |  |

| EN_EXT_SEL         | H4  | I                   | External Selection Input. $\overline{\text{EN\_EXT\_SEL}}$ has an internal 50-k $\Omega$ resistive pull- up to V <sub>CCO</sub> . The $\overline{\text{EN\_EXT\_SEL}}$ pin must be connected to Ground.                                                                                                          |  |  |  |

| D1                 | H5  | _                   | Do Not Connect. Leave unconnected.                                                                                                                                                                                                                                                                               |  |  |  |

| D0                 | H6  | 0                   | DATA output pin to provide data for configuring the DLPC910 in serial mode.                                                                                                                                                                                                                                      |  |  |  |

## 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (see (1) (2))

|                    |                                          |                          | MIN  | MAX | UNIT |

|--------------------|------------------------------------------|--------------------------|------|-----|------|

| V <sub>CCINT</sub> | Internal supply voltage                  | Relative to ground       | -0.5 | 2.7 | V    |

| V <sub>CCO</sub>   | I/O supply voltage                       | Relative to ground       | -0.5 | 4.0 | V    |

| V                  | land to obtain a with manner to any and  | V <sub>CCO</sub> < 2.5 V | -0.5 | 3.6 | V    |

| V <sub>IN</sub>    | Input voltage with respect to ground     | V <sub>CCO</sub> ≥ 2.5 V | -0.5 | 3.6 | V    |

| V                  | Voltage applied to high-impedance output | V <sub>CCO</sub> < 2.5 V | -0.5 | 3.6 | V    |

| $V_{TS}$           |                                          | V <sub>CCO</sub> ≥ 2.5 V | -0.5 | 3.6 | V    |

| TJ                 | Junction temperature                     |                          |      | 125 | °C   |

| T <sub>stg</sub>   | Storage temperature, ambient             |                          | -65  | 125 | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                        |                         |                                                              | VALUE | UNIT |

|------------------------|-------------------------|--------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> (1) | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins | 2000  | V    |

<sup>(1)</sup> Electrostatic discharge (ESD) to measure device sensitivity and immunity to damage caused by assembly line electrostatic discharges in to the device.

#### 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                                                                  |                 | MIN  | NOM | MAX       | UNIT |

|--------------------|----------------------------------------------------------------------------------|-----------------|------|-----|-----------|------|

| V <sub>CCINT</sub> | Internal voltage supply                                                          |                 | 1.65 | 1.8 | 2.0       | V    |

| $V_{CCO}$          | Supply voltage for output drivers                                                | 3.3-V operation | 3.0  | 3.3 | 3.6       | V    |

| $V_{IL}$           | Low-level input voltage                                                          | 3.3-V operation | 0    |     | 8.0       | V    |

| $V_{IH}$           | High-level input voltage                                                         | 3.3-V operation | 2.0  |     | 3.6       | V    |

| Vo                 | Output voltage                                                                   |                 | 0    |     | $V_{CCO}$ | V    |

| t <sub>IN</sub>    | Input signal transition time (measured between 10% $V_{CCO}$ and 90% $V_{CCO}$ ) |                 |      |     | 500       | ns   |

| T <sub>A</sub>     | Operating ambient temperature                                                    |                 | -40  |     | 85        | °C   |

### 7.4 Thermal Information

Refer to the XCF16P product specifications at www.xilinx.com.

### 7.5 Electrical Characteristics

Refer to the XCF16P product specifications at www.xilinx.com.

<sup>(2)</sup> Maximum DC undershoot below GND must be limited to either 0.5 V or 10 mA. During transitions, the device pins can undershoot to -2 V or overshoot to 7 V, provided this overshoot or undershoot lasts less than 10 ns and with the forcing current being limited to 200 mA.

<sup>(2)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

<sup>(3)</sup> JEDEC Standard JESD22-A114A (C1 = 100 pF, R1 = 1500  $\Omega$ , R2 = 500  $\Omega$ ).

### 7.6 Supply Voltage Requirements for Power-On Reset and Power-Down

(see (1))

|                    |                                                                                                                                | MIN | MAX | UNIT |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| t <sub>VCC</sub>   | V <sub>CCINT</sub> rise time from 0 V to nominal voltage <sup>(2)</sup>                                                        | 0.2 | 50  | ms   |

| V <sub>CCPOR</sub> | POR threshold for V <sub>CCINT</sub> supply                                                                                    | 0.5 | _   | V    |

| t <sub>OER</sub>   | OE/RESET release delay following POR (3)                                                                                       | 0.5 | 30  | ms   |

| V <sub>CCPD</sub>  | Power-down threshold for V <sub>CCINT</sub> supply                                                                             |     | 0.5 | V    |

| t <sub>RST</sub>   | Time required to trigger a device reset when the $V_{\text{CCINT}}$ supply drops below the maximum $V_{\text{CCPD}}$ threshold | 10  |     | ms   |

(1)  $V_{CCINT}$ ,  $V_{CCO}$ , and  $V_{CCJ}$  supplies can be applied in any order.

### 7.7 Timing Requirements

Refer to the XCF16P product specifications at www.xilinx.com.

<sup>(2)</sup> At power up, the device requires the V<sub>CCINT</sub> power supply to monotonically rise to the nominal operating voltage within the specified T<sub>VCC</sub> rise time. If the power supply cannot meet this requirement, then the device might not perform power-on-reset properly. See Figure 6, in the Xilinx XCF16P (v2.19) Product Specification for more information.

<sup>(3)</sup> If the V<sub>CCINT</sub> and V<sub>CCO</sub> supplies do not reach their respective recommended operating conditions before the OE/RESET pin is released, then the configuration data from the PROM is not available at the recommended threshold levels. The configuration sequence must be delayed until both V<sub>CCINT</sub> and V<sub>CCO</sub> have reached their recommended operating conditions.

## 8 Detailed Description

#### 8.1 Overview

The configuration bit stream stored in the DLPR910 device supports reliable operation of the DLPC910 device with the DLP9000X and DLP9000XUV DMDs, or the DLP6500 family of DMDs. The DLPC910 digital controller loads this configuration bit stream from the DLPR910 device.

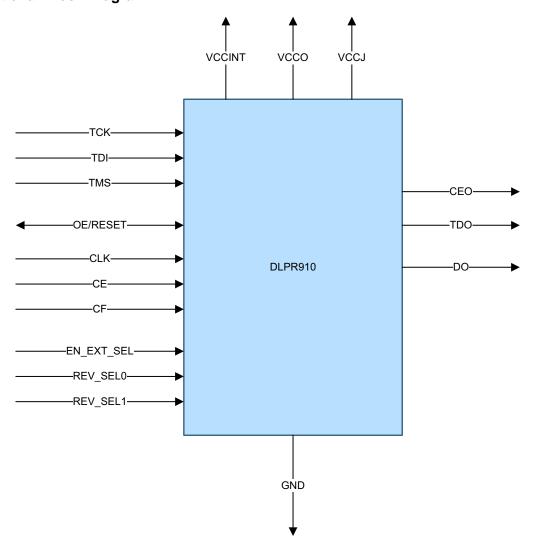

### 8.2 Functional Block Diagram

### 8.3 Feature Description

#### 8.3.1 Data Interface

### 8.3.1.1 Data Outputs

The DLPR910 device is configured for serial mode operation, where D0 is the data output pin. D0 output pin provides a serial connection to the DLPC910, where the configuration is read out by the DLPC910.

### 8.3.1.2 Configuration Clock Input

The configuration CLK is connected to the DLPC910 in Master Serial mode, where the DLPC910 provides the clock pulses to read the configuration from the DLPR910 device.

Submit Documentation Feedback

### **Feature Description (continued)**

#### 8.3.1.3 Output Enable and Reset

When the OE/RESET input is held <u>low</u>, the address counter is reset and the Data and CLKOUT outputs are placed in high-impedance state. **OE/RESET** must be pulled High using an external 4.7-k $\Omega$  pull-up to  $V_{CCO}$ .

#### 8.3.1.4 Chip Enable

The  $\overline{\text{CE}}$  input is asserted by the DLPC910 to enable the Data and CLKOUT outputs. When  $\overline{\text{CE}}$  is held high, the DLPR910 device address counter is reset, and the Data and CLKOUT outputs are placed in high-impedance states.

### 8.3.1.5 Configuration Pulse

The DLPR910 device is configured in serial mode when it holds configuration pulse pin,  $\overline{CF}$ , high and it enables the  $\overline{CE}$  and  $\overline{OE}$  pins. New data is available a short time after each rising clock edge.

#### 8.3.1.6 Revision Selection

The device uses the REV\_SEL\_0, REV\_SEL\_1, and EN\_EXT\_SEL signals to select a revision to act as the default. Setting all three signals to GND defaults to revision 0 for simple DLPR910 device setup.

#### 8.4 Device Functional Modes

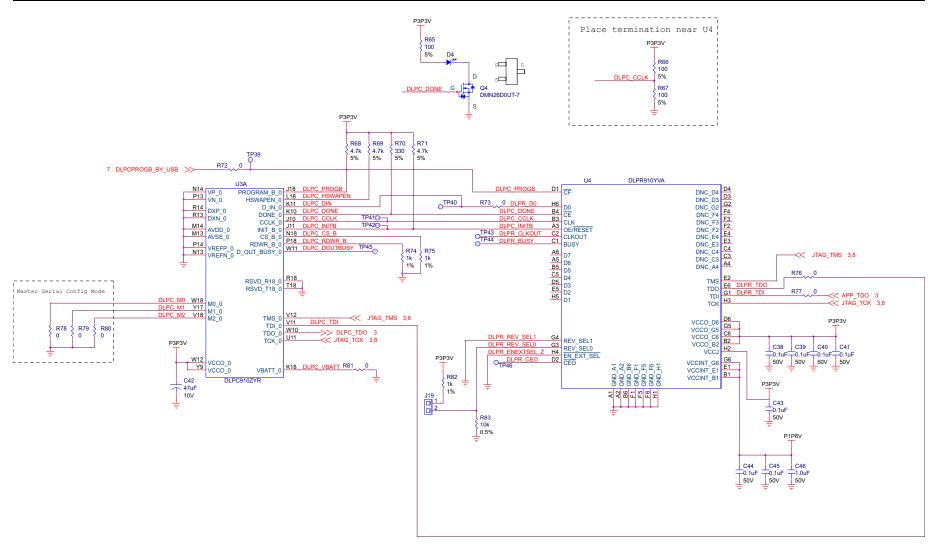

To successfully program the DLPC910 upon power-up, the DLPR910 device must be configured and connected to the DLPC910 as shown in Figure 1.

Copyright © 2015–2019, Texas Instruments Incorporated Product Folder Links: *DLPR910*

Figure 1. DLPC910 and DLPR910 Connection Schematic

## 9 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

## 9.1 Application Information

The DLPR910 device configuration PROM ships pre-programmed with configuration code for the DLPC910. Upon power-up, the DLPC910 and the DLPR910 device connect to enable configuration information to be sent from the DLPR910 device to the DLPC910, such that the DLPC910 can configure itself for proper operation within the application. Without the DLPR910 device properly connected to the DLPC910 in the application system, the DLPC910 does not boot and the system remains inoperable.

### 9.2 Typical Application

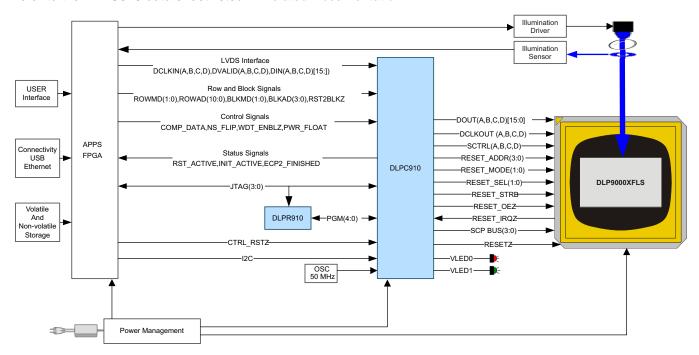

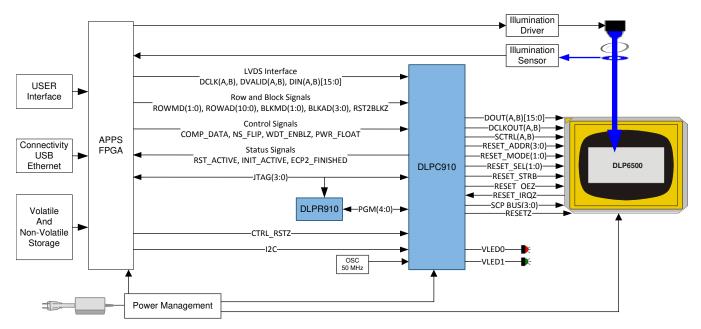

A typical use case for a high speed lithography application is shown in Figure 2 and in Figure 3. Both applications offer continuous run of printing by changing the digitally created patterns without stopping the imaging head. The DLPR910 prom configures the DLPC910 digital controller to reliably operate with the DLP9000X and DLP9000XUV DMDs, or the DLP6500 DMDs. These chipset combinations provide an ideal backend imager that takes in digital images at 2560 x 1600 and 1920 x 1080 in resolution to achieve speeds greater than 61 Gigabits per second (Gbps) and 24 Gbps respectively. For complete details of this typical application refer to the DLPC910 data sheet listed in *Related Documentation*.

Figure 2. Typical High Speed DLP9000X (or DLP9000XUV) Application Schematic

## **Typical Application (continued)**

Figure 3. Typical High Speed DLP6500 Application Schematic

#### 9.2.1 Design Requirements

The DLPR910 is part of a multi-chipset solution, and it is required to be coupled with the DLPC910 for reliable operation of the DLP9000X and DLP9000XUV DMDs, or the DLP6500 family of DMDs. For more information, refer to the DLPC910 datasheet listed in *Related Documentation*.

# 10 Power Supply Recommendations

The DLPR910 uses two power supply rails as shown in Table 2.

Table 2. DLPR910 Power Supply Rails

| SUPPLY | POWER PINS | COMMENTS                                                                                             |

|--------|------------|------------------------------------------------------------------------------------------------------|

| 1.8 V  |            | All $V_{\text{CCINT}}$ pins must be connected with a 0.1- $\mu\text{F}$ decoupling capacitor to GND. |

| 3.3 V  |            | All $V_{CCO}$ and $V_{CCJ}$ pins must be connected with a 0.1- $\mu F$ decoupling capacitor to GND.  |

### 11 Layout

### 11.1 Layout Guidelines

The DLPR910 is part of a multi-chipset solution, and it is required to be coupled with the DLPC910 for reliable operation of the DLP9000X and DLP9000XUV DMDs, or the DLP6500 family of DMDs. Refer to the DLPC910 datasheet listed in *Related Documentation* for a layout example for this multi-chipset solution.

# 12 Device and Documentation Support

### 12.1 Device Support

### 12.1.1 Device Compatibility

| TI PART NUMBER <sup>(1)</sup> | DLP9000XFLS | DLP9000XBFLS   | DLP9000XUVFLS  | DLP6500FYE<br>DLP6500FLQ | DLP6500BFYE<br>DLP6500BFLQ |

|-------------------------------|-------------|----------------|----------------|--------------------------|----------------------------|

| DLPR910YVA                    | Compatible  | Not Compatible | Not Compatible | Compatible               | Not Compatible             |

| DLPR910AYVA                   | Compatible  | Compatible     | Compatible     | Compatible               | Compatible                 |

<sup>(1)</sup> Refer to each individual DMD datasheet under Device and Documentation Support to determine location and revision of the DMD.

#### 12.1.2 Device Nomenclature

**Table 3. Part Number Description**

| TI PART NUMBER | DESCRIPTION                 | REFERENCE NUMBER |

|----------------|-----------------------------|------------------|

| DLPR910AYVA    | DLPR910A Configuration PROM | 2514595-0002     |

### 12.1.3 Device Markings

Figure 4. DLPR910 Device Markings

Where XXXXXXXXXXX is the reference number located in Table 3.

### 12.2 Documentation Support

#### 12.2.1 Related Documentation

For related documentation, see the following:

- DLPC910 datasheet (DLPS064)

- DLP9000(X) datasheet (DLPS036)

- DLP9000XUV datasheet (DLPS158)

- DLP6500 Type A datasheet (DLPS040)

- DLP6500 S600 datasheet (DLPS053)

- XCF16P data sheet (www.xilinx.com)

### 12.3 Community Resources

TI E2E™ support forums are an engineer's go-to source for fast, verified answers and design help — straight from the experts. Search existing answers or ask your own question to get the quick design help you need.

Linked content is provided "AS IS" by the respective contributors. They do not constitute TI specifications and do not necessarily reflect TI's views; see TI's Terms of Use.

#### 12.4 Trademarks

E2E is a trademark of Texas Instruments. Xilinx is a registered trademark of Xilinx, Inc. All other trademarks are the property of their respective owners.

### 12.5 Electrostatic Discharge Caution

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

### 12.6 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

# 13 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this datasheet, refer to the left-hand navigation.

### 13.1 Package Option Addendum

### 13.1.1 Packaging Information

| Orderable Device | Status (1) | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan (2) | Lead/Ball Finish | MSL Peak Temp (3)    | Op Temp (°C) | Device Marking <sup>(4)(5)</sup> |

|------------------|------------|-----------------|--------------------|------|----------------|--------------|------------------|----------------------|--------------|----------------------------------|

| DLPR910AYVA      | ACTIVE     | DSBGA           | YVA                | 48   | 1              | Call TI      | Call TI          | Level-3-260C-168 HRS | -40 to 85    | Call TI                          |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PRE\_PROD Unannounced device, not in production, not available for mass market, nor on the web, samples not available.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free** (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

- (3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device

- (5) Multiple Device markings will be inside parentheses. Only on Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# YVA (R-XBGA-N48)

# DIE-SIZE BALL GRID ARRAY

- NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. NanoFree™ package configuration.

- The package size (Dimension D and E) of a particular device is specified in the device Product Data Sheet version of this drawing, in case it cannot be found in the product data sheet please contact a local TI representative.

- E. Reference Product Data Sheet for array population. 6 x 8 matrix pattern is shown for illustration only.

- F. This package contains Pb—free balls.

NanoFree is a trademark of Texas Instruments.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (<a href="www.ti.com/legal/termsofsale.html">www.ti.com/legal/termsofsale.html</a>) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated