# **DAVICOM Semiconductor, Inc.**

# DM130160

15V / 30V Selectable Output & 162 Hi-V Channels Driver IC

# DATA SHEET

Preliminary Version: DM130160-11-MCO-DS-P01 August 31, 2016

# Content

| 1  | General Description                            |   |

|----|------------------------------------------------|---|

| 2  | Features                                       |   |

| 3  | Block Diagram                                  | 5 |

| 4  | PAD Diagram                                    | 6 |

| 5  | Pin Description                                |   |

| 6  | Function Description                           |   |

|    | 6.1 Generate Hi-V Driving Bias Supply          |   |

|    | 6.1.1 Internal Charge Pump Supply              |   |

|    | 6.1.2 External Driving Bias Supply for pumping |   |

|    | 6.2 Multi-drivers Application                  |   |

|    | 6.3 EPD Driver Control Register                |   |

|    | 6.4 Control Signal Waveform                    |   |

|    | 6.4.1 Format of One Byte                       |   |

|    | 6.4.2 SPI Control Waveform                     |   |

|    | 6.4.3 Com & Segment vs. Control Signal         |   |

| 7  | Operating Rating                               |   |

| 8  | Absolute Maximum Ratings                       |   |

| 10 | Ordering Information                           |   |

#### **1** General Description

The DM130160 consist of DC-DC Hi-V charge pump for EPD (Electrophoretic display) application. User can chose 15V or 30V to drive EPD. All the functions are controlled by 2-wires serial interface or SPI interface. DM130160 support synchronous serial signal interface (Maximum 4 chips cascadable).

- 2 Features

- Operating voltage 2.2V ~ 5.5V

- Selectable 15V or 30V driving voltage for EPD

- 160 SEG + 1 COM + 1 Background

- DC-DC charge pump circuit

- ON chip RC oscillator

- 2-wire serial interface

- SPI interface control

- Voltage regulator

- Synchronous serial signal interface (Maximum 4 chips cascadable)

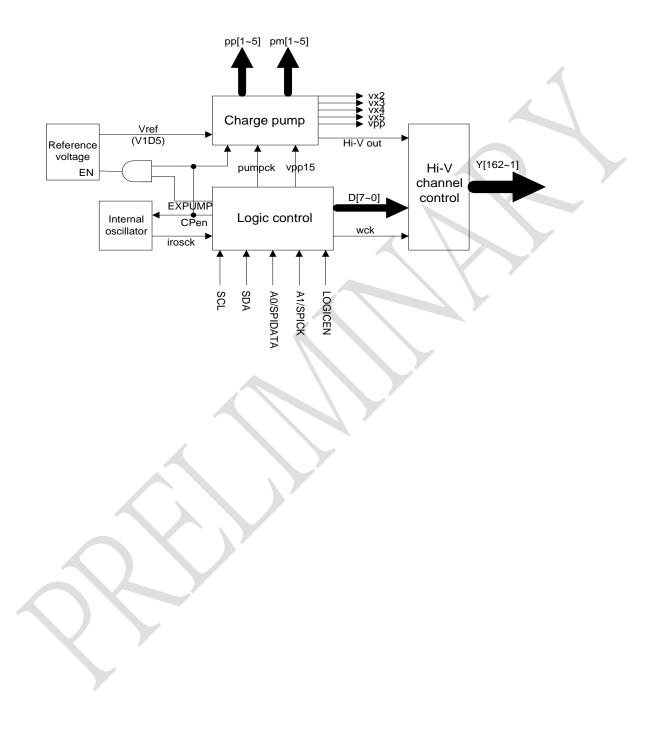

# 3 Block Diagram

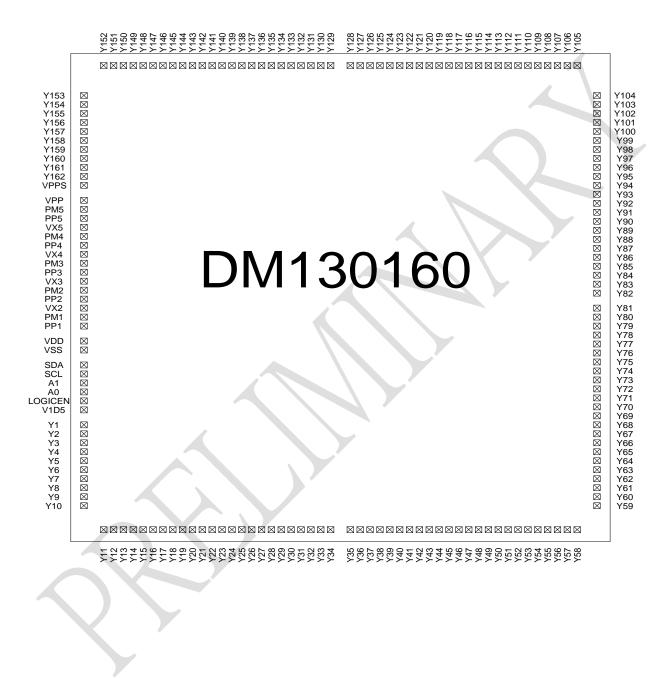

### 4 PAD Diagram

# 5 Pin Description

| PIN NAME     | Description                                                        |  |  |  |  |

|--------------|--------------------------------------------------------------------|--|--|--|--|

| SCL          | 2-wires serial interface clock input                               |  |  |  |  |

| SDA / SPIEN  | 2-wires serial interface data input or SPIEN pin                   |  |  |  |  |

| A1 / SPICK   | Device ID setting bit1 or SPICK pin                                |  |  |  |  |

| A0 / SPIDATA | Device ID setting bit0 or SPIDATA pin                              |  |  |  |  |

| LOGICEN      | Select the control interface<br>LOGICEN=1 2-wires serial interface |  |  |  |  |

|              | LOGICEN=0 SPI interface                                            |  |  |  |  |

| VPP          | Charge pump output pin about 30v                                   |  |  |  |  |

| VPPS         | Power source of EPD channels (IN)                                  |  |  |  |  |

| VX5          | Charge pump output pin about 15v                                   |  |  |  |  |

| VX4          | Charge pump output pin about 7.5v                                  |  |  |  |  |

| VX3          | Charge pump output pin about 5v                                    |  |  |  |  |

| VX2          | Charge pump output pin about 2.5v                                  |  |  |  |  |

| PP[1:5]      | Positive terminal for charge pump capacitor                        |  |  |  |  |

| PM[1:5]      | Negative terminal for charge pump capacitor                        |  |  |  |  |

| Y[1:162]     | EPD Hi-V channels                                                  |  |  |  |  |

| VDD          | Positive power source                                              |  |  |  |  |

| VSS          | Negative power source                                              |  |  |  |  |

| V1D5         | Charge pump reference Voltage                                      |  |  |  |  |

Note : SCL & SDA need pull high resistor  $4.7K\Omega$  to VDD VID5 needs connect to 0.1uF to VSS

#### 6 Function Description

#### 6.1 Generate Hi-V Driving Bias Supply

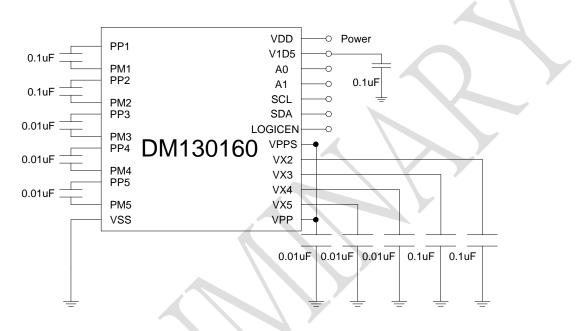

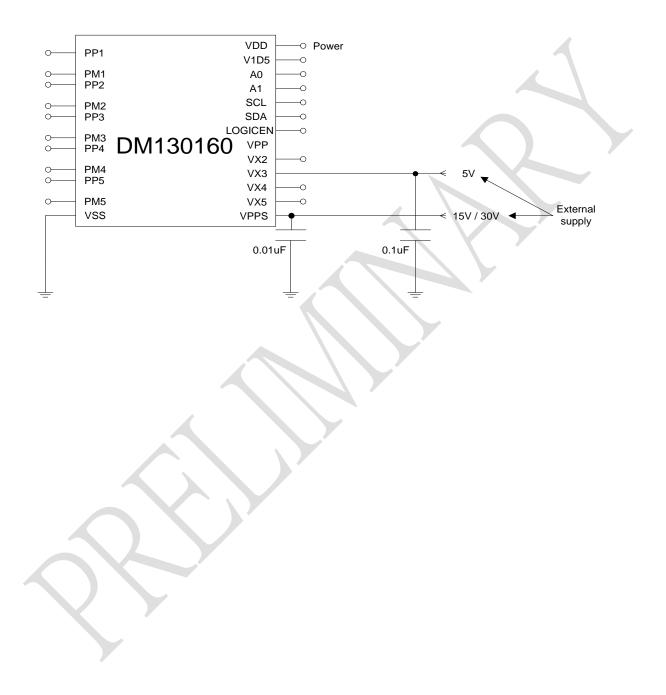

#### 6.1.1 Internal Charge Pump Supply – 30V

The charge pump circuit can generate Hi-voltage up to 30V. User also can select 0V, 15V or 30V to drive EPD by hardware connection.

The value of Hi-voltage that pump can generate as following. VPP=30V, VX5=15V, VSS=0V

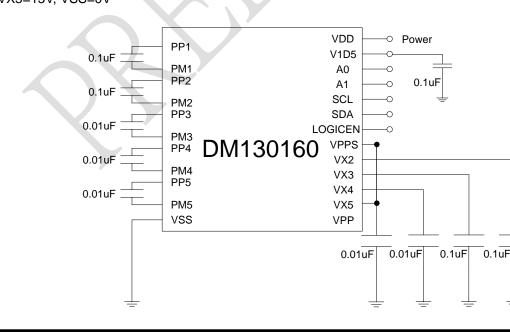

#### 6.1.2 Internal Charge Pump Supply – 15V

The charge pump circuit can generate Hi-voltage up to 30V. User also can select 0V, 15V or 30V to drive EPD by hardware connection.

The value of Hi-voltage that pump can generate as following. VX5=15V, VSS=0V

#### 6.1.3 External Driving Bias Supply for pumping

External power source supply to VPPS & VX3. First, user need to turn off internal pump function then supply 15V/30V to VPPS, 5V to VX3

#### 6.2 Multi-drivers Application

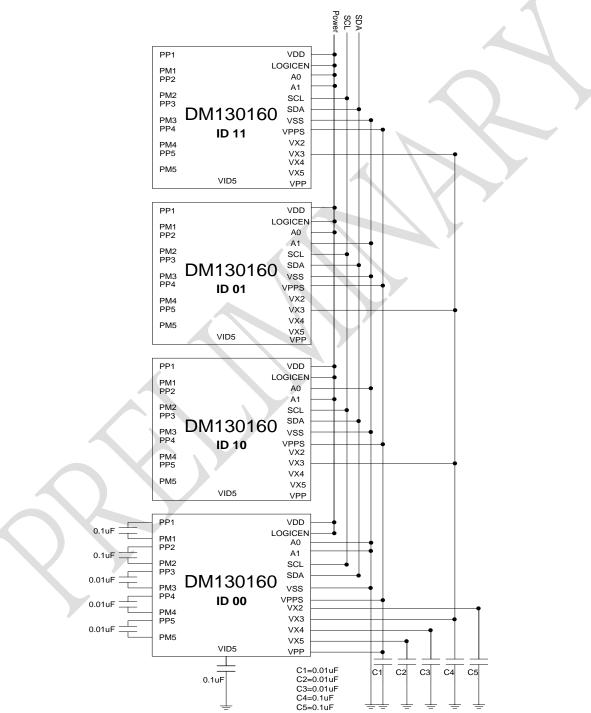

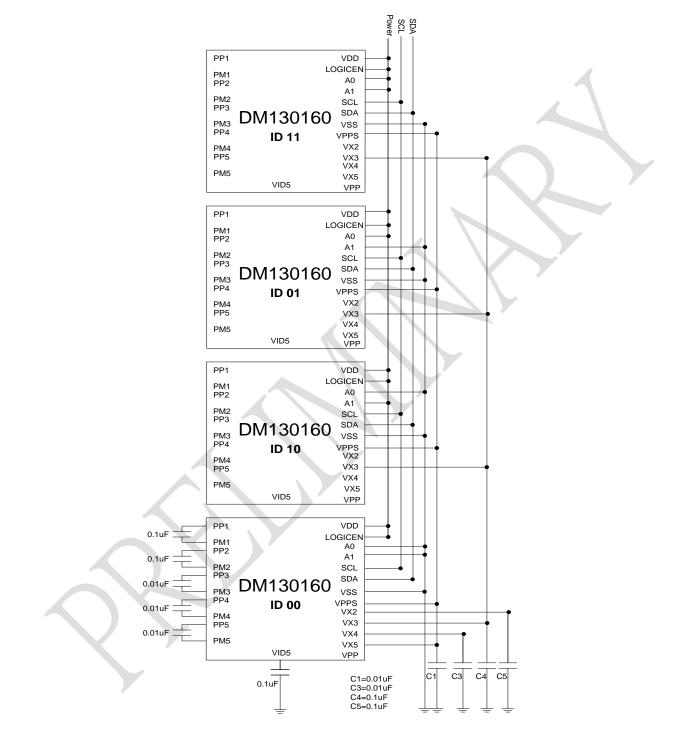

With 2-wires serial interface that the host device could control DM130160. (A1,A0) pins correspond the ID setting (Maximum support 4 chips). ID setting see the following figure.

Note: SPI don't support Multi-drivers application.

#### Internal charge pump supply-30V

#### Internal Charge Pump Supply – 15V

#### 6.3 EPD Driver Control Register

| REGISTER | ISTER Data |      |       |      |      |      |       |       |

|----------|------------|------|-------|------|------|------|-------|-------|

| Address  | Bit7       | Bit6 | Bit5  | Bit4 | Bit3 | Bit2 | Bit1  | Bit0  |

| \$00H    | Y8         | Y7   | Y6    | Y5   | Y4   | Y3   | Y2    | Y1    |

| \$01H    | Y16        | Y15  | Y14   | Y13  | Y12  | Y11  | Y10   | Y9    |

| \$02H    | Y24        | Y23  | Y22   | Y21  | Y20  | Y19  | Y18   | Y17   |

| \$03H    | Y32        | Y31  | Y30   | Y29  | Y28  | Y27  | Y26   | Y25   |

| \$04H    | Y40        | Y39  | Y38   | Y37  | Y36  | Y35  | Y34   | Y33   |

| \$05H    | Y48        | Y47  | Y46   | Y45  | Y44  | Y43  | Y42   | Y41   |

| \$06H    | Y56        | Y55  | Y54   | Y53  | Y52  | Y51  | Y50   | Y49   |

| \$07H    | Y64        | Y63  | Y62   | Y61  | Y60  | Y59  | Y58   | Y57   |

| \$08H    | Y72        | Y71  | Y70   | Y69  | Y68  | Y767 | Y66   | Y65   |

| \$09H    | Y80        | Y79  | Y78   | Y77  | Y76  | Y75  | Y74   | Y73   |

| \$0AH    | Y88        | Y87  | Y86   | Y85  | Y84  | Y83  | Y82   | Y81   |

| \$0BH    | Y96        | Y95  | Y94   | Y93  | Y92  | Y91  | Y90   | Y89   |

| \$0CH    | Y104       | Y103 | 102   | Y101 | Y100 | Y99  | Y98   | Y97   |

| \$0DH    | Y112       | Y111 | Y110  | Y109 | Y108 | Y107 | Y106  | Y105  |

| \$0EH    | Y120       | Y119 | Y118  | Y117 | Y116 | Y115 | Y114  | Y113  |

| \$0FH    | Y128       | Y127 | Y126  | Y125 | Y124 | Y123 | Y122  | Y121  |

| \$10H    | Y136       | Y135 | Y134  | Y133 | Y132 | Y131 | Y130  | Y129  |

| \$11H    | Y144       | Y143 | Y142  | Y141 | Y140 | Y139 | Y138  | Y137  |

| \$12H    | Y152       | Y151 | Y150  | Y149 | Y148 | Y147 | Y146  | Y145  |

| \$13H    | Y160       | Y159 | Y158  | Y157 | Y156 | Y155 | Y154  | Y153  |

| \$14H    | #          | #    | #     | #    | #    | #    | Y162  | Y161  |

| \$15H    | CPEN       | C3   | VPP15 | C2   | Load | C1   | VSEL1 | VSEL0 |

Y1~Y162 output setting :

Y1~Y160 mapping to segment pins

Y161 correspond to COM(Common) pin

Y162 correspond to BG(Background) pin

The output voltage (0V,15V,30V) for Y[1~162] are selectable. If user want Y[1~162] to output 30V or 15V. Setting the correspond bit to "1" If user want Y[1~162] to output 0V. Setting the correspond bit to "0"

Example :

If users wants Y9, Y11, Y13, Y15 output VPP and Y10, Y12, Y14, Y16 output "0V" Register \$01H = 01010101

Register "\$15h" bit7 "CPEN": Charge pump on / off CPEN=1 , charge pump enable CPEN=0 , charge pump disable

Register "\$15h" bit6 "C3" : Internal test parameter C3. User has to set up "0" here.

Register "\$15h" bit5 "VPP15" : Half VPP output switch

VPP15=1 : Hi-V channels logic high will output VX5, the voltage equal to half VPP. VPP15=0 : Hi-V channels logic high will output VPP.

Register"\$15h" bit4 "C2": Internal test parameter "C2". Set up "0" here for recommendation.

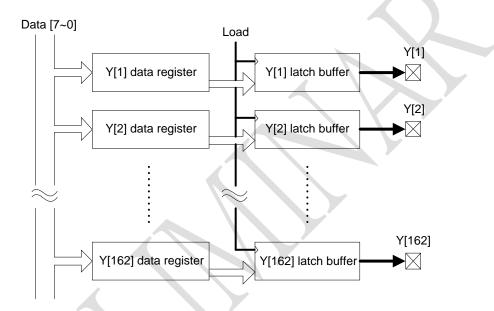

Register"\$15h" bit3 "Load": Load data from Y[1~162] and then latch out for synchronous Load=1 : Load data from Y[1~162] to output buffer Load=0 : Latch the buffer and output

#### **Output synchronous**

For the reason of output synchronous that user have to set up 15h, bit3 = 0 first. This step will load the data Y [1~162] from register[00h~14h] into each buffer. And then set up 15h, bit3 = 1 for the next step. Y [1~162] latch buffers will latch and output the data synchronous.

Note:

The data hold time for this bit should be over "1us". That means, customer set up register \$15h.bit3 =1 for latching output then wait over 1us that will be available for next data.

Register"\$15h" bit2 "C1": Internal test parameter "C1". Set up "0" here for recommendation.

Register"\$15h" bit0~1 "VSEL0~1" : Adjustable internal reference voltage All the selections are shown as below:

| VSEL[1:0] | V1D5 |

|-----------|------|

| 00        | 1.5V |

| 01        | 1.6V |

| 10        | 1.7V |

| 11        | 1.8V |

Note:

- 1. All control registers don't have initialize value after power on. Users need to initial all register manually.

- 2. \$xxH means address and represent in hexadecimal form.

- 3. "xxxxxxxb" means 8-bits data of register and represent in binary form.

- 4. The "VPP" here means the most high pumped voltage, "VX5" means half VPP and "GND" means the most low voltage of system power.

- 5. Write by default value 00b.

#### 6.4 Control Signal Waveform

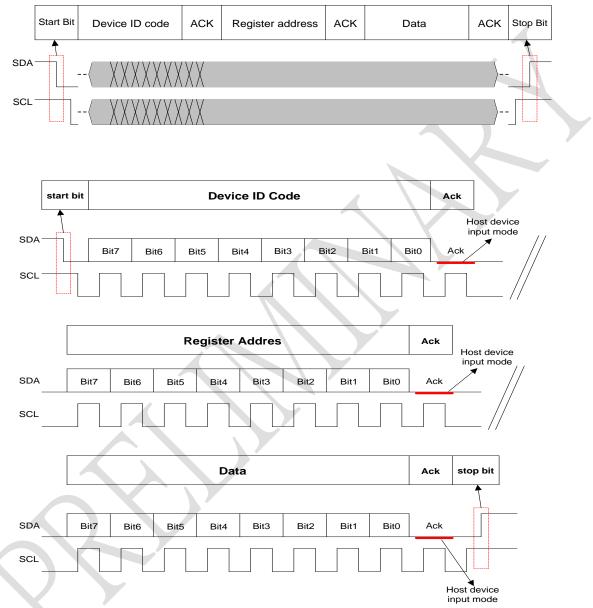

#### 6.4.1 Format of One Byte

This byte could be  $00H \sim 15H$ , see 6..3 EPD driver control register.

Note: Timing diagram above is when SCL=500KHz

Device ID code :

ID code defined by (A0&A1) pins. See figure5 multi-driver application. Control signal input 8-bits "111100A1,A0" (A1,A0)=00,01,10,11 then only matched driver will operate.

#### Register address :

Address of control register from \$00H ~ \$15H. The control signal here follow Device ID code

#### Data of register :

Definition of all control register see chapter 2.3 EPD driver control register.

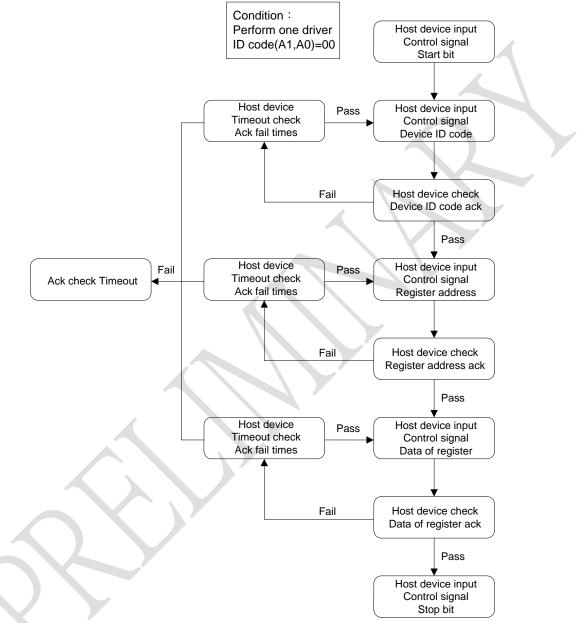

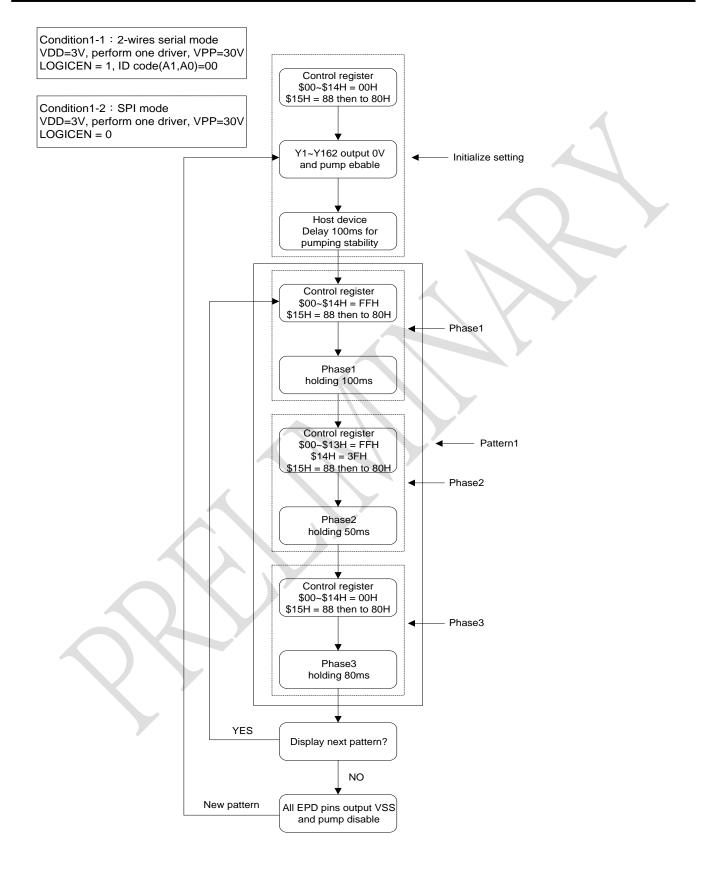

### **Condition setting** Perform with one driver IC and ID code (A1,A0)=00

#### Operating flow of one byte

#### Note :

- 1. According to operating flow above, host device need set SDA to input mode at ACK feedback. Also check ACK feedback "Low" that means current byte transmission pass.

- 2. Each byte of control register has complete format as operating flow above. Following one-byte format to compose sequent transmission.

- 3. Operating flow above is only for reference. For actual situation, please refer to E-paper spec.

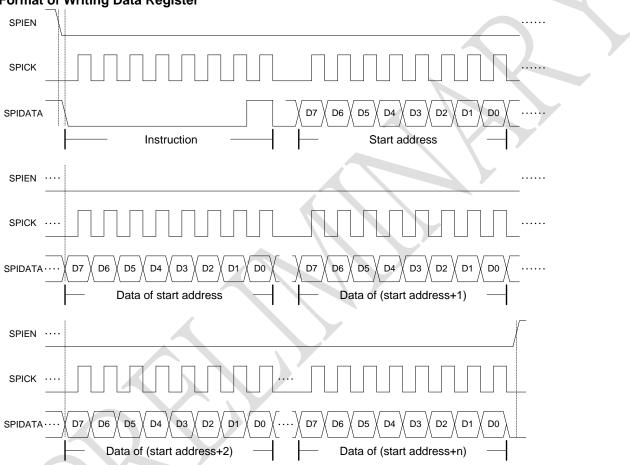

#### 6.4.2 SPI Control Waveform

There are two format of controlled signal as below.

| Instruction code | Function                 |

|------------------|--------------------------|

| 0000001          | Writing Data register    |

| 00000011         | Writing control register |

### Format of Writing Data Register

- SPIEN low active 1.

- SPIDATA input instruction [00000001] for writing data register 2.

- 3. SPIDATA input start address (selectable from \$00H~\$0FH)

- 4. SPIDATA input the data of start address

- SPIDATA input data of next address. For example, start address from  $00H \rightarrow \#FFH(contain of 00H) \rightarrow$ 5. #02H (here is the contain of \$01H)....etc.

- 6. SPIEN high disable while data register writing finished.

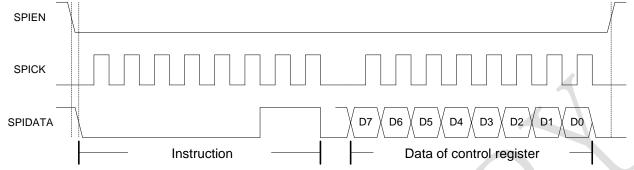

#### Format of Writing Control Register

- 1. SPIEN low active

- 2. SPIDATA input instruction [00000011] for writing control register

- 3. SPIDATA input data of control register

- 4. SPIEN high disable after control register writing done.

#### Note :

- 1. ID code setting isn't needed in SPI mode.

- 2. Writing data register could be sequent, but control register is single.

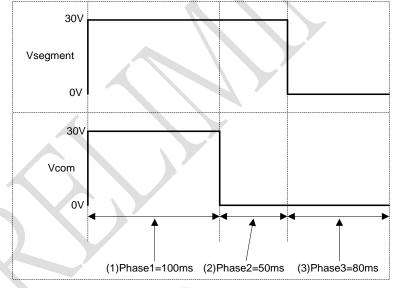

#### 6.4.3 Com & Segment vs. Control Signal

Figure 9

#### Condition1-1: 2-wires serial mode (one driver)

VDD=3V, use internal pump function, perform with one driver, pin LOGICEN = 1, ID code (A1,A0)=00 Register \$15H. bit5 VPP15=0, bit6 PUMPH=0  $\rightarrow$  VPP=30V Vsegment including Y1~Y160, Vcom = Y161, Vbg = Y162

#### Condition1-2 : SPI mode (one driver)

VDD=3V , use internal pump function , perform with one driver, pin LOGICEN = 0 Register \$15H. bit5 VPP15=0 , bit6 PUMPH=0  $\rightarrow$  VPP=30V Vsegment including Y1~Y160 , Vcom = Y161, Vbg = Y162

#### Condition1-1 & 1-2 operate flow

- Control register \$00H~\$14H = "0000000b", \$15H = "1000000b". This step Y1~Y162 will load data from data register and output "0V" to all EPD pins simultaneously. After that \$15H = "10001000b" here will latch all EPD pins to "0V" and enable charge pump. Note! \$15H bit3 load = 1 → 0 will load all data to EPD pins and then latch output state.

- 2. Host device delay 100ms for internal pumping stability.

- 3. Control register \$00H~\$14H = "11111111b", \$15H = "10001000b". Then \$15H = "10000000b". Here all EPD pins will output VPP.

- 4. Host device delay 100ms to display phase1 pattern.

- 5. Control register \$00H~\$13H = "11111111b" , \$14H = "00000000b" , \$15H = "10001000b". Then \$15H = "10000000b". All segment will output VPP, but Y161~Y162 output "0V".

- 6. Host device delay 50ms to display phase2 pattern.

- Control register \$00H~\$14H = "00000000b", \$15H = "10001000b". Then \$15H = "10000000b". All EPD pins will output "0V".

- 8. Host device delay 80ms to display phase3 pattern.

- 9. All EPD pins output "0V" and disable pump if there's no pattern will be display.

Note : \$xxH means address and represent in hexadecimal form. "xxxxxxb" means 8-bits data and represent in binary form.

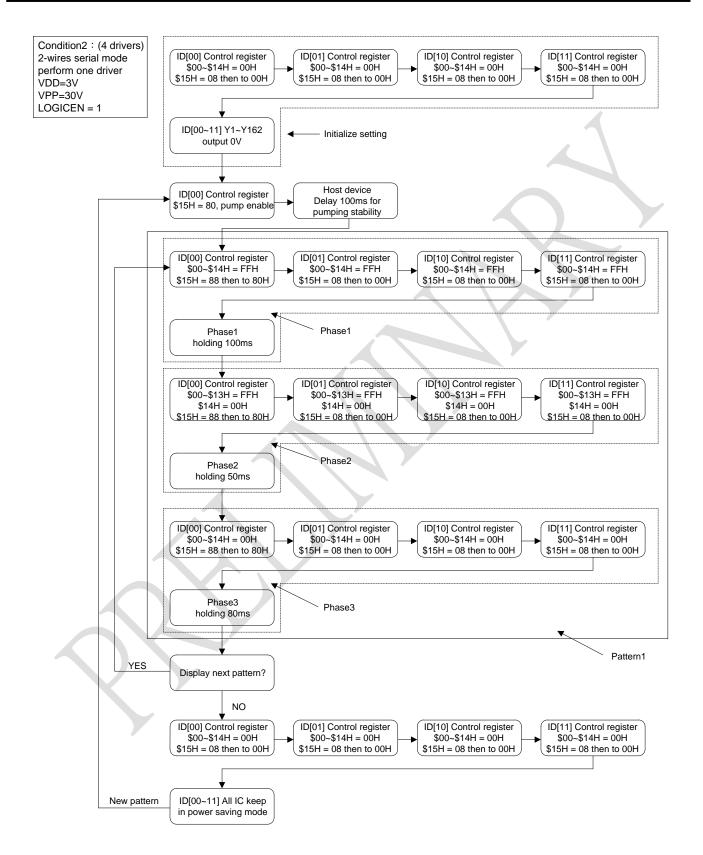

#### Condition2 : 2-wires serial mode (cascade four drivers)

VDD=3V, perform with four drivers, one driver be the pumping source and others set up supply from external source, pin LOGICEN = 1

Register \$15H. bit5 VPP15=0, bit6 PUMPH=0  $\rightarrow$  VPP=30V Vsegment including Y1~Y160, Vcom = Y161, Vbg = Y162

#### **Condition2 operate flow**

- ID[00] Control register \$00H~\$14H = "0000000b", \$15H = "00001000b". This step Y1~Y162 will load data from data register and output "0V" to all EPD pins simultaneously. After that \$15H = "0000000b" here will latch all EPD pins to "0V". Note! \$15H bit3 load = 1 → 0 will load all data to EPD pins and then latch output state.

- 2. ID[01~11] follow step1 to initialize all EPD pins to output "0V"

- 3. ID[00] register \$15H = "10000000b" to enable charge pump and take ID[00] as pumping source others IC set up supply from external source.

- 4. Host device delay 100ms for internal pumping stability.

- ID[00~11] Control register \$00H~\$14H = '1111111b", \*ID[00] \$15H = "10001000b", ID[01~11] \$15H = "00001000b". Then ID[00] \$15H = "10000000b", ID[01~11] \$15H = "00000000b". Here all EPD pins will output VPP.

- 6. Host device delay 100ms to display phase1 pattern.

- 7. ID[00~11] Control register \$00H~\$13H = "11111111b", \$14H = "00000000b", \*ID[00] \$15H = "10001000b", ID[01~11] \$15H = "00001000b". Then ID[00] \$15H = "10000000b", ID[01~11] \$15H = "00000000b". All segment and background will output VPP, but Y161 output "0V".

- 8. Host device delay 50ms to display phase2 pattern.

- ID[00~11] Control register \$00H~\$14H = "00000000b", \*ID[00] \$15H = "10001000b", ID[01~11] \$15H = "00001000b". Then ID[00] \$15H = "10000000b", ID[01~11] \$15H = "00000000b". All EPD pins will output "0V".

- 10. Host device delay 80ms to display phase3 pattern.

- 11. All EPD pins output "0V" and disable pump if there's no pattern will be display.

Note : \$xxH means address and represent in hexadecimal form.

"xxxxxxxb" means 8-bits data and represent in binary form.

# **DM130160**

15V / 30V Selectable Output & 162 Hi-V Channels Driver IC

# 7 Operating Rating

| Description                | Symbol | Value |         |     | Unit               |  |

|----------------------------|--------|-------|---------|-----|--------------------|--|

| Description                | Symbol | Min   | Тур     | Max | onit               |  |

| Working voltage            | VDD    | 2.2   | 3       | 5.5 | V                  |  |

| Driver supply voltage      | Vdrv   |       | 30      | 32  | V                  |  |

| Ripple                     | Vrip   |       | 200     |     | mV                 |  |

| Hi-V1                      | Vpp15  |       | 15V     |     | V, (load =15M ohm) |  |

| Hi-V2                      | Vpp30  |       | 30V     |     | V, (load =15M ohm) |  |

| Stop mode current          | Istop  |       | 0.1     |     | uA                 |  |

| Pumping enable current     | Icpen  |       | 350     |     | uA                 |  |

| Input high voltage         | Vih    |       | 0.8*VDD |     | V                  |  |

| Input low voltage          | VIL    |       | 0.2*VDD |     | V                  |  |

| 2wir speed (SCL&SDA) *(1)  | FI2C   |       |         | 1M  | Hz                 |  |

| 2wir load capacitance *(1) | CI2C   |       | 15      |     | pF                 |  |

| SPI speed                  | FSPI   |       |         | 1M  | Hz                 |  |

| SPI load capacitance       | CSPI   |       | 15      |     | рF                 |  |

Note : \*(1) 2wir represent SCL & SDA pins

SPI represent SPICK & SPIDATA

# 8 Absolute Maximum Ratings

| Symbol | Description           | Rating                      | Unit |

|--------|-----------------------|-----------------------------|------|

| Vdd    | Supply Voltage        | -0.5 ~ +3.6                 | V    |

| Vin    | Input Voltage         | out Voltage -0.5 ~ VDD +0.5 |      |

| Vout   | Output Voltage        | -0.5 ~ VDD +0.5             | V    |

| Topr   | Operation Temperature | 0 ~ 70                      | °C   |

| Tstg   | Storage Temperature   | -40 ~ 125                   | °C   |

| Part Number | Pin Count | Package                        |

|-------------|-----------|--------------------------------|

| DM130160W   | -         | Wafer (Pb-Free)                |

| DM130160WB  | -         | Wafer + Gold bump<br>(Pb-Free) |

| DM130160    | 186       | Dice (Pb-Free)                 |

| DM130160B   | 186       | Dice + Gold bump<br>(Pb-Free)  |

| DM130160C   | 239       | COF (Roll) (Pb-Free)           |

| DM130160P   | 239       | COF (Tray) (Pb-Free)           |

#### 10 Ordering Information

#### Disclaimer

The information appearing in this publication is believed to be accurate. Integrated circuits sold by DAVICOM Semiconductor are covered by the warranty and patent indemnification provisions stipulated in the terms of sale only. DAVICOM makes no warranty, express, statutory, implied or by description regarding the information in this publication or regarding the information in this publication or regarding the freedom of the described chip(s) from patent infringement. FURTHER, DAVICOM MAKES NO WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PURPOSE. DAVICOM reserves. the right to halt production or alter the specifications and prices at any time without notice. Accordingly, the reader is cautioned to verify that the data sheets and other information in this publication are current before placing orders. Products described herein are intended for use in normal commercial applications. Applications involving unusual environmental or reliability requirements, e.g. military equipment or medical life support equipment, are specifically not recommended without additional processing by DAVICOM for such applications.

Please note that application circuits illustrated in this document are for reference purposes only.

DAVICOM's terms and conditions printed on the order acknowledgment govern all sales by DAVICOM. DAVICOM will not be bound by any terms inconsistent with these unless DAVICOM agrees otherwise in writing. Acceptance of the buyer's orders shall be based on these terms.

#### **Company Overview**

DAVICOM Semiconductor Inc. develops and manufactures integrated circuits for integration into data communication products. Our mission is to design and produce IC products that are the industry's best value for Data, Audio, Video, and Internet/Intranet applications. To achieve this goal, we have built an organization that is able to develop chipsets in response to the evolving technology requirements of our customers while still delivering products that meet their cost requirements.

#### Products

We offer only products that satisfy high performance requirements and which are compatible with major hardware and software standards. Our currently available and soon to be released products are based on our proprietary designs and deliver high quality, high performance chipsets that comply with modem communication standards and Ethernet networking standards. customized For products, please contact to Davicom's sales

#### **Contact Windows**

For additional information about DAVICOM products, contact the Sales department at:

#### Headquarters

Hsin-chu Office: No.6, Li-Hsin 6th Rd., Hsinchu Science Park, Hsin-chu City 300, Taiwan, R.O.C. TEL: +886-3-5798797 FAX: +886-3-5646929 MAIL: <u>sales@davicom.com.tw</u> HTTP: http://www.davicom.com.tw

#### WARNING

Conditions beyond those listed for the absolute maximum rating may destroy or damage the products. In addition, conditions for sustained periods at near the limits of the operating ranges will stress and may temporarily (or permanently) affect and damage structure, performance and function.