# **DM141**

Version: A.012

Issue Date: 2004/04/09

File Name : SP-DM141-A.012.doc

Total Pages: 16

# 8x2-Channels Constant Current LED Driver

### **DM141**

### 8x2-Bit Constant Current LED Drivers

### **General Description**

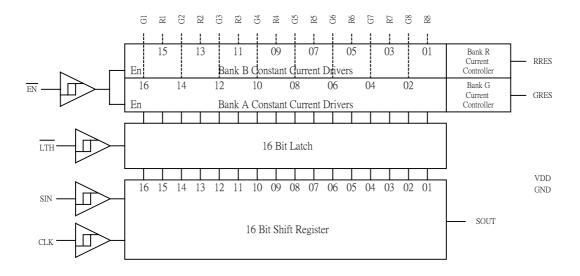

The DM141 is a constant current driver specifically designed for LED display applications. The device includes a 16-bit shift register, a latch, and dual-interleaved banks of constant current drivers on a single Silicon CMOS chip. Each of the dichotomous 8-bit banks requires a current setting resistor. The output current ranges from 5mA to 60mA.

#### **Features**

• Constant Current Output: From 5mA to 60mA

• Maximum Clock Frequency: 25MHz (Max)

• Power Supply Voltage: 3.3V to 5.0V

CMOS Compatible Input/Output

• Package: QFN32, SDIP28, SSOP28

• Constant Current Matching:

10mA to 60mA : Bit-to-Bit :  $\pm$  4.0% (Max) \cdot

Chip-to-Chip:  $\pm 10.0\%$  (Max)

5mA to 10mA : Bit-to-Bit :  $\pm$  6.0% (Max) \cdot

Chip-to-Chip:  $\pm 12.0\%$  (Max)

Maximum Output Voltage: 17V

• Two-color LED driving capability on chip

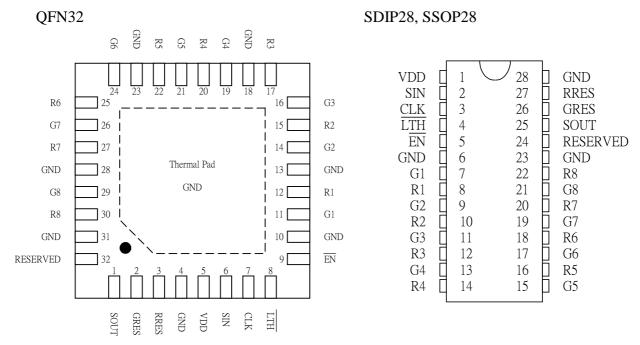

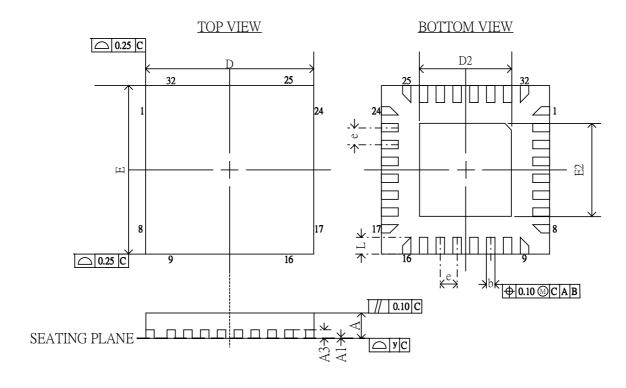

### Pin Connection (Top view)

### **Pin Description**

| Pin No.                           | Pin No.                    | Pin NAME    | FUNCTION                                                                                                                                                                        |

|-----------------------------------|----------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (QFN32)                           | (SDIP28, SSOP28)           |             |                                                                                                                                                                                 |

| 5                                 | 1                          | $V_{ m DD}$ | Supply voltage terminal.                                                                                                                                                        |

| 6                                 | 2                          | SIN         | Input terminal of a data shift register. Data for R8 should be shifted in first, and then the data for G8 followed.                                                             |

| 7                                 | 3                          | CLK         | Input terminal of a clock for shift register. Data is sampled at the rising edge of CLK.                                                                                        |

| 8                                 | 4                          | LTH         | Input terminal of data strobe. Data is latched when LTH is low. And data on shift register goes through when LTH is high.                                                       |

| 9                                 | 5                          | EN          | Input terminal of output enable (active low), all outputs are off when EN is high.                                                                                              |

| 11, 14, 16, 19,                   | 7,9,11,13,                 | G1~8        | Constant current output terminals (Bank G).                                                                                                                                     |

| 21, 24, 26, 29                    | 15,17,19,21                |             |                                                                                                                                                                                 |

| 12, 15, 17, 20,<br>22, 25, 27, 30 | 8,10,12,14,<br>16,18,20,22 | R1~8        | Constant current output terminals (Bank R).                                                                                                                                     |

| 4, 10, 13, 18,<br>23, 28, 31      | 6,23,28                    | GND         | Ground terminals.                                                                                                                                                               |

| 32                                | 24                         | RESERVED    | Reserved pin for future.                                                                                                                                                        |

| 1                                 | 25                         | SOUT        | Output terminal of a data shift register.                                                                                                                                       |

| 2                                 | 26                         | GRES        | Input terminal of an external resistor (Bank G). The current flows through the resistor from GRES to ground will be the (Bank G) reference base current of output sink current. |

| 3                                 | 27                         | RRES        | Input terminal of an external resistor (Bank R).                                                                                                                                |

# **Block Diagram**

# **Equivalent Circuit of Inputs and Outputs**

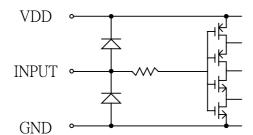

### 1. CLK, SIN, LTH, EN terminals

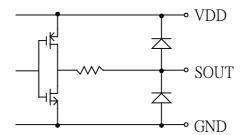

#### 2. SOUT terminal

# Maximum Ratings (Tj<sub>(max)</sub> = 150°C)

| CHARACTERISTIC       | SYMBOL   | RATING                   | UNIT |

|----------------------|----------|--------------------------|------|

| Supply Voltage       | Vdd      | 0 ~ 7.0                  | V    |

| Input Voltage        | Vin      | -0.3 ~ VDD+0.3           | V    |

| Output Current       | Iout     | 60                       | mA   |

| Output Voltage       | Vout     | -0.3 ~ 17                | V    |

| Clock Frequency      | fCLK     | 25                       | MHz  |

| GND Terminal Current | IGND     | 960                      | mA   |

|                      |          | 3.08 (QFN-32 : Ta=25°C)  |      |

| Power Dissipation    | PD       | 3.12 (SDIP-28 : Ta=25°C) | W    |

|                      |          | 1.1 (SSOP-28 : Ta=25°C)  | 1    |

|                      |          | 40.6 (QFN-32)            |      |

| Thermal Resistance   | Rth(j-a) | 40 (SDIP-28)             | °C/W |

|                      |          | 113.3 (SSOP-28)          | 1    |

| Storage Temperature  | Tstg     | -40 ~ 150                | °C   |

# **Recommended Operating Condition**

| CHARACTERISTIC        | SYMBOL    | CONDITION                      | MIN.   | TYP. | MAX.    | UNIT                   |

|-----------------------|-----------|--------------------------------|--------|------|---------|------------------------|

| Supply Voltage        | Vdd       | <del></del>                    | 3.0    | 5.0  | 5.5     | V                      |

| Output Voltage        | Vout      |                                |        |      | 17      | V                      |

| Operating temperature | $T_{OPR}$ | _                              | -20    |      | 85      | $^{\circ}\!\mathbb{C}$ |

|                       | Io        | (G, R)n                        | 5      |      | 60      |                        |

| Output Current        | Іон       | SOUT                           |        |      | 1.0     | mA                     |

|                       | IOL       | SOUT                           |        |      | -1.0    |                        |

| Input Voltage         | VIH       |                                | 0.8VDD |      | VDD+0.3 | V                      |

| input voitage         | VIL       |                                | -0.3   |      | 0.2VDD  | V                      |

| LTH Pulse Width       | tw LAT    |                                | 15     |      |         | ns                     |

| CLK Pulse Width       | tw CLK    |                                | 15     |      |         | ns                     |

| Set-up Time for DATA  | tsetup(D) | $VDD = 3.3 \sim 5.0 \text{ V}$ | 10     |      | _       | ns                     |

| Hold Time for DATA    | thold(D)  |                                | 10     |      |         | ns                     |

| Set-up Time for LTH   | tsetup(L) |                                | 15     |      |         | ns                     |

| Clock Frequency       | fCLK      | Cascade operation              |        |      | 25      | MHz                    |

### Electrical Characteristics (Typ:VDD = 5.0 V, Ta = 25°C unless otherwise noted)

| CHARACTERISTIC             | SYMBOL    | COND                                                                  | OITION                                   | MIN.    | TYP. | MAX.   | UNIT  |

|----------------------------|-----------|-----------------------------------------------------------------------|------------------------------------------|---------|------|--------|-------|

| Input Voltage "H" Level    | VIH       | _                                                                     |                                          | 0.8VDD  | _    | VDD    | V     |

| Input Voltage "L" Level    | VIL       | -                                                                     | _                                        | GND     | _    | 0.2VDD | v     |

| Output Leakage Current     | ЮН        | VOH = 17 V                                                            |                                          | _       | _    | ±1.0   | uA    |

| Output Voltage (SOUT)      | VOL       | IOL = 1.0  mA                                                         |                                          | _       | _    | 0.3    | V     |

| Output voltage (SOO1)      | VOH       | IOH = -1.0  mA                                                        |                                          | VDD-0.3 | _    | _      | v     |

| Output Current (Bit-Bit)   | IOL1      | $V(G, R)n = 1.0$ $RES = 11.2K\Omega$                                  |                                          |         | _    | ±6     | %     |

| Output Current (Chip-Chip) | 101.2     | V(G, R)n = 1.0V,                                                      | Vdd=5.0V                                 | 4.66    | 5.3  | 5.94   | mA    |

| Output Current (Cnip-Cnip) | IOL3      | RES = $11.2$ K $\Omega$                                               | Vdd=3.3V                                 | 4.57    | 5.2  | 5.83   |       |

| Output Voltage Regulation  | % / VDD   | RES = $1400\Omega$ , V                                                | RES = $1400\Omega$ , V(G, R)n = 1V to 3V |         | ±0.1 | ±0.5   | % / V |

| Supply Voltage Regulation  | % / VDD   | V(G, R)n = 1.0V,                                                      | $RES = 1400\Omega$                       | _       | ±1.5 | ±3.0   | % / V |

|                            | IDD(off)1 | Input Signal is sta<br>RES = OPEN, (G                                 |                                          | _       | 6    | _      |       |

| Supply Current "OFF"       | IDD(0ff)2 | Input Signal is static,<br>RES = $2800\Omega$ , (G, R) $1\sim8$ = off |                                          | _       | 9.5  | _      |       |

|                            | IDD(off)3 | Input Signal is static,<br>RES = $1400\Omega$ , (G, R) $1\sim8$ = off |                                          | _       | 12.5 | _      | mA    |

| g 1 g                      | IDD(on)1  | Input Signal is sta $RES = 2800\Omega$ , (C                           |                                          | _       | 9.5  | _      |       |

| Supply Current "ON"        | IDD(on)2  | Input Signal is sta $RES = 1400\Omega$ , (C                           |                                          | _       | 12.5 | _      |       |

# Switching Characteristics (Ta = 25 °C unless otherwise noted)

| CHARA                               | CTERISTIC                | SYMBOL | CONDITION                                           | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------|--------------------------|--------|-----------------------------------------------------|------|------|------|------|

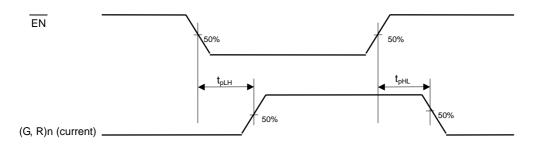

| Propagation Delay Time ("L" to "H") | EN-(G, R)n               | tpLH   | VDD=5.0V<br>VIH=VDD<br>VIL=GND                      | _    | 60   | _    | ns   |

| Propagation Delay Time ("H" to "L") | EN-(G, R)n               | tpHL   | $(G, R)RES=1400\Omega$<br>VL=3.3V<br>RL=51 $\Omega$ | _    | 30   | _    | ns   |

| Output Curren                       | t Rise Time              | tor    | CL=15pF                                             | _    | 90   | _    | ns   |

| Output Curren                       | Output Current Fall Time |        |                                                     | _    | 17   | _    | ns   |

| CHARA                               | CTERISTIC                | SYMBOL | CONDITION                            | MIN. | TYP. | MAX. | UNIT |

|-------------------------------------|--------------------------|--------|--------------------------------------|------|------|------|------|

| Propagation Delay Time ("L" to "H") | EN-(G, R)n               | tpLH   | VDD=3.3V<br>VIH=VDD<br>VIL=GND       |      | 90   | _    | ns   |

| Propagation Delay Time ("H" to "L") | EN-(G, R)n               | tpHL   | (G, R)RES=1400Ω<br>VL=3.3V<br>RL=51Ω |      | 35   | _    | ns   |

| Output Curren                       | t Rise Time              | tor    | CL=15pF                              | _    | 140  | _    | ns   |

| Output Curren                       | Output Current Fall Time |        |                                      | _    | 30   | _    | ns   |

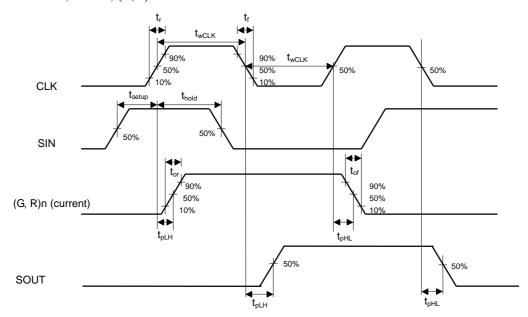

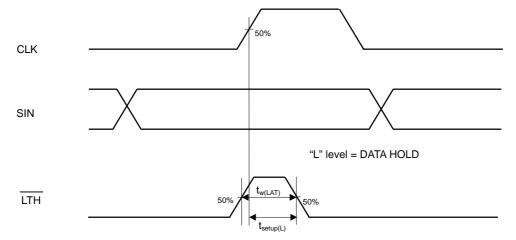

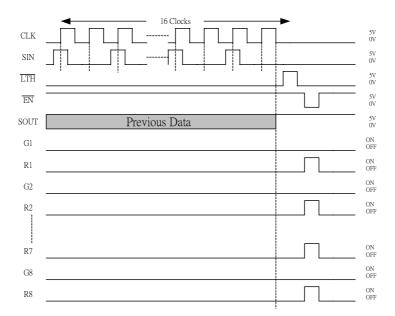

# **Timing Diagram**

### 1. CLK-SIN, SOUT, (G,R)n

### 2. CLK-LTH

### $3. \overline{EN}$ -(G, R)n

# **Detailed Description**

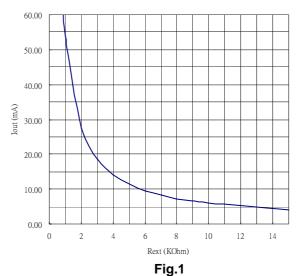

#### Constant Current Output Value Setting

The output current is determined by resistor value. The resistors connected between RES(G, R) pin and GND decide the base current output. Fig1. shows the approximate relation between resistor value and output current value. The resistor should be placed as close to Rext terminal as possible to avoid the noise influence

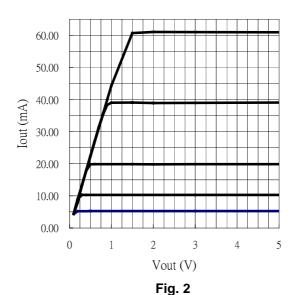

#### Output Current Performance vs. Output Voltage

In order to obtain the good constant current output performance, the minimum output voltage is necessary.

#### • Serial\_In Data, Serial\_Out and Latch

The SIN data will be clocked into the 16 bits shift register synchronized on the rising edge of CLK. And the data '1' represents the corresponding current output 'ON', while the data '0' stands for 'OFF'. The data will be transferred into the latch as the LTH pin goes high. And the data will be latched when LTH goes low. The SERIAL\_OUT data is shifted out on synchronization to the falling edge of CLOCK. The graph below depicts the timing of data serial-in and serial-out.

#### Package and Thermal Pad

The IC's thermal pad (QFN) which is internally connected to the bottom side of chip should be connected to GND. And, good PCB layout pattern conducted to thermal pad will have better performance in thermal effect. Due to the small size and low profile, the majority of heat generated by the die within this package is dissipated through the thermal pad to PCB. The PCB configuration and metal layers embedded in the PCB become important to achieving good thermal performance. By increasing the embedded copper area, the thermal performance will be improved. Thermal vias which conduct heat from the surface of the PCB to the ground plane are necessary. More vias may improve the package thermal performance.

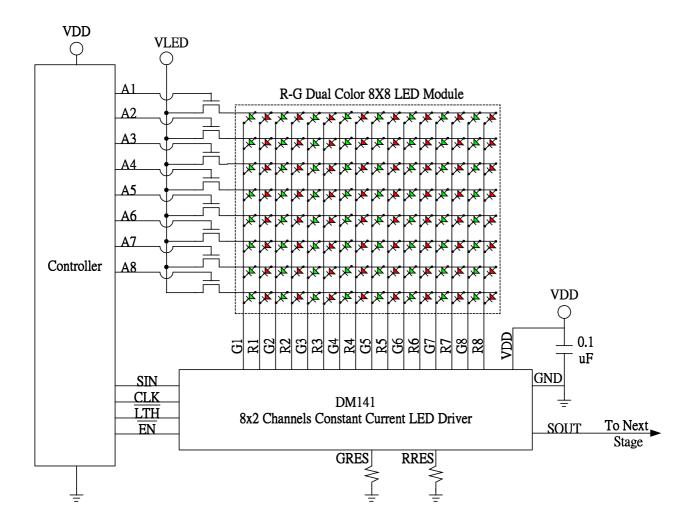

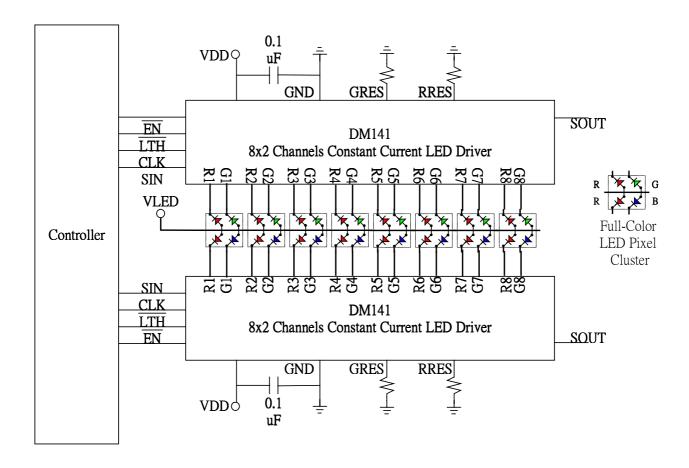

# **Typical Application**

# **Typical Application**

# **Package Outline**

QFN32

|        | DIMENSION |          |      | DIMENSION  |           |        |  |

|--------|-----------|----------|------|------------|-----------|--------|--|

| SYMBOL |           | (MM)     |      | (MIL)      |           |        |  |

|        | MIN.      | NOM.     | MAX. | MIN.       | NOM.      | MAX.   |  |

| A      | 0.70      | 0.75     | 0.80 | 27.6       | 29.5      | 31.5   |  |

| A1     | 0         | 0.02     | 0.05 | 0          | 0.79      | 1.97   |  |

| A3     | 0.25 REF  |          |      | 9.84 REF   |           |        |  |

| В      | 0.18      | 0.23     | 0.30 | 7.09       | 9.06      | 11.81  |  |

| D      |           | 5.00 BSC |      | 196.85 BSC |           |        |  |

| D2     | 1.25      | 2.70     | 3.25 | 49.21      | 106.30    | 127.95 |  |

| Е      |           | 5.00 BSC |      | 196.85 BSC |           |        |  |

| E2     | 1.25      | 2.70     | 3.25 | 49.21      | 106.30    | 127.95 |  |

| e      | 0.50 BSC  |          |      |            | 19.69 BSC |        |  |

| L      | 0.30      | 0.40     | 0.50 | 11.81      | 15.75     | 19.69  |  |

| у      | 0.10      |          |      |            | 3.94      |        |  |

Note: 1.DIMENSIONING AND TOLERANCING CONFORM TO ASME Y145.5M-1994.

2. REFER TO JEDEC STD. MO-220 WHHD-2 ISSUE A

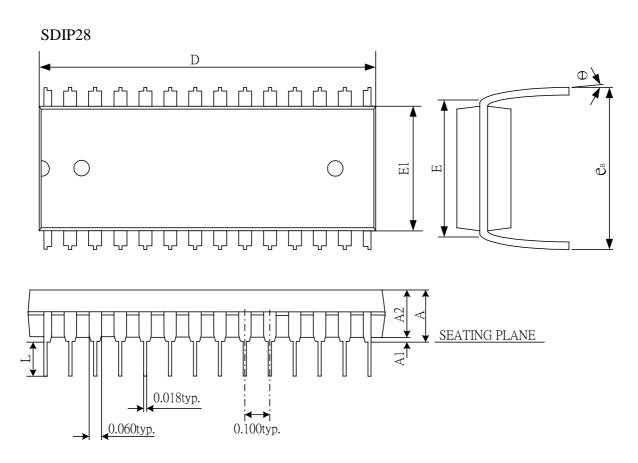

# **Package Outline**

| SYMBOLS  | DIMENSION IN INCH |          |       |  |  |

|----------|-------------------|----------|-------|--|--|

| SIMBOLS  | MIN.              | NOM.     | MAX.  |  |  |

| А        | -                 | -        | 0.210 |  |  |

| A1       | 0.015             | -        | ı     |  |  |

| A2       | 0.125             | 0.130    | 0.135 |  |  |

| D        | 1.385             | 1.390    | 1.400 |  |  |

| E1       | 0.283             | 0.288    | 0.293 |  |  |

| Е        |                   | 0.31 BSC | ,     |  |  |

| L        | 0.115             | 0.130    | 0.150 |  |  |

| ев       | 0.330             | 0.350    | 0.370 |  |  |

| $\theta$ | 0                 | 7        | 15    |  |  |

Note:

1. JEDEC OUTLINE: N/A

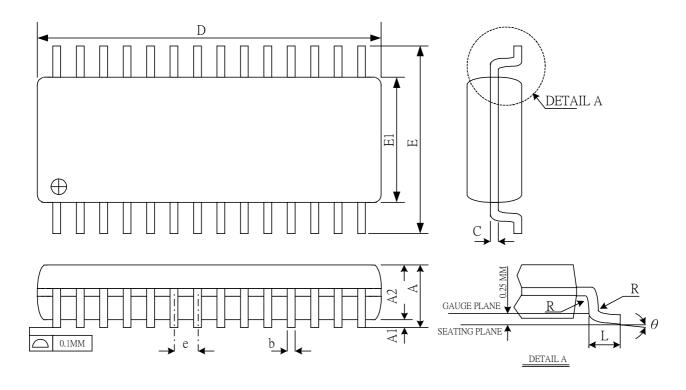

### **Package Outline**

#### SSOP28

#### NOTES:

1. JEDEC OUTLINE : MO-15D AH

2. DIMENSION D AND E1 DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS, BUT DOES INCLUDE MODE MISMATCH AND ARE MEASURED AT DATUM PLANE, MOLD PARTING LINE. MOLD FLASH OR PROTRUSION SHALL NOT EXCEED 0.2MM PER SIDE.

3.DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION/INTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.13mm TOTAL IN EXCESS OF b DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR INTRUSION SHALL NOT REDUCE DIMENSION b BY MORE THAN 9.07mm AT LEAST MATERIAL CONDITION.

| SYMBOLS  | DIMENSION IN MM |          |        |  |  |

|----------|-----------------|----------|--------|--|--|

| 21MDOL2  | MIN.            | NOM.     | MAX.   |  |  |

| А        | -               | -        | 2.0    |  |  |

| A1       | 0.05            | -        | -      |  |  |

| A2       | 1.62            | 1.75     | 1.85   |  |  |

| ь        | 0.22            | ı        | 0.38   |  |  |

| С        | 0.09            | -        | 0.25   |  |  |

| е        |                 | 0.65 BSC | (<br>, |  |  |

| D        | 9.9             | 10.20    | 10.50  |  |  |

| Е        | 7.4             | 7.8      | 8.2    |  |  |

| E1       | 5.00            | 5.30     | 5.60   |  |  |

| L        | 0.55            | 0.75     | 0.95   |  |  |

| R        | 0.09            | -        | -      |  |  |

| $\theta$ | 0               | 4        | 8      |  |  |

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.