# WESTERN DIGITAL

# DM1883A/B Direct Memory Access Controller

# FEATURES

- AUTOMATIC DAISY CHAINING OF BUS AND

INTERRUPT ACKNOWLEDGE SIGNALS

- AUTO LOAD OPTION

- SINGLE +5 VDC POWER SUPPLY

- 8 BIT BI-DIRECTIONAL DATA BUS

- TRUE OR COMPLEMENT DATA BUS

- 8 CPU ADDRESSABLE DMAC REGISTERS

- 8 CPU ADDRESSABLE DEVICE REGISTERS

- AUTOMATIC GENERATION OF DEVICE CS DURING DMA AND CPU DEVICE ACCESSES

- 256K MEMORY ADDRESSING

- 64K PROGRAMMABLE PAGE PROTECTION

- BYTE OR WORD DMA TRANSFERS

- INTERRUPT AND BUS REQUEST CAPABILITIES

- END-OF-BLOCK SHUT OFF BY DMAC

- TIME-OUT INTERRUPT CAPABILITY

- SINGLE CLOCK INPUT

- CS, RE, WE, A0-A3 ADDRESSING

- STOP REQUEST INPUT TO DELAY INTER-RUPT OR BUS REQUESTS

- COMPATIBLE WITH OUR FLOPPY DISC CONTROLLERS

- 8 BIT PROGRAMMABLE INTERRUPT ID CODE

#### **GENERAL DESCRIPTION**

The DM1883 Direct Memory Access Controller (DMAC) is packaged in a 40 pin standard dual inline package. The chip requires a single +5 power supply input and a single clock input. The device contains 8 CPU addressable registers, and allows for up to 8 CPU addressable device registers if the automatic device chip select feature is used. Byte or word transfers can be programmed, and all memory DMA operations are handshaked for compatibility with a variety of bus structures. Up to 256K bytes of memory can be accessed directly with 64K page protection and nonexistent memory interrupt as options. Bus and Interrupt Acknowledge signals are internally daisy chained, and a STOP REQUEST input prevents new requests while a current request is active. Device accesses are not handshaked, and a BUS HOLD feature is present for high speed devices. Device interrupt input, end-of-block output, and I/O read/write output pins simplify hardware interfacing to the device and the CPU bus. The AUTO LOAD feature allows automatic bootloading of up to 64K bytes or words into memory starting at location zero. An 8 bit interrupt ID code is also provided.

101010-01030

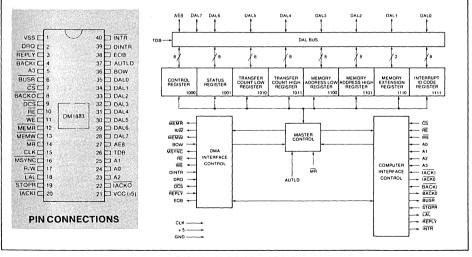

# DM1883 BLOCK DIAGRAM

AUGUST, 1980

SECH-OZ

# INTERFACE SIGNALS DESCRIPTIONS

| PIN<br>NUMBER | SIGNAL NAME      | SYMBOL | FUNCTION                                                                                                                                                                                                                                                                                                                           |

|---------------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | GROUND           | VSS    | Ground                                                                                                                                                                                                                                                                                                                             |

| 2             | DATA REQUEST     | DRQ    | Data service request input from the peripheral device. A DMA transfer is initiated when this signal goes high.                                                                                                                                                                                                                     |

| 3             | REPLY            | REPLY  | Active low bi-directional handshake signal for both CPU and DMA transfers.                                                                                                                                                                                                                                                         |

| 4             | BACK IN          | BACKI  | Bus acknowledge in. An active low input signal from the CPU or a previous device in the BACK daisy chain. When low this signal will initiate a DMA transfer if the DMAC was requesting a DMA cycle.                                                                                                                                |

| 5, 23, 24, 25 | REGISTER SELECTS | A0-A3  | These inputs select one of eight DMAC registers or one of eight device registers. When A3 is high the DMAC is selected. When A3 is low the DMAC is deselected and DCS is made low by the DMAC to activate device transfers. C5 input to the DMAC must be made low before either the DMAC or the device may be selected by the CPU. |

| 6             | BUS REQUEST      | BUSR   | Active low output signal to initiate a CPU bus request and<br>to latch A8-A15, A17 of the 18 bit DMA transfer address<br>from DAL0-DAL7, AE8 into an external register.                                                                                                                                                            |

| 7             | CHIP SELECT      | CS     | Active low chip select input signal for CPU controlled operations.                                                                                                                                                                                                                                                                 |

| 8             | BACK OUT         | BACKO  | Bus acknowledge out. An active low output signal used to pass BACKI along the daisy chain when the DMAC is not requesting a DMA cycle. This output is not affected by STOPR.                                                                                                                                                       |

| 9             | DEVICE SELECT    | DCS    | Active low device chip select output signal for CPU and DMAC controlled operations.                                                                                                                                                                                                                                                |

| 10            | READ ENABLE      | RE     | Active low bi-directional read enable for the DMAC and the device.                                                                                                                                                                                                                                                                 |

| 11            | WRITE ENABLE     | WE     | Active low bi-directional write enable for the DMAC and<br>the device. RE and WE are inputs during CPU controlled<br>operations, and outputs to the device during DMAC con-<br>trolled operations.                                                                                                                                 |

| 12            | MEMORY READ      | MEMR   | Active low output to initiate a memory read during DMA transfers to the peripheral device.                                                                                                                                                                                                                                         |

| 13            | MEMORY WRITE     | MEMW   | Active low output to initiate a memory write during DMA transfers from the peripheral device.                                                                                                                                                                                                                                      |

| 14            | MASTER RESET     | MR     | Active low master reset signal to initialize the DMAC.                                                                                                                                                                                                                                                                             |

| 15            | CLOCK            | CLK    | Clock input                                                                                                                                                                                                                                                                                                                        |

| 16            | MEMORY SYNC      | MSYNC  | Active low memory sync output to initiate a memory access during DMA transfers.                                                                                                                                                                                                                                                    |

| 17            | READ/WRITE       | R/W    | This output indicates the direction of transfer for the<br>peripheral device. High for device-to-memory transfers<br>(READ), and low for memory to device transfers (WRITE).<br>Tied directly to Control Register bit 4.                                                                                                           |

| 18            | LOAD ADDRESS LOW | LAL    | Active low output signal to latch A0-A7, A16 of the 18-bit<br>DMA transfer address from DAL0-DAL7, AE8 into an ex-<br>ternal register. BUSR and LAL are compatible with INTEL<br>8212 devices.                                                                                                                                     |

| PIN<br>NUMBER | SIGNAL NAME       | SYMBOL          | FUNCTION                                                                                                                                                                                                                                                                                                                                                                    |

|---------------|-------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19            | STOP REQUEST      | STOPR           | Active low input that prevents INTR and BUSR from going<br>low even if a request becomes active. An active INTR or<br>BUSR request will not be affected by this input going low.<br>This signal is used to speed up daisy chaining of bus and<br>interrupt acknowledge inputs, and to prevent new requests<br>while some other request is in the process of being serviced. |

| 20            | IACK IN           | IACKI           | Interrupt acknowledge in. An active <u>low</u> input signal from<br>the CPU or a previous device in the IACK daisy chain. The<br>DMAC is selected when INTR is low and this signal goes<br>low. If RE also goes low while the DMAC is selected via this<br>signal then the interrupt ID code is gated onto DAL0-DAL7.                                                       |

| 21            | POWER SUPPLY      | V <sub>CC</sub> | +5 VDC power supply input                                                                                                                                                                                                                                                                                                                                                   |

| 22            | IACK OUT          | IACKO           | Interrupt acknowledge out. An active low output signal used to pass IACKI along the daisy chain when the DMAC is not requesting an interrupt. This output is not affected by STOPR.                                                                                                                                                                                         |

| 26            | TRUE DATA BUS     | TDB             | This input selects a true data bus on the DAL lines when<br>high or open, and a complemented data bus on the DAL<br>lines when low.                                                                                                                                                                                                                                         |

| 27            | ADDRESS EXTENSION | AE8             | Address extension bit output. Used during DMA opera-<br>tions to extend the address to 18 bits. This bit is true if TDB is high and complemented if TDB is low.                                                                                                                                                                                                             |

| 28-35         | DATA ACCESS LINES | DAL0-DAL7       | An 8-bit bi-directional three-state bus for CPU and DMAC<br>controlled transfers to and from the DMAC. These signals<br>remain in a three-state mode if the peripheral device is<br>selected via A3 instead of the DMAC.                                                                                                                                                    |

| 36            | BYTE OR WORD      | BOW             | Byte or word DMA transfer mode input. When high mem-<br>ory addresses are incremented by one after every DMA<br>transfer. When low memory addresses are incremented<br>by two after every DMA transfer and the LSB of the memory<br>address is forced to zero.                                                                                                              |

| 37            | AUTO LOAD         | AUTLD           | Active high input to initiate a non-programmed 64K device to memory data transfer.                                                                                                                                                                                                                                                                                          |

| 38            | END OF BLOCK      | EOB             | Active high output to shut off the peripheral device when<br>the transfer count goes to zero.                                                                                                                                                                                                                                                                               |

| 39            | DEVICE INTERRUPT  | DINTR           | Interrupt service request input from the peripheral device.<br>An interrupt request is generated by the DMAC if this in-<br>put is high and the device interrupt enable bit in the com-<br>mand register is also set.                                                                                                                                                       |

| 40            | INTERRUPT REQUEST | INTR            | Active low interrupt service request output. This output<br>goes low if: 1) Any one of the three interrupt conditions is<br>active, and 2) The STOPR input is high, and 3) The corres-<br>ponding interrupt enable bit for the interrupting condition<br>is set.                                                                                                            |

ช อ.

NOTE: The following pins float when not active low and require an external pull-up resistor of 10 KΩ (or greater) to +5 VDC:

# INTR, REPLY, RE, WE, MEMR, MEMW, MSYNC

The following pins have internal 10 K pull-up resistors to +5 VDC:

# TBD, DRQ, DINTR

# WIRE-ORABLE SIGNALS

The following output signals can be wired together with a single common pull-up resistor if multiple DMAC chips exist on the same board:

MSYNC, MEMR, MEMW, INTR

# REGISTER SELECTION

A 4-bit address input (A0, A1, A2, A3) is used to select one of 8 internal DMAC registers or to generate a device chip select (DCS) output signal for selection of up to 8 peripheral device registers. The following table details the selection process.

|    | INPUTS |    | OUTPUT | SELECTED |     |                                         |

|----|--------|----|--------|----------|-----|-----------------------------------------|

| ĈŜ | A3     | A2 | A1     | A0       | DCS | REGISTER                                |

| L  | L      | x  | х      | x        | L   | One of 8 peripheral<br>device registers |

| L  | н      | L  | L      | L        | н   | DMAC control regis-<br>ter (0)          |

| L  | н      | L  | L      | н        | н   | DMAC status register (1)                |

| L  | н      | L  | н      | L        | н   | DMAC TC low register<br>(2)             |

| L  | н      | L  | н      | н        | н   | DMAC TC high regis-<br>ter (3)          |

| L  | н      | н  | L      | L        | н   | DMAC MA low regis-<br>ter (4)           |

| L  | н      | н  | L      | н        | н   | DMAC MA high regis-<br>ter (5)          |

| L  | н      | н  | н      | L        | н   | DMAC MA ext. regis-<br>ter (6)          |

| L  | н      | н  | н      | н.       | н   | DMAC ID code regis-<br>ter (7)          |

NOTE: L = Low voltage level, H = High voltage level, X = don't care.

# **REGISTER DEFINITIONS**

# TRANSFER COUNT REGISTER (TCR)

A 16-bit counter register that holds the two's complement of the transfer count (words or bytes) for DMA transfer operations. The low order 8 bits are in TC low, and the high order 8 bits are in TC high. The count is incremented by one after every DMA transfer. When the count reaches zero bit 3 of the Status Register is set to a one. If bit 3 in the Command Register is also a one then INTR will go low (providing STOPR is also high). TCR is set to a one on a MASTER RESET to allow a 64K transfer count during auto load.

#### MEMORY ADDRESS REGISTER (MAR)

An 18-bit counter register that occupies 3 DMA registers. Bits 0-7 are in MA low, bits 8-15 are in MA high, and bits 16-17 are in MA ext. The carry from bit 15 to 16 is enabled if and only if bit 6 of the Command Register is set to a one. If the BOW input pin is high then the MAR is incremented by one after every DMA transfer. If the BOW input pin is low then the MAR is incremented by two after every transfer and bit 0 is forced to a zero. This register is cleared to all zeros on a MASTER RESET.

During a DMA operation the DMA address is gated onto the DAL lines in two 9-bit bytes. The first byte out contains MAR 8-15 on DAL 0-7 and MAR 17 or AE8. The second byte out contains MAR 0-7 on DAL 0-7 and MAR 16 on AE8. The first byte is valid on the trailing edge of BUSR, and the second byte is valid on the trailing edge of LAL. Note that the address can easily be extended to 24 bits by decoding the address of the 2-bit extension register externally and gating the 6 unused bits into an external latch. This would give the system 16 Mbytes of addressing with either 65K or 256K bytes of paging.

|     | 7                                                                                                                                         | 6                                                                                                                                                                                                   | 5                                                                                                                                                                                                              | 5 4 |      | 2   | 1   | 0 |  |  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-----|---|--|--|

| N   | /A /                                                                                                                                      | AECE                                                                                                                                                                                                | HBUS                                                                                                                                                                                                           | IOM | TOIE | DIE | RUN |   |  |  |

| віт | SYMBOL                                                                                                                                    |                                                                                                                                                                                                     |                                                                                                                                                                                                                | N   |      |     |     |   |  |  |

| 0   | RUN                                                                                                                                       | Run/stop bit. A 1 places the DMAC in the run mode. A 0 terminates DMAC operat                                                                                                                       |                                                                                                                                                                                                                |     |      |     |     |   |  |  |

| 1   | DIE                                                                                                                                       | Device i                                                                                                                                                                                            | Device interrupt enable. A 1 allows a high input on DINTR to set the INTR output low.                                                                                                                          |     |      |     |     |   |  |  |

| 2   | TOIE                                                                                                                                      | Time-out interrupt enable. A 1 allows the time-out one-shot to set the INTR output<br>The time-out interrupt is set during a DMA transfer if REPLY does not go low of<br>5 usec of MSYNC going low. |                                                                                                                                                                                                                |     |      |     |     |   |  |  |

| 3   | TCIE                                                                                                                                      | CIE Transfer count zero interrupt enable. A 1 allows a zero in the transfer count register set the INTR output low.                                                                                 |                                                                                                                                                                                                                |     |      |     |     |   |  |  |

| 4   | IOM                                                                                                                                       | and a 0 s                                                                                                                                                                                           | Input or output mode. A 1 sets READ mode (from the peripheral device to mem and a 0 sets WRITE mode (from memory to the peripheral device). This bit also app as an ungated output on the $R\overline{W}$ pin. |     |      |     |     |   |  |  |

| 5   | HBUS Hold bus. A 1 informs the DMAC to hold onto the bus for the entire block instead releasing the bus after each byte or word transfer. |                                                                                                                                                                                                     |                                                                                                                                                                                                                |     |      |     |     |   |  |  |

#### DMAC CONTROL REGISTER (CR)

| BIT    | SYMBOL      | FUNCTION                                                                                                               |

|--------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 6<br>7 | AECE<br>N/A | Address extension carry enable. A 1 allows a carry from DMA address bit 15 to propo-<br>gate into bit 16.<br>Not used. |

NOTE: Bits 1, 2, 3 set INTR low on an active condition if and only if the STOPR input is high.

# DMAC STATUS REGISTER (SR)

|     | 7                                                                                                                  | 6                                                                                                    | 5                               | 4                               | 3                                                                     | 2                              | 1                             | 0            |  |  |  |

|-----|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------|-----------------------------------------------------------------------|--------------------------------|-------------------------------|--------------|--|--|--|

| BL  | JSY                                                                                                                | SY AECE HBUS IOM TCZI TOI DINT                                                                       |                                 |                                 |                                                                       |                                |                               |              |  |  |  |

| BIT | SYMBOL                                                                                                             | SYMBOL FUNCTION                                                                                      |                                 |                                 |                                                                       |                                |                               |              |  |  |  |

| 0   | BOW                                                                                                                | pin. A 1 b<br>after eac                                                                              | oit indicates b<br>h DMA transf | yte mode, an<br>er. A 0 bit ind | only bit that in<br>d the DMA me<br>icates word mo<br>d to a 0) after | mory address<br>ode, and the D | s is increment<br>MA memory a | ed by one    |  |  |  |

| 1   | DINT If set a device interrupt has occurred. This is a read/write bit. Resetting this bit to a ze will reset INTR. |                                                                                                      |                                 |                                 |                                                                       |                                |                               | t to a zero  |  |  |  |

| 2   | тоі                                                                                                                |                                                                                                      | me-out interr<br>reset INTR.    | upt has occu                    | irred. This is a                                                      | read/write b                   | it. Resetting th              | his bit to a |  |  |  |

| 3   | TCZI                                                                                                               | I If set a transfer count equals zero interrupt has occurred. A read only bit. Sets output when set. |                                 |                                 |                                                                       |                                |                               |              |  |  |  |

| 4   | IOM Input-output mode. This bit reflects the status of bit 4 in the Command Register. A only bit.                  |                                                                                                      |                                 |                                 |                                                                       |                                |                               | er. A read   |  |  |  |

| 5   | HBUS                                                                                                               | Hold bus                                                                                             | s. This bit refle               | ects the statu                  | is of bit 5 in the                                                    | e Command F                    | Register. A rea               | d only bit.  |  |  |  |

| 6   | AECE                                                                                                               |                                                                                                      | extension ca<br>. A read only   |                                 | This bit reflects                                                     | s the status o                 | f bit 6 in the C              | Command      |  |  |  |

| 7   | BUSY                                                                                                               |                                                                                                      | ata transfer no<br>ommand Reg   |                                 | . A read only bi                                                      | it that reflects               | the status of b               | it 0 (RUN)   |  |  |  |

NOTE: Bits 1, 2, 3 are set if the corresponding condition occurs. The enable bits in the CR affect only the INTR output, and not the Status Register.

# ID CODE REGISTER (IDR)

An 8-bit programmable interrupt ID code register that gives the system an efficient way to establish a jump or vector address during a DMAC interrupt. The register is cleared to all zeros during a MASTER RESET, and must be loaded by the program during system initialization. If INTR is low, and IACKI and RE go low then the <u>contents of this</u> register are gated onto DAL 0-7. IACKI and CS must not be allowed to be low at the same time.

# MASTER RESET

All register bits are reset to a zero during a MASTER RESET except the following which are set to ones: TCR bit 0, CR4, CR5, CR6, SR4, SR5, and SR6. This sets up the DMAC for a 64K transfer from the peripheral device to memory starting at address 0. The hold bus mode is also enabled. Execution of an Auto Load will begin DMA transfers under the above conditions.

# AUTO LOAD

If the AUTLD input is made active after a MASTER RESET then bits CR3, CR1, and CR0 are also set. This places the DMAC in run mode, and enables two of the interrupt conditions. The DMAC will initiate data transfers, and will continue until either the transfer count reaches zero or a device interrupt occurs. Either event will terminate transfers and generate an interrupt.

# WRITE PROTECT FEATURE

During CPU controlled transfers to the DMAC, if the RUN bit is set then any attempt to write into any of the Memory Address or Transfer Count registers will result in a NOP. REPLY will be made low in any case.

# **CPU CONTROLLED DATA TRANSFERS**

During a CPU controlled transfer the CPU must have control of the system bus. When a CPU cycle is

initiated the system decodes the address on the bus. If the DMAC or its associated peripheral device is selected then CS to the DMAC is made low. The DMAC looks at the A3 input. If A3 is low the peripheral device is selected, and DCS is made low. The DMAC will not respond to an active RE or WE if A3 is low, and the DAL bus will stay in a high impedance state. This allows the DMAC DAL bus and the device DAL bus to be tied together if the device DAL bus is also in a high impedence state when the device is not selected.

If A3 is high when  $\overline{CS}$  is low then the DMAC is selected and will respond to an active low  $\overline{RE}$  or  $\overline{WE}$ . A0-A2 selects the DMAC as described under the REGISTER SELECTION section. If  $\overline{RE}$  goes low the DMAC places the contents of the selected register on the DAL bus and activates  $\overline{REPLY}$  to inform the CPU that valid data is on the bus. If  $\overline{WE}$  goes low the DMAC gates the contents of the DAL bus into the selected register and activates  $\overline{REPLY}$  to inform the CPU that data has been accepted.

If the peripheral device has more than 8 registers, or the device has fewer than 8 registers and there are one or more auxiliary registers external to the device, then it may be easier for the user to separate DMAC and device chip selects. In this mode  $\overline{CS}$  to the DMAC is activated if and only if the DMAC is selected and A3 is tied to +5 VDC. The chip select to the device from a CPU controlled data transfer is ORed with  $\overline{DCS}$  out of the DMAC. In this mode  $\overline{DCS}$ will go low if and only if a DMA transfer is in effect and can be used by the controller as a "DMA ACTIVE" signal. Note that in any case actual data transfers to and from the CPU and the peripheral device are done by way of the device's DAL bus, not the DMAC's DAL bus.

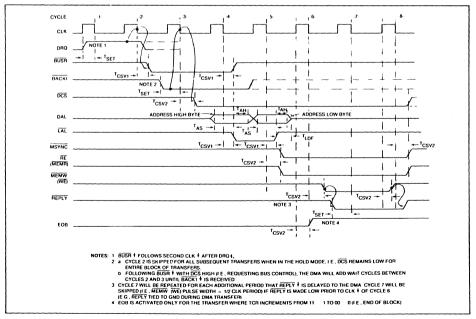

# DMAC CONTROLLED DATA TRANSFERS

When the DMAC is in RUN mode (CR0=1) it waits for a Data Request (DRQ) input from the peripheral device. When DRQ becomes active the <u>DMAC</u> requests the bus from the CPU by activating BUSR. If STOPR was active when <u>DRQ</u> went active then the DMAC would wait until ST<u>OPR</u> went high before activating BUSR. When <u>BACKI</u> goes low in response to an active <u>BUSR</u> the request has been granted and the DMAC controls data transfers between the peripheral device and memory. The direction of the transfer is determined by the status of the READ/WRITE (R/W) output pin. Note that R/W is tied directly to CR4.

# 1.) DEVICE-TO-MEMORY DMA TRANSFERS (CR4=1)

Once the DMAC has been granted the bus the following occurs:

A.) The DMAC places the high byte of the memory address on the DAL lines, activates DCS, and then raises BUSR. The trailing edge of BUSR can be used to latch the address into an external buffer.

- B.) The DMAC places the low byte of the memory address on the DAL lines while activating LAL, and then activates MSYNC. The trailing edge of LAL can be used to latch the address into an external buffer

- C.) The DAL lines are placed into a high impedence state in anticipation of a data transfer across the bus.

- D.) The DMAC activates  $\overline{\text{RE}}$  and then activates MEMW.

- E.) The DMAC waits for REPLY to go low. When REPLY is active the DMAC deactivates MEMW and then deactivates RE.

- F.) If the DMAC is not in hold bus mode (CR5=1) then the DMAC deactivates DCS and gives up control of the bus. If the DMAC is in hold bus mode then DCS remains low until after the completion of the final data transfer. Note that BUSR still cycles for every transfer.

- G.) After the completion of every data transfer the memory address register is incremented by one in byte mode or two in word mode.

- H.) After the completion of every data transfer the transfer count is incremented by one. Transfers are considered to be completed when the transfer count equals zero.

# 2.) MEMORY-TO-DEVICE DMA TRANSFERS (CR4=0)

Once the DMAC has been granted the bus it goes through the same steps as in the DEVICE-TO-MEMORY mode with the exception of steps "D" and "E" which are as follows:

- D.) The DMAC activates MEMR and then activates WE.

- E.) The DMAC waits for REPLY to go low. When REPLY is active the DMAC deactivates WE and then deactivates MEMR.

In either mode BACKI will be gated out to BACKO as soon as the DMAC deactivates DCS. This allows other devices in the chain to gain access to the bus immediately.

# INTERRUPTS

There are three individually enabled interrupt conditions. If any of the conditions occurs it will set its corresponding bit in the Status Register. If the appropriate enable bit in the Command Register is set then INTR is also activated. Note that these are independent functions. When INTR is active then the DMAC can be selected by an active IACKI instead of an active CS. CS and IACKI must not both be active at the same time.

ADDRESS BUS **BIDIRECTIONAL 8-BIT BUS** (HIGH BYTE) (LOW BYTE) 8-BIT 8-BIT 2-8T26 LATCH LATCH BUSR -BUS WE - RÊ 8212 8212 TRANSCEIVERS NOTE: EOB R/W, AND AUTLD ON THE DMAC ARE NOT USED AND NOT SHOWN. DMAIP AE8 4 LAL D0-D7 ADDRESS ĊŚ FLOPPY DAL BUS COMPARATOR D0-D7 DISK cs A0-A3-DCS INTERFACE ► cs INTR DINTR PSYNC FDC ÷ TDB DRQ DRQ DMAC 1771 HE BOW WE 1883 WE 1781 + 5 RE RE 179 X CLK -Q 510К A0· AC 7432 10K б10к 10K\$10K\$10K\$ MR DMAIP 9 7432 ۵ - CLK ξ 10K +5 A1 7404 INTR BUSR MSYNC WE REPLY MEMR MEMW DMAIP 8097 IACKO BACKO STOPR **IACKI** BACKI 7404 ٦ DCS DMAIP CS 7402 ł 7404 7402 BUSR DMAIP DMAREQ 8097 CREPLY (CPU MODE) -CS 1 REPLY -743 CS-Å CONTROL BUS

# TYPICAL DMAC TO FDC APPLICATION

N ZO--10MW

Once an interrupt condition sets its corresponding bit in the status register the bit stays set until a CPU write to the status register occurs with a zero in the bit position.<sup>•</sup> If any one (or more) of the three interrupt condition bits in the Status Register is set then IACKI will not be gated out to IACKO even if the interrupt is *not* enabled.

NOTE: For a transfer-count-equals-zero interrupt condition to be cleared the Transfer Count Register must be loaded with a non-zero count.

The three interrupt conditions are as follows:

#### 1.) DEVICE INTERRUPT (DINT)

A device interrupt condition occurs when the DINTR input is made high. This sets SR1 and, if CR1 is set, it activates INTR. The RUN bit is also reset thus terminating all subsequent DMA transfers. A device interrupt could be generated by a number of causes, and the program will have to test the device's Status Register to determine the cause of the interrupt. The DINT status bit in the DMAC Status Register must be cleared by the program as a part of the interrupt service routine.

# 2.) TRANSFER COUNT EQUALS ZERO INTERRUPT (TCZI)

When the TCR is incremented to zero after a DMA transfer the TCZI status bit (SR3) is set and the RUN bit (CR0) is reset. This terminates all DMA operations and, if CR3 is set, activates INTR. SR3 can be cleared only by loading a non-zero value into the TCR. The EOB output pin is high whenever SR3 is set.

#### 3.) TIME-OUT INTERRUPT (TOI)

During any DMA transfer the leading edge of MSYNC triggers an internal time delay of approximately 5 microseconds. If the DMAC does not receive an active low REPLY input within that time delay then the DMA operation is terminated, the RUN bit is reset, and the TOI status bit (SR2) is set. If CR2 is set then INTR is activated. SR2 can only be cleared by writing a zero into that position of the Status Register.

#### INTERRUPT OPERATION

When the DMAC activates INTR the CPU responds by activating IACKI. This signal can be daisy chained through all devices. The first device in the chain that has any bit in SR1-SR3 set will block the gating of IACKI out to IACKO. In addition, if INTR is active an IACKI will select the DMAC. An active RE after an IACKI select will gate the contents of the interrupt ID code register onto the DAL lines. The ID code stays active on the DAL lines as long as IACKI and RE are active. This code, which is cleared to zero by a MASTER RESET and loaded by the program during system initialization, can be used by the system to create a JUMP or VECTOR address for the device interrupt routine. Note that an active  $\overline{CS}$  during a DMAC select via an active IACKI will cause unspecified results. Note also that no condition can activate INTR unless its corresponding enable bit is set and STOPR is high. If STOPR is active when the interrupt condition occurs then the DMAC will hold INTR inactive until STOPR goes inactive. At that time the DMAC will activate INTR automatically.

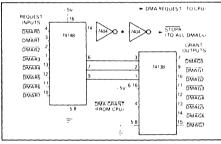

# DMA PRIORITY SYSTEMS

# **Fixed Priority**

A fixed priority can be established in two ways: through a parallel request-grant system or through a CPU controlled daisy chain system. A typical asynchronous parallel DMA priority system is shown. In this system any request generates an active STOPR, which is gated to all devices, and an active DMA request to the CPU. The CPU DMA grant generates a grant to the requesting device with the highest priority. If more than one request is received at the same time then the grants are honored from the highest to the lowest priority. In most cases, however, grants are not received simultaneously. The highest priority devices, therefore, will receive most of the immediate grants with the others being delayed by an active STOPR.

#### ASYNCHRONOUS PARALLEL DMA PRIORITY SYSTEM

Establishing a fixed priority system through a daisy chain approach requires the CPU monitor a "DMA IN PROGRESS" signal on the bus. This signal can be generated from DCS during a DMA transfer (i.e., DCS <u>CS</u>). In this mode the CPU activates BACKI and <u>STOPR</u> in response to some bus request. STOPR is tied to all <u>DMA</u> controllers to prevent new bus requests while BACKI is propagating through all non-requesting DMAC devices. When the requesting DMAC gains control over the bus and activates DCS the CPU drops BACKI\*. When DCS is deactivated the CPU deactivates <u>STOPR</u> to allow new requests. In this manner the device physically closest to the CPU on the daisy chain has highest priority for all request cycles.

NOTE: BACKI and STOPR can be dropped at the same time with no effect on the priority scheme, but the CPU may have to capture new requests until DCS goes high.

# **Rotating Priority**

This is a daisy chain approach that prevents one device from getting most of the bus grants if multiple devices are active at the same time. In this mode any device requesting the bus causes the CPU to activate BACKI. This signal is tied to the BACKI and STOPR inputs of the first DMAC. The BACKO output of the first DMAC goes to the BACKI and <u>STOPR</u> inputs of the second DMAC, and so on. The BACKO output of the last DMAC in the chain goes back to the CPU to reset its BACKI output. In this mode the first device cannot request again until all other requesting devices in the chain have also been serviced.

In any case, if the CPU has to have the DMA request held active throughout the DMA cycle then the user will have to create this signal on the controller thusly: DMAREQ = BUSR + (DCS $\cdot$ CS). If the device and DMAC chip selects are generated on the controller separately then the CS can be eliminated from the equation. It is needed only to distinguish a CPU chip select from a DMA cycle chip select. Note that in either case the second term in the equation is equivalent to "DMA CYCLE IN PROGRESS" (DMAIP).

#### SPECIFICATIONS

# Absolute Maximum Ratings

| Ambient Temperature Under Bias0°C to +70°C |

|--------------------------------------------|

| Voltage on Any Pin with Respect            |

| to Ground                                  |

| Power Dissipation 0.6 Watt                 |

# **DC Electrical Characteristics**

$T_A = 0^{\circ}C$  to +70°C;  $V_{CC} = 5.0V \pm 5\%$ ; GND =0V

NOTE: Maximum ratings indicate limits beyond which permanent damage may occur. Continuous operation at these limits is not intended and should be limited to those conditions specified under de electrical characteristics.

| SYMBOL          | PARAMETER            | MIN. | TYP.      | MAX. | UNIT | TEST CONDITIONS           |

|-----------------|----------------------|------|-----------|------|------|---------------------------|

| VIL             | Input Low Voltage    | -0.5 |           | 0.8  | V    |                           |

| VIH             | Input High Voltage   | 2.4  |           | Vcc  | V    |                           |

| VOL             | Output Low Voltage   |      |           | 0.45 | V    | I <sub>OL</sub> = 1.6 mA  |

| ∨он             | Output High Voltage  | 2.4  | D-State - |      | V    | I <sub>OH</sub> = -100 µA |

| I <sub>DL</sub> | Data Bus Leakage     |      |           | -50  | ДЦ   | $V_{IN} = 0.45V$          |

|                 |                      |      |           | 10   | μА   | VIN = VCC                 |

| Ι               | Input Leakage        |      |           | 10   | μА   | VIN = VCC                 |

| loc             | Power Supply Current |      | 45        | 90   | mA   |                           |

NOTE: VOL ≤0.4V when interfacing with low power Schottky parts (IOL <1 mA).

# Capacitance

$T_{A} = 25^{\circ}C; V_{CC} = GND = 0V$

| -           |                              |                   | MIN. | TYP.     | MAX.     |                                                               | TEST CONDITIONS |

|-------------|------------------------------|-------------------|------|----------|----------|---------------------------------------------------------------|-----------------|

|             | nput Capacita<br>O Capacitan |                   |      | 10<br>20 | pF<br>pF | f <sub>C</sub> = 1 MHz<br>Unmeasured pins<br>returned to GND. |                 |

| System Cloc | :k (CLK) Cha                 | racteristics      |      | L        |          |                                                               | I               |

| Maximum Fi  | requency                     | 2.0 MHz           |      |          |          |                                                               |                 |

| Minimum Pu  | ulse Width                   | 250 ns            |      |          |          |                                                               |                 |

| Maximum P   | ulse Width                   | 50% of duty cycle | 3    |          |          |                                                               |                 |

SECT

ę

2

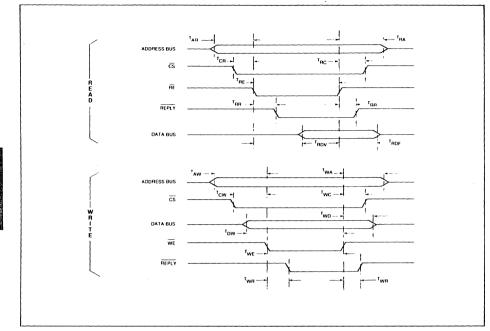

# CPU CONTROLLED TRANSFER

DMA CONTROLLED TRANSFER TIMING

# AC Electrical Characteristics

$T_{A} = 0^{\circ}C \text{ to } +70^{\circ}C; V_{CC} = 5.0V +5\%; \text{ GND} = 0V$

| SYMBOL                                                                                        | DESCRIPTION                                                                                                                                                                    | MIN            | M          | AX. ι               | JNIT      | COND                                   |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|---------------------|-----------|----------------------------------------|

| CPU CO                                                                                        | NTROLLED TRANSFER TIMING - READ                                                                                                                                                |                |            |                     |           |                                        |

| TAR                                                                                           | Address Valid to RE ¥                                                                                                                                                          | 80             |            |                     | ns        |                                        |

| TCR                                                                                           | CS to RE t                                                                                                                                                                     | 0              |            |                     | ns        |                                        |

| TRE                                                                                           | RE Pulse Width                                                                                                                                                                 | 300            |            |                     | ns        |                                        |

| TRDV                                                                                          | RE to Data Valid                                                                                                                                                               |                | 3          | 75                  | ns        | CL = 50 pF                             |

| TRR                                                                                           | RE + (4) to REPLY + (4)                                                                                                                                                        | 50             | 3          | 50                  | ns        | CL = 50 pF                             |

| TRA                                                                                           | Address Hold from RE                                                                                                                                                           | 30             |            |                     | ns        |                                        |

| TRC                                                                                           | CS Hold from RE 4                                                                                                                                                              | 0              |            |                     | ns        |                                        |

| TRDF                                                                                          | Data Float from RE↓                                                                                                                                                            |                | 2          | 00                  | ns        |                                        |

| CPU CO                                                                                        | NTROLLED TRANSFER TIMING - WRITE                                                                                                                                               |                |            |                     |           |                                        |

| TAW                                                                                           | Address Valid to WE t                                                                                                                                                          | 80             |            |                     | ns        |                                        |

| тсw                                                                                           | CS + to WE +                                                                                                                                                                   | 0              |            |                     | ns        |                                        |

| TDW                                                                                           | Data Valid to WE                                                                                                                                                               | 300            |            |                     | ns        | CL = 50 pF                             |

| TWE                                                                                           | WE Pulse Width                                                                                                                                                                 | 300            |            |                     | ns        |                                        |

| TWR                                                                                           | WE + (4) to REPLY + (4)                                                                                                                                                        | 50             | 3          | 50                  | ns        | CL = 50 pF                             |

| TWA                                                                                           | Address Hold from WE                                                                                                                                                           | 30             |            |                     | ns        |                                        |

| Twc                                                                                           | CS Hold from WE                                                                                                                                                                | 0              |            |                     | ns        |                                        |

| TWD                                                                                           | Data Hold from WE                                                                                                                                                              | 30             |            |                     | ns        |                                        |

| SYMBOL                                                                                        | DESCRIPTION                                                                                                                                                                    | MIN            | ТҮР        | MAX.                | UNIT      | COND                                   |

| DMA CO                                                                                        | NTROLLED TRANSFER TIMING                                                                                                                                                       |                |            |                     |           |                                        |

| TCSV1                                                                                         | Indicated CLK Edge to Indicate Signal Valid                                                                                                                                    |                | 150        | 250                 | ńs        | CL = 50 pF                             |

| TCSV2                                                                                         | Indicated CLK Edge to Indicated Signal Valid                                                                                                                                   |                | 250        | 400                 | ns        | CL = 50 pF                             |

| TAS                                                                                           | DAL Set Up to BUSR + or LAL + (4)                                                                                                                                              | 80             |            |                     | ns        | CL = 50 pF                             |

| TAH                                                                                           | DAL Hold from BUSR & or LAL # (4)                                                                                                                                              | 50             |            |                     | ns        | CL = 50 pF                             |

| TLDF                                                                                          | LAL 4 to DAL Float                                                                                                                                                             |                |            | 250                 | ns        | CL = 50 pF                             |

| TSET                                                                                          | Indicated Signal Setup to Indicated CLK Edge                                                                                                                                   | 80             |            | and the second      | ns        |                                        |

| MISCELI                                                                                       | LANEOUS TIMING ( T 1 CLOCK PERIOD)                                                                                                                                             |                |            | 1                   | J         |                                        |

|                                                                                               |                                                                                                                                                                                |                |            | Contract Grand Sec. | 100000000 |                                        |

|                                                                                               | o DCS ♦ ∯Propogation Delay                                                                                                                                                     |                |            |                     |           |                                        |

| (for A3 Ic                                                                                    | (wo                                                                                                                                                                            |                | 150        | 250                 | ns        | CL 50 pF                               |

| (for A3 Ic<br>IACKI † (<br>when No                                                            | w)<br>₩ to IACKO † (4) Propogation Delay<br>tt Requesting Interrupt                                                                                                            |                | 150<br>150 | 250<br>250          | ns<br>ns  |                                        |

| (for A3 lo<br>IACKI † (<br>when No<br>BACKI †                                                 | w)<br>∯ to IACKO † (♠ Propogation Delay<br>of Requesting Interrupt<br>(♣ to BACKO † ♠ Propogation Delay                                                                        |                | 150        |                     | ns        | CL = 50 pF<br>CL = 50 pF<br>CL = 50 pF |

| (for A3 Ic<br>IACKI † (<br>when No<br>BACKI †<br>when No                                      | w)<br>(4) to IACKO † (4) Propogation Delay<br>ot Requesting Interrupt<br>(4) to BACKO † (4) Propogation Delay<br>ot Requesting Bus                                             | 21             |            | 250                 |           | CL = 50 pF                             |

| (for A3 Ic<br>IACKI † (<br>when No<br>BACKI †<br>when No<br>MR Pulse                          | w)<br>(4) to IACKO ∳ (4) Propogation Delay<br>th Requesting Interrupt<br>(4) to BACKO ∳ (4) Propogation Delay<br>th Requesting Bus<br>e Width                                  | 2t<br>15       | 150        | 250                 | ns        | CL = 50 pF                             |

| (for A3 lo<br>IACKI † (<br>when No<br>BACKI †<br>when No<br>MR Pulse<br>DINTR, /              | w)<br>(#) to IACKO ∳ (#) Propogation Delay<br>th Requesting Interrupt<br>(#) to BACKO ∳ (#) Propogation Delay<br>th Requesting Bus<br>e Width<br>AUTLD, DRQ, REPLY Pulse Width | 1τ             | 150        | 250                 | ns        | CL = 50 pF                             |

| (for A3 lo<br>IACKI † (<br>when No<br>BACKI †<br>when No<br>MR Pulse<br>DINTR, /<br>BOW † (4) | w)<br>(4) to IACKO ∳ (4) Propogation Delay<br>th Requesting Interrupt<br>(4) to BACKO ∳ (4) Propogation Delay<br>th Requesting Bus<br>e Width                                  | Section States | 150        | 250                 | ns        |                                        |

NOTE: A 1 TTL load is assumed on all output signals

SUCTION 2

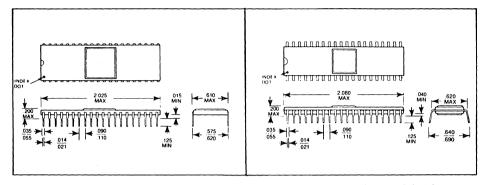

#### DM1883 CERAMIC PACKAGE

**DM1883 PLASTIC PACKAGE**

This is a preliminary specification with tentative device parameters and may be subject to change after final product characterization is completed.

Information furnished by Western Digital Corporation is believed to be accurate and reliable. However, no responsibility is assumed by Western Digital Corporation for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation for each of the western Digital Corporation or otherwise under any patent or patent rights of Western Digital Corporation. Western Digital Corporation responsibility at any time without notice.

WESTERN DIGITAL

3128 REDHILL AVENUE, BOX 2180 NEWPORT BEACH, CA 92663 (714) 557-3550,TWX 910-595-1139