March 1987

## DM85S06 Open-Collector DM75S07/DM85S07 TRI-STATE® DM75S07A/DM85S07A High Speed TRI-STATE Non-Inverting, 64-Bit (16 x 4) RAMs

### **General Description**

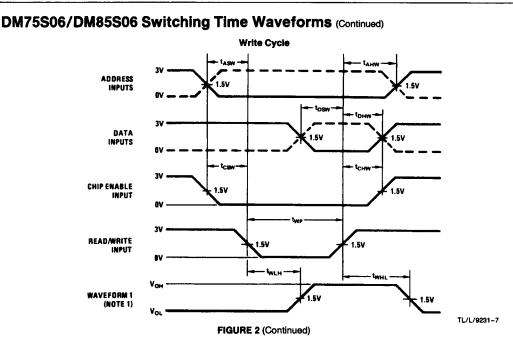

These 64-bit active-element memories are monolithic Schottky-clamped transistor-transistor logic (TTL) arrays organized as 16 words of 4 bits each. They are fully decoded and feature a chip-enable input to simplify decoding required to achieve the desired system organization. The memories feature PNP input transistors that reduce the low level input current requirement to a maximum of -0.25 mA, only one-eighth that of a DM54S/DM74S standard load factor. The chip-enable circuitry is implemented with minimal delay times to compensate for added system decoding.

The TRI-STATE output combines the convenience of an open-collector with the speed of a totem-pole output; it can be bus-connected to other similar outputs; yet it retains the fast rise time characteristics of the TTL totem-pole output. Systems utilizing data bus lines with a defined pull-up impedance can employ the open-collector DM85S06.

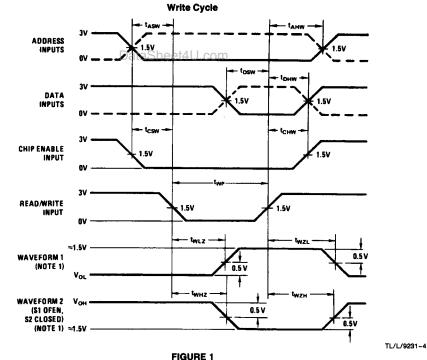

Write Cycle: The information at the data input is written into the selected location when both the chip-enable input and the read/write input are low. While the read/write input is the read/write input are low. While the read/write input is the location of the DM85S07 outputs are bus-connected, this high-impedance state will neither load nor drive the bus line, but it will allow the bus line to be driven by another active output or a passive pull-up if desired.

Read Cycle: The stored information is available at the outputs when the read/write input is high and the chip-enable

is low. When the chip-enable is high, the outputs will be in the high-impedance state.

The fast access time of the DM75S07A makes it particularly attractive for implementing high-performance memory functions requiring access times less than 25 ns. The high capacitive drive capability of the outputs permits expansion without additional output buffering. The unique functional capability of the DM75S07 outputs being at a high-impedance during writing, combined with the data inputs being inhibited during reading, means that both data inputs and outputs can be connected to the data lines of a bus-organized system without the need for interface circuits.

#### **Features**

- Schottky-clamped for high speed applications (75S07A)

Access from chip-enable input

Access from address inputs

17 ns max

25 ns max

- TRI-STATE outputs drive bus-organized systems and/or Unign capacitive loads

- DM85S06 is functionally equivalent and has open-collector outputs

- DM75SXX is guaranteed for operation over the full military temperature range of -55°C to +125°C

- Compatible with most TTL logic circuits

- Chip-enable input simplifies system decoding

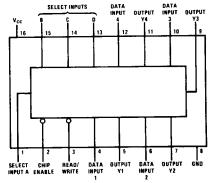

### **Connection Diagram**

### Dual-In-Line Package

TL/L/9231-1

#### **Truth Table**

|          | Inp             | uts            |                |

|----------|-----------------|----------------|----------------|

| Function | Chip-<br>Enable | Read/<br>Write | Output         |

| Write    | L               | L              | High-Impedance |

| Read     | L               | н              | Stored Data    |

| Inhibit  | Н               | Х              | High-Impedance |

H = High Level, L = Low Level, X = Don't Care

Order Number DM75S07J, DM75S07AJ, DM85S06J, DM85S07J, DM85S07AJ, DM85S06N, DM85S07N or DM85S07AN See NS Package Number J16A or N16E

www.DataSheet4U.com

DataSheet4U.com

**Top View**

et4U.co

| <b>Absolute Maximum Rat</b>                                                                                      | Operating Conditions |                                                 |                   |                   |            |  |  |  |

|------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------|-------------------|-------------------|------------|--|--|--|

| if Military/Aerospace specified de-<br>contact the National Semiconduc<br>Distributors for availability and spec | tor Sales Office/    | Supply Voltage (V <sub>CC</sub> )<br>DM75S07(A) | <b>Min</b><br>4.5 | <b>Max</b><br>5.5 | Units<br>V |  |  |  |

| Supply Voltage, V <sub>CC</sub>                                                                                  | 7.0V                 | DM85S06/DM85S07(A)                              | 4.75              | 5.25              | v          |  |  |  |

| input Voltage                                                                                                    | 5.5V                 | Temperature (T <sub>A</sub> )                   |                   |                   |            |  |  |  |

| Output Voltage                                                                                                   | 5.5V                 | DM75S07(A)<br>DM85S06/DM85S07(A)                | -55               | + 125             | °C         |  |  |  |

| Storage Temperature Range                                                                                        | -65°C to +150°C      | DM65506/DM65507(A)                              | 0                 | + 70              | °C         |  |  |  |

| Lead Temperature (Soldering, 10 sec.)                                                                            | +300°C               |                                                 |                   |                   |            |  |  |  |

# DM85S06, DM75S07/DM85S07, DM75S07A/DM85S07A Electrical Characteristics

over recommended operating free-air temperature range unless otherwise noted (Notes 2 and 3)

| Symbol          | Parameter                                               | Co                                                                     | enditions                                                            | Min | Тур  | Max  | Units |

|-----------------|---------------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------|-----|------|------|-------|

| V <sub>IH</sub> | High Level Input Voltage                                |                                                                        |                                                                      | 2   |      |      | V     |

| V <sub>IL</sub> | Low Level Input Voltage                                 |                                                                        |                                                                      |     |      | 0.8  | ٧     |

| V <sub>OH</sub> | High Level Output<br>Voltage                            | V <sub>CC</sub> = Min I <sub>OH</sub> = -2.0 mA,<br>DM75S07(A)         |                                                                      | 2.4 | 3.4  |      | ٧     |

|                 |                                                         |                                                                        | $I_{OH} = -5.2 \text{ mA},$ DM85S07(A)                               | 2.4 | 3.2  |      | ٧     |

| ICEX            | High Level Output Current                               | V <sub>CC</sub> = Min                                                  | V <sub>OH</sub> = 2.4V                                               |     |      | 40   | μА    |

|                 | Open-Collector Only                                     |                                                                        | V <sub>OH</sub> = 5.5V                                               |     |      | 100  | μА    |

| V <sub>OL</sub> | Low Level Output                                        | V <sub>CC</sub> = Min                                                  | I <sub>OL</sub> = 16 mA                                              |     |      | 0.45 | V     |

|                 | Voltage                                                 |                                                                        | I <sub>OL</sub> = 20 mA                                              |     |      | 0.5  | V     |

| liH             | High Level Input Current                                | V <sub>CC</sub> = Max, V                                               | / <sub>I</sub> = 2.4V                                                |     |      | 10   | μΑ    |

| l <sub>l</sub>  | High Level Input Current at Maximum Voltage             | V <sub>CC</sub> = Max, v                                               | nest40.com                                                           |     |      | 1.0  | mA    |

| I <sub>IL</sub> | Low Level Input Current                                 | V <sub>CC</sub> = Max, V                                               |                                                                      |     | -250 | μΑ   |       |

| los             | Short Circuit Output<br>Current (Note 4)                |                                                                        | V <sub>CC</sub> = Max, V <sub>O</sub> = 0V<br>DM75S07(A), DM85S07(A) |     |      | -90  | mA    |

| lcc             | Supply Current (Note 5)                                 | V <sub>CC</sub> = Max                                                  | V <sub>CC</sub> = Max                                                |     | 75   | 100  | mA    |

| V <sub>IC</sub> | Input Clamp Voltage                                     | V <sub>CC</sub> = Min, I <sub>1</sub>                                  | = -18 mA                                                             |     |      | -1.2 | mA    |

| lozh            | TRI-STATE Output Current,<br>High Level Voltage Applied | V <sub>CC</sub> = Max, V<br>DM75S07(A),                                | •                                                                    |     |      | 40   | μΑ    |

| lozL            | TRI-STATE Output Current,<br>Low Level Voltage Applied  | V <sub>CC</sub> = Max, V <sub>O</sub> = 0.4V<br>DM75S07(A), DM85S07(A) |                                                                      | -40 |      |      | μΑ    |

| C <sub>IN</sub> | Input Capacitance                                       | V <sub>CC</sub> = 5V, V <sub>IN</sub><br>T <sub>A</sub> = 25°C, 1      |                                                                      | 4   |      | ρF   |       |

| Co              | Output Capacitance                                      | $V_{CC} = 5V$ , $V_O = 2V$ , $T_A = 25^{\circ}C$ , 1 MHz Output "Off"  |                                                                      |     | 6    |      | pF    |

www.DataSheet4U.com

DataSheet4U.com

DM85S06/DM75S07/DM75S07A/DM85S07/DM85S07A

et4U.com

# DM75S07/DM85S07 Switching Characteristics

|                  |                                     | Conditions                       |                                             | DM75S07         | 1   | DM85S07 |                 |     |       |    |

|------------------|-------------------------------------|----------------------------------|---------------------------------------------|-----------------|-----|---------|-----------------|-----|-------|----|

| Symbol           | Parameter                           |                                  | Min                                         | Typ<br>(Note 1) | Max | Min     | Typ<br>(Note 1) | Max | Units |    |

| t <sub>AA</sub>  | Access Time from Addre              | ess                              | ]                                           |                 | 25  | 50      |                 | 25  | 35    | ns |

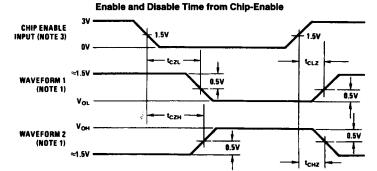

| t <sub>CZH</sub> | Output Enable Time to<br>High Level | Access Times from<br>Chip-Enable |                                             |                 | 12  | 25      |                 | 12  | 17    | ns |

| <sup>t</sup> CZL | Output Enable Time to<br>Low Level  |                                  | $C_L = 30 \text{ pF},$<br>$R_L = 280\Omega$ |                 | 12  | 25      |                 | 12  | 17    | ns |

| twzн             | Output Enable Time to<br>High Level | Sense Recovery Times             | (Figure 4)                                  |                 | 13  | 35      |                 | 13  | 25    | ns |

| t <sub>WZL</sub> | Output Enable Time to<br>Low Level  | from Read/Write                  |                                             |                 | 13  | 35      |                 | 13  | 25    | ns |

| <sup>†</sup> CHZ | Output Disable Time from High Level | Disable Times from               |                                             |                 | 12  | 25      |                 | 12  | 17    | ns |

| <sup>t</sup> CLZ | Output Disable Time from Low Level  | Chip-Enable                      | $C_L = 5 \text{ pF},$<br>$R_I = 280\Omega$  |                 | 12  | 25      |                 | 12  | 17    | ns |

| t <sub>WHZ</sub> | Output Disable Time from High Level | Disable Times from               | (Figure 4)                                  |                 | 15  | 35      |                 | 15  | 25    | ns |

| t <sub>WLZ</sub> | Output Disable Time from Low Level  | Read/Write                       |                                             |                 | 15  | 35      |                 | 15  | 25    | ns |

| t <sub>WP</sub>  | Width of Write Enable P             | ulse (Read/Write Low)            |                                             | 25              |     |         | 25              |     |       | ns |

| t <sub>ASW</sub> | Set-Up Time (Figure 1)              | Address to Read/Write            |                                             | 0               |     |         | 0               |     |       | ns |

| tosw             |                                     | Data to Read/Write hee           | t4U.com                                     | 25              |     |         | 25              |     |       | ns |

| tcsw             |                                     | Chip-Enable to<br>Read/Write     |                                             | 0               |     |         | 0               |     |       | ns |

| t <sub>AHW</sub> | Hold Time (Figure 1)                | Address from Read/Write          |                                             | 0               |     |         | 0               |     |       | ns |

| t <sub>DHW</sub> |                                     | Data from Read/Write             |                                             | 0               |     |         | 0               |     |       | ns |

| tchw             |                                     | Chip-Enable from<br>Read/Write   |                                             | 0               |     |         | 0               |     |       | ns |

DataSheet4U.com

www.DataSheet4U.com

# <code>DM75S07A/DM85S07A Switching Characteristics</code> over recommended operating ranges of $T_A$ and $V_{CC}$ unless otherwise noted

|                  |                                     |                                   |                                             | DM75S07/ | <u> </u>        |     | DM85S07 | <b>.</b>        | Units   |     |

|------------------|-------------------------------------|-----------------------------------|---------------------------------------------|----------|-----------------|-----|---------|-----------------|---------|-----|

| Symbol           | Parameter                           |                                   | Conditions                                  | Min      | Typ<br>(Note 1) | Max | Min     | Typ<br>(Note 1) |         | Max |

| t <sub>AA</sub>  | Access Time from Addr               | ess                               |                                             |          | 20              | 30  |         | 20              | 25      | ns  |

| <sup>t</sup> CZH | Output Enable Time to<br>High Level | Access Times from                 |                                             |          | 12              | 25  |         | 12              | 17      | ns  |

| t <sub>CZL</sub> | Output Enable Time to<br>Low Level  | Chip-Enable                       | $C_L = 30 \text{ pF},$<br>$R_L = 280\Omega$ |          | 12              | 25  |         | 12              | 17      | ns  |

| <sup>t</sup> WZH | Output Enable Time to<br>High Level | Sense Recovery Times              | (Figure 4)                                  |          | 13              | 35  |         | 13              | ¿<br>25 | ns  |

| t <sub>WZL</sub> | Output Enable Time to<br>Low Level  | from Read/Write                   |                                             |          | 13              | 35  |         | 13              | 25      | ns  |

| <sup>t</sup> CHZ | Output Disable Time from High Level | Disable Times from<br>Chip-Enable |                                             |          | 12              | 25  |         | 12              | 17      | ns  |

| tCLZ             | Output Disable Time from Low Level  |                                   | $C_L = 5  pF,$<br>$R_L = 280 \Omega$        |          | 12              | 25  |         | 12              | 17      | ns  |

| twHZ             | Output Disable Time from High Level | Disable Times from                | (Figure 4)                                  |          | 15              | 35  |         | 15              | 25      | ns  |

| t <sub>WLZ</sub> | Output Disable Time from Low Level  | Read/Write                        |                                             |          | 15              | 35  |         | 15              | 25      | ns  |

| t <sub>WP</sub>  | Width of Write Enable P             | ulse (Read/Write Low)             |                                             | 25       |                 |     | 20      |                 |         | ns  |

| tasw             | Set-Up Time (Figure 1)              | Address to Read/Write             |                                             | 0        | ·               |     | 0       |                 |         | ns  |

| tosw             |                                     | Data to Read/Write Data           | Sheet4U.c                                   | 25       |                 |     | 20      |                 |         | ns  |

| tcsw             |                                     | Chip-Enable to<br>Read/Write      |                                             | 0        |                 |     | 0       |                 |         | ns  |

| t <sub>AHW</sub> | Hold Time (Figure 1)                | Address from Read/Write           |                                             | 0        |                 |     | 0       |                 |         | ns  |

| t <sub>DHW</sub> |                                     | Data from Read/Write              |                                             | 0        |                 |     | 0       |                 |         | ns  |

| tchw             |                                     | Chip-Enable from<br>Read/Write    |                                             | 0        |                 |     | 0       |                 |         | ns  |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device

Note 2: Unless otherwise specified min/max limits apply across the --55°C to +125°C temperature range for the DM75S07(A) and across the 0°C to +70°C range for the DM85S07(A). All typicals are given for  $V_{CC} = 5.0V$  and  $T_A = 25$ °C.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: I<sub>CC</sub> is measured with all inputs grounded; and the outputs open.

www.DataSheet4U.com

DataSheet4U.com

et4U.com

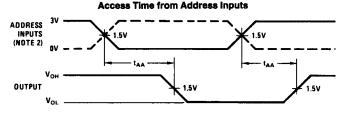

## DM75S07(A)/DM85S07(A) Switching Time Waveforms

ACCESS Time from Address Inputs

ADDRESS INPUTS (NOTE 2) OV 1.5V

OUTPUT 1.5V

1.5V

TL/L/9231-3

TL/L/9231-2

DataShe

Note 1: Waveform 1 is for the output with internal conditions such that the output is low except when disabled. Waveform 2 is for the output with internal conditions such that the output is high except when disabled.

Note 2: When measuring delay times from address inputs, the chip-enable input is low and the read/write input is high.

www.DataSheet4U.com

Note 3: When measuring delay times from chip-enable input, the address inputs are steady-state and the read/write input is high.

Note 4: Input waveforms are supplied by pulse generators having the following characteristics:  $t_r \le 2.5$  ns,  $t_f \le 2.5$  ns, PRR  $\le 1$  MHz and  $Z_{OUT} = \approx 50\Omega$ .

DataSheet4U

### over recommended operating ranges of TA and VCC unless otherwise noted

| Symbol            |                                  | Conditions                          | DM75S06                                                                        |                 |     |     | DM85S06         |     |       |    |

|-------------------|----------------------------------|-------------------------------------|--------------------------------------------------------------------------------|-----------------|-----|-----|-----------------|-----|-------|----|

|                   | Parameter                        |                                     | Min                                                                            | Typ<br>(Note 1) | Max | Min | Typ<br>(Note 1) | Max | Units |    |

| t <sub>AA</sub>   | Access Times from Address        |                                     |                                                                                | 25              | 50  |     | 25              | 35  | ns    |    |

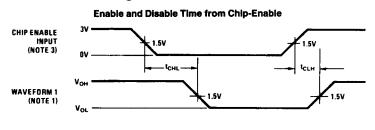

| t <sub>CHL</sub>  | Enable Time from<br>Chip-Enable  |                                     | $C_{L} = 30 \text{ pF},$ $R_{L1} = 300\Omega,$ $R_{L2} = 600\Omega$ (Figure 4) |                 | 12  | 25  |                 | 12  | 17    | ns |

| twHL.             | Enable Time from Read/Write      | Sense Recovery Time from Read/Write |                                                                                | ٠.              | 13  | 35  |                 | 13  | 25    | ns |

| t <sub>CLH</sub>  | Disable Time from<br>Chip-Enable |                                     |                                                                                |                 | 12  | 25  |                 | 12  | 20    | ns |

| twLH              | Disable Time from Read/Write     |                                     |                                                                                |                 | 13  | 35  |                 | 13  | 25    | ns |

| twp               | Width of Write Enable P          | ulse (Read/Write Low)               |                                                                                | 25              |     |     | 25              |     |       | ns |

| tasw              | Set-Up Time (Figure 2)           | Address to Read/Write               |                                                                                | 0               |     |     | 0               |     |       | ns |

| n <sub>tosw</sub> |                                  | Data to Read/Write                  |                                                                                | 25              |     |     | 25              |     |       | ns |

| tcsw              |                                  | Chip-Enable to<br>Read/Write        |                                                                                | 0               |     |     | 0               |     |       | ns |

| tAHW              | Hold Time (Figure 2)             | Address from Read/Write             |                                                                                | 0               |     |     | 0               |     |       | ns |

| <sup>t</sup> DHW  |                                  | Data from Read/Write                |                                                                                | 0               |     |     | 0               |     |       | ns |

| t <sub>CHW</sub>  |                                  | Chip-Enable from<br>Read/Write      |                                                                                | 0               |     |     | 0               |     |       | ns |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Temperature Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Unless otherwise specified min/max limits apply across the  $-55^{\circ}$ C to  $+125^{\circ}$ C temperature range for the DM75S07(A) and across the 0°C to  $+70^{\circ}$ C range for the DM85S07(A). All typicals are given for  $V_{CC} = 5.0V$  and  $T_A = 25^{\circ}$ C.

Note 3: All currents into device pins shown as positive, out of device pins as negative, all voltages referenced to ground unless otherwise noted. All values shown as max or min on absolute value basis.

Note 4: Only one output at a time should be shorted.

Note 5: I<sub>CC</sub> is measured with all inputs grounded; and the outputs open.

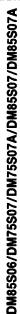

### DM75S06/DM85S06 Switching Time Waveforms

FIGURE 2

TL/L/9231-6 WWW.DataSheet4U.com

TL/L/9231-5

2

DataSheet4U.com

et4U.com

Note 1: Waveform 1 is for the output with internal conditions such that the output is low except when disabled.

Note 2: When measuring delay times from address inputs, the chip-enable input is low and the read/write input is high.

Note 3: When measuring delay times from chip-enable input, the address inputs are steady-state and the read/write input is high.

Note 4: Input waveforms are supplied by pulse generators having the following characteristics: t₁ ≤ 2.5 ns, t₁ ≤ 2.5 ns, PRR ≤ 1 MHz and Z<sub>OUT</sub> ≈ 50Ω.

DataSheet4U.com

www.DataSheet4U.com

DataShe

et4U.com

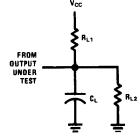

### DM75S06/DM85S06 Vcc

TL/L/9231-9

TL/L/9231-10

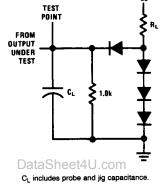

### DM75S07(A)/DM85S07(A)

All diodes are 1N3064.

FIGURE 4

DataSheet4U.com

www.DataSheet4U.com