# DM7820/DM9820 User's Manual

Versatile High Speed Digital I/O

>(Real Time Devices)

RTD Embedded Technologies, Inc. "Accessing the Analog World"®

> BDM-610010036 Rev B

ISO9001 and AS9100 Certified

# DM7820/DM9820 User's Manual

RTD EMBEDDED TECHNOLOGIES, INC. 103 Innovation Blvd State College, PA 16803-0906

> Phone: +1-814-234-8087 FAX: +1-814-234-5218

E-mail sales@rtd.com techsupport@rtd.com

Web Site <u>http://www.rtd.com</u>

#### Manual Revision History

- Rev A Initial Release

- Rev B Better DREQ description on page 40. Improved description of FIFO on page 12. Improved description of FIFOn\_CON\_STAT on page 41. Corrected PWM Period formula on page 55. Added DM9820 information.

#### Published by:

RTD Embedded Technologies, Inc. 103 Innovation Boulevard State College, PA 16803

Copyright 2009 by RTD Embedded Technologies, Inc. All rights reserved

Specification and features described in this manual may change without notice.

The RTD Embedded Technologies Logo is a registered trademark of RTD Embedded Technologies. dspModule, cpuModule, and utilityModule are trademarks of RTD Embedded Technologies. PC/104, PC/104-Plus, PCI-104, PC/104-Express, and PCIe/104 are registered trademark of PC/104 Consortium. All other trademarks appearing in this document are the property of their respective owners.

# **Table of Contents**

| Introduction                                                                                                                                        | 1           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Product Overview<br>Board Features<br>Digital I/O<br>Deep FIFOs with DMA                                                                            | 1<br>1<br>1 |

| Pulse Width Modulators                                                                                                                              |             |

| Advanced Interrupts<br>Programmable Clocks                                                                                                          | 2           |

| 82C54 Timer/Counters<br>Physical Attributes                                                                                                         | 2           |

| Available Options                                                                                                                                   |             |

| Getting Technical Support                                                                                                                           |             |

| Block Diagram                                                                                                                                       |             |

| Connector and Jumper Locations                                                                                                                      | 5           |

| DM9820<br>External I/O Connections<br>Connector CN10 – Digital Input / Output                                                                       | 6           |

| Connector CN11 – Digital Input / Output<br>PC/104 ISA Connectors –DM7820                                                                            | 7           |

| PC/104-Express Bus Connectors–DM9820<br>PC/104-Plus PCI Connector                                                                                   | 8<br>8      |

| PCI Configuration Options (DM7820 Only)<br>Switch SW1 – PCI Slot Selector<br>Jumper JP2 – Bus Master Control<br>Solder Blob B1 – Force Three Master | 9<br>9      |

| Board Installation                                                                                                                                  |             |

| Installing the Hardware                                                                                                                             | 0<br>0      |

| Functional Overview                                                                                                                                 | 2           |

| Internal Architecture       1         FIFOs       1         Board Interrupts       1         Advanced Triggering Examples       1                   | 2<br>3      |

| Board Operation and Programming                                                                                                                     |             |

| PCI Interface                                                                                                                                       | 6<br>6<br>6 |

| FPGA_VERSION                                                                                                                                        | 7<br>7<br>7 |

| INT_ENABLE                           |      |

|--------------------------------------|------|

| INT_STATUS                           | . 29 |

| Standard I/O                         |      |

| PORTx_OUTPUT                         |      |

| PORTx_INPUT                          |      |

| PORTx_TRISTATE                       |      |

| PORTX_MODE                           |      |

| PORTx_PERIPH_SEL_L                   | . 33 |

| PORTx_PERIPH_SEL_H                   |      |

| STROBE_STATUS                        | . 34 |

| 82C54 Timer Counter Control          |      |

| TC_ID                                |      |

| TC_INT                               |      |

| TC_xy_CONTROL                        |      |

| FIFO Channel n                       |      |

| FIFOn_ID                             |      |

| FIFOn_INT                            |      |

| FIFOn_IN_CLK                         |      |

| FIFOn_OUT_CLK                        |      |

| FIFOn_IN_DATA_DREQ                   |      |

| FIFOn_CON_STAT                       | . 41 |

| FIFOn_RW_PORT                        |      |

| Programmable Clock n                 | . 41 |

| PROGCLKn_ID                          | . 42 |

| PROGCLKn_MODE                        | . 42 |

| PRGCLKn_CLK                          |      |

| PRGCLKn_START_STOP                   | . 43 |

|                                      | . 45 |

| Advanced Interrupt n                 | . 46 |

| ADVINTn_ID                           |      |

| ADVINTn_INT_MODE                     | . 46 |

| ADVINTn_CLK                          | . 47 |

| ADVINTN PORTX MASK                   | . 47 |

| ADVINTn PORTx CMP                    | . 48 |

| ADVINTN PORTX CAPT                   | . 48 |

| Dual Incremental Encoder n           |      |

| INCENCn ID                           | 49   |

|                                      | . 50 |

| INCENCn CLK                          |      |

| INCENCn MODE                         |      |

| INCENCn_VALUEy                       | . 52 |

| Quad Pulse Width Modulator n         |      |

| PWMn ID                              | . 54 |

| PWMn_MODE                            |      |

| PWMn <sup>-</sup> CLK                |      |

| PWMn <sup>¬</sup> PERIOD             |      |

| PWMn WIDTHx                          |      |

| 82C54 Timer Counter n                |      |

| DESCRIPTION OF OPERATION             |      |

| Control Word and Count Value Program |      |

| Mode definition                      |      |

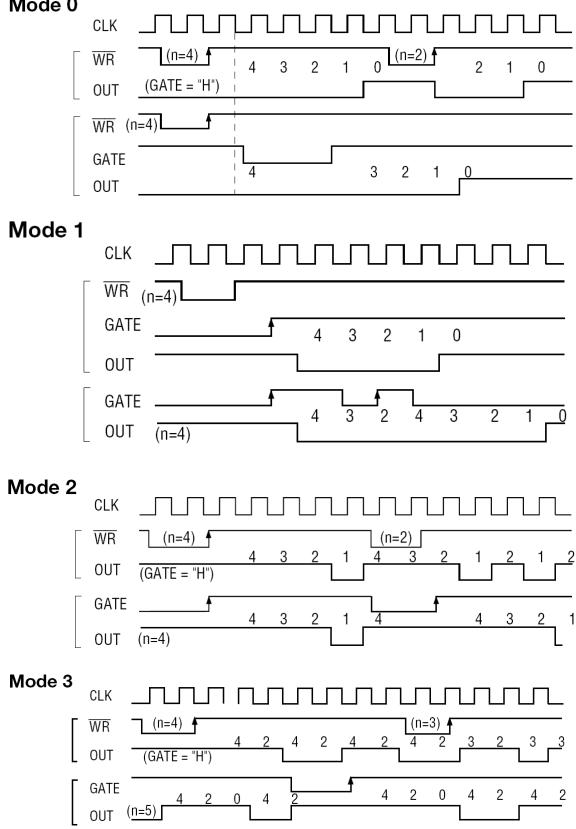

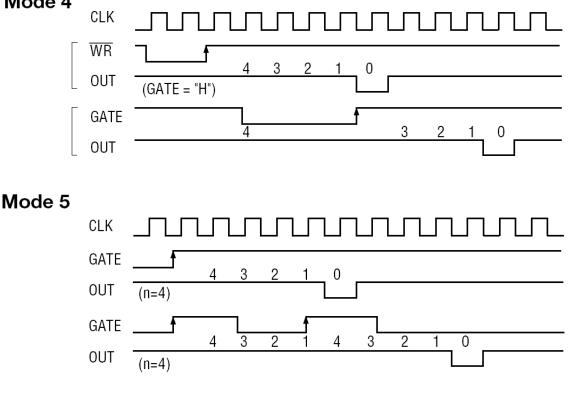

| Mode 0                               |      |

| Mode 1                               |      |

| Mode 2                               |      |

| Mode 3                               |      |

| Mode 4                               |      |

|                                      | -    |

| Reading Counter Values       62         Direct reading.       62         Counter latching.       62         Read Back Command Operation.       63         PLX Registers       66         Memory Map Overview       66         DMA Register Description       67 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Counter latching                                                                                                                                                                                                                                                |

| Read Back Command Operation                                                                                                                                                                                                                                     |

| PLX Registers                                                                                                                                                                                                                                                   |

| Memory Map Overview                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                 |

| DMA Register Description 67                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                 |

| DMAMODEn                                                                                                                                                                                                                                                        |

| DMAPADRn                                                                                                                                                                                                                                                        |

| DMALAPADRn                                                                                                                                                                                                                                                      |

| DMASIZn                                                                                                                                                                                                                                                         |

| DMAPRn70                                                                                                                                                                                                                                                        |

| DMACSRn                                                                                                                                                                                                                                                         |

| DMAARB                                                                                                                                                                                                                                                          |

| DMATHR                                                                                                                                                                                                                                                          |

| DMADAn                                                                                                                                                                                                                                                          |

| INTCSR                                                                                                                                                                                                                                                          |

| Additional Information                                                                                                                                                                                                                                          |

| PLX PCI9056                                                                                                                                                                                                                                                     |

| 82C54 Timer/Counter Programming                                                                                                                                                                                                                                 |

| Interrupt Programming                                                                                                                                                                                                                                           |

|                                                                                                                                                                                                                                                                 |

| DC Characteristics                                                                                                                                                                                                                                              |

| Absolute Maximum Ratings                                                                                                                                                                                                                                        |

| DC Input / Output Levels                                                                                                                                                                                                                                        |

| Limited Warranty79                                                                                                                                                                                                                                              |

# Table of Figures

| Figure 1: DM7820/DM9820 Block Diagram                                         | 4    |

|-------------------------------------------------------------------------------|------|

| Figure 2: Digital I/O Block Diagram                                           | . 12 |

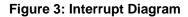

| Figure 3: Interrupt Diagram                                                   | . 14 |

| Figure 4: Digital I/O Block Diagram                                           | . 31 |

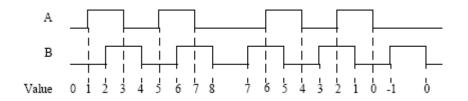

| Figure 5: Incremental Encoder Signals                                         | . 49 |

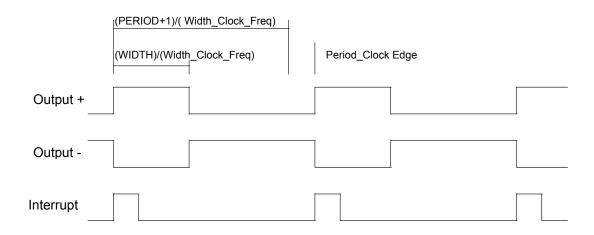

| Figure 6: PWM Output                                                          | . 53 |

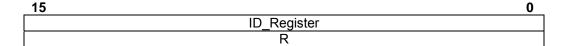

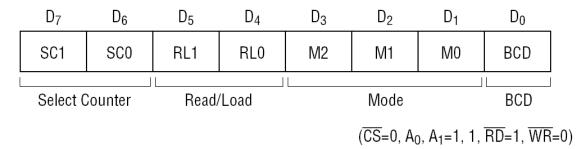

| Figure 7: Counter latching executed for counter #1 (Read/Load 2-byte setting) | . 63 |

# **Table of Tables**

| Table 1: CN10 Pin Assignments                                          | 6  |

|------------------------------------------------------------------------|----|

| Table 2: CN11 Pin Assignments                                          | 7  |

| Table 3: PCI Configuration Registers                                   | 16 |

| Table 4: DM7820/DM9820 Memory Map                                      | 17 |

| Table 5: Peripheral Outputs                                            | 33 |

| Table 6: Incremental Encoder Inputs                                    | 49 |

| Table 7: Select Counter SC[1:0]: Selection of set counter              | 56 |

| Table 8: Read/Load RL[1:0]: Count Value Reading/Loading format setting | 56 |

| Table 9: Mode M[2:0]: Operation waveform mode setting                  | 56 |

| Table 10: BCD: Operation count mode setting                            | 57 |

| Table 11: PLX DM7820/DM9820 Memory Map                                 | 66 |

| Table 12: DMA Threshold Nybble Values                                  | 72 |

# Introduction

# **Product Overview**

The DM7820/DM9820 is designed to provide high speed digital I/O for PC/104-Plus Systems. It interfaces with the PCI bus and uses large FIFOs and DMA transfers to allow for efficient data management. Several peripherals, including Pulse Width Modulators, Incremental Encoders, and Programmable Clocks are also provided.

# **Board Features**

#### Digital I/O

48 Diode protected I/O lines 24 mA source and sink current Compatible with DMR and DOP expansion boards

#### Deep FIFOs with DMA

Two 2M-Word FIFOs Each FIFO is attached to a separate DMA channel 25 MHz bursted throughput 12.5 MHZ continuous throughput FIFO can be looped

#### **Pulse Width Modulators**

Eight PWM outputs Single-ended or Differential Outputs 16-bit resolution Separate period and width clocks provide full resolution at low duty cycles Optional Interrupt generations

#### **Incremental Encoders**

Four Incremental Encoder channels Single-ended or Pseudo-differential Inputs Variable frequency input filtering Max input speed of 40ns per transition 16-bit resolution Two channels can be combined for 32-bit resolution Connect to FIFO for position sampling

#### **Advanced Interrupts**

Two Advanced Interrupt Modules Interrupt on Match, Change, or Strobe All 48 bits are captured when the interrupt is generated Any combination of the 48 bits can be monitored

#### Programmable Clocks

Four programmable clocks Maximum frequency of 25 MHz Can be started and stopped by an interrupt or another clock Continuous or One-Shot Operation Can be cascaded

#### 82C54 Timer/Counters

Six Timer/Counter Channels Fully programmable Input clock and gate driven from internal or external source 10 MHz maximum input

#### **Physical Attributes**

Size:  $3.6^{\circ}L \times 3.8^{\circ}W \times 0.6^{\circ}H$  (90mm L x 96mm W x 15mm H) Weight: 0.22 lbs (0.10 Kg) Operating Temperature:  $-40^{\circ}$  C to  $+85^{\circ}$  C Storage Temperature:  $-55^{\circ}$  C to  $+125^{\circ}$  C Power Requirements: Typical: 1.5 W @ +5 VDC

# **Available Options**

The DM7820/DM9820 is a modular design. Custom feature sets are available. Please contact RTD Embedded Technologies for more information on custom boards.

# **Getting Technical Support**

For help with this product, or any other product made by RTD, you can contact RTD Embedded Technologies via the following methods:

Phone: +1-814-234-8087

E-Mail: techsupport@rtd.com

Be sure to check the RTD web site (<u>http://www.rtd.com</u>) frequently for product updates, including newer versions of the board manual and application software.

# **Hardware Description**

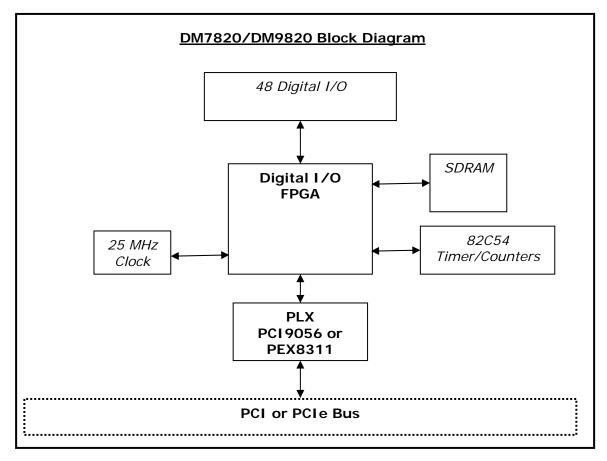

# Block Diagram

Below is a block diagram of the DM7820/DM9820. Primary board components are in bold, while external I/O connections and jumpers are italicized.

Figure 1: DM7820/DM9820 Block Diagram

# **Connector and Jumper Locations**

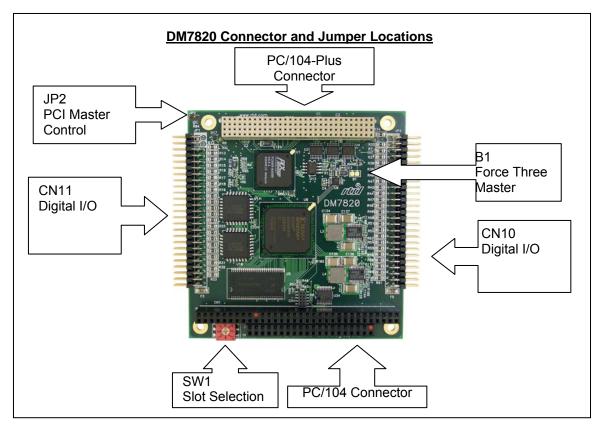

### DM7820

The following diagram shows the location of all connectors and jumpers on the DM7820. For a description of each jumper and connector, refer to the following sections.

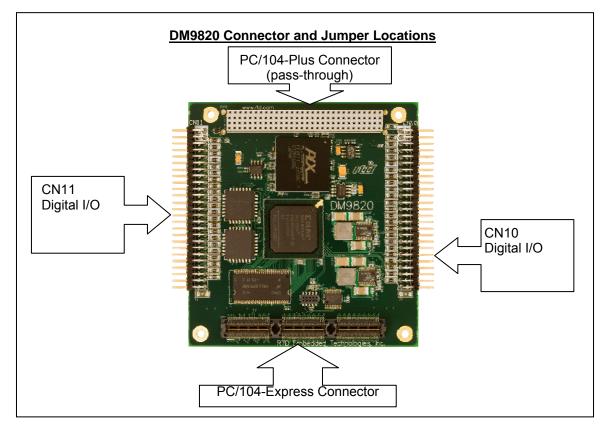

### DM9820

The following diagram shows the location of all connectors and jumpers on the DM9820. For a description of each jumper and connector, refer to the following sections.

# External I/O Connections

The following sections describe the external I/O connections of the DM7820/DM9820.

### Connector CN10 – Digital Input / Output

Connector CN10 provides 24 digital input/output lines, along with a +5V pin and ground pins. The pin assignments for CN10 are shown in Table 1.

**Note:** Pin 1 can be identified by a square solder pad. Pins 2 – 50 have round solder pads.

#### Table 1: CN10 Pin Assignments

| Signal | Pin | Pin | Signal  |

|--------|-----|-----|---------|

| P2[7]  | 1   | 2   | Strobe2 |

| P2[6]  | 3   | 4   | GND     |

| P2[5]  | 5   | 6   | GND     |

| P2[4]  | 7   | 8   | GND     |

| P2[3]  | 9   | 10  | GND     |

| P2[2]  | 11  | 12  | GND     |

DM7820/DM9820 User's Manual

| Din | Din                                                                                                                                                                                | Signal                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|     |                                                                                                                                                                                    | Signal                                                                                                                                                                                                                                                                                                                                                          |

| 13  | 14                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 15  | 16                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 17  | 18                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 19  | 20                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 21  | 22                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 23  | 24                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 25  | 26                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 27  | 28                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 29  | 30                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 31  | 32                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 33  | 34                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 35  | 36                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 37  | 38                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 39  | 40                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 41  | 42                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 43  | 44                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 45  | 46                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 47  | 48                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

| 49  | 50                                                                                                                                                                                 | GND                                                                                                                                                                                                                                                                                                                                                             |

|     | 17         19         21         23         25         27         29         31         33         35         37         39         41         43         45         47         49 | 13       14         15       16         17       18         19       20         21       22         23       24         25       26         27       28         29       30         31       32         33       34         35       36         37       38         39       40         41       42         43       44         45       46         47       48 |

#### Table 1: CN10 Pin Assignments

See Table 5 and Table 6 for peripheral pin assignments.

### **Connector CN11 – Digital Input / Output**

Connector CN11 provides 24 digital input/output lines, along with a +5V pin and ground pins. The pin assignments for CN11 are shown in Table 2.

**Note:** Pin 1 can be identified by a square solder pad. Pins 2 – 50 have round solder pads.

| Signal | Pin | Pin | Signal  |

|--------|-----|-----|---------|

| P2[15] | 1   | 2   | Strobe1 |

| P2[14] | 3   | 4   | GND     |

| P2[13] | 5   | 6   | GND     |

| P2[12] | 7   | 8   | GND     |

| P2[11] | 9   | 10  | GND     |

| P2[10] | 11  | 12  | GND     |

| P2[9]  | 13  | 14  | GND     |

| P2[8]  | 15  | 16  | GND     |

| P1[15] | 17  | 18  | GND     |

| P1[14] | 19  | 20  | GND     |

| P1[13] | 21  | 22  | GND     |

| P1[12] | 23  | 24  | GND     |

| P1[11] | 25  | 26  | GND     |

| P1[10] | 27  | 28  | GND     |

| P1[9]  | 29  | 30  | GND     |

| P1[8]  | 31  | 32  | GND     |

#### Table 2: CN11 Pin Assignments

DM7820/DM9820 User's Manual

| Signal      | Pin | Pin | Signal |

|-------------|-----|-----|--------|

| P1[7]       | 33  | 34  | GND    |

| P1[6]       | 35  | 36  | GND    |

| P1[5]       | 37  | 38  | GND    |

| P1[4]       | 39  | 40  | GND    |

| P1[3]       | 41  | 42  | GND    |

| P1[2]       | 43  | 44  | GND    |

| P1[1]       | 45  | 46  | GND    |

| P1[0]       | 47  | 48  | GND    |

| +5V, 2A max | 49  | 50  | GND    |

#### Table 2: CN11 Pin Assignments

See Table 5 and Table 6 for peripheral pin assignments.

### PC/104 ISA Connectors –DM7820

The PC/104 connectors carry the signals of the PC/104-*Plus* ISA bus. Refer to PC/104-*Plus* Specification Revision 1.0 for the pinout of this connector. This is a pass-through connector. The DM7820 connects to the power and ground pins only, and does not use any of the signals.

# PC/104-Express Bus Connectors–DM9820

The PC/104-Express connectors provide the PCI Express bus connections. CN1 is on the top, and CN2 is on the bottom. Refer to the PC/104-Express<sup>TM</sup> Specification Revision 1.0 for the pinout of these connectors.

The DM9820 connects to one of the PCIe x1 links on the PCIe bus connector, and passes through the x16 link. It will automatically detect the direction to the host, so it can be stacked above or below the CPU.

# PC/104-Plus PCI Connector

The PC/104-*Plus* connector carries the signals of the PC/104-*Plus* PCI bus. Refer to PC/104-*Plus*<sup>TM</sup> Specification for the pinout of this connector. The DM9820 connects to the power and ground pins only, and does not use any of the signals. The DM7820 uses this connector for communication with the CPU.

### PCI Configuration Options (DM7820 Only)

To install the DM7820 into the stack, the PCI Slot Number must be configured correctly. This is done by the PCI Slot Selector located at SW1.

There are four possible PCI Slot Numbers (0 - 3). Each PCI device (PC/104-*Plus* or PCI-104) must a use a different slot number. The slot number is related to the position of the board in the stack. Slot 0 represents the PCI device closest to the CPU. Slot 3 represents the PCI devices farthest away from the CPU.

**Note:** In a PC/104-*Plus* or PCI-104 system, all PCI devices should be located on one side of the CPU board (above or below the add-on cards). The CPU should not be located between two PCI devices.

DM7820/DM9820 User's Manual

#### Switch SW1 – PCI Slot Selector

When the PC/104-*Plus* Specification was first introduced, it only allowed for three PCI add-on cards to be bus masters. Version 2.0 of the PC/104-*Plus* specification was released in November 2003. This version of the specification (which the DM7820 is designed for) adds support for all 4 PCI slots to be bus masters.

There are two methods for compatibility with CPUs designed for the older PC/104-*Plus* Specification. One method is to use slot positions 4-7 instead of the usual 0-3. The second is to short solder jumper B1.

| Switch<br>Position | PCI Slot Number         | Compatibility | Master |

|--------------------|-------------------------|---------------|--------|

| 0                  | Slot 0 (closest to CPU) | 4             | yes    |

| 1                  | Slot 1                  | 4             | yes    |

| 2                  | Slot 2                  | 4             | yes    |

| 3                  | Slot 3                  | 4             | yes    |

| 4                  | Slot 0 (closest to CPU) | 3             | yes    |

| 5                  | Slot 1                  | 3             | yes    |

| 6                  | Slot 2                  | 3             | If JP2 |

| 7                  | Slot 3                  | 3             | If JP2 |

The PCI Slot Number can be configured as follows:

#### Jumper JP2 – Bus Master Control

Install JP2 to enable bus mastering when in Slot 2 or Slot 3 in three bus master mode.

#### Solder Blob B1 – Force Three Master

The DM7820 offers a configuration solder blob at location B1. If this solder blob is open (the default), the board supports bus mastering in all 4 PCI slots when SW1 is in position 0-3. If it is closed, the board will work in a 3 bus master configuration. If B1 is closed, SW1 positions 0-3 will be identical to positions 4-7.

**Note:** The DM7820 comes with solder blob B1 open by default. This should be compatible with most PC/104-*Plus* CPUs. There is no need to change this blob unless you are having compatibility problems with your specific CPU.

# **Board Installation**

# Installing the Hardware

The DM7820 can be installed into a PC/104-*Plus* or PCI-104 stack. It can be located above or below the CPU, as long as all PCI add-on cards are on the same side of the CPU.

The DM9820 can be installed into a PC/104-Express or PCIe/104 stack. It can be located above or below the CPU.

### **Static Precautions**

Keep your board in its antistatic bag until you are ready to install it into your system! When removing it from the bag, hold the board at the edges and do not touch the components or connectors. Handle the board in an antistatic environment and use a grounded workbench for testing and handling of your hardware.

#### **Steps for Installing**

- 1. Shut down the PC/104 system and unplug the power cord.

- 2. Ground yourself with an anti-static strap.

- 3. Set the PCI Slot Selector as described in the previous chapter.

- 4. If any other PCI add-on cards are to be included in the stack, be sure that their PCI slot numbers are configured correctly (Slot 0 for the board closest to the CPU, Slot 1 for the next board, etc).

- 5. Line up the pins of the DM7820/DM9820's connectors with the corresponding bus connectors of the stack. Make sure that both connectors are lined up.

- 6. Apply pressure to both bus connectors and gently press the board onto the stack. The board should slide into the matching bus connectors. Do not attempt to force the board, as this can lead to bent/broken pins.

- 7. Attach any cables to the DM7820/DM9820

- 8. If any boards are to be stacked above the DM7820/DM9820, install them.

- 9. Attach any necessary cables to the PC/104-Plus stack.

- 10. Re-connect the power cord and apply power to the stack.

- 11. Boot the system and verify that all of the hardware is working properly.

**Note:** If multiple PCI devices are configured to use the same PCI slot number, the system will not boot.

# Installing Software

Drivers are required to use the DM7820/DM9820. They are provided, along with example programs, on the CD that ships with the board, and are also available from the RTD website (<u>www.rtd.com</u>). For further information on installing the drivers, review README.TXT in the driver archive file.

# **Functional Overview**

# Internal Architecture

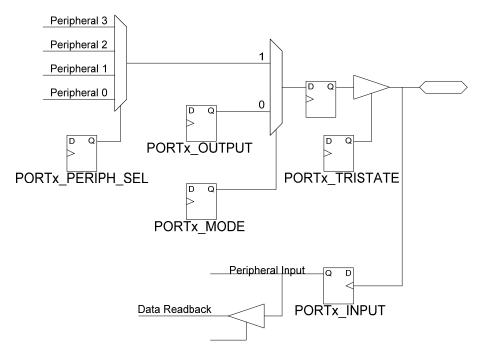

A diagram of the standard I/O is shown in Figure 4. Each digital I/O pin can be an input, output, or peripheral output. The peripheral outputs are the Pulse Width Modulators, FIFO, Timer/Counters, etc.

Figure 2: Digital I/O Block Diagram

# **FIFOs**

The DM7820/DM9820 provides two FIFOs to buffer data going into and out of the board. Each FIFO is 16-bit wide and 2,097,661 Words deep. The input strobe, output strobe, and data input for each FIFO can be individually selected. The output data is made available to the peripheral outputs, and also the PCI interface.

Each FIFO is attached to a DMA Channel in the PLX chip. FIFO0 is attached to DMA0, and FIFO1 is attached to DMA1.

FIFO0 can have its input data attached to its output data. In this case, the same data is repeated forever. This is useful for some types of pattern generation.

Internally, the FIFO system consists of a single 8MB SDRAM device, with 255-word input and output buffers for each channel. When data is available in the input buffer, it is moved into the area of SDRAM device for that channel. When data is in the SDRAM device, and there is room available in the output buffer, data is moved to the output buffer. All of the internal data movement is handled automatically. Greatest data efficiency is achieved when there is at least 128 words of data in the FIFO.

The FIFO also provides "Write Request" and "Read Request" signals. For these signals, the internal buffers are monitored to signal when data can be sent into, and read from the FIFO. The "Write Request" is asserted when there is at least 256 words of space available in the FIFO, and negated when there is less than 128 words available. The "Read Request" is asserted when at least 256 words of data is in the FIFO, and negated when there is less than 128 words available. The "Read Request" is asserted when at least 256 words of data is in the FIFO, and negated when there is less than 128 words of data. Using these signals guarantees a burst of at least 128 words, which provides for efficient communication over the PCI bus, and robustly guards against over-run and under-run conditions. However, it does not allow for the FIFO to be completely filled of emptied.

There is a total of 45 M-words per second of available bandwidth for the entire FIFO system. This bandwidth is allocated between all input and output sources. This is assuming that at least 256 Words stay in the FIFO at all times to maximize bursting (i.e., the Read Request and Write Request are used for DREQ). If only one word is available in the FIFO (i.e. Not Empty is used as for DREQ) the available bandwidth drops to 3.75 M-words per second. When a FIFO is looped, the data must be read and written. The table below shows examples of configurations and their maximum data rate. Note that for uniform sampling (samples are taken at uniform sampling intervals) the data rate must be an integer divisor of the 25 MHz overall clock.

| Description                                   | Max Data Rate |

|-----------------------------------------------|---------------|

| One FIFO in use, burst capture only           | 25 MHz        |

| One FIFO in use, burst output only            | 25 MHz        |

| One FIFO in use, continuous capture or output | 12.5 MHz      |

| Two FIFOs in use, continuous capture/output   | 12.5 MHz +    |

|                                               | 6.25 MHz      |

| Two FIFOs in use, continuous capture/output,  | 11 MHz +      |

| non-uniform sampling                          | 11 MHz        |

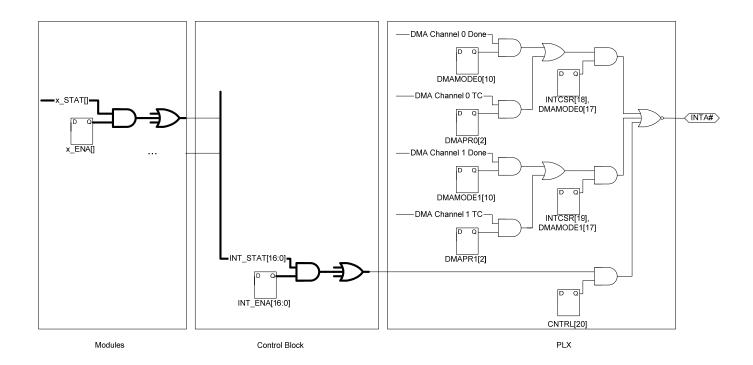

# **Board Interrupts**

There are three levels of interrupt sources for this board: the interrupt sources generated in the PLX chip, the interrupt sources generated by the modules in the Control Block, and the interrupt sources within the modules. Each level must be enabled in the previous level. Figure 3 shows a block diagram of the interrupt sources. Note that there are some other sources in the PLX bridge chip; consult the datasheet for more details.

# Advanced Triggering Examples

The modules on the DM7820/DM9820 can be combined to generate a broad range of complex sampling scenarios. The following example shows how to use the Advanced Interrupt and 4 counters to capture N words before and M words after an event. Programmable Clock 0 is the sample clock, and is used to clock data into the FIFO. It is started after all of the other Programmable clocks are initialized. As soon as it starts, Programmable Clock 1 starts counting samples to be captured before the triggering event. This is also known as "pre-fill." When it expires, it starts Programmable Clock 2, which removes samples from the FIFO at the same rate that they are stored, keeping a constant number of samples in the FIFO. When the triggering event happens, Programmable Clock 2 is stopped, and the FIFO begins to fill. Also, the triggering event starts Programmable Clock 3, which counts the number of samples to be captured after the triggering event. When Programmable Clock 3 expires, it stops Programmable Clock 0, and data collection ends. The triggering event can also generate an interrupt that changes the FIFO output to PCI Read, and start DMA transfers. This allows the data to be moved to system memory before data collection has ended.

- AdvInt0

- o Set to event desired

- During the Interrupt Service Routine...

- Change FIFO output clock to PCI Read

- Start DMA transfers

- Prog Clock 0 Sample Input Clock

- Period = sample period

DM7820/DM9820 User's Manual

- Master Clock = any

- Start Event = always

- Stop Event = Prog Clock 3

- o Continuous operation

- Prog Clock 1 Pre-capture clock

- Period = N (samples before event)

- Master Clock = Prog Clock 0

- Start Event = always

- o One-shot

- Prog Clock 2 Sample output clock

- Period = same as Prog Clock 0

- Master Clock = same as Prog Clock 0

- Start Event = Prog Clock 1

- Stop Event = AdvInt 0

- o Continuous

- Prog Clock 3 Post-Capture clock

- Period = M (samples after event)

- Master Clock = Prog Clock 0

- Start Event = AdvInt0

- o One-Shot

- FIFO 0

- Data In = any

- Data in clock = Prog Clock 0

- Data out clock = Prog Clock 2 (before AdvInt0)

- Data out clock = PCI Read (after Adv Int0)

- DReq0 = Read Ready

# **Board Operation and Programming**

# PCI Interface

This board attaches to the PCI bus using a PLX PCI9056. The PCI9056 is operating in "C Mode." Most of the registers in the PLX chip are automatically programmed at power up by the on-board EEPROM or by the system BIOS. The only PLX registers that the user needs to access are the DMA registers found on page 66, and the Configuration Registers found in Table 3 below.

For more information on the PLX PCI9056 bridge chip, contact PLX Technologies, (<u>www.plxtech.com</u>).

#### Table 3: PCI Configuration Registers

| PCI Config.<br>Register<br>Address (Hex) | Register Name                                                       |                                                                 |                   |                    |  |  |

|------------------------------------------|---------------------------------------------------------------------|-----------------------------------------------------------------|-------------------|--------------------|--|--|

| 0x00                                     | PCI Device ID = 0x7820 PCI Vendor ID = 0x1435                       |                                                                 |                   |                    |  |  |

| 0x04                                     | PCI Status                                                          |                                                                 | PCI Command       |                    |  |  |

| 0x08                                     | PCI Class Code = 0>                                                 | (118000                                                         |                   | PCI Rev. ID = 0x00 |  |  |

| 0x0C                                     | PCI BIST                                                            | PCI Header Type                                                 | Bus Latency Timer | Cache Line Size    |  |  |

| 0x10                                     | PCI Base Address R                                                  | PCI Base Address Register 0: Memory Access to PLX9056 Registers |                   |                    |  |  |

| 0x14                                     | PCI Base Address Register 1: I/O Access to PLX9056 Registers        |                                                                 |                   |                    |  |  |

| 0x18                                     | PCI Base Address Register 2: Memory Access to Digital I/O Registers |                                                                 |                   |                    |  |  |

| 0x1C                                     | PCI Base Address Register 3: Reserved                               |                                                                 |                   |                    |  |  |

| 0x20                                     | Reserved                                                            |                                                                 |                   |                    |  |  |

| 0x24                                     | Reserved                                                            |                                                                 |                   |                    |  |  |

| 0x28                                     | Reserved                                                            |                                                                 |                   |                    |  |  |

| 0x2C                                     | PCI Subsystem ID = 0x9056 PCI Subsystem Vendor = 0x10B5             |                                                                 |                   |                    |  |  |

| 0x30                                     | Reserved                                                            |                                                                 |                   |                    |  |  |

| 0x34                                     | Reserved Reserved                                                   |                                                                 |                   |                    |  |  |

| 0x38                                     | Reserved                                                            |                                                                 |                   |                    |  |  |

| 0x3C                                     | PCI Max Latency                                                     | PCI Min Grant                                                   | PCI Interrupt Pin | PCI Interrupt Line |  |  |

## **Device Memory**

The DM7820/DM9820 is a memory mapped device. The address for the memory mapped registers can be found in Base Address Register 2. Generally, the registers are 16 bits wide. However, they can be read and written as 8, 16, or 32 bits. (There are a few exceptions as noted in the memory map.)

### Memory Map Overview

Table 4 shows the memory map of the DM7820/DM9820 digital I/O registers. These are found at the offset from BAR2.

| Offset           | Register Name  | Register Function                                             |

|------------------|----------------|---------------------------------------------------------------|

| (Hex)            |                | Describer                                                     |

| 0.0000           |                | Board Control                                                 |

| 0x0000           | FPGA_VERSION   | b[15:8] Type ID<br>b[7:0] Version                             |

| 0x0002           | SVN VERSION    | b[15:0] Extended Version                                      |

| 0x0002<br>0x0004 | BOARD RESET    | Write 0xA5A5 to reset board                                   |

| 0x0004<br>0x0006 | Reserved       |                                                               |

| 0x0008           | BRD STAT       | b[15:1] Reserved                                              |

| 020008           | BRD_STAT       | b0 MSTR – 0 = PCI Master Capable, 1 = Not PCI                 |

|                  |                | Master Capable (Read Only)                                    |

| 0x0010           | INT ENABLE     | b[15:0] Interrupt Enable – Set to '1' to enable a specific    |

|                  | —              | interrupt                                                     |

| 0x0012           | INT_STAT       | b [15:0] Interrupt Status – Reading a '1' indicates interrupt |

|                  |                | condition has occurred. Write a '1' to clear an               |

|                  |                | interrupt bit.                                                |

| 0x0014-          | Reserved       |                                                               |

| 0x003E           |                | Standard I/O                                                  |

| 0x0040           | PORTO OUTPUT   | b [15:0] Value to port 0 when it is an output.                |

| 0x0040           | PORTO INPUT    | b [15:0] Read only value from Port 0.                         |

| 0x0042           | PORTO TRISTATE | b [15:0] '1' for output, '0' for input.                       |

| 0x0044           | PORTO MODE     | b[15:0] '1' for peripheral output, '0' for digital I/O        |

| 0x0048           | PORT1 OUTPUT   | b [15:0] Value to port 1 when it is an output.                |

| 0x004A           | PORT1 INPUT    | b [15:0] Read only value from Port 1.                         |

| 0x004C           | PORT1 TRISTATE | b [15:0] '1' for output, '0' for input.                       |

| 0x004E           | PORT1 MODE     | b[15:0] '1' for peripheral output, '0' for digital I/O        |

| 0x0050           | PORT2 OUTPUT   | b [15:0] Value to port 2 when it is an output.                |

| 0x0052           | PORT2_INPUT    | b [15:0] Read only value from Port 2.                         |

| 0x0054           | PORT2_TRISTATE | b [15:0] '1' for output, '0' for input.                       |

| 0x0056           | PORT2_MODE     | b[15:0] '1' for peripheral output, '0' for digital I/O        |

| 0x0058           | STROBE_STATUS  | b [9] STR2_TRI – '0' = strobe2 is input, '1' = srobe2 is      |

|                  |                | output.                                                       |

|                  |                | b [8] STR1_TRI – '0' = strobe1 is input, '1' = srobe1 is      |

|                  |                | output.<br>b [5] STR2_OUT – Value for strobe2 when an output. |

|                  |                | b [4] STR1_OUT – Value for strobe1 when an output.            |

|                  |                | b [1] STR2 IN – Current value of Strobe2.                     |

|                  |                | b [0] STR1_IN – Current value of Strobe1.                     |

| 0x005A-          | Reserved       |                                                               |

| 0x005E           |                |                                                               |

| Offset            | Register Name      | Register Function                                               |

|-------------------|--------------------|-----------------------------------------------------------------|

| (Hex)             |                    |                                                                 |

| 0x0060            | PORT0_PERIPH_SEL_L | b[15:14]Port0[7]_Periph_Select                                  |

|                   |                    | b[13:12]Port0[6]_Periph_Select                                  |

|                   |                    | b[11:10]Port0[5]_Periph_Select<br>b[9:8] Port0[4]_Periph_Select |

|                   |                    | b[7:6] Port0[3]_Periph_Select                                   |

|                   |                    | b[5:4] Port0[2]_Periph_Select                                   |

|                   |                    | b[3:2] Port0[2]_Periph_Select                                   |

|                   |                    | b[1:0] Port0[0]_Periph_Select                                   |

| 0x0062            | PORTO PERIPH SEL H | b[15:14]Port0[15]_Periph_Select                                 |

|                   |                    | b[13:12]Port0[14]_Periph_Select                                 |

|                   |                    | b[11:10]Port0[13]_Periph_Select                                 |

|                   |                    | b[9:8] Port0[12]_Periph_Select                                  |

|                   |                    | b[7:6] Port0[11]_Periph_Select                                  |

|                   |                    | b[5:4] Port0[10]_Periph_Select                                  |

|                   |                    | b[3:2] Port0[9]_Periph_Select                                   |

| 00004             |                    | b[1:0] Port0[8]_Periph_Select                                   |

| 0x0064            | PORT1_PERIPH_SEL_L |                                                                 |

| 0x0066            | PORT1_PERIPH_SEL_H |                                                                 |

| 0x0068            | PORT2_PERIPH_SEL_L |                                                                 |

| 0x006A            | PORT2_PERIPH_SEL_H |                                                                 |

| 0x0070–<br>0x007E | Reserved           |                                                                 |

| 00072             | 8205               | 4 Timer Counter Control                                         |

| 0x0080            | TC ID              | b[15:0] ID Register – equals 0x1001                             |

| 0x0080            | TC INT             | b[15:14]Reserved                                                |

| 020002            |                    | b [13:8] Interrupt Status – '1' = Interrupt condition has       |

|                   |                    | occurred. Write '1' to clear. Interrupts are asserted           |

|                   |                    | on the positive edge of the clock.                              |

|                   |                    | b[7:6] Reserved                                                 |

|                   |                    | b[5:0] Interrupt Enable – '1' = Interrupt is enabled, '0' =     |

|                   |                    | disabled                                                        |

|                   |                    | Interrupt source are:                                           |

|                   |                    | 5 TC B2                                                         |

|                   |                    | 4 TC B1<br>3 TC B0                                              |

|                   |                    | 3 TC B0<br>2 TC A2                                              |

|                   |                    | 1 TC A1                                                         |

|                   |                    | 0 TC A0                                                         |

| 0x0084            | TC A0 CONTROL      | b[15:13]Reserved                                                |

| 0x0086            | TC A1 CONTROL      | b[12:8] Gate Select                                             |

| 0x0088            | TC A2 CONTROL      | 31-16 = Port 2 [15-0]                                           |

| 0x008A            | TC B0 CONTROL      | 15-2 = Clock_Bus [15-2]                                         |

| 0x008C            | TC B1 CONTROL      | 1 = 1'                                                          |

| 0x008E            | TC B2 CONTROL      | 0 = '0'<br>b[7:4] Reserved                                      |

|                   |                    | b[3:0] Clock Select                                             |

|                   |                    | 15-2 = Clock_Bus [15-2]                                         |

|                   |                    | $13-2$ = Clock_bds [13-2]<br>1 = reserved                       |

|                   |                    | 0 = 5  MHz                                                      |

|                   | l                  | FIFO Channel 0                                                  |

| FIFU Channel U    |                    |                                                                 |

DM7820/DM9820 User's Manual

| Offset | Register Name      | Register Function                                                                                                                                                                                                                                                                                                                                                                                       |

|--------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Hex)  | 5                  | 5                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x00C0 | FIFO0_ID           | b[15:0] ID Register = 0x2011                                                                                                                                                                                                                                                                                                                                                                            |

| 0x00C2 | FIFO0_INT          | <ul> <li>b [15:8] Interrupt Status – '1' = Interrupt condition has occurred. Write '1' to clear.</li> <li>b[7:0] Interrupt Enable – '1' = Interrupt is enabled, '0' = disabled</li> <li>Interrupt source are: <ul> <li>7 Reserved</li> <li>6 Reserved</li> <li>5 Underflow</li> <li>4 Overflow</li> <li>3 Empty</li> <li>2 Full</li> <li>1 Write Request</li> <li>0 Read Request</li> </ul> </li> </ul> |

| 0x00C4 | FIFO0_IN_CLK       | b[15:5] Reserved<br>b[4:0] Input Clock Select<br>31 = PCI Write<br>30 = PCI Read<br>29-16 = Interrupts[13-0]<br>15-0 = Clock_Bus [15-0]                                                                                                                                                                                                                                                                 |

| 0x00C6 | FIFO0_OUT_CLK      | b[15:5] Reserved<br>b[4:0] Input Clock Select<br>31 = PCI Write<br>30 = PCI Read<br>29-16 = Interrupts[13-0]<br>15-0 = Clock_Bus [15-0]                                                                                                                                                                                                                                                                 |

| 0x00C8 | FIFO0_IN_DATA_DREQ | b[15:10]Reserved<br>b[9:8] DREQ0 Source<br>3 = Not Full<br>2 = Write Request<br>1 = Not Empty<br>0 = Read Request<br>b[7:4] Reserved<br>b[3:0] Input Data Select<br>3 = FIFO0 Output<br>2 = Port 2<br>1 = Port 0<br>0 = PCI Data                                                                                                                                                                        |

| 0x00CA | FIFO0_CON_STAT     | b[15:10]Reserved<br>b[9] Write Request (non-sticky)<br>b[8] Read Request (non-sticky)<br>b[7:1] Reserved<br>b[0] '1' = Enable, '0' = Clear                                                                                                                                                                                                                                                              |

| 0x00CC | FIFO0_RW_PORT      | b [15:0] Read/Write Port.<br>(Word access only)                                                                                                                                                                                                                                                                                                                                                         |

|        |                    | FIFO Channel 1                                                                                                                                                                                                                                                                                                                                                                                          |

| 0x00D0 | FIFO1_ID           | b[15:0] ID Register = 0x2011                                                                                                                                                                                                                                                                                                                                                                            |

| Offset          | Register Name                         | Register Function                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (Hex)<br>0x00D2 | FIFO1_INT                             | <ul> <li>b [15:8] Interrupt Status – '1' = Interrupt condition has occurred. Write '1' to clear.</li> <li>b[7:0] Interrupt Enable – '1' = Interrupt is enabled, '0' = disabled</li> <li>Interrupt source are: <ul> <li>7 Reserved</li> <li>6 Reserved</li> <li>5 Underflow</li> <li>4 Overflow</li> <li>3 Empty</li> <li>2 Full</li> <li>1 Write Request</li> <li>0 Read Request</li> </ul> </li> </ul> |

| 0x00D4          | FIFO1_IN_CLK                          | b[15:5] Reserved<br>b[4:0] Input Clock Select<br>31 = PCI Write<br>30 = PCI Read<br>29-16 = Interrupts[13-0]<br>15-0 = Clock_Bus [15-0]                                                                                                                                                                                                                                                                 |

| 0x00D6          | FIFO1_OUT_CLK                         | b[15:5] Reserved<br>b[4:0] Input Clock Select<br>31 = PCI Write<br>30 = PCI Read<br>29-16 = Interrupts[13-0]<br>15-0 = Clock Bus [15-0]                                                                                                                                                                                                                                                                 |

| 0x00D8          | FIFO1_IN_DATA_DREQ                    | b[15:10]Reserved<br>b[9:8] DREQ1 Source<br>3 = Not Full<br>2 = Write Request<br>1 = Not Empty<br>0 = Read Request<br>b[7:4] Reserved<br>b[3:0] Input Data Select<br>3 = Incremental Encoder B1<br>2 = Incremental Encoder B0<br>1 = Port 1<br>0 = PCI Data                                                                                                                                              |

| 0x00DA          | FIFO1_CON_STAT                        | b[15:10]Reserved<br>b[9] Write Request (non-sticky)<br>b[8] Read Request (non-sticky)<br>b[7:1] Reserved<br>b[0] '1' = Enable, '0' = Clear                                                                                                                                                                                                                                                              |

| 0x00DC          | FIFO1_RW_PORT                         | b [15:0] Read/Write Port.<br>(Word access only)                                                                                                                                                                                                                                                                                                                                                         |

|                 | · · · · · · · · · · · · · · · · · · · | rogrammable Clock 0                                                                                                                                                                                                                                                                                                                                                                                     |

| 0x0100          | PRGCLK0_ID                            | b[15:0] ID Register = 0x1000                                                                                                                                                                                                                                                                                                                                                                            |

| Offset<br>(Hex)                                       | Register Name        | Register Function                                      |  |

|-------------------------------------------------------|----------------------|--------------------------------------------------------|--|

| 0x0102                                                | PRGCLK0_MODE         | b[15:2] Reserved                                       |  |

|                                                       | —                    | b[1:0] '00' = Disabled                                 |  |

|                                                       |                      | '01' = Continuous                                      |  |

|                                                       |                      | '10' = Reserved                                        |  |

|                                                       |                      | '11' = One-Shot                                        |  |

| 0x0104                                                | PRGCLK0_CLK          | b[15:4] Reserved<br>b[3:0] Master Clock Source         |  |

|                                                       |                      | 15-0 = Clock_Bus [15-0]                                |  |

| 0x0106                                                | PRGCLK0_START_STOP   | b[15:13]Reserved                                       |  |

| UNO TOO                                               |                      | b[12:8] Stop Clock                                     |  |

|                                                       |                      | 31-16 = Interrupt_Bus[15-0]                            |  |

|                                                       |                      | 15-1 = Clock_Bus [15-1]                                |  |

|                                                       |                      | 0 = No Stop Clock                                      |  |

|                                                       |                      | b[7:5] Reserved                                        |  |

|                                                       |                      | b[4:0] Start Trigger<br>31-16 = Interrupt Bus[15-0]    |  |

|                                                       |                      | 31-16 = Interrupt_Bus[15-0]<br>15-1 = Clock_Bus [15-1] |  |

|                                                       |                      | 0 = Start Immediate                                    |  |

| 0x0108                                                | PRGCLK0 PERIOD       | b[15:0] Period of Clock                                |  |

|                                                       | —                    | Output frequency is:                                   |  |

|                                                       |                      | Master Clock Frequency                                 |  |

|                                                       |                      | $\overline{(PRG\_CLK\_PERIOD+1)}$                      |  |

|                                                       | Programmable Clock 1 |                                                        |  |

| <b>0x0140</b> PRGCLK1_ID b[15:0] ID Register = 0x1000 |                      | b[15:0] ID Register = 0x1000                           |  |

| 0x0142                                                | PRGCLK1_MODE         | b[15:2] Reserved                                       |  |

|                                                       |                      | b[1:0] '00' = Disabled                                 |  |

|                                                       |                      | '01' = Continuous                                      |  |

|                                                       |                      | '10' = Reserved                                        |  |

| 0x0144                                                | PRGCLK1 CLK          | '11' = One-Shot<br>b[15:4] Reserved                    |  |

| 0.0144                                                | INGOERT_OER          | b[3:0] Master Clock Source                             |  |

|                                                       |                      | 15-0 = Clock_Bus [15-0]                                |  |

| 0x0146                                                | PRGCLK1_START_STOP   | b[15:13]Reserved                                       |  |

|                                                       |                      | b[12:8] Stop Clock                                     |  |

|                                                       |                      | 31-16 = Interrupt_Bus[15-0]                            |  |

|                                                       |                      | 15-1 = Clock_Bus [15-1]                                |  |

|                                                       |                      | 0 = No Stop Clock<br>b[7:5] Reserved                   |  |

|                                                       |                      | b[4:0] Start Trigger                                   |  |

|                                                       |                      | 31-16 = Interrupt_Bus[15-0]                            |  |

|                                                       |                      | 15-1 = Clock Bus [15-1]                                |  |