## **Highly Integrated Offline Current Mode PWM Power Switch**

#### **FEATURES**

- Integrated with 600V Power MOSFET

- ±1% CV Regulation

- Less than 75mW Standby Power

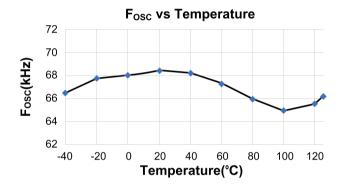

- Fixed 65KHz Switching Frequency

- Green Mode and Burst Mode Control

- Very Low Startup and Operation Current

- Built-in Frequency Shuffling to Reduce EMI

- Built-in Current Mode Control with Internal Slope Compensation

- Built-in Protections with Auto Recovery:

- VDD Under Voltage Lockout (UVLO)

- VDD Over Voltage Protection (OVP)

- On-Chip Thermal Shutdown (OTP)

- Cycle-by-Cycle Current Limiting

- Over Load Protection (OLP)

- CS Pin Float Protection

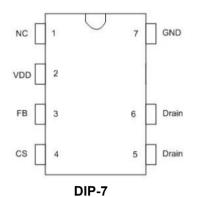

- Available with DIP-7/DIP8 Package

#### **GENERAL DESCRIPTION**

DP2354 is a high performance current mode PWM power switch for offline flyback converter applications.

In DP2354, PWM switching frequency with shuffling is fixed to 65KHz and is trimmed to tight range. The IC has built-in green and burst mode control for light and zero loadings, which can achieve less than 75mW standby power.

DP2354 integrates functions and protections of Under Voltage Lockout (UVLO), VDD over Voltage Protection (VDD OVP), Cycle-by-cycle Current Limiting (OCP), Over Load Protection (OLP), On-Chip Thermal Shutdown (OTP), Soft Start, VDD Clamping and CS Pin Float Protection, etc.

### **APPLICATIONS**

- Power Adapter

- General Switch Mode Power Supply

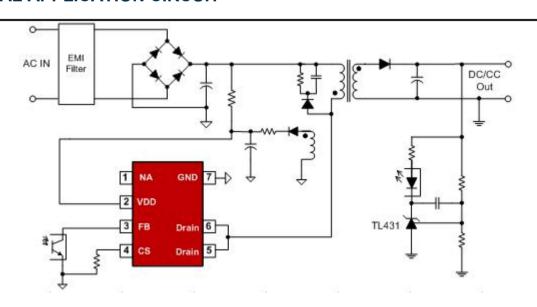

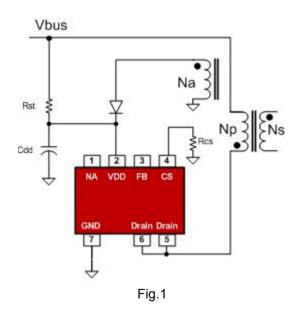

### TYPICAL APPLICATION CIRCUIT

# **Pin Configuration**

# **Marking Information**

## **Pin Description**

| Pin Number | Pin Number | I/O | Description                                                                                                                                                                     |

|------------|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NA         |     | Un-connection Pin. Left float in the practical design                                                                                                                           |

| 2          | VDD        | Р   | IC power supply pin                                                                                                                                                             |

| 3          | FB         | I   | Feedback pin. The loop regulation is achieved by connecting a photo-coupler to this pin. PWM duty cycle is determined by this pin voltage and the current sense signal at Pin 4 |

| 4          | cs         | I   | Current Sense Input Pin                                                                                                                                                         |

| 5,6        | Drain      | 0   | The Power MOSFET Drain                                                                                                                                                          |

| 7,8        | GND        | Р   | The Ground of the IC                                                                                                                                                            |

### **Ordering Information**

| Part Number | Description                     |

|-------------|---------------------------------|

| DP2354      | DIP-7/DIP8, Pb free, 50Pcs/Tube |

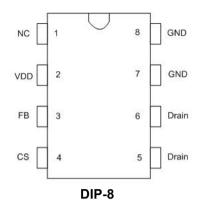

## **Block Diagram**

## **Absolute Maximum Ratings (Note 1)**

| Parameter                                            | Value       | Unit |

|------------------------------------------------------|-------------|------|

| VDD DC Supply Voltage                                | 30          | V    |

| VDD DC Clamp Current                                 | 10          | mA   |

| Drain Pin                                            | -0.3 to 600 | V    |

| FB, CS Voltage Range                                 | -0.3 to 7   | V    |

| Package Thermal ResistanceJunction to Ambient(DIP-7) | 105         | °C/W |

| Maximum Junction Temperature                         | 175         | °C   |

| Storage Temperature Range                            | -65 to 150  | °C   |

| Lead Temperature (Soldering, 10sec.)                 | 260         | °C   |

| ESD Capability, HBM (Human Body Model)               | 4           | kV   |

| ESD Capability, MM (Machine Model)                   | 500         | V    |

# **Recommended Operation Conditions (Note 2)**

| Parameter                     | Value     | Unit |

|-------------------------------|-----------|------|

| Supply Voltage, VDD           | 10 to 26  | V    |

| Operating Ambient Temperature | -40 to 85 | °C   |

## **Electrical Characteristics (Ta = 25°C, VIN=12V, if not otherwise noted)**

| Symbol                   | Parameter                          | Test Conditions                         | Min | Тур. | Max  | Unit |  |

|--------------------------|------------------------------------|-----------------------------------------|-----|------|------|------|--|

| Supply Volta             | Supply Voltage Section(VDD Pin)    |                                         |     |      |      |      |  |

| I <sub>VDD_st</sub>      | Start-up current into VDD pin      |                                         |     | 2    | 20   | uA   |  |

| I <sub>VDD_Op</sub>      | Operation Current                  | V <sub>FB</sub> =3V                     |     | 1.2  | 2    | mA   |  |

| I <sub>VDD_standby</sub> | Standby Current                    |                                         |     | 0.6  | 1    | mA   |  |

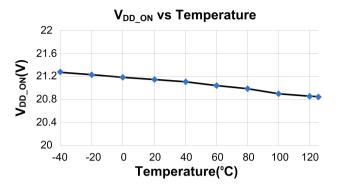

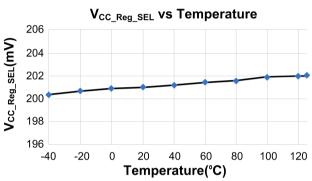

| V <sub>DD_ON</sub>       | VDD Under Voltage Lockout Exit     |                                         | 19  | 21   | 21.5 | V    |  |

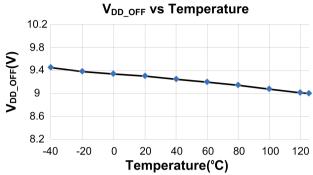

| V <sub>DD_OFF</sub>      | VDD Under Voltage Lockout<br>Enter |                                         | 8   | 9    | 10   | V    |  |

| $V_{DD\_OVP}$            | VDD OVP Threshold                  |                                         | 29  | 31   | 33   | V    |  |

| V <sub>DD_Clamp</sub>    | VDD Zener Clamp Voltage            | I(V <sub>DD</sub> )=7 mA                | 33  | 35   | 37   | V    |  |

| Feedback In              | Feedback Input Section (FB Pin)    |                                         |     |      |      |      |  |

| V <sub>FB_Open</sub>     | FB Open Voltage                    |                                         |     | 5.9  |      | V    |  |

| I <sub>FB_Short</sub>    | FB Short Circuit Current           | Short FB Pin to GND,<br>Measure Current |     | 0.3  |      | mA   |  |

| Z <sub>FB_IN</sub>       | FB Input Impedance                 |                                         |     | 20   |      | ΚΩ   |  |

| Acs                      | PWM Gain                           | ΔV <sub>FB</sub> /ΔV <sub>CS</sub>      |     | 2.0  |      | V/V  |  |

## Highly Integrated Offline Current Mode PWM Power Switch

| V <sub>skip</sub>                | FB Under Voltage PWM Clock is OFF              |                     |      | 1.0  |      | V   |  |  |

|----------------------------------|------------------------------------------------|---------------------|------|------|------|-----|--|--|

| V <sub>TH_OLP</sub>              | Power Limiting FB Threshold Voltage            |                     |      | 3.6  |      | V   |  |  |

| T <sub>D_OLP</sub>               | Power Limiting Debounce Time                   | SEL Pin is floating |      | 75   |      | ms  |  |  |

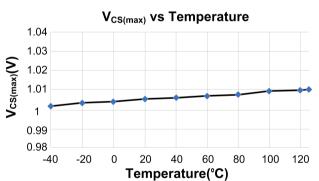

| Current Sen                      | Current Sense Input Section (CS Pin)           |                     |      |      |      |     |  |  |

| T <sub>LEB</sub>                 | CS Input Leading Edge<br>Blanking Time         |                     |      | 250  |      | ns  |  |  |

| V <sub>cs(max)</sub>             | Current limiting threshold                     |                     | 0.97 | 1.0  | 1.03 | V   |  |  |

| T <sub>D_OC</sub>                | Over Current Detection and Control Delay       |                     |      | 70   |      | ns  |  |  |

| Oscillator Se                    | ection                                         |                     |      |      |      |     |  |  |

| Fosc                             | Normal Oscillation Frequency                   |                     | 60   | 65   | 70   | KHz |  |  |

| ΔF(shuffle)<br>/F <sub>osc</sub> | Frequency Shuffling Range                      |                     | -4   |      | 4    | %   |  |  |

| T(shuffle)                       | Frequency Shuffling Period                     |                     |      | 32   |      | ms  |  |  |

| D <sub>MAX</sub>                 | Maximum Switching Duty Cycle                   |                     |      | 66.7 |      | %   |  |  |

| F <sub>Bust</sub>                | Burst Mode Base Frequency                      |                     |      | 22   |      | KHz |  |  |

| On-Chip The                      | On-Chip Thermal Shutdown                       |                     |      |      |      |     |  |  |

| T <sub>SD</sub>                  | Thermal Shutdown                               | (Note 3)            |      | 165  |      | °C  |  |  |

| T <sub>RC</sub>                  | Thermal Recovery                               | (Note 3)            |      | 140  |      | °C  |  |  |

| Power MOSFET Section (Drain Pin) |                                                |                     |      |      |      |     |  |  |

| V <sub>BR</sub>                  | Power MOSFET Drain<br>Source Breakdown Voltage |                     | 600  |      |      | V   |  |  |

| R <sub>dson</sub>                | Static Drain-Source On Resistance              |                     |      | 10   |      | Ω   |  |  |

**Note1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note2. The device is not guaranteed to function outside its operating conditions.

Note3. Guaranteed by the Design.

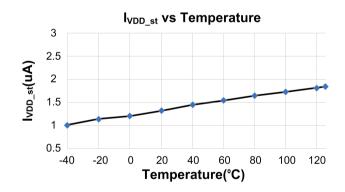

### **Characterization Plots**

### **Operation Description**

DP2354 is a high performance current mode PWM power switch for offline flyback converter, motor driver power supply, and adapter applications.

### System Start-Up Operation and IC Operation Current

Before the IC starts to work, it consumes only startup current (typically 2uA) which allows a large value startup resistor to be used to minimize the power loss and the current flowing through the startup resistor charges the VDD hold-up capacitor from the high voltage DC bus. When VDD reaches turn on threshold VDD\_ON (typical 21V), DP2354 begins switching and the IC operation current is increased to be 1mA (typical). The hold-up capacitor continues to supply VDD before the auxiliary winding of the transformer takes the control of VDD voltage. When the IC enters into burst mode, the IC operation current will decrease further, thus less than 75mW standby power.

#### Oscillator with Frequency Shuffling

PWM switching frequency in DP2354 is fixed to 65KHz and is trimmed to tight range. To improve

system EMI performance, DP2354 operates the system with 4% frequency shuffling around setting frequency.

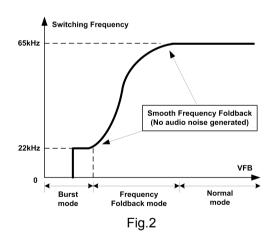

#### Green Mode Operation

Since the main power dissipation at light/zero load in a switching mode power supply is from the switching loss which is proportional to the PWM switching frequency. To meet green mode requirement, it is necessary to reduce the switching cycles under such conditions either by skipping some switching pulses or by reducing the switching frequency.

#### **Smooth Frequency Foldback**

In DP2354, a Proprietary "Smooth Frequency Foldback" function is integrated to foldback the PWM switching frequency when the loading is light. Compared to the other frequency reduction implementations, this technique can reduce the PWM frequency smoothly without audible noise.

#### **Burst Mode Control**

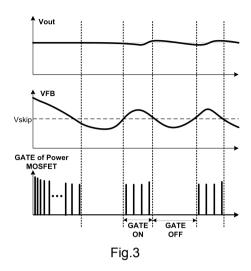

When the loading is very small, the system enters into burst mode. When VFB drops below Vskip, DP2354 will stop switching and output voltage starts to drop (as shown in Fig.3), which causes the VFB to rise. Once VFB rises above Vskip, switching resumes. Burst mode control alternately

enables and disables switching, thereby reducing switching loss in standby mode.

#### Built-in Slope Compensation

In the conventional application, the problem of the stability is a critical issue for current mode controlling, when it operates in higher than 50% of the duty-cycle. In DP2354 the slope compensation circuit is integrated by adding voltage ramp onto the current sense input voltage for PWM generation. This greatly improves the close loop stability at CCM and prevents the sub-harmonic oscillation and thus reduces the output ripple voltage.

#### Leading Edge Blanking (LEB)

Each time the power MOSFET is switched on, a turn-on spike occurs across the sensing resistor. The spike is caused by primary side capacitance and secondary side rectifier reverse recovery. To avoid premature termination of the switching pulse, an internal leading edge blanking circuit is built in. During this blanking period (250ns, typical), the PWM comparator is disabled and cannot switch off the gate driver.

#### On Chip Thermal Shutdown (OTP)

When the IC temperature is over 165  $^{\circ}$ C, the IC shuts down. Only when the IC temperature drops to 140  $^{\circ}$ C, IC will restart.

#### Soft Start

DP2354 features an internal 2ms (typical) soft start that slowly increases the threshold of cycle-by-cycle current limiting comparator during startup sequence. It helps to prevent transformer saturation and reduce the stress on the secondary diode during startup. Every restart attempt is followed by a soft start activation.

#### Constant Power Limiting

A proprietary "Constant Power Limiting" block is integrated to achieve constant maximum output power capability over universal AC input range. Based on the duty cycle information, the IC generates OCP threshold according to a proprietary analog algorithm.

#### Over Load Protection (OLP)

If over load occurs, a fault is detected. If this fault is present for more than 75ms (typical), the protection will be triggered, the IC will experience an auto-recovery mode protection as mentioned above. The 75ms delay time is to prevent the false trigger from the power-on and turn-off transient.

### VDD Over Voltage Protection (OVP) and Zener Clamp

When VDD voltage is higher than 31V (typical), the IC will stop switching. This will cause VDD fall down to be lower than  $V_{DD\_OFF}$  (typical 9V) and then the system will restart up again. An internal 35V (typical) zener clamp is integrated to prevent the IC from damage.

#### CS Pin Float Protection

When VDD voltage is higher than  $V_{DD\_ON}$  (21V typical), IC firstly starts to check whether CS pin is floated. If CS pin is floated, switching is blocked and IC enters auto-recovery mode; otherwise, normal work begins. With this protection, system stability is enhanced.

#### Auto Recovery Mode Protection

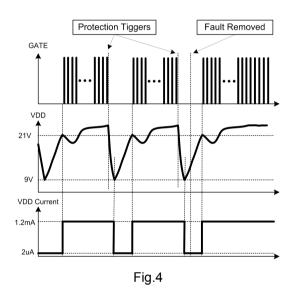

As shown in Fig.4, once a fault condition is detected, PWM switching will stop. This will cause VDD to fall because no power is delivered form the auxiliary winding. When VDD falls to  $V_{DD\_OFF}$  (typical 9V), the protection is reset and the operating current reduces to the startup current, which causes VDD to rise. The system begins switching when VDD reaches to  $V_{DD\_ON}$  (typical 21V). However, if the fault still exists, the system will experience the above mentioned process. If the fault has gone, the system resumes normal operation. In this manner, the auto restart can alternatively enable and disable the switching until the fault condition is disappeared.

### Soft Totem-Pole Gate Driver

DP2354 has a soft totem-pole gate driver with optimized EMI performance. An internal gate

clamp is added for power MOSFET gate protection when high VDD input.

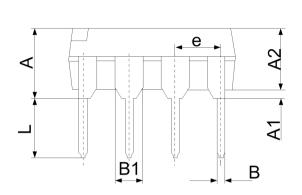

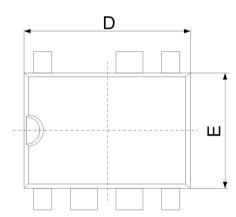

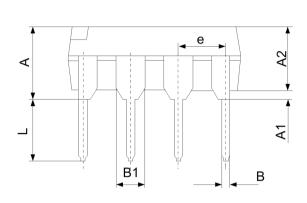

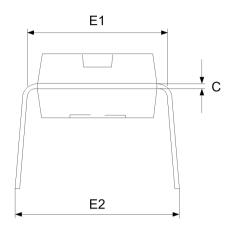

## **Package Dimension**

DIP-7

| Symbol | Dimensions In Millimeters |       | Dimensions In Inches |       |

|--------|---------------------------|-------|----------------------|-------|

|        | Min                       | Max   | Min                  | Max   |

| А      | 3.710                     | 4.310 | 0.146                | 0.170 |

| A1     | 0.510                     |       | 0.020                |       |

| A2     | 3.200                     | 3.600 | 0.126                | 0.142 |

| В      | 0.380                     | 0.570 | 0.015                | 0.022 |

| B1     | 1.524(BSC)                |       | 0.060(BSC)           |       |

| С      | 0.204                     | 0.360 | 0.008                | 0.014 |

| D      | 9.000                     | 9.400 | 0.354                | 0.370 |

| E      | 6.200                     | 6.600 | 0.244                | 0.260 |

| E1     | 7.320                     | 7.920 | 0.288                | 0.312 |

| е      | 2.540(BSC)                |       | 0.100                | (BSC) |

| L      | 3.000                     | 3.600 | 0.118                | 0.142 |

| E2     | 8.400                     | 9.000 | 0.331                | 0.354 |

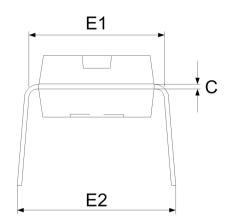

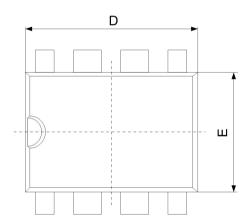

# **Package Dimension**

# DIP8

| Symbol | Dimensions In Millimeters |             | Dimensions In Inches |            |  |  |

|--------|---------------------------|-------------|----------------------|------------|--|--|

|        | Min                       | Max         | Min                  | Max        |  |  |

| Α      | 3.710                     | 5.334       | 0.146                | 0.210      |  |  |

| A1     | 0.381                     |             | 0.015                |            |  |  |

| A2     | 3.175                     | 3.600       | 0.125                | 0.142      |  |  |

| В      | 0.350                     | 0.650       | 0.014                | 0.026      |  |  |

| B1     | 1.524 (                   | 1.524 (BSC) |                      | 0.06 (BSC) |  |  |

| С      | 0.200                     | 0.360       | 0.008                | 0.014      |  |  |

| D      | 9.000                     | 10.160      | 0.354                | 0.400      |  |  |

| E      | 6.200                     | 6.600       | 0.244                | 0.260      |  |  |

| E1     | 7.320                     | 7.920       | 0.288                | 0.312      |  |  |

| е      | 2.540 (BSC)               |             | 0.1 (BSC)            |            |  |  |

| L      | 2.921                     | 3.810       | 0.115                | 0.150      |  |  |

| E2     | 8.200                     | 9.525       | 0.323                | 0.375      |  |  |