#### GENERAL DESCRIPTION

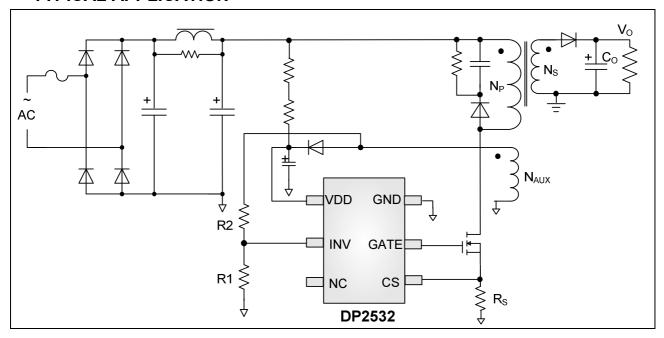

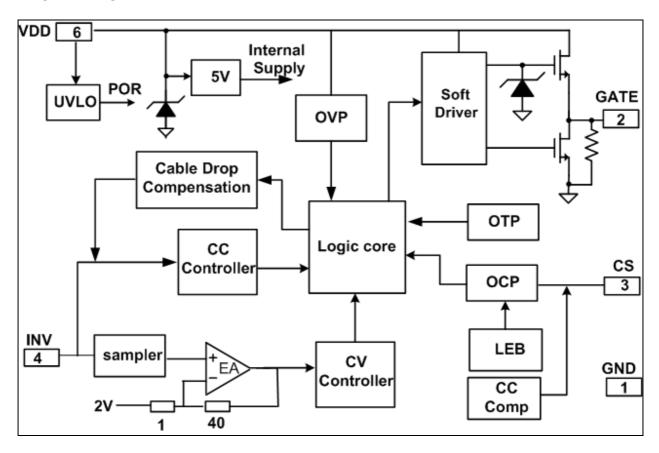

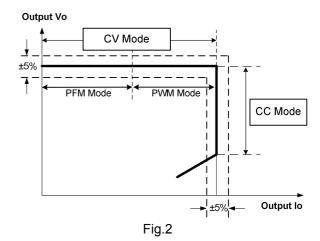

DP2532 is a high performance offline PWM controller for low power AC/DC charger and adapter applications. It operates in primary-side sensing and regulation. Consequently, opto-coupler and TL431 could be eliminated. High Precision Constant Voltage (CV) and Constant Current (CC) control are integrated as shown in the figure below.

In CC control, the current and output power setting can be adjusted externally by the sense resistor Rs at CS pin. In CV control, multi-mode operations are utilized to achieve high performance and high efficiency. In addition, good load regulation is achieved by the built-in Cable Drop Compensation. Device operates in PFM in CC mode as well at large load condition and it operates in PWM with frequency reduction at light/medium load. The chip consumes very low operation current, it can achieve less than 80mW standby power.

DP2532 offers comprehensive protection coverage with auto-recovery features including Cycle-by-Cycle current limiting, VDD Over Voltage Protection (VDD OVP), short circuit protection, built-in leading edge blanking, VDD under voltage lockout (UVLO), OTP, etc.

High precision constant voltage (CV) and constant current (CC) can be achieved by DP2532.

DP2532 is offered in SOT23-6 package..

#### **FEATURES**

- ± 5% Constant Voltage Regulation and Current Regulation at Universal AC Input

- Primary Side Regulation (PSR) Without TL431 and Opto-coupler

- No Need for Control Loop Compensation

- Programmable CV and CC Regulation

- Multi-Mode PWM/PFM Operation

- Output Short Load Protection

- Less than 80mW Standby Power

- Built-in Line Voltage and Primary Winding Inductance Compensation

- Built-in Adaptive Current Peak Regulation

- Programmable Cable Drop Compensation

- Audio Noise Free Operation

- Built-in Over Temperature Protection (OTP)

- Soft Gate Driver for Good EMI Performance

- Built-in Leading Edge Blanking (LEB)

- Cycle-by-Cycle Current Limiting

- VDD Under Voltage Lockout with Hysteresis (UVLO)

- VDD OVP & Clamp

#### **APPLICATIONS**

Low Power AC/DC offline SMPS for

- Cell Phone Charger

- Digital Camera Charger

- Small Power Adapter

- Auxiliary Power for PC, TV etc.

- Linear Regulator/RCC Replacement

## TYPICAL APPLICATION

## **GENERAL INFORMATION**

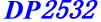

## **Pin Configuration**

The pin map of SOT23-6 package is shown as below.

Ordering Information

| Cracing information |                        |  |  |  |  |

|---------------------|------------------------|--|--|--|--|

| Part Number         | Description            |  |  |  |  |

| DP2532              | SOT23-6, Halogen free, |  |  |  |  |

| DF2332              | 3000Pcs/Reel           |  |  |  |  |

Note: All Devices are offered in Pb-free Package if not otherwise noted.

High Precision CC/CV Primary-Side PWM Controller

**Package Dissipation Rating**

| Package | RθJA (°C/W) |  |  |

|---------|-------------|--|--|

| SOT23-6 | 200         |  |  |

**Absolute Maximum Ratings**

| Parameter                                                                                  | Value         |

|--------------------------------------------------------------------------------------------|---------------|

| VDD Zener Clamp Voltage                                                                    | 34.5V         |

| VDD Clamp Continuous Current                                                               | 10 mA         |

| GATE Voltage                                                                               | 20V           |

| CS Input Voltage                                                                           | -0.3 to 7V    |

| INV Input Voltage                                                                          | -0.3 to 7V    |

| Maximum Operating Junction Temperature T <sub>J</sub>                                      | 150 °C        |

| $\begin{array}{c} \text{Min/Max Storage Temperature} \\ \text{T}_{\text{stq}} \end{array}$ | -55 to 150 °C |

| Lead Temperature (Soldering, 10secs)                                                       | 260 °C        |

**Note:** Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

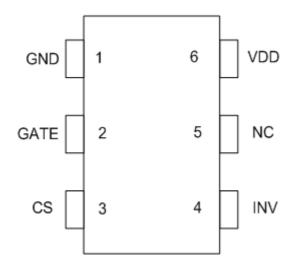

# **Marking Information**

# Description:

- 1.1. The first line of the five points represent the assembly house commissioning date, a total of 1-31.

- 1.2. DPXX for product name: D represent DP brand, P represents the power supply, XX on behalf of the commodity (32: DP2532)

- 1.3. After the product name, X on behalf of the month, 1-12 months.

- 1.4. The third row four point on behalf of the last year.

## **TERMINAL ASSIGNMENTS**

| Pin Num | Pin Name | I/O | Description                                                                                                                  |

|---------|----------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Р   | IC Ground.                                                                                                                   |

| 2       | GATE     | 0   | Totem-pole gate driver for power MOSFET                                                                                      |

| 3       | CS       | I   | Current sense input. Connected to power MOSFET current sensing resistor node                                                 |

| 4       | INV      | I   | The voltage feedback from auxiliary winding. Connected to resistor divider from auxiliary winding reflecting output voltage. |

| 5       | NC       | -   | No connect.                                                                                                                  |

| 6       | VDD      | Р   | Power supply.                                                                                                                |

# **BLOCK DIAGRAM**

# RECOMMENDED OPERATING CONDITION

| Symbol         | Parameter                     | Min | Max | Unit |

|----------------|-------------------------------|-----|-----|------|

| VDD            | VDD Supply Voltage            | 11  | 27  | V    |

| T <sub>A</sub> | Operating Ambient Temperature | -40 | 85  | °C   |

# **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = 25<sup>o</sup>C, VDD=18V if not otherwise noted)

| Symbol                               | Parameter                                     | Test Conditions                             | Min  | Тур  | Max  | Unit |  |

|--------------------------------------|-----------------------------------------------|---------------------------------------------|------|------|------|------|--|

| Supply Voltage                       | ge Section (VDD Pin)                          |                                             |      |      |      |      |  |

| I <sub>VDD_st</sub>                  | Start-up current into VDD pin                 |                                             |      | 2    | 20   | uA   |  |

| I <sub>VDD_Op</sub>                  | Operation Current                             | V <sub>INV</sub> =3V,GATE=0.5nF,<br>VDD=20V |      | 1    | 1.5  | mA   |  |

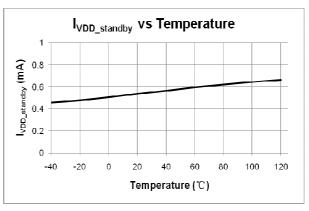

| I <sub>VDD standby</sub>             | Standby Current                               |                                             |      | 0.5  | 1    | mA   |  |

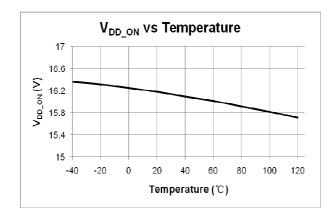

| $V_{DD\_ON}$                         | VDD Under Voltage Lockout Exit                |                                             | 15   | 16.3 | 17.5 | V    |  |

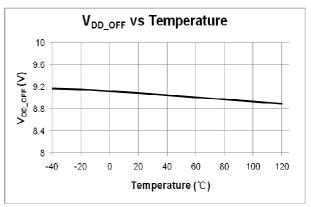

| $V_{DD\_OFF}$                        | VDD Under Voltage Lockout Enter               |                                             | 8    | 9    | 10   | V    |  |

| $V_{DD\ OVP}$                        | VDD OVP Threshold                             |                                             | 28   | 30   | 32   | V    |  |

| $V_{\text{DD\_Clamp}}$               | VDD Zener Clamp<br>Voltage                    | $I(V_{DD}) = 7 \text{ mA}$                  | 32.5 | 34.5 | 36.5 | V    |  |

| Feedback Inp                         | ut Section (INV Pin)                          |                                             |      |      |      |      |  |

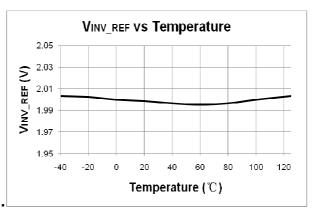

| $V_{INV\_REF}$                       | Internal Error Amplifier (EA) Reference Input |                                             | 1.97 | 2.0  | 2.03 | V    |  |

| $V_{INV\_SLP}$                       | Short Load Protection (SLP) Threshold         |                                             |      | 0.7  |      | V    |  |

| T <sub>INV_Short</sub>               | Short Load Protection (SLP) Debounce Time     |                                             |      | 10   |      | ms   |  |

| $V_{INV\_DEM}$                       | Demagnetization Comparator Threshold          |                                             |      | 25   |      | mV   |  |

| T <sub>off min</sub>                 | Minimum OFF time                              |                                             |      | 2    |      | us   |  |

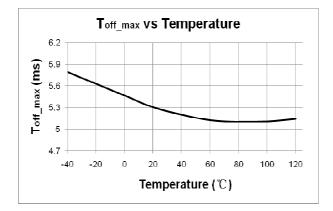

| T <sub>off max</sub>                 | Maximum OFF time                              |                                             |      | 5    |      | ms   |  |

| I <sub>Cable_max</sub>               | Maximum Cable Drop compensation current       |                                             |      | 63   |      | uA   |  |

| Current Sense Input Section (CS Pin) |                                               |                                             |      |      |      |      |  |

| T <sub>LEB</sub>                     | CS Input Leading Edge Blanking Time           |                                             |      | 500  |      | ns   |  |

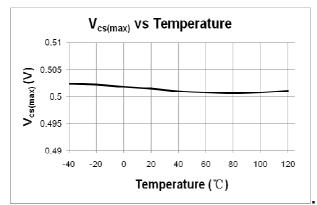

| $V_{cs(max)}$                        | Current limiting threshold                    |                                             | 490  | 500  | 510  | mV   |  |

| T <sub>D_OCP</sub>                   | Over Current Detection and Control Delay      | GATE=0.5nF                                  |      | 100  |      | ns   |  |

| Over tempera                         | ture Protection                               |                                             |      |      |      |      |  |

| T <sub>SD</sub>                      | Thermal Shutdown                              |                                             |      | 165  |      | °C   |  |

| T <sub>RC</sub>                      | Thermal Recovery                              |                                             |      | 135  |      | °C   |  |

| Gate Drive Output (GATE Pin)         |                                               |                                             |      |      |      |      |  |

| $V_{G\_Clamp}$                       | Output Clamp Voltage<br>Level                 | VDD=24V                                     |      | 16   |      | V    |  |

| T_r                                  | Output Rising Time                            | GATE=0.5nF                                  |      | 700  |      | ns   |  |

| T_f                                  | Output Falling Time                           | GATE=0.5nF                                  |      | 40   |      | ns   |  |

# **CHARACTERIZATION PLOTS**

## **OPERATION DESCRIPTION**

DP2532 is a cost effective PWM controller optimized for off-line low power AC/DC applications including battery chargers and adapters. It operates in Primary Side Regulation (PSR), thus opto-coupler and TL431 are not required. High precision CV and CC control can be achieved to meet most small power charger and adapter applications requirements.

#### Startup Current and Start up Control

Startup current of DP2532 is designed to be very low (typically 2uA) so that VDD could be charged up above UVLO threshold level and device starts up quickly. A large value startup resistor can therefore be used to minimize the power loss yet reliable startup in application.

#### Operating Current

The operating current of DP2532 is as low as 1mA. Good efficiency is achieved by the low operating current together with extended burst mode control schemes at No/light load conditions.

#### Primary Side CC/CV Control

DP2532 is designed to produce good CC/CV control. In charger applications, a discharged battery charging starts in CC portion of the curve until it is nearly full charged and smoothly switched to operate in CV portion of the curve. In an AC/DC adapter, the normal operation occurs only on the CV portion of the curve. The CC portion provides output current limiting.

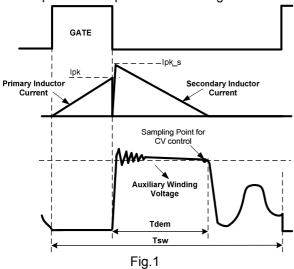

As shown by Fig 1, when the GATE is off the secondary side diode is conducted and the auxiliary winding voltage is proportion to the output voltage. Via a resistor divider connected

between the auxiliary winding and INV (pin 3), the auxiliary voltage is sampled at the end of the demagnetization and it is hold until the next sampling. The sampled voltage is compared with  $V_{\text{INV\_REF}}$  (2.0V) and the error is amplified by an internal Error Amplifier (EA). The internal EA output reflects the load condition and control the PWM switching frequency to regulate the output voltage, thus constant voltage (CV) can be achieved.

When system enters over load condition, the output voltage falls down and the INV sampled voltage should be lower than 2V internal reference which makes system enter CC Mode automatically.

### Multi Mode CV Operation for High Efficiency

DP2532 is a multi-mode PSR controller. In CV mode, the controller changes the mode of operation by sampling INV voltage. Under the medium to large load conditions, the IC operates in PWM mode, which improves the system audio noise performance. Under normal to light load conditions, the IC operates in PFM mode to achieve high efficiency. The IC can achieve less than 80mW standby power, as shown in Fig.2

## CC Operation Switching Frequency

The switching frequency of DP2532 is adaptively controlled according to the load conditions and the operation modes.

For flyback operation in DCM, the maximum output power is given by

$$Po_{MAX} = \frac{1}{2} L_P F_{SW} I_P^2$$

Where Lp indicate the inductance of primary winding and Ip is the peak current of primary winding.

Refer to the equation above, the change of the primary winding inductance results in the change of the maximum output power and the constant output current in CC mode. To compensate the change from variations of primary winding inductance, the switching frequency is locked by and internal loop such that the switching frequency is

$$F_{SW} = \frac{1}{2T_{DEM}}$$

Since  $T_{DEM}$  is inversely proportional to the inductance, as a result, the product of Lp and Fsw is constant, thus the maximum output power and constant current in CC mode will not change as primary winding inductance changes. Up to  $\pm$  10% variation of the primary winding inductance can be compensated.

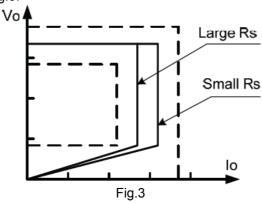

### Adjustable CC Point and Output Power

In DP2532, the CC point and maximum output power can be externally adjusted by external current sense resistor Rs at CS pin as illustrated in typical application diagram. The larger Rs, the smaller CC point is, and the smaller output power becomes, and vice versa as shown in Fig.3.

## Current Sensing and Leading Edge Blanking

Cycle-by-Cycle current limiting is offered in DP2532. The switch current is detected by a sense resistor into the CS pin. An internal leading edge blanking circuit is built in. During this blanking period (500ns, typical), the cycle-by-cycle current limiting comparator is disabled and cannot switch off the GATE driver.

## Audio Noise Free Operation

DP2532 can provide audio noise free operation from full loading to zero loading.

## Optimized Dynamic Response

In DP2532, an optimized dynamic response control is integrated to improve system dynamic

response performance, which enables charger system to meet the USB charge requirements.

# Programmable Cable Drop Compensation

In DP2532, cable drop compensation is implemented to achieve good load regulation. An offset voltage is generated at INV pin by an internal current flowing into the resistor divider. The current is proportional to the switching off time, as a result, it is inversely proportional to the output load current, thus the drop due to the cable loss can be compensated. As the load current decreases from full-load to no-load, the offset voltage at INV pin will increase. It can also be programmed by adjusting the resistance of the divider to compensate the drop for various cable lines used.

The percentage of maximum compensation is

$$\frac{\Delta V}{Vout} \approx \frac{Icable\_max \times (R1//R2)}{V_{INV\_REF}} \times 100\%$$

$\Delta V$  is load compensation voltage and Vout is output voltage:

For example: R1=3K  $\Omega$  , R2=18K  $\Omega$  , The percentage of maximum compensation is given by

$$\frac{\Delta V}{Vout} = \frac{63uA \times (3K//18K)}{2V} \times 100\% = 8.1\%$$

## Over Temperature Protection (OTP)

When the IC temperature is over 165 °C, the IC shuts down. Only when the IC temperature drops to 135 °C, IC will restart.

#### Output Short Load Protection

In DP2532, the output is sampled on INV pin and then compared with a threshold of UVP (0.7V typically) after an internal blanking time (10ms typical). When sensed INV voltage is below 0.7V, the IC will enter into Short Load Protection (SLP) mode, in which the IC will enter into auto recovery protection mode.

#### VDD OVP and Zener Clamp

When VDD voltage is higher than 30V (typical), the IC will stop switching. This will cause VDD fall down to be lower than VDD\_OFF (typical 9V) and then the system will restart up again. An internal 34.5V (typical) zener clamp is integrated to prevent the IC from damage.

#### Soft Gate Drive

DP2532 has a soft totem-pole gate driver with optimized EMI performance. An internal 16V clamp is added for MOSFET gate protection at higher than expected VDD input.

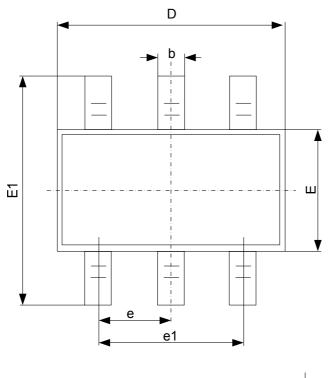

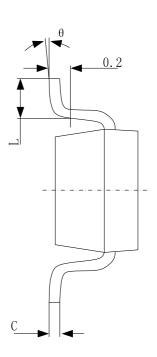

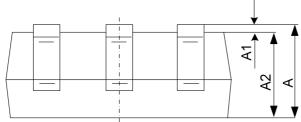

# **Package Dimension**

# SOT23-6

| Symbol | Dimensions In Millimeters |             | Dimensions In Inches |       |  |

|--------|---------------------------|-------------|----------------------|-------|--|

| Symbol | Min                       | Max         | Min                  | Max   |  |

| Α      | 0.900                     | 1.200       | 0.035                | 0.047 |  |

| A1     | 0.000                     | 0.150       | 0.000                | 0.006 |  |

| A2     | 0.900                     | 1.100       | 0.035                | 0.043 |  |

| b      | 0.300                     | 0.500       | 0.012                | 0.020 |  |

| С      | 0.100                     | 0.200       | 0.004                | 0.008 |  |

| D      | 2.800                     | 3.020       | 0.110                | 0.119 |  |

| Е      | 1.500                     | 1.700       | 0.059                | 0.067 |  |

| E1     | 2.600                     | 3.000       | 0.102                | 0.118 |  |

| е      | 0.950                     | 0.950 (BSC) |                      | (BSC) |  |

| e1     | 1.800                     | 2.000       | 0.071                | 0.079 |  |

| L      | 0.300                     | 0.600       | 0.012                | 0.024 |  |

| θ      | 0°                        | 8°          | 0°                   | 8°    |  |