# **DP3115**

40V, 2.5A Monolithic Buck Converter with CC/CV Control

**Rev2.2**

## Description

DP3115 integrates a high efficiency synchronous step-down switching regulator, which includes a 40V,  $80m\Omega$  high side P-MOS and a 40V,  $39m\Omega$  low side N-MOS to provide 2.5A continuous load current over 10V to 40V wide operating input voltage with 38V input over voltage protection. Conductance Peak current mode control provides fast transient responses and cycle-by-cycle current limiting.

DP3115 has configurable line drop compensation, configurable charging current limit. A simple Power system with few external components is possible with DP3115.

- Applications

- USB car charger

- Portable charging device

- General purpose USB charger

- General purpose DC-DC conversion

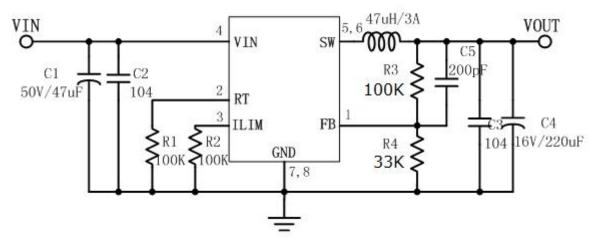

## Typical Application Schematic

## Features

- 2.5A continuous output current capability

- 10V to 40V wide operating input range with input Over Voltage Protection

- Integrated 40V, 80m Ω high side and 40V, 39m Ω low side power MOSFET switches

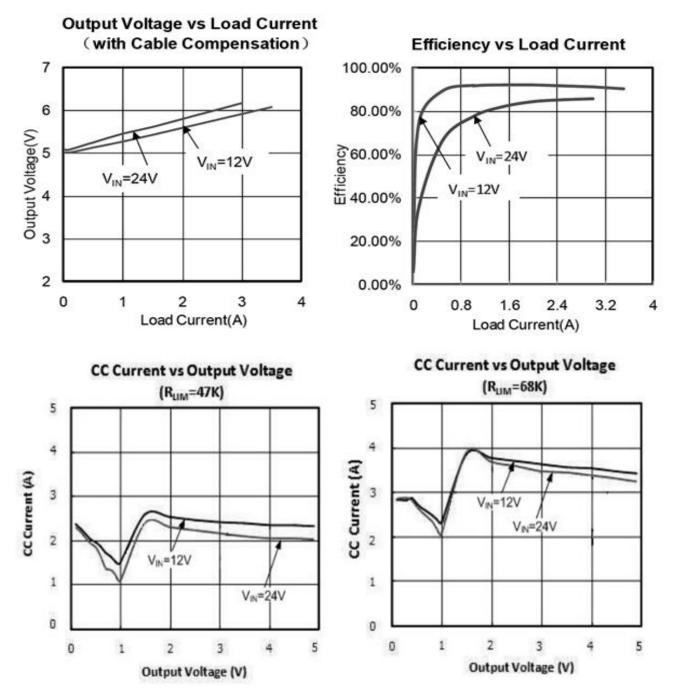

- Up to 93% efficiency

- CV Mode control (Constant voltage). Cycle-by-Cycle Current Limiting

- Configurable Line Drop Compensation with resistor

- Internal Soft-Start limits the inrush current at turn-on

- Internal compensation to save external components

- Stable with Low ESR Ceramic Output Capacitors

- Configurable Switching Frequency with resistor

- Over-Temperature Protection

- 38V input voltage protection to protect power MOSFETs from working at high current ,high input voltage condition

- Fixed Soft start time

- Under-Input Voltage Lockout.

- Over-Temperature Protection

- SOP-8 Package

VOUT is set by R3 and R4, calculated by the following equation : **VOUT=1.21V\*[1+(R3/R4)]** The stability of power system can be enhanced when using C5.

DP3115 Rev2.2

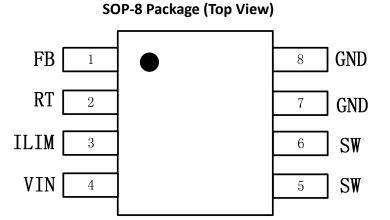

## Pin Configuration and Functions

| Pin    |      | Description                                                                                                                |  |  |  |

|--------|------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Number | Name | Description                                                                                                                |  |  |  |

|        |      | Feedback Input PIN. FB senses the output voltage. Connect FB with a resistor divider connected                             |  |  |  |

| 1      | FB   | between the output and ground. <b>FB</b> is a sensitive node. Keep <b>FB</b> away from <b>SW</b> . It is better to connect |  |  |  |

|        |      | a 200pF ceramic capacitor between <b>FB</b> pin and <b>VOUT</b> .                                                          |  |  |  |

| 2      | RT   | Resistor to set scillation frequency.Connect to GND. Keep RT away from SW                                                  |  |  |  |

| 3      | ILIM | Resistor to set Ipeak of inductance. Connect to GND. Keep ILIM away from SW                                                |  |  |  |

|        |      | Power Input PIN. Vin supplies the power to the IC. Supply Vin with a 10V to 40V power source. Bypass                       |  |  |  |

| 4      | VIN  | Vin to GND with a large capacitor and at least another 0.1uF ceramic capacitor to eliminate noise on                       |  |  |  |

|        |      | the input to the IC. Put the capacitors close to Vin and GND pins.                                                         |  |  |  |

| 5      | SW   | Dower Switching pin. Connect this pin to the switching node of industor                                                    |  |  |  |

| 6      | 300  | Power Switching pin. Connect this pin to the switching node of inductor.                                                   |  |  |  |

| 7      | CND  |                                                                                                                            |  |  |  |

| 8      | GND  | GROUND                                                                                                                     |  |  |  |

## Absolute Maximum Ratings(Note1)

|                | PARAMETER                | MIN  | MAX   | Unit |

|----------------|--------------------------|------|-------|------|

|                | V <sub>IN</sub> to GND   | -0.3 | 40    | V    |

|                | V <sub>RT</sub> to GND   | -0.3 | 6     | V    |

| Input Voltages | V <sub>ILIM</sub> to GND | -0.3 | 6     | V    |

|                | V <sub>FB</sub> to GND   | -0.3 | 6     | V    |

|                | V <sub>sw</sub> to GND   | -0.3 | VIN+1 | V    |

### Handling Ratings

| PARAMETER       | DEFINITION                | MIN | MAX | Unit |

|-----------------|---------------------------|-----|-----|------|

| T <sub>ST</sub> | Storage Temperature Range | -65 | 150 | °C   |

| TJ              | Junction Temperature      |     | 150 | °C   |

| Τι              | Lead Temperature          |     | 260 | °C   |

#### DEVELOPER MICROELECTRONICS

## DP3115

## **Rev2.2**

## ■ Electrical Characteristics(Typical at Vin = 12V, TJ=25°C, unless otherwise noted.)

| Parameter                                 | Symbol | Conditions | Min   |      | Max   | Units |

|-------------------------------------------|--------|------------|-------|------|-------|-------|

| Fardineter                                | Symbol | Conditions |       | Тур  | Wax   | Units |

| Input Voltage                             | Vin    |            | 10    |      | 40    | V     |

| No-load current                           | lcc    | ILOAD=0A   | 0     | 0.5  | 2     | mA    |

| Stand By current                          | lsт    |            | 0     | 0.2  | 1     | mA    |

| Input UVL0                                | Vuvlo  |            |       | 6.8  | 8     | V     |

| Input UVLO hysteresis voltage             | ΔVuvlo |            | 0.2   | 0.6  | 1     | V     |

| Voltage of FB                             | Vfb    |            | 1.188 | 1.21 | 1.236 | V     |

| Input current of FB                       | lfв    |            |       |      | 0.5   | uA    |

|                                           | Fosc   |            | 80    |      | 500   | KHz   |

| operating frequency range                 |        | RT=100K    | 80    | 120  | 150   |       |

| Max duty cycle                            | DC     |            |       |      | 100   | %     |

| R <sub>DSON</sub> of P-MOS                | Rpfet  |            |       | 80   |       | mΩ    |

| R <sub>DSON</sub> of N-MOS                | RNFET  |            |       | 39   |       | mΩ    |

| Over-Temperature Protection               | Tsd    |            |       | 150  |       | °C    |

| Over-Temperature Protection<br>hysteresis | ∆Tsd   |            |       | 30   |       | Ĉ     |

Test Condition: TA = 25°C, VIN=12V, CIN=100uF, COUT=470uF, L=47uH, unless otherwise noted.

## **Rev2.2**

**DP3115**

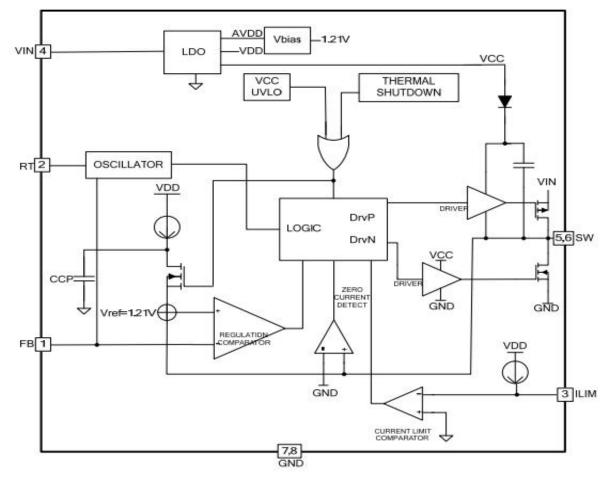

## Functional Block Diagram

#### Overview

DP3115 works at a constant frequency mode. The output Voltage is set by  $V_{FB}$  which is divided by R3 and R4.DP3115 adjusts the drop-down current of FB by monitoring the Ipeak of inductance and  $V_{FB}$  to stabilize the output voltage.

At normal operation mode, DP3115 controls and drives the internal P-MOS and N-MOS to on and off by internal oscillator. When P-MOS is ON,N-MOS is OFF.

#### Thermal Shutdown

The internal thermal-shutdown circuitry forces the device to stop switching if the junction temperature exceeds 160°C typically.

#### Inductance peak current limiting

DP3115 Limit the P-MOS peak current to limit input power, DP3115 detect the peak current of P-MOS at toff of every cycle, if higher than the set limit DP3115 will shut down the P-MOS. When the temperature rise up, the R<sub>DSON</sub> of P-MOS will become larger.

| Rilim      | 56K  | 62K  | 68K  | 75K  | 90K  | 100K | 110K | 120K | 130K |

|------------|------|------|------|------|------|------|------|------|------|

| Type Ipeak | 2.3A | 2.5A | 2.7A | 2.9A | 3.2A | 3.5A | 3.7A | 3.9A | 4.1A |

#### The lpeak of DP3115 Actual tested on a DP3115 demo board

$Ipeak(A) \approx 0.5 \cdot R_{DSON} \cdot RILIM(K\Omega)$

#### DEVELOPER MICROELECTRONICS

#### Oscillation frequency

The oscillation frequency of DP3115 is set by a resistor connected between RT and GND. This resistor should be placed as close as possible to the DP3115. The output current of RT is 12uA. If RT value is smaller, the oscillation frequency of DP3115 will be higher.

| RT        | <b>20K</b> Ω | <b>27 Κ</b> Ω | <b>36Κ</b> Ω | <b>47 K</b> Ω | <b>62Κ</b> Ω | <b>75K</b> Ω | <b>100Κ</b> Ω |

|-----------|--------------|---------------|--------------|---------------|--------------|--------------|---------------|

| Type Freq | 500KHz       | 400KHz        | 300KHz       | 240KHz        | 190KHz       | 160KHz       | 120Kz         |

#### The frequency of DP3115 Actual tested on a DP3115 demo board

#### Output Shutdown voltage

DP3115 will shutdown the output if the output voltage is lower than about 2V when the output load is too heavy.

#### Setting Output Voltage

The output voltage is set by FB voltage, which is divided by resistor (R3 & R4) from output node to Ground. That resistor with 1% or higher accuracy is preferred. The output voltage value is set by equation as below. Suggest R3/R4=3.16:

#### R3 = R4\*[(VOUT / VREF) - 1]

Vref is the internal reference voltage of DP3115, 1.21V.

#### Line drop compensation

If USB cable is too long or resistance value is high, the voltage of charging device end will be dropped a lot. If the voltage across the load input terminals is too low, it will affect charging time. So recommend to adjust the output voltage of charger to compensate this voltage drop. DP3115 has an excellent configurable line drop compensation function. The compensation value of line drop can be programmed by the down feedback resistor R4. The value can be roughly calculated by equation as below:

#### ΔVout(V)=3\*R4(KΩ)\*Iout(A)/1000

#### Inductor selection

An inductor is required to supply constant current to the load while being driven by the switched input voltage. The common value of the inductance is between **4.7uH** to **47uH**. A larger value inductor will result in less current ripple and lower output voltage ripple. However, the larger value inductor will have larger physical size, higher DC resistance, and/or lower saturation current. A good rule to calculate the inductance is to allow the peak-to-peak ripple current in the inductor to be approximately 25% of the maximum load current. At the same time, it is needed to make sure that the peak inductor current is below the inductor saturation current.

The inductance value can be calculated by:

$$L = \frac{V_{OUT}}{f_{s} \times \Delta I_{L}} \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

Where VOUT is the output voltage, VIN is the input voltage, fs is the switching frequency, and  $\Delta L$  is the peak-to-peak inductor ripple current.

The choice of which style inductor to use mainly depends on the price vs. size requirements and any EMI constraints.

#### Input capacitors selection

The input current to the step-down converter is discontinuous, therefore a capacitor is required to supply the AC current to the converter. It is recommend to use low ESR capacitors to optimize the performance. Ceramic capacitor is preferred, but tantalum or low-ESR electrolytic capacitors may also meet the requirements. It is better to choose X5R or X7R dielectrics when using ceramic capacitors.

Since the input capacitor (C<sub>IN</sub>) absorbs the input switching current, a good ripple current rating is required for the capacitor. The

RMS current in the input capacitor can be estimated by:

$$I_{CIN} = I_{load} \times \sqrt{\frac{V_{OUT}}{V_{IN}}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

The worst-case condition occurs at VIN = 2×VOUT, where:

$$I_{CIN} = \frac{I_{load}}{2}$$

For simplification, choose the input capacitor whose RMS current rating is greater than half of the maximum load current. When electrolytic or tantalum capacitors are used, a small, high quality ceramic capacitor, i.e. 0.1µF, should be placed as close to the IC as possible. When ceramic capacitors are used, make sure that they have enough capacitance to maintain voltage ripple at input. The input voltage ripple caused by capacitance can be estimated by:

$$\Delta V_{IN} = \frac{I_{load}}{f_s \times C_{IN}} \times \frac{V_{OUT}}{V_{IN}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

CIN is the input capacitance.

#### Output capacitors selection

The output capacitor (C<sub>OUT</sub>) is required to maintain the DC output voltage. Ceramic, tantalum, or low ESR electrolytic capacitors are recommended.

Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_{s} \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times \left(R_{ESR} + \frac{1}{8 \times f_{s} \times C_{OUT}}\right)$$

Where L is the inductor value, RESR is the equivalent series resistance (ESR) value of the output capacitor and COUT is the output capacitance value. In the case of ceramic capacitors, the impedance at the switching frequency is dominated by the capacitance. The output voltage ripple is mainly determined by the capacitance. For simplification, the output voltage ripple can be estimated by:

$$\Delta V_{OUT} = \frac{V_{OUT}}{8 \times f_8^2 \times L \times C_{OUT}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

In the case of tantalum or electrolytic capacitors, the ESR dominates the impedance at the switching frequency. For simplification, the output ripple can be approximated to:

$$\Delta V_{OUT} = \frac{V_{OUT}}{f_s \times L} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right) \times R_{ESR}$$

The characteristics of the output capacitor also affect the stability of the regulation system. The DP3119B can be optimized for a wide range of capacitance and ESR values.

#### PCB Layout

PCB layout is a critical portion of good power supply design. The following guidelines will help users design a PCB with the best power conversion efficiency, thermal performance, and minimized EMI.

1. The feedback network, resistor R<sub>3</sub> and R<sub>4</sub>, should be kept close to FB pin. V<sub>out</sub> sense path should stay away from noisy nodes, such as SW signals and preferably through a layer on the other side of shielding layer.

2. The input bypass capacitor C<sub>1</sub> and C<sub>2</sub> must be placed as close as possible to the V<sub>IN</sub> pin and ground. Grounding for both the input and output capacitors should consist of localized top side planes that connect to the GND pin and PAD. It is a good practice to place a ceramic cap near the V<sub>IN</sub> pin to reduce the high frequency injection current.

3. The inductor L should be placed close to the SW pin to reduce magnetic and electrostatic noise.

4. The output capacitor, Cour should be placed close to the junction of L. The L, and Cour trace should be as short as possible to reduce conducted and radiated noise and increase overall efficiency.

5. The ground connection for C<sub>1</sub>, C<sub>2</sub> and C<sub>3</sub>, C<sub>4</sub> should be as small as possible and connect to system ground plane at only one spot (preferably at the Court ground point ) to minimize injecting noise into system ground plane.

6. Place R1 and R2 as close as possible to the chip and stay away from noisy nodes such as SW, BST.

7. Large GND Copper Pour near IC is recommended to minimize the heat of DP3115.

|         |            |                | l L     |

|---------|------------|----------------|---------|

|         |            |                |         |

| ula a l | Dimensions | In Millimeters | Dimensi |

| npol    | Min        | Max            | Min     |

| (       | 1.350      | 1.750          | 0.053   |

| 1       | 0.100      | 0.250          | 0.004   |

| 2       | 1.350      | 1.550          | 0.053   |

D

## Packaging Information

E

ions In Inches Sym Max A 0.069 A1 0.010 A2 0.061 1.550 0.003 b 0.330 0.510 0.013 0.020 С 0.170 0.250 0.006 0.010 D 4.700 5.100 0.185 0.200 Е 3.800 4.000 0.150 0.157 E1 5.800 6.200 0.228 0.244 1.270(BSC) 0.050(BSC) е L 0.400 1.270 0.016 0.050 0° 8° 0° θ 8°

DP3115

#### IMPORTANT NOTICE

DP assumes no responsibility for any errors which may appear in this document.

DP reserves the right to change devices or specifications detailed herein at any time without notice.

DP does not assume any liability arising out of the application or use of any product described herein; neither it does it convey any license under its patent rights, nor the rights of others.

DP products are not authorized for use as critical components in life support devices or systems without written approval letter from the Chief Executive Officer of DP. The use of products in such applications shall assume all risks of such use and will agree to not hold against DP for all damages.